# Optimization-Based Mappers and Lower Bounds for Tensor Problems

Grace Dinh

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-293 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-293.html

December 22, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Optimization-Based Mappers and Lower Bounds for Tensor Problems

Ву

Grace Dinh

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

Engineering - Electrical Engineering and Computer Science

in

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor James Demmel, Chair Professor Kurt Keutzer Professor Satish Rao Professor Bernd Sturmfels

Fall 2023

# Optimization-Based Mappers and Lower Bounds for Tensor Problems

Copyright 2023 By Grace Dinh

#### Abstract

Optimization-Based Mappers and Lower Bounds for Tensor Problems

By

#### Grace Dinh

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor James Demmel, Chair

Obtaining good performance for tensor problems requires computing an architecture-specific mapping from the algorithm to the target hardware. Choosing a mapping requires optimizing an objective function over a large, nonconvex space; this objective function represents a performance metric which may be modeled, simulated, or (if possible) measured. Each such objective function incurs different tradeoffs in terms of speed, accuracy, and the strength of results that can be formally proven, and as a result requires its own optimization methods. In this dissertation, we describe optimization approaches for several performance objectives.

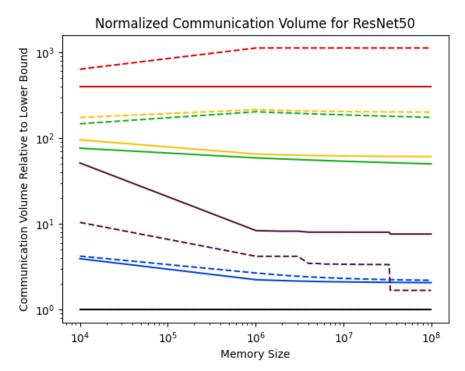

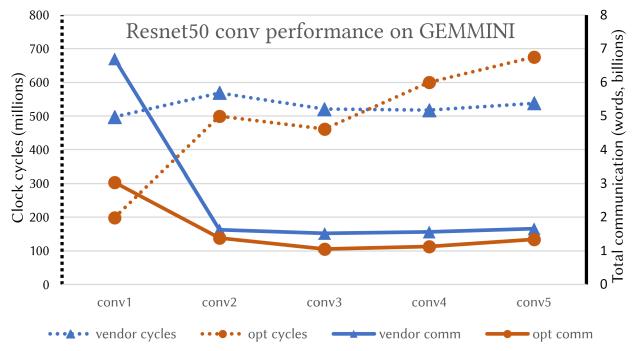

- In a simple abstract memory hierarchy model, we derive an unconditional communication lower bound for "projective" tensor operations (which includes most dense linear algebra) and convolutions. We show that this can always be attained (up to a constant factor) by solving a mathematical optimization problem, and that these methods provide significant benefits in practice, halving the communication volume in one case.

- We extend these lower bound techniques and corresponding algorithms to handle combinations of communication and convolution for *randomized* matrix multiplication.

- We then describe how to incorporate support for additional mapping decisions and to

account for more architectural information by extending our optimization-based approach to support analytical performance models. While these performance models are

too complex to prove strong lower bounds for, empirical results show that optimizationbased methods can find more performant mappings using significantly less runtime and

sample complexity than pure search-based methods.

# Contents

| Contents  1 Introduction |                                                      |                                                      |               |  |  |

|--------------------------|------------------------------------------------------|------------------------------------------------------|---------------|--|--|

| •                        |                                                      |                                                      |               |  |  |

| 2                        | <b>Bac</b> 2.1                                       | ekground                                             |               |  |  |

|                          |                                                      | Architectures for Tensor Computations                |               |  |  |

|                          | 2.2                                                  | Mapping                                              |               |  |  |

|                          |                                                      | 11 0 1                                               |               |  |  |

|                          |                                                      | 2.2.1.1 Tiling                                       | 1             |  |  |

|                          |                                                      | r                                                    | 1             |  |  |

|                          |                                                      | 11 0                                                 | 1<br>1        |  |  |

|                          |                                                      | 1 1                                                  | 1             |  |  |

|                          |                                                      | 3 11                                                 | 1             |  |  |

|                          |                                                      | 0 11 0                                               | 1             |  |  |

|                          | 2.3                                                  | 2.2.2.2 Searching For Mappings                       | 1             |  |  |

|                          | 2.3                                                  | 2.3.1 Computational DAGs and Pebble Games            | 1             |  |  |

|                          |                                                      | 2.3.1 Computational DAGs and Febble Games            | $\frac{1}{2}$ |  |  |

|                          |                                                      | 2.3.3 The Discrete Brascamp-Lieb Inequalities        | $\frac{2}{2}$ |  |  |

|                          |                                                      | 2.5.5 The Discrete Brascamp-Lieb mequanties          | 4             |  |  |

| 3                        | Tilings and Lower Bounds for Projective Nested Loops |                                                      |               |  |  |

|                          | 3.1                                                  | The Lower Bound                                      | 3             |  |  |

|                          |                                                      | 3.1.1 One Small Index                                | 3             |  |  |

|                          |                                                      | 3.1.2 Multiple Small Bounds                          | 3             |  |  |

|                          | 3.2                                                  | Tiling construction                                  | 4             |  |  |

|                          | 3.3                                                  | Examples and Applications                            | 4             |  |  |

|                          |                                                      | 3.3.1 Matrix-Matrix and Matrix-Vector Multiplication | 4             |  |  |

|                          |                                                      | 3.3.2 Tensor Contraction                             | 4             |  |  |

|                          |                                                      | 3.3.3 <i>n</i> -body Pairwise Interactions           | 4             |  |  |

| 4                        | T;I;                                                 | ngs and Communication Lower Bounds for Convolutions  | 5             |  |  |

|                          |                                                      | nga ang vonununganon nower bounds tot vonvonthous    | J             |  |  |

|    |                                                                    | 4.1.1  | Derivation of the Trivial Bound                  | 52 |  |  |  |

|----|--------------------------------------------------------------------|--------|--------------------------------------------------|----|--|--|--|

|    |                                                                    | 4.1.2  | Derivation of the "Large Loop Bound" Lower Bound | 52 |  |  |  |

|    |                                                                    | 4.1.3  | Derivation of the "Small Filter" Lower Bound     | 58 |  |  |  |

|    | 4.2                                                                | A Tili | ng that Obtains the Lower Bound                  | 61 |  |  |  |

|    | 4.3                                                                | Perfor | mance Analysis                                   | 65 |  |  |  |

|    |                                                                    | 4.3.1  | Comparison of Convolution Algorithms             | 65 |  |  |  |

|    |                                                                    | 4.3.2  | Benchmarks on accelerators                       | 65 |  |  |  |

| 5  | Communication-Computation Combinations for Randomized Matrix Mul-  |        |                                                  |    |  |  |  |

|    | tipl                                                               |        |                                                  | 69 |  |  |  |

|    | 5.1                                                                |        | lower Bound                                      | 70 |  |  |  |

|    | 5.2                                                                |        | thms for Attaining the Lower Bound               | 73 |  |  |  |

| 6  | Optimizing More Realistic Performance Models and Simulated Perfor- |        |                                                  |    |  |  |  |

|    | mance                                                              |        |                                                  |    |  |  |  |

|    | 6.1                                                                |        | sly Optimizing Proxy Models                      | 78 |  |  |  |

|    |                                                                    | 6.1.1  | Representing mappings                            | 78 |  |  |  |

|    |                                                                    | 6.1.2  | Mapping Constraints                              | 79 |  |  |  |

|    |                                                                    | 6.1.3  | Optimization                                     | 80 |  |  |  |

|    | 6.2                                                                | Bayesi | ian Optimization                                 | 82 |  |  |  |

|    |                                                                    | 6.2.1  | Mapspace Encoders                                | 83 |  |  |  |

|    |                                                                    | 6.2.2  | Evaluation                                       | 85 |  |  |  |

|    |                                                                    | 6.2.3  | Convergence                                      | 85 |  |  |  |

|    |                                                                    | 6.2.4  | Transfer Learning                                | 86 |  |  |  |

|    |                                                                    | 6.2.5  | Sensitivity Analysis                             | 87 |  |  |  |

| 7  | Cor                                                                | clusio | n and Future Work                                | 89 |  |  |  |

| Ri | Bibliography                                                       |        |                                                  |    |  |  |  |

## Acknowledgments

Many people have supported me throughout my time in graduate school, and I would not be the person I am today without them. This dissertation is dedicated to them.

I'd like to thank my advisor, James Demmel for close to a decade of mentorship, wisdom, support, and always fascinating discussions, both technical and nontechnical.

I've worked with many brilliant people during my time as a graduate student, especially Julian Bellavita, Gilbert Bernstein, Anthony Chen, Younghyun Cho, Armando Fox, Hasan Genc, Amir Gholami, Adrian Castello Gimeno, Mason Haberle, Olga Holtz, Charles Hong, Coleman Hooper, Jenny Huang, Yuka Ikarashi, Josh Kang, Iniyaal Kannan, Tarun Kathuria, Kurt Keutzer, Mahmoud Abo Khamis, Seehoon Kim, Nayiri Krzysztofowicz, Sherry Li, Yang Liu, Hengrui Luo, Hung Ngo, Jonathan Ragan-Kelley, Alex Reinking, Miles Rusch, Satish Rao, Alex Rusciano, Sophia Shao, Harsha Simhadri, Dan Suciu, Luca Trevisan, and Nate Young. Originally, I had thought to divide this list into "collaborator" and "mentor" categories, but in truth I've learned so much from everyone I've worked with that my attempts to draw such a distinction would be arbitrary, and for this they have my deepest gratitude.

I've also had the privilege of having mentors from industry: Randy Huang and Hongbin Zheng at Amazon; Bill Athas and Bryan Raines at Apple; and Andrew Krioukov and Andy Konwinski, who organized an incredibly interesting class at Berkeley on entrepreneurship.

My friends: Amit, Eve, Logan, Paras, SJ, Tarun, Zoe, plus a sizable subset of people above whose names have already been mentioned, and the entire Bay Area paragliding community (especially Glenn, who picked me up after I crashed and drove me to my hotel just in time prepare my talk about Chapter 4). Thank you for keeping me sane all these years.

Last, but not least, I would like to thank my family - my partner, Mae Milano, and my parents, Hoa Dinh and My Nguyen, for their love and support (and for putting up with me during dissertation-writing stress!).

# Chapter 1

# Introduction

Tensor operations play a central role in many applications, such as machine learning, signal processing, and dense linear algebra. These tensor operations are increasing significantly in size. The number of parameters used in popular large language models, for instance, has ballooned from 1.5 billion (GPT-2, 2019) to 175 billion (GPT-3, 2020) to 530 billion (Megatron-Turing, 2021)<sup>1</sup>. Furthermore, there is increasing demand to run tensor operations efficiently on systems with significant energy and latency constraints, such as edge and Internet of Things (IoT) devices.

As a result, many high-performance software libraries have been developed to run tensor operations performantly and efficiently on CPUs and GPUs, which are ubiquitous and capable of handling a large variety of workloads. The design of these software libraries significantly impacts the performance that can be achieved.

This is even more the case for software targeting domain-specific accelerators, which sacrifice features such as branch predictors and automatically managed caches for performance. Such accelerators offload many scheduling decisions, such as movement of data between parts of the memory hierarchy, to the programmer; as a result, their performance is even more affected by the exact manner in which tensor problems are targeted, or mapped, onto them.

As a result, it is increasingly important for implementors of performance software to determine how to map an algorithm onto a given CPU, GPU, or accelerator. However, the space of possible mappings (mapspace) is challenging to search, as the number of choices that comprise a mapping leads to a combinatorial explosion in the number of possible mappings. Furthermore, this space is highly nonconvex and changes significantly with the target architecture; as a result, we wish to develop general techniques that can be quickly specialized to different target architectures.

This dissertation addresses this problem by developing both *lower bounds* on the cost of different mappings (under some abstract computational models), and *optimization methods* that often attain these lower bounds.

Chapter 2 introduces the necessary background for this work: a characterization of the

<sup>1</sup>https://huggingface.co/blog/large-language-models

general types of hardware we consider, as well as a formal definition of the decisions a programmer must make when implementing a performant kernel targeting a particular piece of hardware, which we refer to as the *mapping*. Mappings may be evaluated using several different performance models, ranging from abstract models of computation to detailed architectural simulations. Motivated by previous studies that show that *loop tiling* is the most consequential decision that a programmer must make when designing a mapping, we focus on an abstract communication model, and describe techniques from prior work that describe how to derive theoretical lower bounds for these models.

Unfortunately, these techniques are practically limited by two main shortcomings: first, they are computationally challenging to solve in the general case, and second, they provide bounds that are not tight for problems that are not asymptotically large in all dimensions. We address these challenges by focusing on special cases of particular practical interest: projective nested loops (which encompass most dense linear algebra operations, tensor contractions, and n-body pairwise interactions), which we cover in Chapter 3, and convolutions, which we cover in Chapter 4. In both cases, we develop efficiently computable lower bounds that apply to problems of all sizes - not just asymptotically large ones - and show how to attain them through an appropriate loop tiling. For convolutions, we show that our approach provides significant practical speedups on a real machine learning accelerator. We extend the techniques used to prove these lower bounds and find algorithms to models incorporating both communication and computation in Chapter 5.

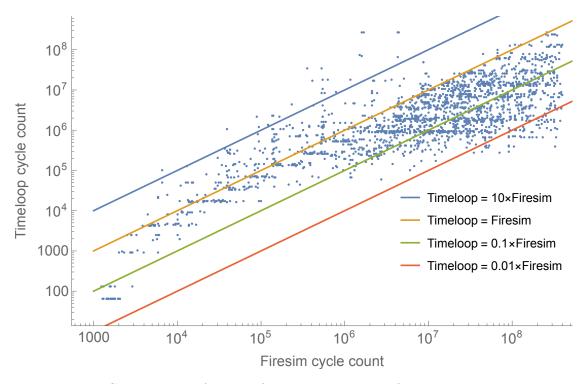

We then describe how these optimization approaches can be extended to performance models beyond the abstract communication model using Bayesian optimization in Chapter 6. While these models are sufficiently complex that proving lower bounds are not possible, we show that optimization techniques inspired by those we use to attain communication lower bounds provide good performance in practice on these more sophisticated lower bounds.

# Chapter 2

# Background

# 2.1 Architectures for Tensor Computations

We will begin with a brief overview of several architectures, focusing on their implications for the high-performance implementations of dense linear algebra and machine learning operations. For our purposes, the primary distinguishing features of an architecture will be the the manner (and amount) of parallelism it exposes, and the design of its memory hierarchy.

CPUs are equipped with several (usually three) levels of associative SRAM caches, usually set-associative, and expose parallelism to programmers in two forms: vector intrinsics and multithreading. Unfortunately, many CPU features add complexity and overhead unnecessary for dense tensor algebra; these include support for both branch prediction, multiple-instruction multiple-data (MIMD) parallelism, prefetching, and hardware-controlled caches. For example, a two-way set-associative cache uses  $2.5\times$  as much energy as a manually controlled scratchpad [33, §7.2]. Such overheads greatly limit the amount of parallelism that can be given for a given power and area budget. As a result, the use of CPUs for programs is generally limited to:

- applications (e.g. embedded systems) where cost or power constraints preclude the inclusion of additional processing units

- tasks where the cost of offloading data to an external chips may be expensive, or where the fixed costs outweigh the size-dependent cost. For example, linear algebra operations on small matrices may be individually cheap enough that the fixed overhead required to offload them onto an external chip would more than offset any potential performance gains. This may be alleviated by batching many small operations into a single, larger one, which can be efficiently offloaded onto a GPU; , but this is not always feasible (e.g. when the outputs of some operations are required as input for others).

- computations where data-dependent optimizations can be performed, such as taking advantage of sparsity, or performing approximations that "sparsify" inputs (e.g.

through the use of locality-sensitive hashing [8]). These optimizations are largely beyond the scope of this work.

GPUs operate on similar principles to CPUs, trading off low latency for significantly higher parallelism (and therefore throughput) and memory bandwidth. Of note, GPUs are typically equipped with their own independent memory (VRAM), and copying data to and from VRAM - an expensive task - is left for the programmer to manage manually. Some modern GPUs have tensor cores, which can perform relatively small ( $4 \times 4 \times 4$ ) tensor operations directly in hardware in the same manner as vector instructions do in CPUs. This, combined with built-in support for many lower precision types popular in machine learning, makes GPUs a common tool for machine learning and other tensor operations.

However, focusing specifically on simple tensor operations such as matrix multiplications and convolutions allows for even simpler architectures to be devised. Without the need for as much flexibility as a CPU or GPU, tensor accelerators eschew the complex mix of vectorization, multithreading, and out-of-order execution present in the aforementioned architectures for two-dimensional systolic arrays comprised of synchronously operating processing elements (PEs). Furthermore, dense tensor algebra's memory access and compute patterns are input-independent and can be determined statically from the problem size, allowing two key memory hierarchy optimizations. First, caches can be replaced with manually-controlled scratchpads, obviating the need for eviction and prefetching logic (and the corresponding area and power costs) and reducing the duplication inherent in an inclusive multi-level memory hierarchy. Furthermore, reduction operations, which are ubiquitous in tensor operations, can be sped up through the use of an accumulator buffer whose contents can be incremented and decremented by arbitrary values using one machine instruction. Together, these optimizations allow for significantly higher levels of throughput for a given power and area budget.

Producing optimized implementations of tensor kernels requires taking into account the target architecture, as well as hardware parameters such as the costs (in both latency and energy) for individual memory and compute operations, as well as memory bandwidth limits. Fortunately, as we will discuss in the following section, the process of *mapping* a tensor kernel onto a particular piece of hardware can be decomposed into several constituent *mapping decisions*, many of which can be analyzed - and therefore optimized over - analytically.

## 2.2 Mapping

As a simple motivating example, let us consider the problem of producing an optimized implementation for the classical three-nested-loop matrix multiplication on a simple simple vectorized CPU with a two-level memory hierarchy; we will generalize this to arbitrary nested loop programs and hardware targets in Section 2.2.1. We start with a simple three-nested loop implementation (Figure 1).

In order to run this matrix multiplication efficiently on a target architecture, we must emit a sequence of hardware instructions controlling not only arithmetic operations but

#### **Algorithm 1:** Classic three-nested loop matrix multiplication

```

1 for m \in [0, M):

2 | for k \in [0, K):

3 | for n \in [0, N):

4 | C(m, n) + = A(m, k) \times B(k, n)

```

also data movement - either implicitly (for caches with automatic evictions) or explicitly (on accelerators with explicitly managed scratchpad memory). We can think of these instructions as being generated by a series of transformations, or *rewrites*, performed on the nested loop, each of which is associated with a set of choices, the final goal of which is to generate a sequence of machine instructions.

For instance, we may wish to first tile the loops in order to increase memory reuse of elements stored on fast memory, reducing the amount of communication required between fast and slow memory, generating Algorithm 2.stop algorithms end of chapter latex memoir If the tile sizes  $T_{m,k,n}$  are not divisors of the problem sizes M, K, and N, we must manually handle the iterations at the end that do not perfectly fit into a tile, which we refer to as tail iterations or as a tail case. Algorithm 2 includes tail cases for n and k axes (we omit the tail case for the m axis for brevity). For the remainder of this section, we will assume for the sake of simplicity that  $T_{m,n,k}$  perfectly divide the loop bounds M, N, and K, allowing us to omit handling for tail iterations. Furthermore, note that the instruction to load subsets of A, B, and C into main memory may be expressed either implicitly, if our fast memory is a cache, or explicitly (which would require a paired eviction/flush instruction), if our fast memory is an explicitly managed scratchpad.

In order to further improve reuse and reduce communication, we may elect to reorder the loops. For instance, consider the current ordering of the outer three loops of Algorithm 2:  $m_{\text{out}}$ ,  $k_{\text{out}}$ ,  $n_{\text{out}}$ . As the outermost loops are  $m_{\text{out}}$  and  $k_{\text{out}}$ , the subset of A (which is indexed by m and k) loaded into fast memory stays fixed in fast memory for each iteration of the  $k_{\text{out}}$  loop, while the subsets of B and C change; we call this a A-stationary dataflow. If the costs of accessing A, B, and C are different - for instance, if C is stored in a higher precision to improve floating point accuracy - it may be beneficial to rearrange the loops to  $m_{\text{out}}$ ,  $n_{\text{out}}$ ,  $k_{\text{out}}$  to create a C-stationary dataflow.

Notice that reordering loops within the inner block, i.e. swapping the positions of  $m_{in}$ ,  $k_{in}$ , and  $n_{in}$  loops, will not change the amount of communication between fast and slow memory, as it only affects computations on tiles already resident in fast memory. However, changing the order of loops is essential for parallelizing the code.

Suppose, for instance, that our target machine supports a vector length 4, and we wish to vectorize our code using a fused-multiply add that performs  $\vec{a} += s \cdot \vec{b}$ , for length-4 vectors  $\vec{a}, \vec{b}$  and a scalar s (on Intel AVX, this is equivalent to loading in s with \_mm\_broadcast\_ss, loading  $\vec{b}$  with \_mm\_load\_ss, and performing the computation with \_mm\_fmadd\_ps).

If B and C are both stored in row-major format, then the simplest solution is to vectorize

Algorithm 2: Three-nested loop matrix multiplication after tiling

```

1 for m_{out} \in [0, |M/T_m|):

2

for k_{out} \in [0, |K/T_k|):

for n_{out} \in [0, \lfloor N/T_n \rfloor):

3

Load subsets of A, B, and C associated with the indices m, n, k spanned

4

by the following inner loops into fast memory

for m_{in} \in [0, T_m):

5

for k_{in} \in [0, T_k):

6

for n_{in} \in [0, T_n):

7

m = T_m m_{\text{out}} + m_{in}

8

k = T_k k_{\text{out}} + k_{in}

9

n = T_n n_{\text{out}} + n_{in}

10

C(m,n)+=A(m,k)\times B(k,n)

11

Load subsets of A, B, and C associated with the indices m, n, k spanned by

12

the following inner loops into fast memory

for m_{in} \in [0, T_m): // Tail iterations for n

13

for k_{in} \in [0, T_k):

14

for n \in [N/T_n] T_n, N:

15

m = T_m m_{\text{out}} + m_{in}

16

k = T_k k_{\text{out}} + k_{in}

17

C(m,n) += A(m,k) \times B(k,n)

18

for n_{out} \in [0, |N/T_n|): // Tail iterations for k

19

Load subsets of A, B, and C associated with the indices m, n, k spanned by

20

the following inner loops into fast memory

for m_{in} \in [0, T_m):

21

for k \in [\lfloor K/T_k | T_k, K):

22

for n_{in} \in [0, T_n):

23

m = T_m m_{\text{out}} + m_{in}

\mathbf{24}

n = T_n n_{\text{out}} + n_{in}

25

C(m,n)+=A(m,k)\times B(k,n)

26

Load subsets of A, B, and C associated with the indices m, n, k spanned by the

27

following inner loops into fast memory

for m_{in} \in [0, T_m): // Tail iterations for n

28

for k \in [\lfloor K/T_k \rfloor T_k, K):

29

for n \in [|N/T_n| T_n, N):

30

m = T_m m_{\text{out}} + m_{in}

31

C(m,n) += A(m,k) \times B(k,n)

32

```

among the n axis. On the other hand, if A and C are stored in column-major format, we would wish to move  $m_{in}$  to be our innermost loop before performing vectorization along the

m axis.

In the following pseudocode (Alg. 3), we denote the loop performed by the vector intrinsic using a spatial-for loop, so named as each its iterations are spatially mapped to physically separate elements of the CPU. This code transformation also induces a tail case in the above code, as the tile size  $T_n$  may not be a multiple of 4. The tail may be executed either as scalar code or a masked vector operation; the choice of which one to use depends on both the number of loop iterations contained in the tail and the target hardware.

Algorithm 3: Three-nested loop matrix multiplication after tiling, vectorization

```

1 for m_{out} \in [0, M/T_m):

for k_{out} \in [0, K/T_k):

\mathbf{2}

for n_{out} \in [0, N/T_n):

3

Load subsets of A, B, and C associated the indices m, n, k spanned by

4

the following inner loops into fast memory

for m_{in} \in [0, T_m):

\mathbf{5}

for k_{in} \in [0, T_k):

6

m = T_m m_{\text{out}} + m_{in}

7

k = T_k k_{\text{out}} + k_{in}

8

for n_{in} \in [0, |T_n/4|):

9

n_{reg} = T_n n_{\text{out}} + 4n_{in}

10

spatial for n \in [n_{reg}, n_{reg} + 3]: // Run as vector op

11

C(m,n)+=A(m,k)\times B(k,n)

12

for n \in [4 | T_n/4 |, T_n]: // tail case

13

C(m,n)+=A(m,k)\times B(k,n)

14

```

Each of the preceding steps is associated with different choices: the tile sizes  $T_{m,k,n}$ , the order of the loops, and the choice of which axes to parallelize. These choices must be made under constraints: for instance, the memory footprints of each inner tile may not exceed the size of fast memory, and we are only permitted to vectorize the innermost loop.

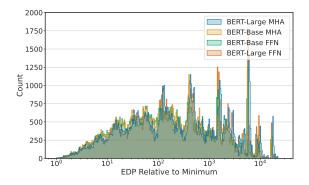

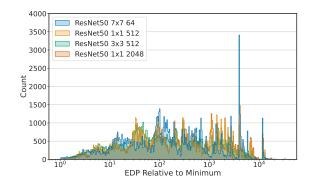

These choices can also significantly affect performance. In Fig. 2.2.1 we plot the energy-delay product (EDP) of 100K randomly chosen mappings for several matrix multiplications (top) and convolutions (bottom) the choices made in mappings can significantly affect performance. Only a small fraction of mappings achieves reasonable performance; the vast majority of mappings are over an order of magnitude more expensive to execute.

Figure 2.2.1: A histogram of energy-delay product (EDP - left is better) values for 100K randomly sampled valid mappings for BERT (matmul-dominated kernel, left) and Resnet50 (convolution, right), simulated on Timeloop [71]. Note that the x-axis is log-scale. Only a minuscule fraction of mappings, on the far left of each graph, provide acceptable performance for each processor.

The mapping problem applies to many tensor algorithms beyond simple matrix multiplies - many other tensor problems, such as convolutions, as seen in the figure, are similarly dependent on high-quality mappings for good performance. We can represent these programs as general *nested loop programs* operating on multidimensional arrays, as described in Algorithm 4. We will assume in this work that the operations may be performed in any

```

Algorithm 4: General nested loops

```

```

data: number of nested loops d \in \mathbb{Z}

loop bounds L_1, \ldots, L_d \in \mathbb{Z}

multidimensional arrays A_1, \ldots, A_n, with A_i being d_i-dimensional

linear data access functions \phi_i : \mathbb{Z}^d \to \mathbb{Z}^{d_i}, for i \in [n]

1 for x_1 \in [0, L_1), \ldots, x_d \in [0, L_d):

2 perform operations on A_1 [\phi_1(x_1, ..., x_d)], ..., A_n [\phi_n(x_1, ..., x_d)]

```

order (i.e. there are no dependencies between different loops, and we are not concerned about floating-point artifacts induced by changing the order of operations).

At each iteration  $x_1, \ldots, x_d$  of the the nested loops, the program accesses the arrays at addresses given by the *data access* functions  $\phi_1, \ldots, \phi_n(x_1, \ldots, x_d)$ , which fully specify the patterns the nested loop uses to access data. For instance, a classical matrix multiply (Algorithm 1) can be represented with the data access functions:

$$\phi_1(x_1, x_2, x_3) = (x_1, x_3)

\phi_2(x_1, x_2, x_3) = (x_1, x_2)

\phi_3(x_1, x_2, x_3) = (x_2, x_3)$$

Adjusting the data access functions  $\phi$  allows us to represent most dense linear algebra and tensor kernels (including convolution), as well as many stencil kernels (especially for image processing). We will now generalize the preceding mapping process from matrix multiplication to general nested loops, by describing each step of the mapping process in detail.

## 2.2.1 Mapping Steps

This section describes the steps involved in mapping a general nested loop onto an accelerator. Each of these steps is associated with a set of choices, such as loop tile sizes and loop orders, which are *constrained* by the target hardware in a manner we will discuss here.

#### 2.2.1.1 Tiling

Loop *tiling*, also referred to as *blocking* - that is, partitioning the loop nest into *tiles* which are executed in sequence - is a key optimization for increasing data reuse and reducing communication complexity of an operation. Note that we will use the term *tile* is to denote both the subsets of the loop nest, and subsets of the arrays used by each (loop nest) tile.

The most common form of tiling, which we refer to as rectangular tiling, breaks the iteration space into rectangular regions, as we did for matrix multiply earlier in Algorithm 2. More precisely, a rectangular tiling transforms a nested loop of the form given by Algorithm 4, given a set of tile sizes  $T_1, \ldots, T_n \in \mathbb{Z}$  (such that  $T_i \leq L_i$ ), into the loop nest shown in Algorithm 5.

#### **Algorithm 5:** Rectangular tiling of nested loop

```

1 for x_{O,1} \in [0, L_1/T_1), \ldots, x_{O,d} \in [0, L_d/T_d): // outer loop

2 Load subsets of A_{1,\ldots,n} required for following nested loops into fast memory

3 for x_{I,1} \in [0,T_1), \ldots, x_{I,d} \in [0,T_d): // inner loop

4 x_i = T_i x_{O,i} + x_{I,i} \quad \forall i \in [d]

5 if x_i > L_i for some i: // tail case handling

6 | break loop i

7 perform operations on A_1 \left[ \phi_1 \left( x_1, \ldots, x_d \right) \right], \ldots, A_n \left[ \phi_n \left( x_1, \ldots, x_d \right) \right]

8 Flush writes to slow memory

9 Evict subsets of A_{1,\ldots,n} not required for next tile

```

If  $T_i$  does not perfectly divide  $L_i$ , a tail case is generated, corresponding to the final few iterations along the  $x_i$  axis. These are represented in Algorithm 5 with an if statement on Line 5 for compactness, but in practice (as branching is expensive, and often infeasible on many accelerator architectures) they are more commonly split off into separate loops as in Algorithm 2.

The choice of the tile sizes  $T_i$  heavily affects the amount of data movement (and therefore the arithmetic intensity) of the resulting mapping, which often dominates the total time and energy cost of many tensor workloads. In fact, both prior work [90, 44] and our own

sensitivity analysis (discussed further in Section 6.2.5) has shown that loop tiling is by far the most important decision involved in constructing a mapping.

In order for a tiling to be executable on a system, the memory footprint of the inner loop - that is, the total size of the tensor tiles corresponding to the inner loop - must be at most the size of the fast memory. For instance, in Alg. 2, the memory footprint of a tile is  $T_nT_m + T_nT_k + T_kT_m$ , which must be bounded above by M. In the case of multiple buffers, with different tensors, each buffer must be able to accommodate the tiles for the tensors assigned to it. For instance, if we have a scratchpad of size  $M_S$  for the inputs and an accumulator of size  $M_A$  for the outputs, the constraints for the matrix multiply example become

$$T_n T_m \le M_A$$

$$T_n T_k + T_k T_m \le M_S$$

For architectures and systems with multilevel memory hierarchies, the inner loop may be recursively tiled to generate a *multilevel tiling*, where each level's memory footprint fits inside a level of the memory hierarchy.

Other architectural features and optimizations can also affect the constraints for a tiling. For instance, *double-buffering* divides the scratchpad into two halves, with one half being used by the processor for computation while the other is loaded with data from memory, interleaving communication and computation in order to minimize latency. This effectively doubles the memory footprint of tiles corresponding to tensors that are not kept *stationary* in fast memory between successive tiles (see next section for more on stationarity).

Furthermore, certain axes may not be tilable. For instance, convolution accelerators are often built with the assumption that the entire filter (being sufficiently small) will be loaded onto purpose-built registers, and therefore will not support tiling along axes corresponding to filter dimensions. For each of these axes, we constrain the tile size  $T_i$  to be equal to the loop bound  $L_i$ .

Rectangular tilings are the main form of tiling used in practice, both because of ease of implementation and because they offer good performance for many common problems. In fact, we will show in Chapter 3 that it rectangular tiles are optimal for the case where all  $\phi_i$  return subsets of their inputs (i.e. are *projections*). However, non-rectangular tiling schemes may be required to attain theoretical optima; we will describe one such case - strided convolutions - in Chapter 4. Loop nests with data dependencies between iterations may also benefit from *polyhedral transformations* [28, 5, 3], but are outside the scope of this work.

#### 2.2.1.2 Loop Permutation

In our matrix multiply example earlier, we permuted the order of the loops in order to change which matrix would remain stationary in fast memory between successive tiles. In general, the tensors indexed by axes spanned by outermost loops surrounding a tile (e.g.  $x_1, x_2, ...$  in Algorithm 5) will be held stationary between successive tiles. Depending on the

target hardware, different loop orderings can result in different costs (especially if different tensors are stored in separate buffers with varying costs), and some orderings may be entirely unsupported.

Consider, for instance, an accelerator that performs accumulation in 32-bit precision but then writes the output to main memory in 16-bit precision. Consider the tiled matrix multiplication loop nest in Algorithm 2. Notice, that this loop ordering requires us to write partial sums of C (which is indexed by m and n) to main memory between successive tiles, as the innermost loop surrounding the tile is  $n_{\text{out}}$ , meaning that two consecutive tiles would correspond to different columns of C. However, writing out partial sums to main memory would require us to first round the 32-bit values present in fast memory to a 16-bit value, leading to loss of precision and possible numerical instability. As a result, this accelerator demands an *output-stationary* dataflow that keeps partial sums of C on-chip between tiles, requiring that  $m_{\text{out}}$  and  $n_{\text{out}}$  be the outermost loops outside the tile. We therefore can only choose between two loop orderings for the outer loops:  $m_{\text{out}}$ ,  $n_{\text{out}}$ ,  $n_{\text{out}}$ ,  $m_{\text{out}}$

#### 2.2.1.3 Parallelization and Hardware Instruction Mapping

Our previous matrix multiply example obtained parallelism through one-dimensional vectorization: Algorithm 3 was obtained by first splitting the innermost loop into two loops, with the inner loop having four iterations (equal to the vector length on our target architecture), and replacing this inner loop with an equivalent vector instruction.

However, different architectures have dramatically diffrent forms of parallelism available to them, ranging from vectorization to systolic parallelism to CPU-style multithreading. A common abstraction that can be used to describe many of these forms is *spatio-temporal mapping*: each *for* loop will be mapped onto hardware *temporally*, with all its iterations being run in sequence (which we denote as a standard *for* loop), or *spatially*, with its iterations being mapped to separate physical resources on a chip (which we denote with the keyword *spatial-for*).

As a spatial-for loop maps each iteration to a separate processing element on the chip, the product of the sizes of loops mapped spatially must be bounded by the total amount of parallelism available on the chip. Beyond that, however, the interpretation of a spatial-for depends on both the axis and the target architecture. Along a non-reduction axis (e.g. m, n in our matrix multiply example), data required by separate iterations in a for loop may be either directly broadcasted to each processing element through dedicated wiring, as is done on the NVDLA [23] and ShiDianNao [21] accelerators, or be transferred systolically, as in TPU [42] and Gemmini [26]. Reduction axes, such as k, may be mapped to reduction trees, as in NVDLA and DianNao [10] or to systolic reductions as in TPU and Gemmini.

#### 2.2.1.4 Graph-Level Optimizations

Most tensor workloads, especially in machine learning, consist of large *graphs* of operations, not just single operations, and are somewhat robust to perturbation. This opens up several

avenues of optimization, which are beyond the scope of this work:

- Layer fusion or operator fusion combines multiple layers (e.g., a matmul followed by a normalization or activation layer) into a single tensor operation to be scheduled and run at once, sometimes through the use of dedicated on-chip hardware to compute activations on the output. This reduces interlayer communication, as the results of one layer can remain on the chip as input without being written to and later read from main memory, at the cost of intralayer communication. The performance gains from such optimizations can vary widely depending on the kernel being run and the amount of hardware available.

- Taking advantage of *sparsity* in the inputs can provide significant speedups. Such optimizations are heavily data-dependent (even more so when sparsity is introduced during runtime for instance, using locality-sensitive hashing to zero out dot products likely to be small [8]) and, as a result, cannot always be estimated a priori [44]. Sparsity-aware architectures and mappings are a topic of active research.

## 2.2.2 Representing, Evaluating, and Optimizing Mappings

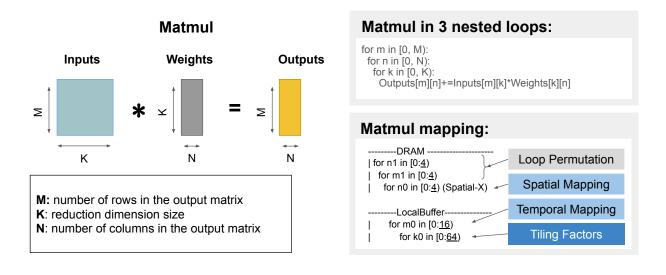

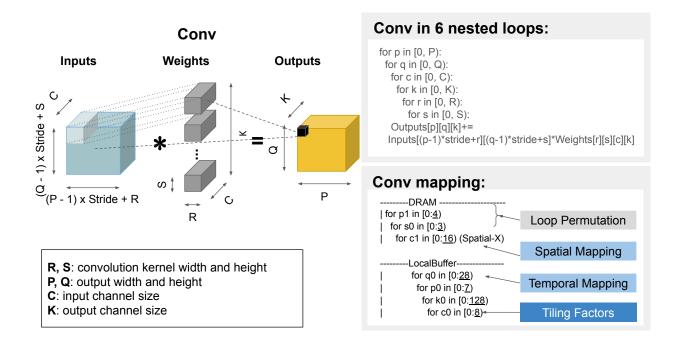

We refer to the set of choices - tile sizes, loop permutations, and tiling factors, e.g. as depicted in Figure 2.2.2 - introduced by the aforementioned rewrites as a *mapping*, and the set of all possible mappings as a *mapspace*. We will refer to each of the above choices as an *axis*.

As the computations involved in a dense tensor computation do not change with inputthere is no branching - finding a mapping can be done entirely at compile time. Furthermore, the simplicity and regularity of the program structure obviates the need for many forms of static analysis, such as dependency analysis. However, constructing mappings that result in good performance on accelerators is challenging. The significant number of choices involved in mappings leads to a combinatorial explosion in the number of possible mappings, giving rise to a mapspace with over  $10^{20}$  points [72]. As Figure 2.2.1 illustrates, only a small fraction of mappings generates good results.

The goal of a mapper or mapping algorithm is to search this large, high-dimensional space to find a mapping that satisfies all hardware constraints and minimizes some objective - usually some combination of energy or latency on a target hardware architecture. Mappers can be evaluated not only on the performance of the mappings they return, but also on their speed of execution, sample complexity, and generalizability to different hardware and software targets.

#### 2.2.2.1 Evaluating Mappings

In order to find a performant mapping, we must first define an objective function to optimize. If the target architecture exists and can be instrumented, actual measured performance usually latency, energy consumption, or a combined figure such as energy-delay product

Figure 2.2.2: Mapping representations for matrix multiplication and convolutions. Originally published in [50]

(EDP) - can be used. However, this is not often not desirable or even possible for a variety of reasons:

- Hardware availability may change rapidly. For instance, for a multi-tenancy setup, the amount of available memory for a given task may be affected by the number and size of other tasks currently running on the same machine.

- The hardware itself may not exist. For instance, design space exploration during the process of developing an accelerator requires performance evaluation of workloads (and therefore mappings) on target hardware that may be described only by a few parameters, with the full design unrealized.

- Simpler performance models (e.g. communication volume on an idealized memory model) allow us to develop *provable* bounds on performance that are infeasible to find for more complex models, and can be used to evaluate actual performance data (e.g. by comparing benchmark results to a roofline [87] model).

Different performance objectives offer different levels of fidelity, runtime cost, target workload scopes, compatibility for various mapping algorithms, and ability to prove theoretical results. We enumerate several here, in roughly increasing order of fidelity.

**Abstract computational models**, such as communication volume on a simple two-level memory hierarchy, are simple to define and can be easily adapted to a large variety of target hardware. They allow the development of theoretical *lower bounds* on performance, which we will cover in detail in the next section. However, their simplicity and generalizability comes at a cost - as they incorporate almost no assumptions on the target hardware, they can only serve as loose proxies for performance.

Adding architectural assumptions (e.g. on the structure of a memory hierarchy and parallelism available) and incorporating parameters such as memory bandwidth, systolic array size, and energy consumption per operation leads to more sophisticated **domain-specific analytical performance models** such as Timeloop and Maestro [71, 53, 57, 62, 38, 35]. These models leverage known iteration space bounds in tensor algebra workloads, as well as statically analyzable data access patterns, to estimate performance extremely quickly. Many of these models are expressed as closed-form mathematical expressions which can also be used directly as the objectives in optimization-based mappers, although their complexity generally precludes the derivation of theoretical lower bounds.

Another class of popular performance models are **data-driven ML models** [9, 32, 48]. Instead of building the performance model analytically to express known relations between mapping decisions and performance, these models use statistical techniques to iteratively fit a model to the mapping performance data collected over time, and often optimize over these models to produce performant mappings. They typically require large amounts of data and training time in order to learn and provide accurate predictions, but are fast to run once trained.

The major drawback of prior models is that the generated mappings might not perform optimally (or even well) on the actual accelerator since the models can fail to capture the implementation differences in the hardware accurately. **Cycle-exact software models** based on real hardware implementation can achieve higher fidelity [86, 77], as can **FPGA emulation** using platforms such as Firesim [46], which can be used to model hardware in development. However, these tools are several orders of magnitude more resource-intensive to run than analytical and trained ML models.

#### Turning Mappings into Code

Both cycle-accurate simulators and emulators and real hardware such platforms require more than a set of problem dimensions and a description of mappings - they require a stream of explicit instructions.

Generating this stream of instructions requires that one account for a large number of edge cases. For example, a simple tiling operation for a matmul - representable as a single line of tile sizes in a DNN accelerator modeling platform such as Timeloop [71] - requires both the insertion of instructions specifying memory movement between different levels of the memory hierarchy as well as the generation code for edge cases that appear when matrix dimensions are not evenly divisible by the tile size (as we did in Algorithm 2). Furthermore, many mapspace optimization methods rely on iterative search, which requires the evaluation of a large number of mappings; this in turn requires that mappings be translatable to code automatically.

As a result, code generation tools are used to actually implement mappings onto hardware (or simulators). Many of these tools integrate not only a specification of the target hardware but also mapping decision algorithms, often tuned for that hardware target. Because of this integration, evaluating the performance of mappings not generated by their internal framework and working on alternative hardware targets is challenging.

In order to address this problem, user-schedulable languages such as Halide [73], TVM [9], Rise/Elevate [30], and Exo [91] have been developed. These tools take as input a description of the computation to be performed and a point in the mapspace. They are generally defined by a set of rewrite rules on representing code transformations such as splitting and rearranging loops, replacing appropriate loops with ISA instructions, and fusing loops. These languages also allow the user to specify and customize the hardware instruction set and seamlessly convert mappings into executable code by representing them as a sequence of rewrite rules [64, 93].

#### 2.2.2.2 Searching For Mappings

Given a performance objective, a variety of methods exist to optimize it over the mapspace. We can cluster them into three general categories:

• Brute-force search methods [15, 71, 90] randomly sample and enumerate large number of points in the mapspace. However, the size of the mapspace and the rarity

of mappings that result in good performance require an extremely large number of points (typically thousands, if not tens of thousands) to be searched and evaluated to determine the mapping for a single kernel. As a result, these methods rely on fast analytical performance models and are generally unsuited for higher-fidelity simulated or emulated models.

- Feedback-driven methods address the sample inefficiency of brute-force search methods using use statistical or machine learning models. These approaches include black-box optimization techniques such as genetic algorithms [45, 43], reinforcement learning [89], and Bayesian optimization [76, 80], which aim to require fewer samples than brute-force methods. Alternatively gradient-based methods [32, 35] build differentiable surrogate functions that estimate performance based on input parameters. However, training gradient-based methods require millions of samples to build surrogate models, and the resulting surrogates cannot easily be used for hardware architectures not yet seen even after fine-tuning, and must be fully retrained from scratch at nontrivial expense [44].

- Heuristics perform one-shot analytic optimizations over a performance model (either defined explicitly to be used as an optimization target, or embedded implicitly in the heuristic). Such methods include polyhedral models [28, 51, 1]and constrained-optimization based approaches [38, 92]. Heuristics are efficient and generalize easily across hardware parameters and problem sizes, although often limited to optimizing certain axes of the mapspace (e.g. tilings, as we focus on in Chapters 2.3, 3, 4, or tilings and reorderings as in [68, 69], which build off our work). This makes them suited for guiding brute-force and feedback-driven methods, either by providing cheap, rapidly calculable features to them, or by eliminating several axes from the mapspace.

As a result, we will begin by examining heuristic tiling algorithms which can be used as building blocks to construct more general mappers, and corresponding lower bounds which can be proven in a simple abstract communication model.

# 2.3 Provably Optimal Tilings in the Two-Layer Memory Model

In order to develop tilings that are provably optimal, we must first specify a model of computation that allows us to derive lower bounds to prove optimality. As communication is the dominant cost in both time and energy for most accelerators, , and tiling largely affects communication, we use the two-level memory hierarchy model has a slow memory of infinite size connected to a processor with an onboard fast memory of size M; all inputs and outputs must be read from and written to fast memory. In this model, the cost is the amount of data transferred in both directions between slow and fast memory. We will largely measure this

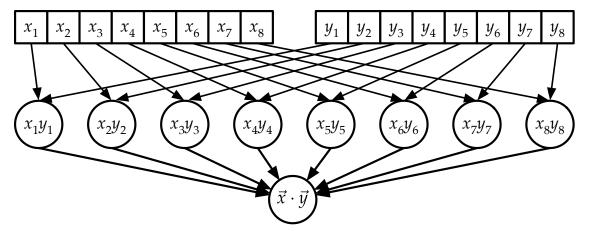

Figure 2.3.1: A CDAG for a dot product

in words, with one word corresponding to a single numeric value; however, problems with multiple datatypes (with different sizes), will require more detailed analysis.

Communication lower bounds derived for the two-level memory model can be used to describe a variety of computations, including multilevel memory hierarchies (by applying the model to bound communication on multiple levels) and distributed-memory systems.

Several methods have been proposed to bound communication in memory hierarchy models, for various models of computation. We establish the fundamentals of these methods in this chapter, and discuss how the derivation of communication lower bounds suggests ways to find tilings that attain them.

## 2.3.1 Computational DAGs and Pebble Games

A straight-line computation (i.e. one without branching) can be described as a computational directed acyclic graph (CDAG) (V, E) with vertices corresponding to computations and edges corresponding to data dependencies. Specifically, the computation represented by vertex v can only be executed after all computations represented by vertices  $u_i$  such that  $(u_i, v) \in E$  have completed. We refer to a schedule of execution of the program represented by a CDAG D as an ordered traversal  $(v_1, v_2, ..., v_n)$  of the vertices of the DAG that respects dependencies; specifically, all ancestors of  $v_i$  must occur before  $v_i$  in the schedule.

Pebble games were first proposed by Sethi [79] to bound the communication complexity of a CDAG in the context of register allocation. Given a CDAG G=(V,E), a player may, at each step, perform one of several operations with pebbles. In the original variant, sometimes referred to as the black pebble game, each pebble corresponds to a register, and the following operations are permitted:

• place a pebble on a source vertex of G (initialize a register)

- place a pebble on a vertex v, provided that all vertices u such that  $(u, v) \in E$  have pebbles on them (perform a computation whose inputs are all in registers, and write the output to another register)

- $\bullet$  remove a pebble from any vertex in G (free a register)

The game completes when all sink vertices of G have pebbles on them. From this formulation, it is clear if a CDAG can be black-pebbled with r pebbles, it can be executed on a machine with r registers.

In order to model communication for a memory hierarchy model, this game must be augmented with an operation corresponding to *communicating* a value between fast memory and slow memory. The resulting *red-blue pebble game*, proposed by Hong and Kung [36], involves two pebble colors: red, corresponding to fast memory, and blue, corresponding to slow memory. At the beginning of the program, all source nodes in G have blue pebbles on them, as the inputs to the program are presumed to initially reside in slow memory. Each turn involves one of the following operations:

- (L) place a red pebble on any vertex with a blue pebble on it (load a value from slow memory to fast memory)

- (S) place a blue pebble on any vertex with a red pebble on it (store a value from fast memory to slow memory)

- (C) place a red pebble on a vertex v, provide that all vertices u such that  $(u, v) \in E$  have red pebbles on them (perform a computation whose inputs are all in fast memory, and write the output to fast memory)

- (D) delete a pebble of any color from a vertex (remove a value from slow or fast memory)

The game concludes when all sink vertices of G have blue pebbles on them, indicating that the result has been computed and written to slow memory.

Given an instance of the red-blue pebble game, the maximum number of red pebbles on the graph at any time is the amount of fast memory required to execute the corresponding schedule, with the communication cost being the the number of (L) and (S) steps that occur. As a result, finding the communication cost of a CDAG in the two-level memory hierarchy model equivalent to determining the minimum number of (L) and (S) steps required to pebble the CDAG given M red pebbles.

Unfortunately, determining the *exact* minimum cost required to pebble an arbitrary CDAG is intractable. Determining the optimal pebbling scheme (and corresponding cost) for black-pebbling (register allocation) and "base" red-blue pebbling are both known to be PSPACE-complete [27, 17], and optimal pebbling for variants of red-blue pebble game that forbid or penalize recomputation have been shown to be NP-complete [70] in the general case.

However, pebbling bounds have been effectively derived, and tight pebbling based bounds have been efficiently derived for certain *classes* of computations.

The main approach is to *partition* the graph into subgraphs, each corresponding to a subset of computations.

**Theorem 1** (Th. 3.1 from [36]). Let an S-partition of a CDAG G = (V, E) be defined as a partition of V into disjoint subsets  $V_1, ..., V_h$  such that each subset  $V_i$  satisfies the following criteria

- $V_i$  must have a dominator set (a set of vertices such that each path from a source vertex of G to a vertex in  $V_i$  must contain at least one vertex in the dominator set) of size at most S. Intuitively,  $V_i$  must depend on at most S values.

- The minimum set (set of vertices in  $V_i$  with no children in  $V_i$ ) must be of size most S. Intuitively, the size of the output of  $V_i$  must be at most S

- Every path between two vertices in  $V_i$  consist entirely of vertices in  $V_i$ . Intuitively, this means the set of tasks represented by  $V_i$  can be executed as a single block, or equivalently, that there are no cyclic dependencies between different subsets.

Suppose there exists a schedule for a CDAG G that, on a machine with M words of fast memory, with communication cost q. Then there exists a 2M-partition of G into h subsets of vertices such that  $M(h-1) \leq q \leq Mh$ .

*Proof.* (from [52]) divide the schedule into h contiguous, consecutive segments  $S_1, ..., S_h$  each of which communicates exactly M words  $^1$  (i.e. uses exactly M (L) and (S) steps). We will use  $V_i$  to denote the set of values computed during segment i. By construction, there can be no cyclic dependencies between segments.

We define the following sets of vertices:

- $D_{R,i}$  is set of vertices whose values are already in fast memory at the beginning of  $S_i$ , i.e. each of its vertices have red pebbles at the start of  $S_i$ . Since fast memory may have no more than M words in it at the beginning of each segment, and in fact at any time,  $|D_{R,i}| \leq M$

- $D_{B,i}$  is the set of vertices whose values are loaded into fast memory during  $S_i$ , i.e. each of its vertices starts segment i with blue pebbles and gain red pebbles during  $S_i$ . By definition of segments,  $|D_{B,i}| \leq M$ .

- $W_{R,i}$  is the set of vertices whose values remain in fast memory at the end of  $S_i$ , i.e. each of its vertices have red pebbles at the end of  $S_i$ . By the constraint on the size of fast memory (as with  $D_{R,i}$ ),  $|W_{R,i}| \leq M$

<sup>&</sup>lt;sup>1</sup>The last segment may communicate less than M words, since we are not guaranteed that the total communication is divisible by M. For simplicity, we will assume the last segment communicates exactly M words of.

•  $W_{B,i}$  is the set of vertices whose values are written to slow memory during  $S_i$ , i.e. each of its vertices have blue pebbles placed on them during  $S_i$ . By definition of segments,  $|W_{B,i}| \leq M$ .

Notice that  $D_{R,i} \cup D_{B,i}$  consist of all inputs to  $V_i$  and therefore forms a dominator set of  $V_i$ , and its size is at most  $|D_{R,i}| + |D_{B,i}| \le 2M$ .

Furthermore, if a vertex  $v \in V_i$  has no children in  $V_i$ , its value must either remain in fast memory and the end of  $S_i$  (to be used by a later segment), giving  $v \in W_{R,i}$ ; or be written to slow memory during  $S_i$  (either to be read in and used by a later segment, or as part of the final output of the program), giving  $v \in W_{B,i}$ . Otherwise v would not be performing any useful work and could be deleted without changing the computation. As a result,  $W_{R,i} \cup W_{B,i}$  must contain the minimum set of  $V_i$ , giving an upper bound of  $|W_{R,i}| + |W_{B,i}| \leq 2M$  on the size of the minimum set.

As a result,  $V_1, ..., V_h$  is a 2M-partition. As each segment communicates exactly M words, and there are h segments, the total communication q is Mh.

We note that the key step of the proof is to divide the schedule into h segments, each of which communicates exactly M words. Determining the minimum number of segments required in such a construction will be key to our approach in the next section.

## 2.3.2 The Segment-Based Approach

Many straight-line computations of interest, including dense linear algebra, n-body problems, convolutions, can be expressed as a collection of *nested loops*, where each iteration accesses elements from several multidimensional arrays, indexed by some affine functions  $\phi : \mathbb{Z}^d \to \mathbb{Z}^{d_n}$  (for some  $d_n \leq d$ ) of the current loop iteration function:

for

$$x_1 \in [L_1]$$

, ..., for  $x_d \in [L_d]$ :

perform operations on  $A_1 [\phi_1 (x_1, ..., x_d)]$ , ...,  $A_n [\phi_n (x_1, ..., x_d)]$ . (2.3.1)

Let us assume that there are no dependencies between loop nests (i.e. any schedule is valid) and that we forbid recomputation. For operations such as matrix multiplication, tensor contraction, and convolution, these tend to be reasonably good assumptions - the accumulation is an associative and commutative operation, and there is no reason to perform recomputations since there is no reuse in the outputs.

For such problems, we apply the segmenting approach from the preceding section as follows; given an arbitrary schedule, divide the schedule into h segments  $S_1, ..., S_h$ , each corresponding to exactly M words of communication. Our goal will be to establish a lower bound on h. We do so by establishing an *upper* bound U on the number of loop iterations

$<sup>^{2}</sup>$ Again, for simplicity, we assume the last segment uses exactly M words of communication, although it may be lower.

that can be performed in each segment. As the total number of operations is  $\prod_{i \in [d]} L_i$ , it follows that

$h \ge \frac{\prod_{i \in [d]} L_i}{II} .$

Notice that any computation performed in segment  $S_i$  may use (by reading from, or writing to) at most 2M words of data: the M words already present in fast memory at the beginning of the computation, and M words that may be read or written during the execution of the segment. As a result, the total communication cost must be at least

$$q \ge 2Mh = 2M \frac{\prod_{i \in [d]} L_i}{U}$$

(2.3.2)

The crux of finding such lower bounds, as a result, is determining the upper bound U, the number of loop iterations that may be performed with access to at most 2M words of memory. Irony, Toledo, and Tiskin [39, 84] apply a geometric approach to this problem to develop such a bound for the classical three-nested loop matrix multiplication problem:

for

$$x_1 \in [L_1], x_2 \in [L_2], x_3 \in [L_3]$$

:

$$A_3[x_1, x_2] + = A_1[x_1, x_3] A_2[x_3, x_2]$$

(2.3.3)

In the above notation, the data access functions are:

$$\phi_1(x_1, x_2, x_3) = (x_1, x_3)$$

$$\phi_2(x_1, x_2, x_3) = (x_3, x_2)$$

$$\phi_3(x_1, x_2, x_3) = (x_1, x_2)$$

.

Each iteration  $\vec{x} = (x_1, x_2, x_3)$  may be represented as an point in a parallelepiped in  $\mathbb{Z}^3$ , and the array addresses required to execute that iteration are given by its projections  $\phi_1$ ,  $\phi_2$ , and  $\phi_3$ . It follows that the array addresses required for a segment  $S \subseteq [L_1] \times [L_2] \times [L_3] \subseteq \mathbb{Z}^3$  - which can be thought of as a set of iteration points - are projections of S, specifically  $\{[\phi_i(\vec{x})] : \vec{x} \in S\}$  for  $i \in [3]$ ; we will denote these  $\phi_i(S)$  for convenience. Therefore, the amount of data required to execute  $S_i$  is  $|\phi_1(S_i)| + |\phi_2(S_i)| + |\phi_3(S_i)|$ , which (by definition) must be bounded above by 2M; this constraint can be relaxed to  $|\phi_i(S)| \leq 2M$ .

As a result, the problem may be reduced geometrically to determining an upper bound on the size of a set  $S \subseteq \mathbb{Z}^3$  subject to constraints on the sizes of its projections  $\phi_i$ . This is immediately given by a classic inequality of Loomis and Whitney:

**Theorem 2** ((Discrete Loomis-Whitney inequality, Theorem 2 from [56])). Let S be a set of points in  $\mathbb{Z}^d$ , and  $\phi_i(S)$  be the set of projections of S onto the d-1-dimensional hyperplane formed by fixing the ith coordinate. Then

$$|S|^{d-1} \le \prod_{i} |\phi_i(s)| .$$

It immediately follows from Theorem 2 that the size of the matrix multiply segment is bounded above by  $|S|^2 \leq (2M)^3$ ; plugging into (2.3.2) gives a communication lower bound of

$$q_{\text{matmul}} = \frac{2ML_1L_2L_3}{(2M)^{3/2}} = \frac{L_1L_2L_3}{\sqrt{2M}}$$

(2.3.4)

It is also instructive to attempt to attain this lower bound. Let us assume as a ansatz that the rectangular tiling of Algorithm 2 is appropriate for this problem. Our goal will be to find the largest possible (in terms of number of operations) tiles whose memory footprint can fit inside fast memory. This results in the optimization program:

$$\max T_1 T_2 T_3$$

s.t.  $T_1 T_2 + T_2 T_3 + T_1 T_3 \le M$

This optimization program may be directly solved using signomial optimization techniques [65]. However, simpler methods suffice to prove the (asymptotic) optimality of this lower bound. Let us relax the memory footprint constraints as we did above during the proof of the lower bound:

$$\max T_1 T_2 T_3$$

s.t.  $T_1 T_2 \leq M$

$$T_2 T_3 \leq M$$

$$T_1 T_3 \leq M$$

This relaxation changes the constraints by at most a factor of 3, which we will ignore as we are operating asymptotically (we will deal with constant factors more precisely in Chapter 4). Taking logs base M, and letting  $\lambda_i = \log_M T_i$ , we have:

$$\max \lambda_1 + \lambda_2 + \lambda_3$$

s.t.  $\lambda_1 + \lambda_2 \le 1$

$$\lambda_2 + \lambda_3 \le 1$$

$$\lambda_1 + \lambda_3 \le 1$$

The solution to this linear program is  $\lambda_1 = \lambda_2 = \lambda_3 = 1/2$ , which suggests a tile size of  $\sqrt{M} \times \sqrt{M} \times \sqrt{M}$ , which implies that each tile consists of  $M^{3/2}$  operations with a memory footprint of (ignoring constant factors) M. As a result, the number of tiles is  $L_1L_2L_3/M^{3/2}$ , leading to asymptotic communication cost of  $L_1L_2L_3/\sqrt{M}$ , which matches the lower bound (2.3.4).

We note that the preceding derivation gives no guarantee that a tile of size  $\sqrt{M} \times \sqrt{M} \times \sqrt{M}$  will fit in the bounds of the problem. For example, if  $L_3 = 1$  (i.e. a matrix-vector multiply), almost every such tiling would be larger than the problem itself. We address this issue in Chapter 3.

## 2.3.3 The Discrete Brascamp-Lieb Inequalities

In order to develop lower bounds and optimal tilings beyond matrix multiplication, we must generalize beyond the Loomis-Whitney inequality (Th. 2). Our main tool will be the *discrete Brascamp-Lieb inequalities* (often abbreviated as "BL" or "HBL", with the H being a reference to Hölder) first introduced in [14].

**Definition 3.** Given a finitely generated group G, let rank(G) denote the size of the smallest generating set of G.

**Theorem 4** (discrete Brascamp-Lieb inequality). Let G and  $G_j$  (for  $j \in [n]$ ) be finitely generated Abelian group, and G be torsion-free. Let  $\phi_j : G \to G_j$  be group homomorphisms. If the rank inequalities

$$rank(H) \le \sum_{j \in [n]} s_j rank(\phi_j(H)) \quad \forall \ subgroups \ H \le G$$

(2.3.5)

hold for some nonnegative numbers  $s_i$ , then so does the following functional inequality:

$$\sum_{x \in G} \prod_{j \in [n]} f_j(\phi_j(x)) \le \prod_{j \in [n]} \|f_j\|_{1/s_j}$$

(2.3.6)

for all nonnegative functions  $f_i$  with a defined  $\ell^{1/s_j}$  norm over  $G_i$ .

We can apply this theorem to generate a Loomis-Whitney style cardinality inequality as follows: let  $S \subseteq \mathbb{Z}^d$  be a segment. Let  $f_j : \mathbb{Z}^{d_j} \to \mathbb{Z}$  be defined to be the following indicator function:

$$f_j(x) = \begin{cases} 1 & x \in \phi_j(S) \\ 0 & \text{otherwise} \end{cases}.$$

It immediately follows from the definition of  $f_i$  that

$$||f_j||_{1/s_i} = |\phi_j(S)|^{s_j}.$$

(2.3.7)

Furthermore, notice that if  $x \in S$ , then  $\phi_j(x) \in \phi_j(S)$  for all j, which implies  $\prod_{j \in [m]} f_j(\phi_j(x)) = 1$ . As a result, the cardinality of S is bounded by the left hand side of 2.3.6:

$$|S| \leq \sum_{x \in \mathbb{Z}^d} \prod_{j \in [n]} f_j(\phi_j(x))$$

$$\leq \prod_{j \in [n]} ||f_j||_{1/s_j} \qquad \text{applying (2.3.6)}$$

$$= \prod_{j \in [n]} |\phi_j(S)|^{s_j} \qquad \text{applying (2.3.7)}$$

which gives us the following generalization of the Loomis-Whitney inequality

Corollary 5. Let  $\phi_j : \mathbb{Z}^d \to \mathbb{Z}^{d_j}$  be linear functions, and S be a subset of  $\mathbb{Z}^d$ . Then for all  $s_j \geq 0$  satisfying

$$rank(H) \le \sum_{j \in [n]} s_j rank(\phi_j(H)) \quad \forall \ subgroups \ H \le \mathbb{Z}^d$$

(2.3.8)

it follows that

$$|S| \le \prod_{j \in [n]} |\phi_j(S)|^{s_j}$$

(2.3.9)

One can immediately apply the same argument from 2.3.2 to derive the following communication lower bound:

**Theorem 6.** Let  $\phi_j : \mathbb{Z}^d \to \mathbb{Z}^{d_j}$  be linear functions, and suppose we have the following loop nest:

for

$$x_1 \in [L_1], ..., for \ x_d \in [L_d]:$$

perform operations on  $A_1 [\phi_1 (x_1, ..., x_d)], ..., A_n [\phi_n (x_1, ..., x_d)]$ . (2.3.10)

The communication q required to execute this loop nest in the two-level memory hierarchy model with fast memory size M is bounded below by

$$q \ge \Omega\left(\frac{\prod_{i \in [d]} L_i}{M^{\sum_{j \in [n]} s_j - 1}}\right)$$

for  $any s_i$  satisfying

$$rank(H) \le \sum_{j \in [n]} s_j rank(\phi_j(H)) \quad \forall \ subgroups \ H \le \mathbb{Z}^d \ .$$

(2.3.11)

In order to find the strongest lower bound (which is also the only one possibly attainable by a tiling), we must minimize  $\sum_{j \in [m]} s_j$  subject to the linear rank constraints (2.3.11) (which form a polytope that we will refer to as the discrete Brascamp-Lieb polytope); this is a simple linear programming problem, provided we can enumerate the rank constraints.

Simple enumeration of the subgroups H does not suffice to determine the rank constraints, as there are infinitely many possible subgroups H of  $\mathbb{Z}^d$ . Note that the number of possible rank constraints is bounded - in particular, there are only d possible values for rank(H), and only  $d_j$  possible values for each of the rank $(\phi_j(H))$ , so any valid rank constraint would be of the form

$$a \le \sum_{j \in [m]} s_j a_j$$

for  $a \leq d$ ,  $a_j \leq d_j$ . Therefore, the most straightforward method to enumerate all the constraints of the Brascamp-Lieb polyhedron would be to enumerate all such possible  $a, a_j$  and pass them to the following decision problem:

**Problem 7.** Given positive integers  $a \leq d$ ,  $a_j \leq d_j$ , does there exist some subgroup  $H \leq \mathbb{Z}^d$  such that  $\operatorname{rank}(H) = a$  and  $\operatorname{rank}(\phi_j(H)) = d_j$  for all j?

Unfortunately, [14] showed that deciding Problem 7 would also decide Hilbert's tenth problem in the rationals: that is, deciding whether a finite set of multivariate polynomials with rational coefficients has a common rational root. The decidability of Hilbert's tenth problem in the rationals has been unknown for many decades, although the equivalent problem for the integers is well known to be undecidable [60].

Note that this does *not* preclude a complete description of the BL polytope. In particular, solving Problem 7 requires checking the validity of *every* possible rank inequality, including those implied - and therefore made redundant - by other valid rank inequalities. It is in fact possible to enumerate a set of constraints that completely defines the BL polytope - i.e. one that implies all the rank inequalities - through an algorithm given in [13]. Unfortunately, this algorithm has no bounds on runtime (other than a guarantee that it terminates), and as a result we are forced to rely on alternative means to do this.

The following theorem, a straightforward extension of the main result of [85] to to our discrete setting, can simplify the process of enumerating the constraints forming the Brascamp-Lieb polytope.

**Definition 8.** Let  $\{H_i\} := \{H_1, \ldots, H_k\}$  be groups. The *lattice* of  $\{H_i\}$ , denoted  $\mathcal{L}_{\{H_i\}}$ , is defined as the smallest set of subspaces containing  $\{H_i\}$  closed under intersection and direct sum: that is, if  $V_1, V_2 \in \mathcal{L}_{\{H_i\}}$ , then so are  $V_1 \cap V_2$  and  $V_1 + V_2 = \{v_1 + v_2 : v_1 \in V_1, v_2 \in V_2\}$ .

In this lattice, the intersection serves as the meet operation, while the sum serves as the join.

**Theorem 9.** Theorems 4 and 6 and Corollary 5 still hold if they are rewritten so the rank conditions (2.3.5), (2.3.8), and (2.3.11) are required only to apply for  $H \in \mathcal{L}_{\{\ker(\phi_i):i\in[n]\}}$ .

*Proof.* Let  $\Phi_j: \mathbb{Q}^d \to \mathbb{Q}^{d_j}$  extend  $\phi_j$  to a  $\mathbb{Q}$ -linear map. In Section 2.2 of [13], it is proved that the polytope of  $(s_j)$  satisfying the rank conditions (2.3.5), (2.3.8), and (2.3.11) is exactly equal to the polytope of  $(s_j)$  satisfying, for each subspace  $V \leq \mathbb{Q}^d$ ,

$$\dim V \le \sum_{j=1}^{m} s_j \dim \phi_j(V).$$

In [85], Theorem 8 states that it suffices to check only these inequalities from subspaces in  $\mathcal{L}_{\{\ker \Phi_j\}}$ . To check these, it suffices to check the original rank conditions (2.3.5), (2.3.8), and (2.3.11) on the subgroups in  $\mathcal{L}_{\{\ker \phi_j\}}$  and then to take  $\mathbb{Q}$ -linear spans of these subgroups. This completes the proof.

We will use Theorem 9 to find lower bounds for convolutions in Chapter (4).

Furthermore, we can also examine subsets of the discrete Brascamp-Lieb polytope, which lead to (potentially weaker, but guaranteed correct) lower bounds. One such subset is given by the real counterpart to Theorem 4.

**Theorem 10** (Real Brascamp-Lieb inequality, from [4]). Let  $B_j : \mathbb{R}^d \to \mathbb{R}^{d_j}$  be linear functions for  $j \in [n]$ , and  $s_j$  be nonnegative reals<sup>3</sup>. If the **rank constraints**

$$\dim(V) \le \sum_{j} s_j \dim(B_j V) \qquad \forall subspaces \ V \le \mathbb{R}^d$$

(2.3.12)

and the scaling constraint

$$d = \sum_{j} s_j d_j \tag{2.3.13}$$

hold as well, then there exists a nonnegative, finite constant C

$$\int_{x \in \mathbb{R}^d} \prod_{j \in [n]} \left( f_j(B_j x) \right)^{s_j} dx \le C \prod_{j \in [n]} \left( \int_{x_j \in \mathbb{R}^{d_j}} f_j(x_j) dx_j \right)^{s_j}$$

for all nonnegative functions f.

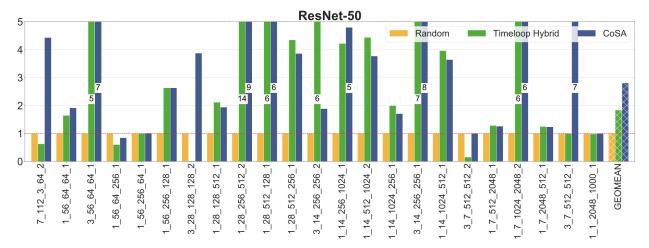

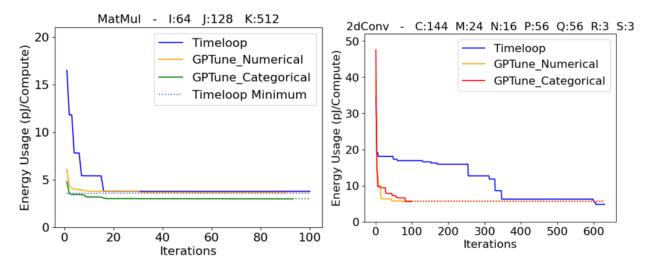

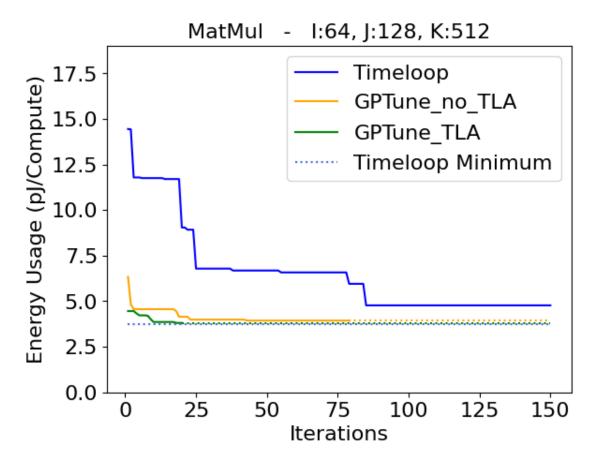

This inequality is very similar to the discrete Brascamp-Lieb inequality, with the exception of the value C, which is referred to as the *capacity* of the inequality. In the discrete formulation, C is always 1 when the inequality is valid; the same does not hold in the real case.