# An Integrated Circuit Design Framework for Human, Computer, and ML Designers

Dan Fritchman

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-275 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-275.html

December 15, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

by

#### Dan Fritchman

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering — Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vladimir Stojanović, Chair Professor Kris Pister Professor Alper Atamturk

Fall 2023

# An Integrated Circuit Design Framework for Human, Computer, and ML Designers

Copyright 2023 by Dan Fritchman

#### Abstract

An Integrated Circuit Design Framework for Human, Computer, and ML Designers

by

#### Dan Fritchman

Doctor of Philosophy in Engineering — Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vladimir Stojanović, Chair

Analog and custom circuits have long been a bottleneck to the integrated circuit design process. Automation generation of such circuits has long been a topic of research, but has failed to break through to popular practice. This work introduces a modular framework including a cloud-native IC design database, an analog circuit programming framework, a web-native schematic system, and tools for directed programming and automatic compilation of semi-custom IC layout. Highlighted applications include wireline transceivers and data converters, including a recent prototype ADC targeted for neural sensing applications, and research infrastructure for distributed, machine learning based circuit optimization.

# Contents

| Co | onten                                                | nts                                      | i                                |

|----|------------------------------------------------------|------------------------------------------|----------------------------------|

| Li | st of                                                | Figures                                  | iii                              |

| Li | st of                                                | Tables                                   | v                                |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4                     | The IC Design Process                    | 1<br>3<br>5<br>6<br>8            |

| 2  | IC I<br>2.1<br>2.2<br>2.3<br>2.4                     | Design Databases  "Databases" (Ahem) 101 | 9<br>10<br>12<br>12              |

| 3  | Ana 3.1 3.2 3.3                                      | A (Somewhat) Brief Intro to Hdl21        | 20<br>20<br>49<br>52             |

| 4  | Web<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | OK, not all of those schematics are bad  | 57<br>59<br>60<br>61<br>65<br>70 |

| 5  | Pro                                                  | gramming Models for IC Layout            | <b>7</b> 9                       |

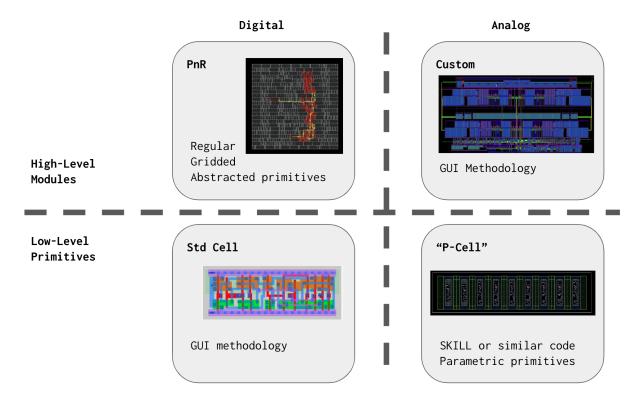

|    | 5.1  | The Digital Way                                           | 80  |

|----|------|-----------------------------------------------------------|-----|

|    | 5.2  | The Analog Way                                            | 80  |

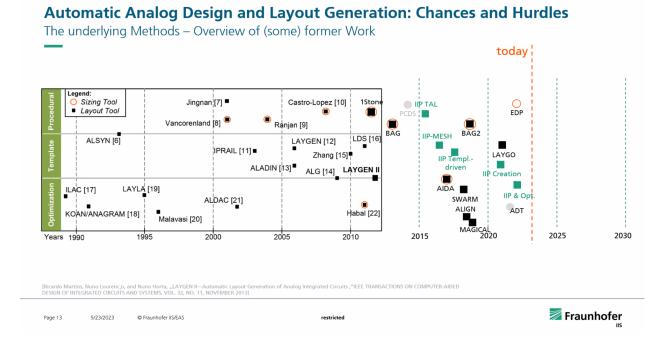

|    | 5.3  | The Two Most Tried (and Mostly Failed) Models             | 82  |

| 6  | Pro  | ogrammed Custom Layout                                    | 84  |

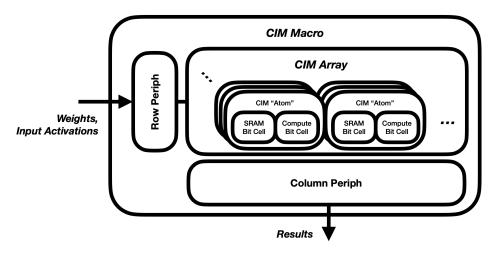

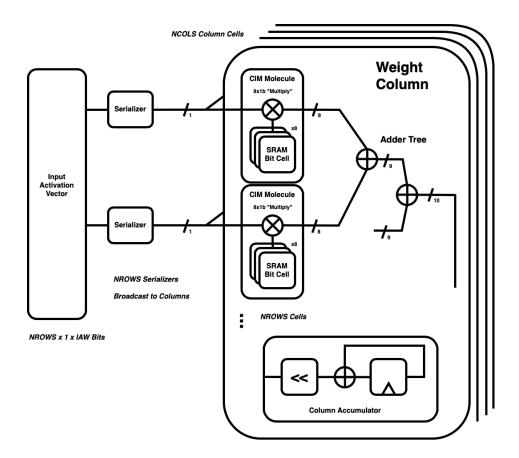

|    | 6.1  | Programmed Custom Success Stories (Mostly SRAM Compilers) | 86  |

|    | 6.2  | Layout21's Layered Design                                 | 89  |

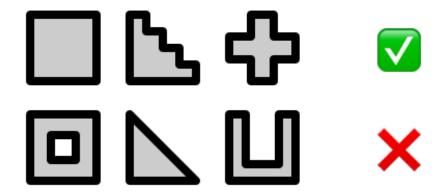

|    | 6.3  | Tetris Layer                                              | 95  |

| 7  | Cor  | mpiled (Analog) Layout                                    | 103 |

|    | 7.1  | Why does PnR work for digital, but fail for analog?       | 103 |

|    | 7.2  | Ramifications for Analog PnR                              | 105 |

|    | 7.3  | Semi-Related: PnR of Digital Logic "Standard Cells"       | 106 |

|    | 7.4  | ALIGN                                                     | 107 |

|    | 7.5  | AlignHdl21                                                | 109 |

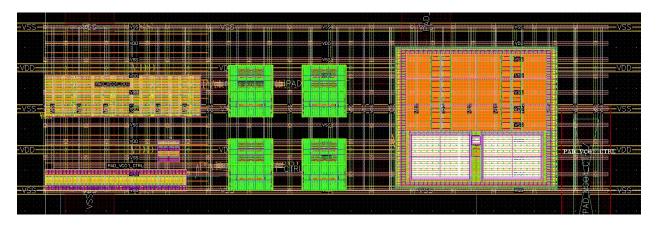

| 8  | Apj  | plications                                                | 121 |

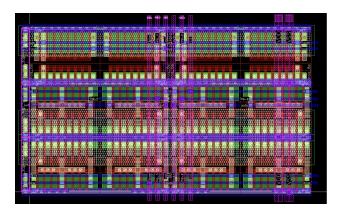

|    | 8.1  | Neural Sensor ADC in Intel 16nm FinFET                    | 121 |

|    | 8.2  | Machine Learners Learning Circuits 101                    | 127 |

| 9  | Fut  | ure Work                                                  | 135 |

|    | 9.1  | ML Designers                                              | 138 |

| Bi | blio | graphy                                                    | 144 |

# List of Figures

| 1.1<br>1.2<br>1.3                                    | Fisher and Pry's S-Curve of Technological Change [12]                                               | 1<br>2<br>4<br>5                             |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2.1<br>2.2                                           | RDBMS Low Layers                                                                                    | 9                                            |

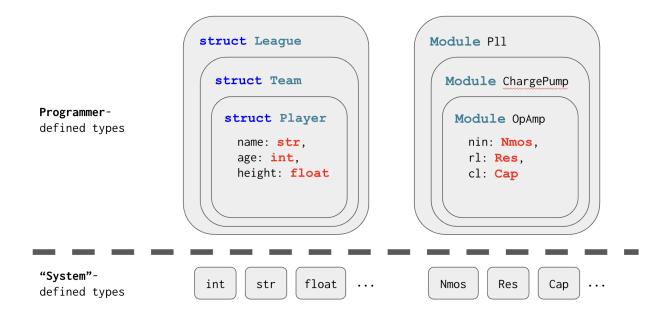

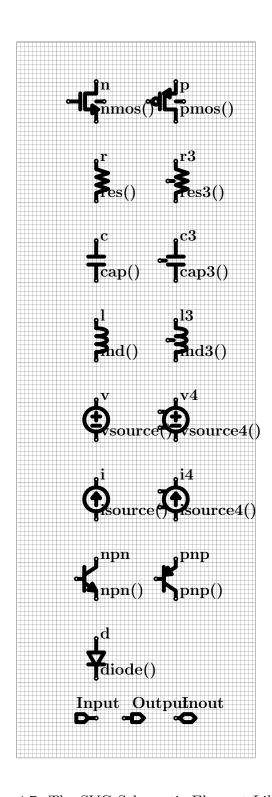

| 3.1                                                  | Primitives in a Typical Programming Language, and in Hdl21                                          | 38                                           |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8 | Test 3                                                                                              | 58<br>59<br>62<br>63<br>64<br>65<br>66<br>68 |

| 5.1<br>5.2<br>5.3                                    | Relationship Between Custom and Programmed Layout Generation in the Digital and Analog Design Flows | 79<br>81<br>82                               |

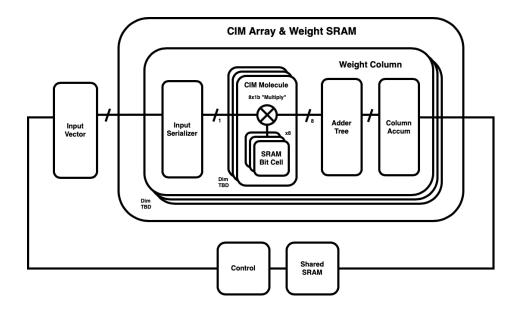

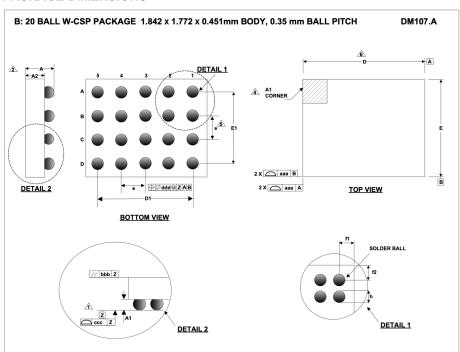

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6               | Compute in Memory Atom/ Bit-Cell from [13]                                                          | 87<br>87<br>88<br>89<br>92<br>96             |

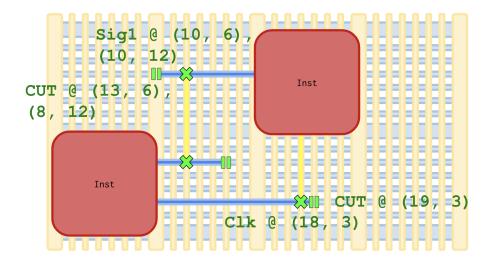

| 6.7<br>6.8                                           | <u>.</u>                                                                                            | 96<br>98                                     |

| 6.9  | MOS Stack Design in Standard Logic Cell Style                                     | 101 |

|------|-----------------------------------------------------------------------------------|-----|

| 6.10 |                                                                                   |     |

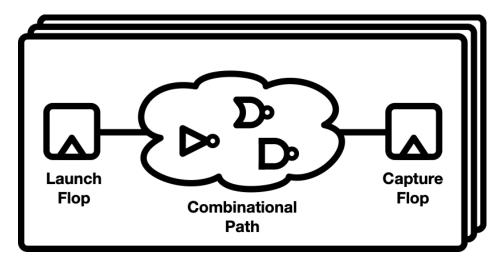

| 7.1  | Conceptual view of how the static timing closure problem sees synchronous digital |     |

|      | circuits                                                                          | 104 |

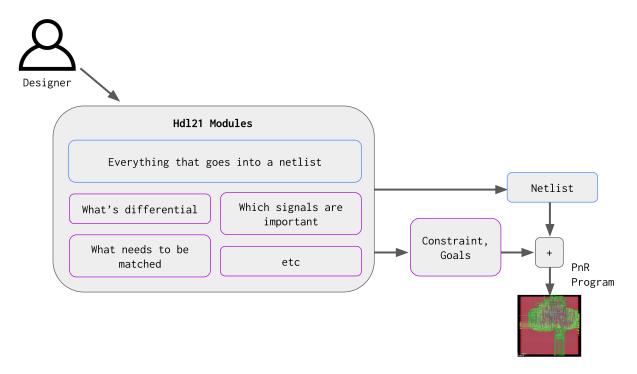

| 7.2  | Hdl21 to Analog PnR Flow                                                          | 109 |

| 7.3  | Example StrongArm Comparator Layout, Compiled from Hdl21 and ALIGN                | 111 |

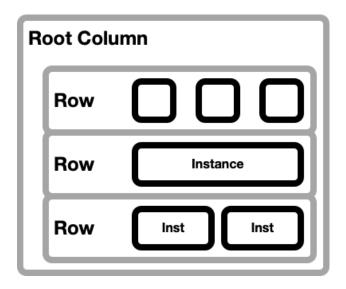

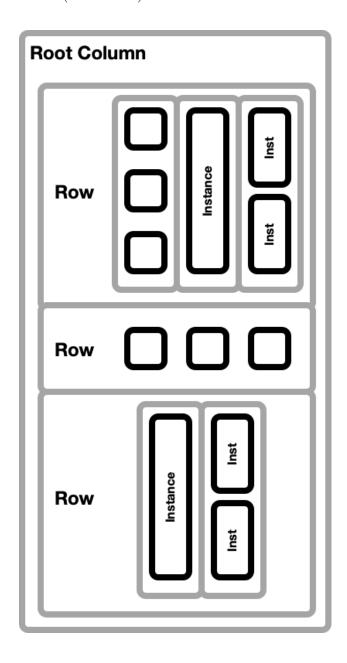

| 7.4  | Example Placement                                                                 | 112 |

| 7.5  | Example Placement                                                                 | 113 |

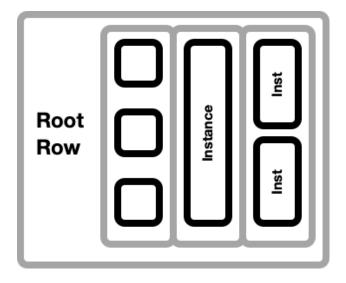

| 7.6  | Example Placement With Nesting                                                    | 114 |

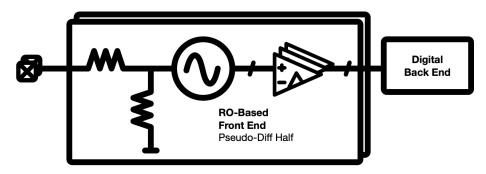

| 8.1  | RO-Based ADC Block Diagram                                                        | 122 |

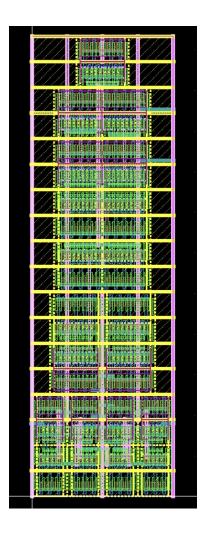

| 8.2  | Test Chip Layout                                                                  | 122 |

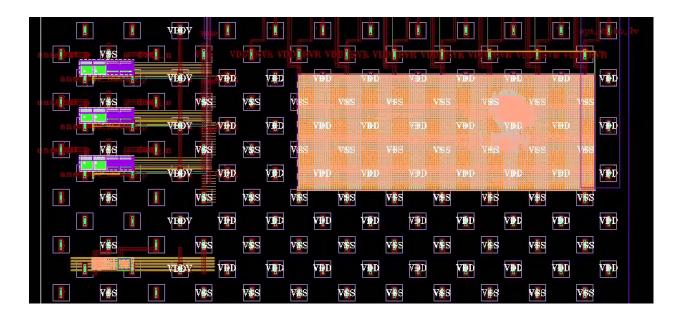

| 8.3  | VCO Layout                                                                        | 123 |

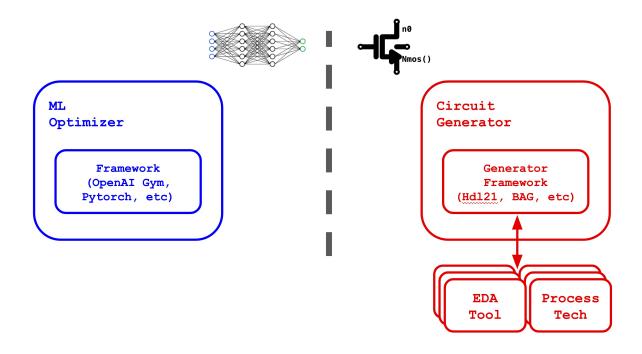

| 8.4  | ML and Circuit Research Silos                                                     | 128 |

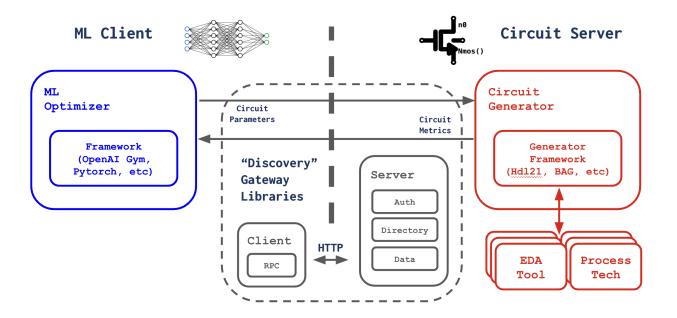

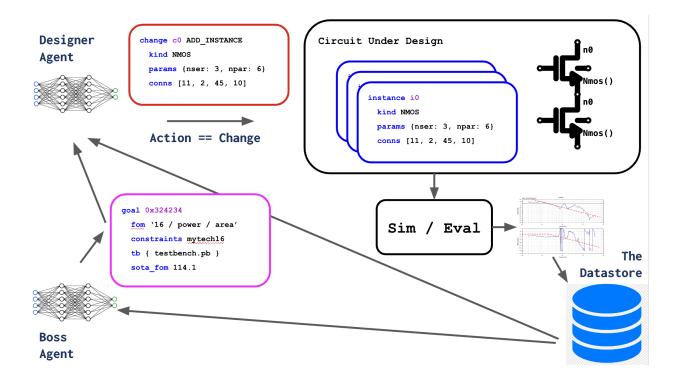

| 8.5  | CktGym Framework                                                                  | 129 |

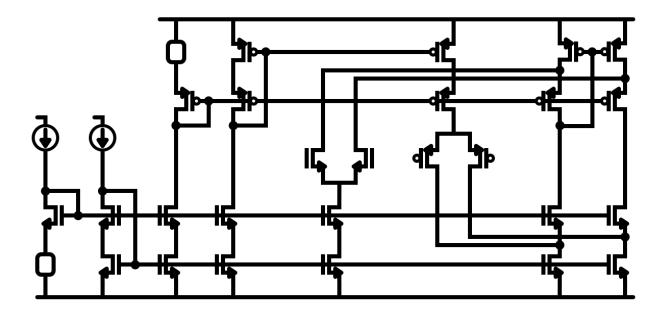

| 8.6  | Rail to Rail Input Op-Amp                                                         | 131 |

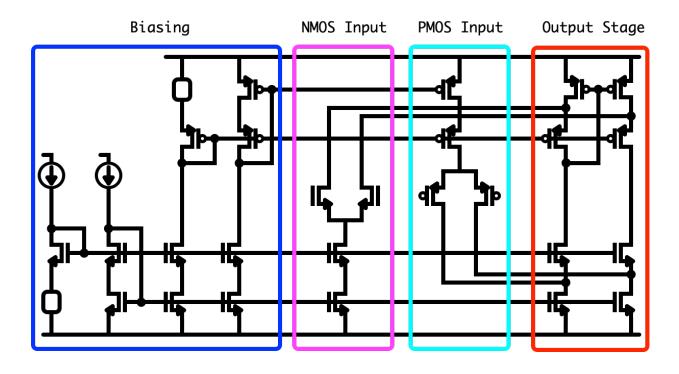

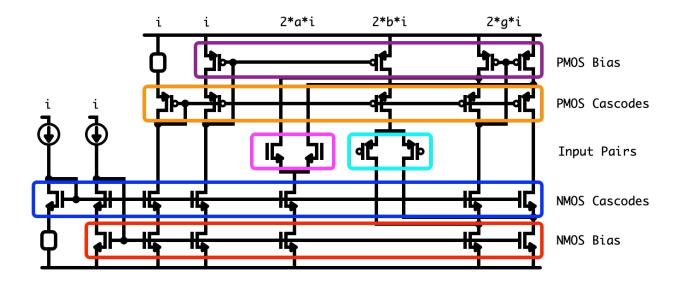

| 8.7  | Op-Amp Separated by Descriptive Sections                                          | 132 |

| 8.8  | Op-Amp in terms of independent devices and current densities                      | 132 |

| 9.1  | ML Designer                                                                       | 138 |

# List of Tables

| 3.1 | Hdl21 Primitives Library |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 3 | 9 |

|-----|--------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|---|

|-----|--------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|---|

#### Acknowledgments

What are we doing here? Why did I do any of this?

Some background: as compared to most authors of these dissertation-acknowledgments, I'm pretty old. I had been a pro for a bit over a decade, designing embedded systems, analog integrated circuits, and software for their designers. Most of that time was at Apple Inc. When I left there in early 2019, my wife Lauren and I hit the road, and were traveling for about the following year, right up until coming to Berkeley at the start of 2020.

Likely related, I always saw the PhD through the lens of at-will employment. It's a weird research job. It's highly disorganized, the pay is pretty bad, but the level of freedom can't be beat. Every job has some element of education attached to it; this one has more than most. And it's got an extra weird bonus after five or so years: once you're any good at it, you're fired.

There is a tell I often detect in how people think of this. It only takes a single word, and that word is *getting*. As in, what you're doing here is *getting* a degree. As in, the actions along the way are the means to an end. And I get it. For most people, at most places in education, that's a fair description. But in this case it was never about a credential. I don't expect there will ever be a job that I want and could get as Dr-Dan, but couldn't get as regular-Dan. There were no ends to be justified; this was always about what happened along the way. (Notably, that is a lot easier outlook to have with cash flowing from the university to me, and not the other way around.)

So, why? There were a few things I wanted to get out of it. I wanted to spend a chunk of my life and career putting something helpful out into the world, without the usual commercial burdens attached. Something that people throughout our field (notably including myself) could benefit from. And I didn't know exactly what it would be. It was always likely to end up in the space it did (the software for the chip designers). But I came in open-minded about a broader change. Sophia Shao, Krste Asanovic, Alberto Sangiovanni-Vincentelli, Kurt Keutzer, and Pieter Abbeel all provided invaluable guidance in this search.

Given that freedom, I thought there was a small (but reasonable) chance of landing on something really cool. I also thought there was a reasonable chance of hating it and quickly bailing. This ties back to the *getting* mentality. In the means-justifying view, walking away is an admission of failure, in the way that, say, taking a new job, disliking it and quitting is not. I never had that feeling of signing up for an extended commitment. I always figured if things weren't good at this weird job, I could try the next one.

And lastly, I figured that at the end of my life, trying so would be an experience that I either had, or didn't. And I figured between those, I'd prefer to have it.

How did it go? Overall, somewhere between OK and good. Those big-picture goals were certainly met. As well as I could have imagined? Not even close. Would I recommend doing the same, to someone similarly situated? Only if you have a very specific program of research in mind, and a great partnership and buy-in to pursue it. So, only for very few extra-weird weirdos like me.

There were a few things I didn't realize going in. For one, we do collaboration different, and I would say on balance, worse. If the department has 1000 grad students (give or take, that's about right), those 1000 people work far more like 1000 one-person start-ups than a single 1000 person company. There's some collaboration, sure, but most of the important stuff is the product of individuals doing what they think is best. Most successful collaboration is self-organized, peer to peer. There aren't great mechanisms for setting a broader agenda, or aligning large swathes of people towards common projects. These agendas can even directly contradict! That is, to a large extent, the nature of the research organization. It's perfectly self-consistent, for example, for someone in the physics department to be trying to prove there is a Higgs boson, and for someone else just down the cube-hall to be trying to prove there is no Higgs boson. Those goals conflict one another, but both serve the institution's broader goal, creating new knowledge wherever it can be found.

Oh and COVID. That didn't help. You may have noticed I mentioned starting in January 2020, shortly before most of the world shut down. Berkeley shut down especially early, especially long, and especially hard. By the time the campus returned to normal, habits had set in, and I more or less continued to work remotely. I had the space and the money to make a nice home office. My home in San Francisco was always just far enough away to make the trans-bay commute a deterrent. That all didn't help to foster collaboration, and ultimately probably hurt the work. But the combination of research-life and WFH-life had an upside I didn't expect, and in retrospect couldn't imagine having gone without.

The COVID era, especially those early days, seemed to drive a lot of locked-down laptop-jockeys pretty crazy. Lauren and I were less affected. We'd been unintentionally preparing for over a year. We had been on the road, usually not knowing anyone but ourselves and our dog, Alice. Of course there were differences. We could no longer hop between cafes or check out new restaurants. But not having an office and having to entertain each other were old hat. Our cat, Sammy, joined the family shortly thereafter and brought his own brand of entertainment. But the fun really began in 2022, when with the birth of our son Daniel.

I can recall hearing so, so many condescending-sounding things about being a parent before becoming one. "You'll understand when you have kids of your own" was a common way my own family tended to put it, with a soft pat on the head. That and countless others did sound condescending at the time. But they reflect some deep truth, on a few levels. There really is a great deal that there's no preparing for, no intellectualizing, no point trying to understand any way but firsthand. Most of this is emotional. It's very hard, and I think typically comes across as very tacky, to try to accurately express how one feels about their kids. It's different from every other close relationship, including those to the rest of family, to friends, to a romantic partner. The non-tacky version tends to be something like: your mother and I love you more than anything, and would do anything for you. That sentence is both true, and immeasurably lacking in reflecting the reality behind it. I have to imagine all parents feel this way. I certainly do, and by any outward indication Lauren does so even more.

That's all to say: it's been great to be at home these past 18 months.

It's also to say, the primary acknowledgments here belong to Lauren, Danny, and the

new guy joining our family in 2024. There is an apparent practice of having a separate dedication section for writings like this, in which the totality of the content is dedicated "to", like, the author's mom, or wife, or cat, or whoever. Who on earth wants this nerdy engineering-stuff dedicated to them? Poetry, music, deep investigations of the human soul, sure. But this stuff? Hopefully I can save them a cringe or two by omitting that section, and better communicate how important they are through ramblings like these.

My deepest appreciation to this work's advisor, Vladimir Stojanovic, and to Bora Nikolic and Elad Alon for guiding its early and middle stages. Vladimir said I should write this (the real thesis, not this soft-core warmup section) for a first year grad student. Not "like a dry academic paper", and not "like my blog". I am confident it achieves at least one of those.

Thanks to Kris Pister, Ali Niknejad, and Bora for inviting me into their one of a kind education experience. That fun - and much of the work presented here - would not be possible without the team at Intel, especially Bryan Casper and Soner Yaldiz. Aviral Pandey and Arya Reais-Parsi have been incredible collaborators on most of the work presented here. Thanks are due to the teams at Blue Cheetah and at GoogleX, including Elad, Krishna Settaluri, Dino Ruic, Raj Apte, and many more.

Thanks to the people who taught me how to do this job: Raman Thiara, Gin Yee, Emerson Fang, Jafar Savoj, Dennis Fischette, Brian Leibowitz, Jose Tierno, Edwin Guo, and so many more, especially Sanjeev Maheshwari. Jared Zerbe deserves special thanks for engendering much of Apple's research outreach in our field, and for providing invaluable real-world design review feedback to our student-designers. Jason Jacobs has long been a great friend and collaborator. He, Elad, and Brian provided some of the first inclings that something like the work presented here would be possible, and that I could do it, and that I should.

Lastly, Ming-Shuan Chen, who once tried to shout me out in his own dissertation. He failed, and instead thanked Dan *Friedman*. Dan is a much more reknown figure in our field, primarily known for his work at IBM. To my knowledge, Dan and Ming-Shuan have never met. And in that vein I would especially like to thank Shaun Chen.

# Chapter 1

# Introduction

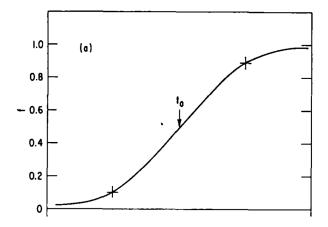

This is a thesis about integrated circuits, and more specifically about how we design them. The first and likely most important question should be *who cares*. ICs were invented in 1959, roughly 65 years before this writing. The whole field may seem old, or may seem fairly combed-over for novel research topics. On Fisher and Pry's "simple model" [12], now more commonly known as the s-curve, one might reasonably believe we are more or less at the top right.

Figure 1.1: Fisher and Pry's S-Curve of Technological Change [12]

In truth, the field stands to become far more important - and far more ripe for design-level breakthroughs - in the next 65 years than it was in its first 65.

Why? To date, the primary manifestation of our semiconductor-based information age is the enablement of software to "eat" countless fields of endeavor. Over the course of the 20th century, silicon and CMOS proved the ideal forum for building general-purpose computation machines. Their general-purpose-ness was their true killer app: it enabled a conceptually new layer, shortly thereafter named *software*, by which they could be redirected to a seemingly endless variety of tasks.

Moreover, these machines kept getting better, year after year. In 1965's Cramming More Components onto Integrated Circuits [40], Gordon Moore introduced the now-famous "law" setting the field on an exponential rate of progress for the foreseeable future. But the phrase Moore's Law has always been off. The inclusion of the term law, coupled with the fact that it concerns a complicated scientific-seeming topic, leads people to believe it is some law of nature, like Newton's laws of motion or the second law of thermodynamics. Or perhaps more like Ahmdal's law, which sets a theoretical limit on a category of abstract quantities (computer programs).

What Gordon Moore made in truth was a prediction, and one about people. Particularly the intellectual progress of a group of people driving semiconductor design and fabrication. He predicted an exponential rate of progress in this field, extending indefinitely into the future. Most incredibly, he proved right, for decades on end. Countless inventions and person-years were required; the "law" became a sort of self-fulfilling prophecy as the north-star goal for the field. Later, predicting the end of Moore's Law became a popular prognostication game. Strangely for many, including some of the leaders of our field, the notion of it having an end failed to dispel the idea of its inevitability. No one expects gravity or entropy to end, much less any time soon. But many accept chip-progress as a fact of nature, somehow confined to the late 20th century.

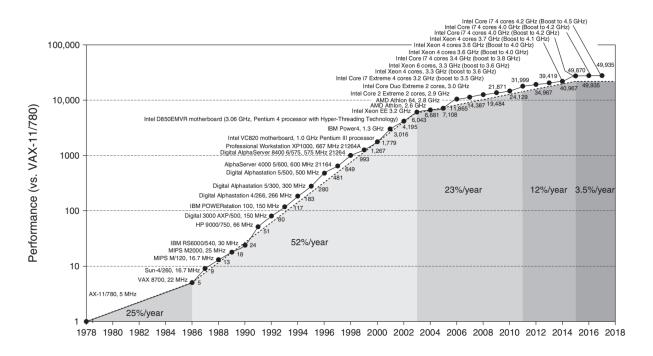

Figure 1.2: Patterson and Hennessy's Depiction of the End of Moore's Law [22]

Herbert Stein made a more ironclad eponymous "law" a few decades later: if something cannot go on forever, it will stop. So it is with Moore's great prediction. There is no definitive accounting for when it ended, but at the time of this writing, the "Moore Era" is over. Countless accounts of its wind-down have been offered, including figure 1.2, excerpted from Patterson & Hennessy's seminal computer architecture text.

The end of the Moore Era coincided with large swaths of human activity just catching on to just how useful all this computation could be. And perhaps more impactfully, other swathes realized that incredibly computation-intensive methods (i.e. those of machine learning) proved a ways more suitable to a variety of tasks than prior, "expert" programmed methods. The combination means one thing: there will be much more need for much more specialized, task-centric hardware. Where software "ate" the last era, hardware will eat the next one. And there is no more free lunch to be dined-out on from a rapidly ever-improving set of process technologies.

While not especially widespread, this outlook is also not novel. The same Patterson & Hennessy responsible for cataloging the wind-down shown in figure 1.2 went so far as to deem the combination of developments the dawn of a "new golden age" [22]. Whether we view this as a challenge or opportunity, the world of the coming decades will need far more customized electronic hardware than that of decades past. Integrated circuits will continue to be at their core. ICs are also among the most laborious, most capital intensive, most challenging parts to design - and especially to get right. We will need a lot - perhaps 10x or 100x - more of them.

### 1.1 The IC Design Process

Integrated circuits are "integrated" in the sense that more than one - and often in current practice, more than ten orders of magnitude more than one - circuit component is integrated in a single silicon die.

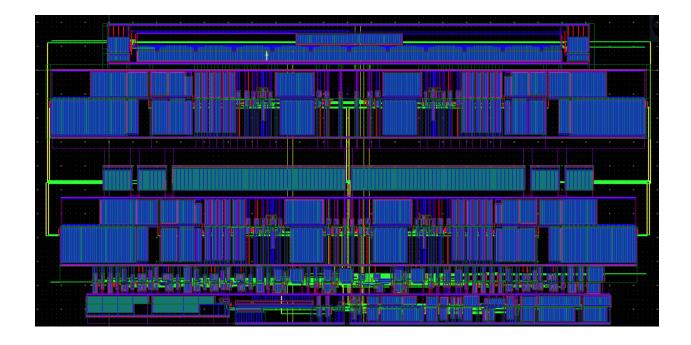

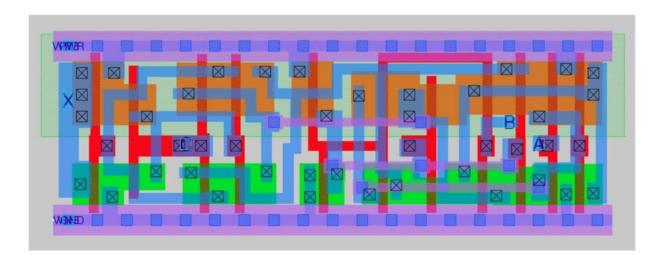

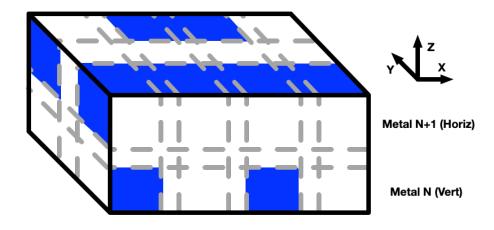

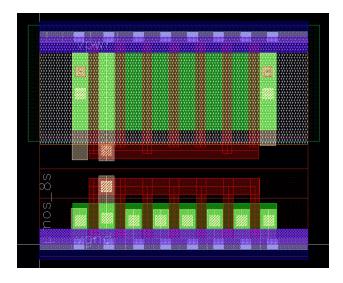

The most detailed representation of these circuits, and the sole representation sufficiently detailed for fabrication, is commonly called *layout*. IC layout is a chip's physical blueprint. The nature of silicon manufacturing allows for representing these blueprints in "2.5D" terms. Each silicon wafer is extremely uniform in one of its three axes. This axis extends into and out of the plane of the die surface, and is commonly referred to as the z-axis. This z-axis is typically split into a discrete number of *layers*. These layers refer to a variety of physical features, such as metal connections, insulators there-between, ion injections which form transistor junctions, etc. The IC "x" and "y" dimensions, in contrast, span the surface of the die, and are much more free-form to be specified by the IC designer. These two axes typically allow for nearly free-form closed 2D polygons. An IC blueprint is therefore conceptually comprised of a list of such polygons, each affixed with a z-axis layer annotation. Figure 1.3 depicts a typical IC layout visualization.

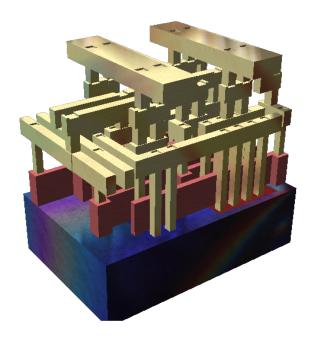

Figure 1.4 expands this view to the three-dimensional structure that it represents.

Figure 1.3: Typical IC Layout Visualization. X and Y axes represent dimensions on-die. Colors represent z-axis layer annotations.

While layout is the sole language comprehensible for IC fabrication, it is generally far too detailed for much of IC design. The silicon design and closely related electronic design automation (EDA) software fields have, over time, produced a substantial stack of software, concepts, and practices which allow for IC-design at far more abstract levels than that of physical layout. Different subsets of the IC field have proven more and less amenable to these improvements.

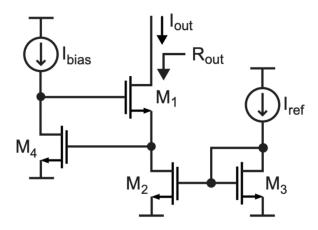

This stack's second-lowest layer is often called the *circuit* level. In circuit terms, chips are made of combinations of primitive components such as MOS transistors and resistors, and connections between them.

Each circuit component (or *element*) generally has a short-form conceptual and mathematical description (such as "V = IR"). Their realizations are technology and implementation specific, often requiring elaborate combinations of the 2.5D layout geometry. For example MOS transistors include their core conceptual terminal diffusions and gate material, but often also include countless performance and yield-enhancing features, especially at advanced geometries. Linear resistors might similarly be built of any of a number of materials. It is the inclusion of more than one of these conceptual components that makes silicon circuits "integrated"; their "integration" refers to a prior era, in which each circuit component would need be a separate element on a circuit board.

In a loose analogy to software, layout is akin to machine code. It is the sole format understood by the underlying implementation technology (in software, the processor; in

Figure 1.4: Three-Dimensional IC Blueprint

silicon, the fab). Circuits are then analogous to the assembly language. Each circuit (and assembly) is specific to its underlying implementation technology.

### 1.2 The Analog Bottleneck

For decades both software and hardware design have searched for more productive, higher levels of abstraction. These efforts have proven more and less successful in different substripes of IC design. The next key layer, popularized in the 1980s, maps roughly to "C-level" languages popular for low-level and "systems" software. Popular hardware description languages (HDLs) introduced around this time include Verilog and VHDL. Each allow for technology-independent descriptions of digital circuits. This paradigm also introduces the logical (rather than the circuit) level as the primary one of simulation and verification. Discrete-event simulation further enhances the efficiency of this verification paradigm.

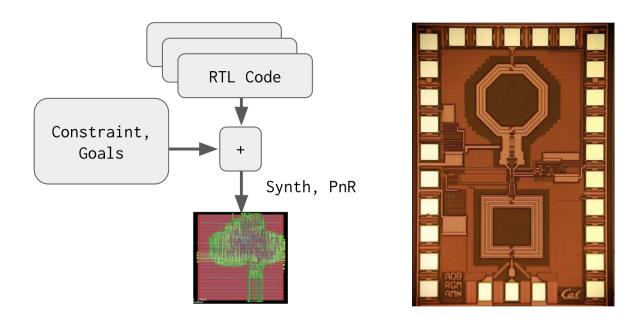

In addition to enhancing the efficacy of verification, the digital HDLs provided a dramatic improvement in workflow to produce layout. In the typical digital back-end flow, HDL code is transformed into layout by way of an optimizing "layout compiler". Designers provide a combination of register-transfer level (RTL) HDL code, plus a set of physical constraints and/or goals. These two primary inputs are fed to a compilation pipeline, generally comprising a combination of logic synthesis which translates RTL to gate-level netlists, and "place and route" (PnR) layout compilation.

Notably, the benefits afforded by the 80s-era HDLs accrue to digital circuits, but largely fail to aid analog ones. Analog circuits escape the logical verification paradigm, and instead rely on the circuit-level concepts such as the solutions to Kirchoff's laws for verification. Moreover, analog circuits have escaped the productivity gains of the automatic layout-compilation pipeline, for reasons covered in detail in later sections of this manuscript.

Analog and custom circuits have accordingly long been acknowledged as a bottleneck in the IC design process. In the author's anecdotal experience, analog efforts tend to produce (notably crude) designer productivity metrics (e.g. transistor-count per designer-month) on the order of 100-1000x lower than their digital peers. This may be, and in the author's opinion is likely to be, the bottleneck to the post-Moore era. Many other research efforts, including many substantial sources of inspiration here, endeavor to further raise the productivity and abstraction-level of the digital flow. This work focuses on analog and custom circuits.

### 1.3 The Likely Role of Open Source

The period during which this work was completed (2020-23) corresponded to something of a renaissance in open source activity in the silicon field. Ironically IC EDA (and particularly its outpost here at Berkeley) were pioneers in open-source distribution, particularly that for industrial-grade applications. SPICE [56] serves as a prime example. The many branches of SPICE's family tree have since largely been absorbed into various commercial and in-house products dotting the IC industry. Open-source then slowly disappeared from the IC field's common set of practices.

We note that three related, relevant quantities can in principle be distributed in opensource form:

- 1. Open-source *design content*, i.e. HDL code, circuits, and/or layouts, possibly coherently arranged into instantiable silicon Intellectual Property (IP),

- 2. Open-source EDA software, the programs required to produce these circuits,

- 3. Open-source *process technology*, i.e. the underlying fabrication steps, or the designer "API" to these technologies, commonly called a Process Design Kit (PDK).

The three are separable in principle, but tightly tied in practice.

The relationship between (2) EDA and (3) fab is particularly tangled. Particularly, most process-portable EDA software requires an elaborate "technology setup" set of input - the details of the technology required by the tool. For digital PnR this often comes in the form of a technology-LEF, for physical verification (Layout vs Schematic (LVS), Design Rule Checks (DRC)) it includes countless design rules and detailed specifications of the process. More important, this fab input is (a) highly laborious (and crucial) to get right, (b) generally tightly tied to the EDA tool it feeds, and (c) often authored in a language or format which is proprietary to each tool. While fabs author their "EDA input", they are often not at liberty to publish it. Fabricators understandably focus on the most popular such tools (buoyed by

relationships with the most popular EDA software providers). Supporting a new suite of EDA software is no small ask.

Design content is, in principle, the easiest of the three to open-source. Digital design in HDL (or modern HDLs such as Chisel) are especially amenable. Many research processor designs - and even a few industrial ones - are accordingly available in open-source distribution. Analog circuits are much more dependent on their implementation technologies, and accordingly have seen much less success in open source.

Open source EDA, especially that for digital design, is the subject of a great deal of academic research. But in every category known to the author, available academic/open-source EDA lags commercial offerings, often substantially and in metrics directly relevant to designers (quality of results, execution time, etc.). More importantly, technology-dependent open-source EDA suffers from the problems of *access* to process technologies described a few paragraphs back.

The tight tying of fab and EDA would seem to drive a desire for open-source process technology. Such efforts, particularly those of [3], have helped to produce open-source process design kits from SkyWater Technologies, GlobalFoundries, and IHP Microlectronics. These efforts have generally been led by third parties and/or communities rather than the fabs themselves. Paired (and often free) multi-project shuttles have enabled a wide variety of projects which would not otherwise have been possible.

Despite these laudable efforts, I do not hold much hope for open-source distribution of silicon process technologies, or even of "just" their PDKs. Before the open-source release of SkyWater's 130nm technology, open-source was clearly highly counter-cultural to the entire fab space. The other fabs have clearly seen the efforts of the early open-sourcers, especially SkyWater. And they have hopefully noticed the amount of additional attention driven to a few roughly two-decades-old technologies. But they have simultaneously observed a more concerning shift: one in world public policy. A number of nations, notably including the US and China, have made semiconductor technologies a central focus of new policy initiatives. The primary impact on the distribution of technology information has been to make it more constrained. Open-source is essentially the *least* constrained form of such distribution. Even if it has not been explicitly banned or prohibited, I expect most fabs have gotten a message, they are far better off staying away.

I do believe that open-source process technologies will have a helpful role in IC education. Berkeley's curriculum includes an unusually great deal of exposure to realistic, modern implementation technologies, culminating in the "tape-out course" series detailed in [6] and [15]. These experiences have proven much more difficult for many peer institutions to provide. Access to these technologies is tightly guarded and costly to maintain. The emergence of (at least a few) open-source technologies allows for a broader suite of educational opportunities in realistic implementation technologies, as described in [2].

### 1.4 The Roadmap

I believe that our field is far more important than most to the world's next several decades. And I think we can - and need to - do it a ways better.

This thesis doesn't have all the answers. <sup>1</sup> It catalogues what I believe are valuable contributions to the technology of producing circuits, particularly custom and analog ones, including their physical layouts. And it attempts to point out a number of what I believe have been dead ends.

One sub-thesis: many such projects suffer from insisting on attempting to reinvent the entirety of our industry, each and every time over. I fear this work has not entirely avoided this trap. One virtue (as defined by its author) is the underlying work's modularity. While I am deeply grateful for all of this work's collaborators both inside and outside of UC Berkeley, the sheer effort involved pales in comparison to the 65 year history of the IC and EDA industries, or even their analog sub-fields. This modularity goal has proven valuable for the several research, corporate, and start-up users who bravely enjoined their fate to this work, often while it was still on the runway. Many have picked up this effort's pieces; to my knowledge, no two have adopted the same set.

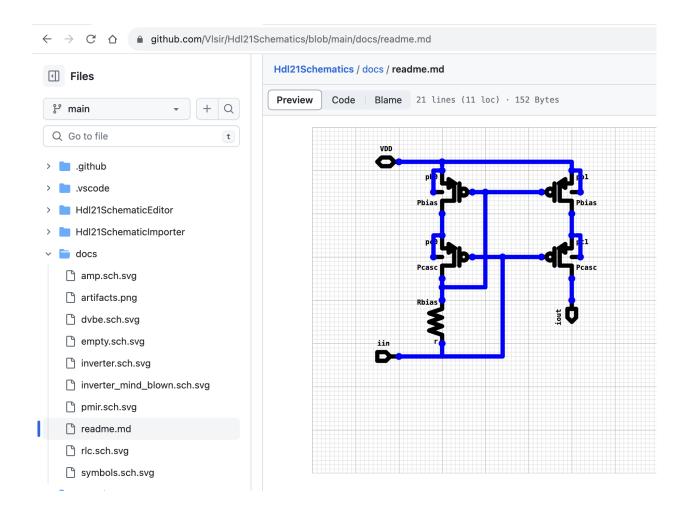

A further sub-thesis: making the next rounds of progress will require taking a few steps back. Particularly, several long-worn ideas need a rethink. We will cover:

- The core data model used to represent IC design content, commonly referred to as the design database, and a cloud-era substitute.

- The primary design-entry mechanisms for custom and analog circuits. For most of their history these have been pictures. This thesis argues for, and introduces methods to, make them better with code instead.

- A re-do of those graphical pictures, for the (smaller number of) cases where we agree they provide value. Emphasis is placed on *portability* and *sharing*.

- A survey of both historical research attempts to, and first-person software attempts to, rethink the custom layout process. Several are tried, to varying effect. My primary answer to what works best remains "it depends".

- An introduction to "Machine Learning (ML) for X", where "X" becomes circuits. What does it require for ML techniques to make real contributions to the production of circuits, layouts, or the software that aids them?

<sup>&</sup>lt;sup>1</sup>I have been accused of believing the opposite. But I don't! It says so, right here in the front!

# Chapter 2

# IC Design Databases

# 2.1 "Databases" (Ahem) 101

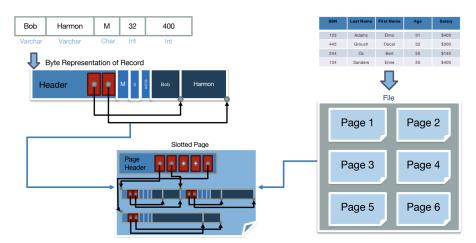

IC design data is commonly represented in "design databases". These systems are inspired by relational database management systems (RDBMS), ubiquitously used throughout modern server-side applications. IC databases generally look much like the low layers of an RDBMS. They include a binary format for storing and packing records, and a API for querying and writing those records. The typical low layers of such an RDBMS are illustrated in Figure 2.1 from our department's own introductory database systems course.

Figure 2.1: RDBMS Low Layers

Instead of a dedicated query *language* (e.g. SQL) and accompanying compiler and query-optimizer, IC databases are typically embedded in a host programming language, and expose

an API to manipulate design data in that language. Perhaps the most prominent commercial example is OpenAccess [14], originally authored by Cadence Design Systems. Perhaps the most prominent freely available database is OpenDB [51], notable for its centrality to the OpenROAD project [27].

These databases are optimized to enable efficient offloading of design data between memory and disk, especially for designs too large to reasonably fit into the former. This goal is near entirely driven by one application: digital place-and-route layout compilation. For common digital circuits including millions of gates and associated metadata, the optimization makes sense. Optimal PnR, and even "good enough" PnR, includes several NP-complete sub-problems, and commonly requires industrial-scale resources and days of runtime. Without such optimizations, large compilations often fail to complete.

Analog circuits differ in several respects. First and perhaps most importantly: they are much smaller. Rarely if ever do they contain millions of elements, and infrequently even thousands.

Second, analog circuits demand to be designed and laid out hierarchically for another reason: their verification is hierarchical. Their necessary mode of evaluation - the SPICE-class simulation - is far too slow, and scales far too poorly, to evaluate compound circuits in useful runtimes. Compound analog circuits such as Radio Frequency (RF) transceivers, wireline Serializer/Deserializer transceivers (SERDES), data converters, and Phase-Locked Loops (PLLs) are commonly comprised of subsystems whose simulation-based verification is far more tractable than that of the complete system.

#### 2.2 ProtoBuf 101

The  $21^{st}$  century advent of widespread cloud computing and accompanying "hyper-scalar" cloud-service providers generated something of a renaissance in markup-style "data languages", and in demand for network-serializable data more generally.

Their demands are entirety practical: projects of their scale require hundreds of serverside programs cooperating and exchanging data. These programs are commonly designed by hundreds of disparate, largely independent teams, comprising thousands (or tens of thousands) of individual engineers. They have no chance at aligning a tall stack of libraries, versions, operating system requirements, and other dependencies which would be required to run on a single machine, in a single program.

Moreover, many of these "datacenter-scale programs" subsystems have vastly different resources needs, and different prospects for *scaling* across usage. Some require specialty compute resources such as machine learning acceleration, either via graphics processors or special-purpose silicon. Others, e.g. for data caching, benefit from little compute but greatly from unusually large memory systems. Others "scale-out", requiring little compute, memory, or other resources per task, but requiring tremendous numbers of copies of that task, benefitting from near-perfect scaling via hardware parallelism. These subcomponents are then broken into sub-programs, each of which executes on appropriate hardware, and in

tailored execution environments. Communication between these components occurs via the datacenter network.

Protocol buffers (ProtoBuf) [55] were introduced first internally to Google and then as open-source software to meet these needs of communication between diverse programs exchanging rich structured data. The ProtoBuf system principally includes three components:

- An efficient binary wire format,

- A data schema description language (SDL), and

- A paired binding code compiler

Several similar, generally related follow-on projects including Cap'n Proto, FlatBuffers, and FlexBuffers each take similar high-level approaches. Each includes the three core protobuf components (binary format, schema language, and compiler), differing in a variety of trade-offs in schema feature-set and format design. Such projects have proliferated sufficiently to motivate comparative research [44] into their relative performance strengths and weaknesses, across a variety of data content.

Meta-programs using protobuf begin by "programming" datatypes in its SDL. This operates much like a programming language in which only struct-definitions are allowed. The core protobuf structure-type message indicates its intended usage in communication. The protobuf compiler then accepts this SDL as input, and transforms it into typed "bindings" in a diverse set of programming languages, notably including Python, C++, Rust, JavaScript, and most other popular alternatives. An example protobuf SDL message definition:

```

syntax = "proto3";

message SearchRequest {

string query = 1;

int32 page_number = 2;

int32 results_per_page = 3;

}

```

Protocol Buffer messages and its SDL are both strongly typed. Messages include a variety of built-in primitive types, similar to those of most programming languages. These include integer and floating-point numeric types, booleans, strings, byte arrays, and user-defined enumerations. Message types can be nested, holding attributes valued by other messages. Several common container-types such as sequences (repeated), union types (oneof), and key-value mappings (map) are also built in. Examples of more of these constructs:

```

message SearchResponse {

repeated Result results = 1;

}

message Result {

```

```

string url = 1;

string title = 2;

repeated string snippets = 3;

}

message SampleMessage {

oneof test_oneof {

string name = 4;

SubMessage sub_message = 9;

}

}

```

### 2.3 The VLSIR Design Database Schema

VLSIR is the name of this work's central design database, and of the broader software system which operates on it. VLSIR is designed in ProtoBuf. Its design database schema is authored in the ProtoBuf SDL. A simplified excerpt from the VLSIR schema, defining the layout.Instance type, is included below.

The VLSIR schema defines such types for circuits, layout, spice-class simulation input and output, and process technology. The schema format serves as a core exchange medium for a variety of programs and libraries written in a variety of languages, with varying trade-offs between designer productivity, performance, and ease of compatibility with related libraries.

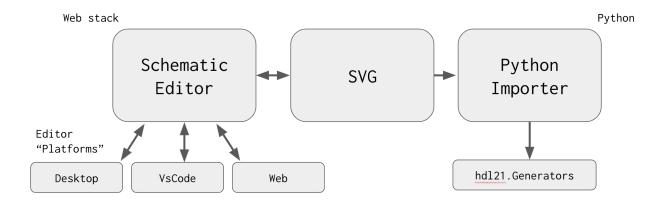

### 2.4 Design of the VLSIR Software System

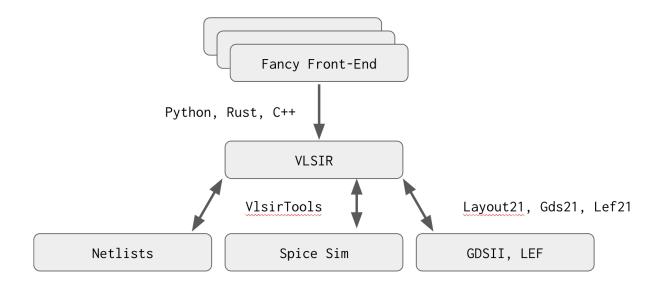

The broader VLSIR system, schematically depicted in Figure 2.2, is heavily inspired by the LLVM [31] compiler platform, and by the FIRRTL system ([23], [32]) developed shortly beforehand by colleagues here at UC Berkeley. Like LLVM and FIRRTL, VLSIR defines a central design interchange format. Both LLVM and FIRRTL name this layer their Intermediate Representation (IR). The name *VLSIR* is in fact a portmanteau of two acronyms: the

Figure 2.2: The VLSIR System

(quite dated) Very Large Scale Integration (VLSI) and intermediate representation. Where LLVM and FIRRTL's IRs are defined through the constructs of their respective implementation languages, VLSIR's is defined in the protocol buffer SDL. All three projects build this central data layer for the purposes of decoupling and reusing diverse *front and back ends*.

The roles of front-ends and back-ends differ somewhat between the three. In LLVM, a front-end is (more or less) a programming language. The compilers for Rust and C++, for example, differ principally in the front-end, which translates user-authored code into LLVM's core intermediate representations. A back-end is (again, more or less) a target compiler platform. Examples generally include combinations of the target instruction set (x86, ARM, RISC-V, etc), and potentially the target OS. FIRRTL has a similar concept of a front-end, whereas its back-ends are hardware "elaboration targets", which might be ASIC synthesis, FPGAs, or cloud-scale distributed processing environments.

VLSIR's front-ends are also user-facing programming tools. Generally we have eschewed designing altogether new languages (or "DSL"s) and focused on providing libraries in existing, popular languages. These front ends include libraries for circuit design (chapter 3), layout design (chapter 5), and several dedicated libraries targeting specific circuit families. VLSIR's back-ends are generally its interface to existing EDA software and data formats. For example, a widely used back end focuses on executing SPICE-class simulation, parsing and providing its results in schema-defined data structures.

The choice of ProtoBuf affords for a rich diversity of front and back ends, implemented in a diversity of programming languages and featuring diverse needs for performance, portability, and designer productivity. Protobuf's efficient binary format is especially invaluable for VLSIR's most information-rich set of data: that of IC layout. While [44] finds that alternative serialization systems can outperform protobuf in space-efficiency and in (de)serialization runtime, the differences are, on VLSIR's scale of demands, fairly immaterial. More important to VLSIR, the protobuf ecosystem and surrounding tools are materially more developed than the peer systems compared. At the scale of VLSIR's needs, the shared high-level approach is what dictates the bulk of performance; relative differences inject second-order effects.

#### VLSIR Circuits

To illustrate the design of the VLSIR schema, we highlight one of its core subcomponents: circuit descriptions. VLSIR's database schema includes a circuit subcomponent which defines its circuit-level data model. The VLSIR circuit model is intentionally low-level, similar to that of structural Verilog. The vlsir.circuit components are a core interchange vessel for most programs using Hdl21, covered in chapter 3.

As in Hdl21 and Verilog, VLSIR's principal element of hardware reuse is called its Module. vlsir.circuit.Modules consist of:

- Instances of other Modules, or of "headers" to externally-defined ExternalModules

- Signals, each of potentially non-unity width. Each vlsir.circuit.Signal is therefore similar to the bus or vector of many popular HDLs, or more specifically to the packed array of Verilog. A subset of Signals are annotated with Port attributes which indicate their availability for external connections.

- Connections there-between. Since Signals, including those used as Ports, have non-unit bus widths, combinations to comprise their connections include sub-bus Slices as well as series Concatenations. This is the principal difference between VLSIR's model and that of lower-level models such as common in SPICE languages; signals and ports are all buses, and therefore can be combined in this variety of ways.

The principal collection of hardware content, vlsir.circuit.Package, is a collection of Module definitions which may instantiate each other. The VLSIR Package might commonly be named a "library" in similar models. Each Package includes a dependency-ordered list of Modules, as well as the headers to any ExternalModules it requires.

A simplified excerpt of the vlsir.circuit data schema:

```

//!

//! # vlsir Circuit Schema

//!

syntax = "proto3";

package vlsir.circuit;

import "utils.proto";

// # Package

```

```

// A Collection of Modules and ExternalModules

message Package {

// Domain Name

string domain = 1;

// `Module` Definitions

repeated Module modules = 2;

// `ExternalModule` Headers

repeated ExternalModule ext_modules = 3;

// Description

string desc = 10;

}

// # Port

// An externally-visible `Signal` with a `Direction`.

message Port {

enum Direction {

INPUT = 0;

OUTPUT = 1;

INOUT = 2;

NONE = 3;

}

string signal = 1;  // Reference to `Signal` by name

Direction direction = 2; // Port direction

}

// # Signal

// A named connection element, potentially with non-unit `width`.

message Signal {

// Signal Name

string name = 1;

// Bus Width

int64 width = 2;

}

// # Signal Slice

// Reference to a subset of bits of `signal`.

// Indices `top` and `bot` are both inclusive,

// similar to popular HDLs.

message Slice {

// Parent Signal Name

string signal = 1;

// Top Index

```

```

int64 top = 2;

// Bottom Index

int64 bot = 3;

}

// Signal Concatenation

message Concat {

repeated ConnectionTarget parts = 1;

}

// # ConnectionTarget Union

// Enumerates all types that can be

// (a) Connected to Ports, and

// (b) Concatenated

message ConnectionTarget {

oneof stype {

string sig = 1;  // Reference to `Signal` (name) `sig`

Slice slice = 2;  // Slice into signals

Concat concat = 3; // Concatenation of signals

}

}

// # Port Connection

// Pairing between an Instance port (name)

// and a parent-module ConnectionTarget.

message Connection {

string portname = 1;

ConnectionTarget target = 2;

}

// Module Instance

message Instance {

// Instance Name

string name = 1;

// Reference to Module instantiated

vlsir.utils.Reference module = 2;

// Parameter Values

repeated vlsir.utils.Param parameters = 3;

// Port `Connection`s

repeated Connection connections = 4;

}

```

```

// Module - the primary unit of hardware re-use

message Module {

// Module Name

string name = 1;

// Port List, referring to elements of `signals` by name

// Ordered as they will be in order-sensitive formats,

// such as typical SPICE netlist dialects.

repeated Port ports = 2;

// Signal Definitions, including externally-facing `Port`s

repeated Signal signals = 3;

// Module Instances

repeated Instance instances = 4;

// Parameters

repeated vlsir.utils.Param parameters = 5;

// Literal Contents, e.g. in downstream EDA formats

repeated string literals = 6;

}

// Spice Type, used to identify what a component is in spice

enum SpiceType {

// The default value is implicitly SUBCKT

SUBCKT = 0;

RESISTOR = 1;

CAPACITOR = 2;

INDUCTOR = 3;

MOS = 4;

DIODE = 5;

BIPOLAR = 6;

VSOURCE = 7;

ISOURCE = 8;

VCVS = 9;

VCCS = 10:

CCCS = 11;

CCVS = 12;

TLINE = 13;

}

// # Externally Defined Module

message ExternalModule {

// Qualified External Module Name

vlsir.utils.QualifiedName name = 1;

```

```

// Description

string desc = 2;

// Port Definitions

// Ordered as they will be in order-sensitive formats,

// such as typical SPICE netlist dialects.

repeated Port ports = 3;

// Signal Definitions

repeated Signal signals = 4;

// Params

repeated vlsir.utils.Param parameters = 5;

// Spice Type, SUBCKT by default

SpiceType spicetype = 6;

}

```

References (or "pointers") between HDL objects are excessively common. Each Instance in a Module needs some form of reference to whatever it should instantiate. Each Slice above requires some indication as to which parent-Signal it is slicing. Markup-style languages tend to lack native such reference capabilities. ProtoBuf is no exception. Unlike a typical executable programming language model, rich with memory-address-values "pointers" between objects, markup languages lack such an implicit address space. Schema-authors are generally required to design such mechanisms for themselves. VLSIR is no different. Most such references in VLSIR are string-based. For example the signal (parent) field of each Slice is not a memory address, or a Signal message itself, but a string-valued "reference" to its name.

The core Instance-Module reference-referent pair has a slightly more elaborate form. Modules may instantiate modules defined outside their parent Package. These "global" references use a domain-qualified name. Each Package includes a (within any given program) necessarily unique domain name-string. References to modules within the same package do not require such a domain-qualifier; their parent domain is essentially the implicit default. References to other packages use a QualifiedName-based combination of domain and module-name.

```

// # Domain-Qualified Name

// Refers to an object outside its own namespace,

// at the global domain `domain`.

message QualifiedName {

string domain = 1;

string name = 2;

}

// # Reference

// Pointer to another message,

```

```

// either defined in its own namespace (`local`)

// or another (`external`).

message Reference {

oneof to {

// Local string-valued reference.

// Typically the `name` or similar field of the referent.

string local = 1;

// Domain-qualified external reference

QualifiedName external = 2;

}

```

We envision the VLSIR reference system extending in a few more directions, e.g. to referents value with web URLs or database primary keys. The flexibility of the union-type based Reference system makes such expansions straightforward.

# Chapter 3

# Analog HDL

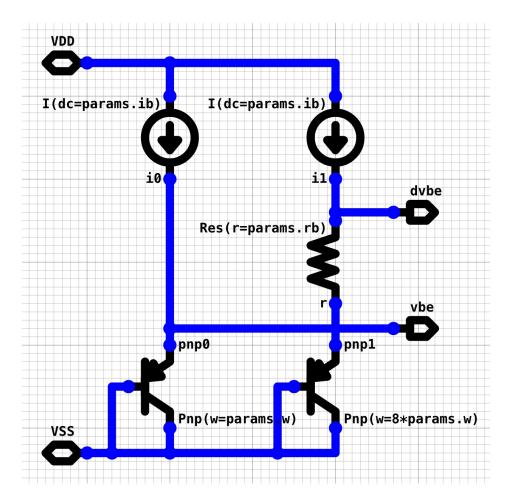

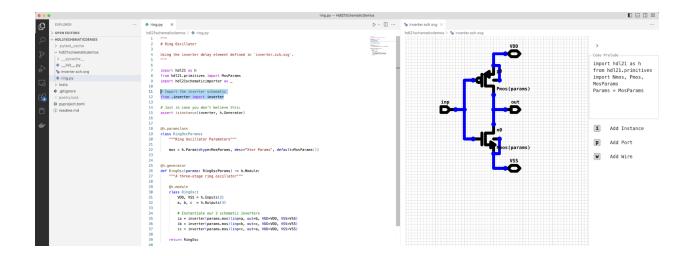

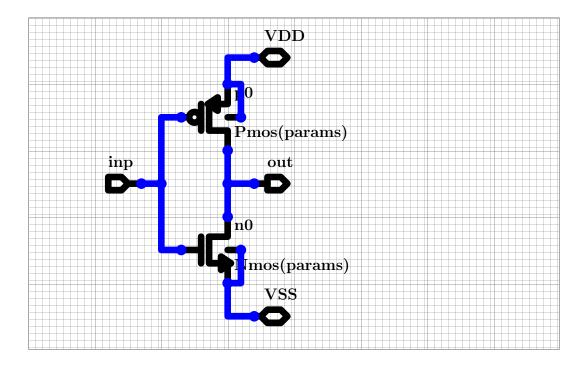

The primary high-productivity interface to producing VLSIR circuits and simulations is the Hdl21 hardware description library. Hdl21 is a Python library, targeted and optimized for analog and custom integrated circuits, and for maximum productivity with minimum fancy-programming skill. Hdl21 exposes the root-level concepts that circuit designers know and think in terms of, in the most accessible programming context available. It is principally designed as a replacement for the *lingua franca* of analog and custom circuits - the graphical schematic.

### 3.1 A (Somewhat) Brief Intro to Hdl21

#### Modules

Hdl21's primary unit of hardware reuse is the Module. It intentionally shares this name with Verilog's module and Chisel's Module, and also bears a strong resemblance to VHDL's entity and SPICE's subckt. Hdl21 Modules are "chunks" of reusable, instantiable hardware. Inside they are containers of a handful of hardware types, including:

- Instances of other Modules

- Connections between them, defined by Signals and Ports

- Fancy combinations thereof

An example Module:

```

import hdl21 as h

m = h.Module(name="MyModule")

m.i = h.Input()

m.o = h.Output(width=8)

```

```

m.s = h.Signal()

m.a = AnotherModule()

```

In addition to the procedural syntax shown above, Modules can also be defined through a class based syntax by applying the hdl21.module decorator to a class-definition.

```

import hdl21 as h

@h.module

class MyModule:

i = h.Input()

o = h.Output(width=8)

s = h.Signal()

a = AnotherModule()

```

The two Module definitions above produce identical results. The declarative style can be much more natural and expressive in many contexts, especially for designers familiar with popular HDLs. This class-based syntax is a pattern in Hdl21 usage. The Bundle and Sim objects covered in subsequent sections also make use of it.

#### **Signals**

Hdl21's primary connection type is its Signal. Hdl21 signals are similar to Verilog's wire. Each Signal has an integer-valued bus width field and serves as a multi-bit "bus". The content of Hdl21 signals is not typed; each single-bit slice of a Signal essentially represents an electrical wire.

A subset of Signals are exposed outside their parent Module. These externally-connectable signals are referred to as Ports. Hdl21 provides four port directions: Input, Output, Inout, and None. The last creates a directionless (or direction unspecified) port akin to those of common spice-level languages.

Creation of Module signal-attributes is generally performed by the built-in Signal, Port, Input, and Output "constructor functions". All of these produce the same Signal type as output. Signals have additional metadata that indicates their port visibility, direction, and usage intent. The "alternate constructors" serve as convenient shorthands for dictating this metadata, again often more comfortable for designers coming from popular HDLs.

```

import hdl21 as h

@h.module

class MyModule:

a, b = 2 * h.Input()

c, d, e = h.Outputs(3, width=16)

z, y, x, w = 4 * h.Signal()

```

#### **Connection Semantics**

Popular HDLs generally feature one of two forms of connection semantics. Verilog, VHDL, and most dedicated HDLs use "connect by call" semantics, in which signal-objects are first declared, then passed as function-call-style arguments to instances of other modules.

Chisel, in contrast, uses "connection by assignment" - more literally using the walrus := operator. Instances of child modules are created first, and their ports are directly walrus-connected to one another. No local-signal objects ever need be declared in the instantiating parent module.

```

class MyModule extends Module {

// Create Module Instances

val i1 = Module(new AnotherModule)

val i2 = Module(new AnotherModule)

// Wire them directly to one another

i1.io.a := i2.io.a

i1.io.b := i2.io.b

i1.io.c := i2.io.c

}

```

Each can be more concise and expressive depending on context. Hdl21 Modules support both connect-by-call and connect-by-assignment forms.

Connections by assignment are performed by assigning either a Signal or another instance's Port to an attribute of a Module-Instance.

```

# Create a module

m = h.Module()

# Create its internal Signals

m.a, m.b, m.c = h.Signals(3)

# Create an Instance

m.i1 = AnotherModule()

# And wire them up

m.i1.a = m.a

m.i1.b = m.b

m.i1.c = m.c

```

Instances of Hdl21 Modules provide by-name dot-access to their port objects. This allows for connect-by-assignment without creating parent-module Signals:

```

# Create a module

m = h.Module()

# Create the Instances

m.i1 = AnotherModule()

m.i2 = AnotherModule()

# And wire them up

m.i1.a = m.i2.a

m.i1.b = m.i2.b

m.i1.c = m.i2.c

```

As in Verilog and VHDL, the semantics of *calling* an Hdl21 module-instance are to provide it with connections.

```

# Create a module

m = h.Module()

# Create the Instances

m.i1 = AnotherModule()

m.i2 = AnotherModule()

# Call one to connect them

m.i1(a=m.i2.a, b=m.i2.b, c=m.i2.c)

```

These connection-calls can also be performed inline, as the instances are being created.

```

# Create a module

m = h.Module()

# Create the Instance `i1`

m.i1 = AnotherModule()

# Create another Instance `i2`, and connect to `i1`

m.i2 = AnotherModule(a=m.i1.a, b=m.i1.b, c=m.i1.c)

```

Unlike in many dedicated HDLs, connection-calls can be made "in pieces", and can be "overridden" by further connection-calls.

```

# Same as above

m = h.Module()

m.i1 = AnotherModule()

# Now only connect part of `i2`

m.i2 = AnotherModule(a=m.i1.a)

# Connect some more

m.i2(b=m.i1.b, c=m.i1.c)

# And change our mind about one

m.i2(c=m.i1.a)

```

#### How Module Works

Many or most Hdl21 Modules are written such that they look like class definitions. They are not. In truth all modules share the same (Python) type - Module itself. Module is a "final" type; it is defined to explicitly disallow sub-typing:

```

class Module:

# A simplified excerpt from `h.Module`

def __init_subclass__(cls, *_, **__):

raise RuntimeError("Sub-Typing `Module` is not supported")

```

Aside: as a design philosophy, Hdl21 generally eschews object-oriented practices in its user-facing interfaces. Several of its central types including Module and Bundle make this ban explicit. Hdl21 does make use of OOP techniques *internally*, and some at the "power user" (e.g. PDK package developer) level, primarily for defining its many hierarchy-traversing data model visitors.

Instead Hdl21 makes heavy use of the decorator pattern, particularly applying decorators to class definitions of related objects. The module (lower-case) decorator function applied to so many class bodies does something like:

```

def module(cls: type) -> Module:

# Create the `Module` object

module = Module(name=cls.__name__)

# Take a lap through the class body,

# add everything to the `Module`

for item in cls:

module.add(item)

# And return the Module

return module

```

Note the input cls is a type. Python classes are runtime objects which can be manipulated like any other. E.g. they can serve as the argument to functions (as in module) and can serve as the return value from functions (as done by many Generators). The module function takes one, trolls through all of its contents, and passes them along to Module.add. Type checking and schema organization, covered in upcoming sections, and implemented by add. When used as a class decorator, the type cls only exists during the execution of the module function body, and is then quickly dropped.

The Python language class-definition semantics have a number of helpful properties in defining typical hardware content, particularly linked modular sets of data we generally refer to as "modules". The language defines the class body to be an execution namespace which runs from top to bottom. Assignments in this class-level namespace are immediately

available both as raw identifiers, and in a "class dictionary", a string to value mapping of all the class-object's attributes. For example:

```

class C:

a = 1

b = a + 2

print(C.__dict__)

# {'a': 1, 'b': 3, ...}

```

This capacity to refer to attributes once they are defined proves particularly handy. Hardware modules are comprised of a linked, named set of hardware attributes. It is common to conceptualize this set as a graph, or as various kinds of graphs depending on context. In both Python's language-level class body definitions and in Hdl21 modules, the edges between these graph nodes are the language's native "pointers" (references).

It is possible, and even commonplace in comparable pieces of software, to define these edges otherwise. Common tactics including using name-based string references, paired with a central repository mapping all available names to their referents. This removes much of the fluidity of programs using the referents (notably, one must always have a reference available to the central repository!). And it erodes much of the value provided by the language's (somewhat) recently adopted gradual typing, generally borne of IDE aids, linters, and similar type-system-based programmer aids.

The class-body is a convenient mechanism for defining what Module is at bottom: a structured collection of these hardware attributes. Each Module's core data is a nested namespace of name-value mappings, one per each primary child HDL type, plus one overall namespace including their intersection. Conceptually Module is:

#### **@dataclass**

#### class Module:

```

ports: Dict[str, Signal]

signals: Dict[str, Signal]

instances: Dict[str, Instance]

instarrays: Dict[str, InstanceArray]

instbundles: Dict[str, InstanceBundle]

bundles: Dict[str, BundleInstance]

namespace: Dict[str, ModuleAttr] # Combination of all these

```

Where each Dict[str, X] is a mapping from a string name which is also an attribute of X. As such, Module doesn't really do all that much. (I.e. it doesn't have many methods, and is almost "plain old data".) Module includes only two API methods: add and get. Both operate on its namespace of HDL attributes. Addition places attributes into their associated type-based container, after checking them for valid types and naming. Module.get simply

retrieves them by name. This structured arrangement of Module is nonetheless a central facet of the Hdl21 data model. Most code which processes it lies elsewhere, in hierarchical traversals performed by Hdl21's elaborators, PDK compilers, and other visitors.

Module has one more central feature, directly attributable to its host language's capability: its by-name dot-access assignments and references. Python allows types to define override methods for setting and getting attributes (\_\_setattr\_\_ and \_\_getattr\_\_) which Hdl21 uses extensively. These by and large route to Module.add and Module.get respectively. Their inclusion is nonetheless a central facet of what makes Hdl21 feel like a native, dedicated language. Designers accustomed to dedicated HDLs are generally familiar with making dot-access references, e.g. to hierarchical design objects. Hdl21 makes this a central part of the process of designing and constructing them. This is also a central motivation for why the Module API is so minimal. The intent is that module dot-accesses usually refer to HDL objects, i.e. they are named references to the signals, ports, instances, etc. that the module-designer has already added.

```

m = h.Module()

m.inp = h.Input() # __setattr__

m.add(h.Output(name="out")) # `m.add` is a method

print(m.get("inp").width) # As is `m.get`

print(m.out.width) # Most other `m.x`'s refer to its HDL objects

```

## Generators

Hdl21 Modules are (almost) "plain old data". The power of embedding Modules in a general-purpose programming language lies in allowing code to create and manipulate them. Hdl21's Generators are functions which produce Modules, and have a number of built-in features to aid embedding in a hierarchical hardware tree.

In other words:

- Modules are "structs". Generators are functions which return them.

- Generators are code. Modules are data.

Generators are python functions, or more specifically wrappers around Python functions which:

- Accept a single argument, by convention named params, which is an Hdl21 paramclass (covered in the next section). And,

- Return an Hdl21 Module

```

@h.generator

def MyFirstGenerator(params: MyParams) -> h.Module:

return h.Module()

```

Generator function bodies execute arbitrary Python code, and are free to do whatever they like: perform complex optimizations, make requests to HTTP servers, query process-technology parameters, and the like. Generators may define Modules either procedurally, via the class-style syntax, or with any combination of the two.

```

0h.generator

def MySecondGenerator(params: MyParams) -> h.Module:

0h.module

class MySecondGen:

i = h.Input(width=params.width)

return MySecondGen

0h.generator

def MyThirdGenerator(params: MyParams) -> h.Module:

# Create an internal Module

0h.module

class Inner:

i = h.Input(width=params.width)

# Manipulate it a bit

Inner.o = h.Output(width=2 * Inner.i.width)

# Instantiate that in another Module

@h.module

class Outer:

inner = Inner()

# And manipulate that some more too

Outer.inp = h.Input(width=params.width)

return Outer

```

## **Parameters**

Generators must take a single argument, by convention named params, which is a collection of hdl21.Param objects. Each Param includes a datatype field which is type-checked at runtime. Each also requires string description desc, forcing a home for designer intent as to the purpose of the parameter. Optional parameters include a default-value, which must be an instance of dtype, or a default\_factory function, which must accept no arguments and return a value of type dtype.

```

npar = h.Param(dtype=int, desc="Number of parallel fingers", default=1)

```

The collections of these parameters used by **Generators** are called param-classes, and are typically formed by applying the hdl21.paramclass decorator to a class-body-full of hdl21.Params:

```

import hdl21 as h

@h.paramclass

class MyParams:

# Required

width = h.Param(dtype=int, desc="Width. Required")

# Optional - including a default value

height = h.Param(dtype=int, desc="Height. Optional", default=11)

```

Each param-class is defined similarly to the Python standard-library's dataclass. The paramclass decorator converts these class-definitions into type-checked dataclasses, with fields using the dtype of each parameter.

```

p = MyParams(width=8, text="Your Favorite Module")

assert p.width == 8  # Passes. Note this is an `int`, not a `Param`

assert p.text == "Your Favorite Module"  # Also passes

```

#### A Note on Parameterization

Hdl21 Generators have parameters. Modules do not.

This is a deliberate decision, which in this sense makes hdl21.Module less feature-rich than the analogous module concepts in existing HDLs (Verilog, VHDL, and even SPICE). These languages support what might be called "static parameters" - relatively simple relationships between parent and child-module parameterization. Setting, for example, the width of a signal or number of instances in an array is straightforward. But more elaborate parameterization-cases are either highly cumbersome or altogether impossible to create. Hdl21, in contrast, exposes all parameterization to the full Python-power of its generators.

## Just what does h.generator... do?

One may wonder: just what is the difference between these two functions:

```

@h.generator

def IsGenerator(params: MyParams) -> h.Module:

m = h.Module()

# ... Add stuff to `m`

return m

```

```

# Same thing, without the `@h.generator` decorator

def NotGenerator(params: MyParams) -> h.Module:

m = h.Module()

# ... Add the same stuff to `m`

return m

```

In short, these are identical function definitions, one of which is decorated by h.generator and therefore wrapped in an h.Generator object. In truth, both can work just fine. Advanced usage in fact tends to mix and match the two, based on the typically (but not always) helpful aids provided by h.generator. The function IsGenerator is run as-is, without modification, by the h.Generator wrapper. The generator machinery adds a few facilities, with the general intent of embedding calls to IsGenerator in a hierarchical hardware tree.

First and foremost are two related tasks: naming and caching. In many use-cases Hdl21 ultimately expects to produce code in legacy EDA formats (Verilog, SPICE, etc) which lack the *namespacing* feature of popular modern programming languages. Moreover these formats tend to reject input in which a module is "multiply defined", even if with identical contents. This might, absent the h.generator's naming and caching facilities, generate problems for programs like so:

```

def G(params: Params) -> h.Module:

m = h.Module()

m.inp = h.Input(width=params.width)

return m

@h.module

class Top:

g1 = G(Params(width=1))

g4 = G(Params(width=4))

```

Here a function G which creates and returns a parametric Module is called twice to produce two parametrically different instances. A naive translation to SPICE-level netlist code might produce something like:

```

.subckt Top

xg1 g

xg4 g

.ends

.subckt g inp

.ends

* This is the problem case: two identically *named* modules

```

```

.subckt g inp_3 inp_2 inp_1 inp_0

.ends

```

Hdl21 generators provide a built-in naming facility for managing these conflicts. Generated modules are named by a few rules:

- If the returned module is anonymous, indicated by a None value for its name field, it is initially given the name of the generator function. This would be the case for a generator-version of the function G above.

- If the generator has a non-zero number of parameters, a string representation of the value of those parameters is then appended to the module name.

The process of uniquely naming each paramclass value similarly has a few rules:

- A small set of built-in Python types are denoted as "scalars". These include strings, built-in numeric types, and options (None-ables) thereof.

- If a parameter class is comprised entirely of scalars, naming attempts to produce a readable name of the form field1=val1 field2=val2, where each val is the string representation of the scalar value.

- If either (a) the parameter class includes non-scalar parameters, or (b) attempts to produce a readable name generate strings of greater than a maximum length, naming is instead done based on a hash of the parameter values. Keeping the unique name to a reasonable maximum length is again a constraint of the desire to export into legacy EDA formats, many of which feature fairly short maximum name lengths.

- Hash-based naming begins by taking a JSON-encoded serialization of the parameter values. This is then hashed using the MD5 hashing algorithm, with random seeding (generally used for security) disabled to enable deterministic naming across processes and runs. The 32 character hex digest is then used as the unique parameter-value name. Note the JSON serialization step cannot natively be performed by many possible parameter types, particularly compound objects. These include many Hdl21 objects which are often valuable as parameters e.g. Modules and Generators themselves. Hdl21 includes built-in "naming only" serialization for these objects, which is used in the hash-based naming process. This serialization is not intended to be used for any other purpose. It generally hashes (something like) the definition path of the object in question, with no regard for its contents. It therefore cannot be used for serializing those contents.

Examples of the unique naming process:

```

@h.paramclass

class Inner:

i = h.Param(dtype=int, desc="Inner int-field")

@h.paramclass

```

```

class Outer:

inner = h.Param(dtype=Inner, desc="Inner fields")

f = h.Param(dtype=float, desc="A float", default=3.14159)

i = Inner(11)

print(h.params._unique_name(i))

# "i=11"

o = Outer(inner=Inner(11))

print(h.params._unique_name(o))

# "3dcc309796996b3a8a61db66631c5a93"

```

Generator's second task, tightly related to unique-naming, is caching. Caching is most commonly used as a performance tactic, to avoid re-calculating lengthy and repeated computations. It serves this purpose for Hdl21 generators, especially complex ones. But its primary goal is elsewhere, again rooted in the desire to export legacy EDA formats with their lack of namespacing. Consider editing our prior example to make two *identical* calls to G:

```

def G(params: Params) -> h.Module:

m = h.Module(name="G")

m.inp = h.Input(width=params.width)

return m

@h.module

class Top:

g1a = G(Params(width=1))

g1b = G(Params(width=1))

```

Here the function G is called twice, and produces two modules each with identical internal content. The naive translation to SPICE-level netlist code might produce something like:

```

.subckt Top

xg1a g

xg2a g

.ends

.subckt g inp

.ends

* Same problem: two identically *named* modules

.subckt g inp

.ends

```

Note that while the modules returned by successive calls to G have identical *content*, they are nonetheless distinct objects in memory. Exporting both - particularly, the identical *names* of both - to legacy EDA formats would generally produce redefinition errors. Wherever possible, Hdl21 avoids producing identical modules in the first place. Each call to a Generator is logged and cached. Successive calls to the same function with identical parameter values return the same object. This ensures each generator-parameters pair produces the same module on each call.

Note the use of such caching places a constraint on generator parameters: they must be hashable to serve as cache keys. Most of Hdl21's built-in types, e.g. Module, Generator, and Signal, are built to support such hashing, generally on an "object identity" basis. This is of course not the case for all possible parameter values, including many common types such as the built-in list. Generators with such unhashable parameters can opt out of the caching behavior via a boolean flag to the generator decorator-function. These generators then take on responsibility for ensuring that each module produced has a unique name.