# Formal Specification and Verification of Secure Information Flow for Hardware Platforms

Kevin Cheang

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-224 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-224.html

August 11, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Formal Specification and Verification of Secure Information Flow for Hardware Platforms

by

#### Kevin Cheang

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Sanjit A. Seshia, Chair Professor Krste Asanović Associate Professor Alvin Cheung Professor Emeritus David L. Dill

$Summer\ 2023$

# Formal Specification and Verification of Secure Information Flow for Hardware Platforms

Copyright 2023 by Kevin Cheang

#### Abstract

Formal Specification and Verification of Secure Information Flow for Hardware Platforms

by

#### Kevin Cheang

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Sanjit A. Seshia, Chair

Hardware platforms, such as microprocessors and Trusted Execution Environments (TEEs), aim to provide strong memory isolation properties. However, in recent years, this has been shown not to be the case through hardware attacks such as the class of transient execution attacks. These attacks affect programs executing on widely-used microprocessor designs in our present-day devices. Although mitigations have been proposed, many have not been adopted and lack formal guarantees. As a result, security-critical applications have been conservative in using hardware platforms without some form of cryptographic approach for secure computation, despite the additional computational overhead. One approach to ensure safety for this class of attacks is to use formal methods to prove information flow properties. Yet, there is limited work in verifying attacks on hardware platforms that are heterogeneous in nature, namely those that contain hardware and software in the trusted computing base.

This thesis defines a notion of secure information flow for hardware platforms and proposes methods to formally verify non-interference-based properties efficiently using abstractions and composition. To accomplish the former, we formalize the trace property-dependent observational determinism property for capturing a new class of non-interference properties. This property is motivated by verifying transient execution attacks and the need for secure speculation. To enable efficient verification on hardware platforms, we introduce an efficient proof system, SymboTaint, and the formalism of information flow state machines to reason about secure information flow compositionally. Finally, we explore a complementary method to enforce secure information flow for general programs by relaxing the programming model of a family of TEE designs and by formally verifying them. This direction builds on top of existing abstractions of TEEs to provide memory isolation guarantees with an efficient memory-sharing scheme on TEEs through combined design and verification. Together, this provides a methodology for enforcing memory isolation for heterogeneous systems, where joint modeling and analysis of hardware and software have become imperative for security.

To my parents.

# Contents

| Co            | onter                                                | nts                                                                 | ii                                                 |  |  |  |  |  |  |  |

|---------------|------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|

| $\mathbf{Li}$ | st of                                                | Figures                                                             | iv                                                 |  |  |  |  |  |  |  |

| Li            | st of                                                | Tables                                                              | viii                                               |  |  |  |  |  |  |  |

| 1             | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5              | The Rise of Insecure Hardware Platforms                             | 1<br>1<br>3<br>6<br>9<br>10                        |  |  |  |  |  |  |  |

| 2             | Har 2.1 2.2 2.3                                      | Speculative Microprocessors                                         | 11<br>11<br>15<br>18                               |  |  |  |  |  |  |  |

| 3             | Sect 3.1 3.2 3.3                                     | Secure Information Flow with Formal Methods Secure Information Flow | 20<br>22<br>24<br>25                               |  |  |  |  |  |  |  |

| 4             | Trace Property-Dependent Observational Determinism   |                                                                     |                                                    |  |  |  |  |  |  |  |

|               | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8 | Introduction                                                        | 33<br>33<br>37<br>42<br>47<br>52<br>60<br>62<br>65 |  |  |  |  |  |  |  |

|   | 4.9    | Summary                                                         | 66  |

|---|--------|-----------------------------------------------------------------|-----|

| 5 |        | npositional Proofs of Information Flow Properties for Hardware- |     |

|   |        | ware Platforms                                                  | 68  |

|   | 5.1    | Introduction                                                    | 68  |

|   | 5.2    | Motivation                                                      | 70  |

|   | 5.3    | Security Model                                                  | 73  |

|   | 5.4    | The SymboTaint Proof System                                     | 76  |

|   | 5.5    | IFSMs: Operational Encoding of SymboTaint                       | 81  |

|   | 5.6    | Verifying Speculative Platforms with IFSMs                      | 84  |

|   | 5.7    | Case Studies                                                    | 86  |

|   | 5.8    | Discussion                                                      | 89  |

|   | 5.9    | Related Work                                                    | 90  |

|   | 5.10   | Summary                                                         | 90  |

| 6 | Des    | igning Secure and Efficient Trusted Execution Environments      | 92  |

|   | 6.1    | Overview                                                        | 92  |

|   | 6.2    | Motivation and Background                                       | 94  |

|   | 6.3    | Design Decisions: Memory Sharing in Enclave Platforms           | 96  |

|   | 6.4    | Formal Model of An Enclave Platform with Memory Sharing         | 100 |

|   | 6.5    | Formal Guarantee of Secure Remote Execution                     | 109 |

|   | 6.6    | Implementation in RISC-V Keystone                               | 114 |

|   | 6.7    | Evaluation                                                      | 115 |

|   | 6.8    | Discussion                                                      | 119 |

|   | 6.9    | Summary                                                         | 120 |

| 7 | Con    | aclusion                                                        | 121 |

| 1 |        |                                                                 |     |

|   | 7.1    | Summary of Contributions                                        | 121 |

|   | 7.2    | Future Work                                                     | 122 |

| B | ibliog | raphy                                                           | 125 |

# List of Figures

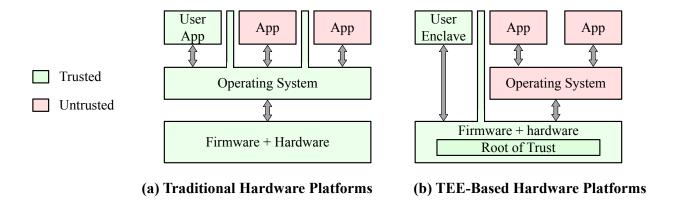

| 1.1 | User executing their application on a platform with untrusted applications and                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | the operating system                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1 | Example speculative microprocessor design [104] with a front-end component, the memory hierarchy, and an out-of-order engine. Arrows represent data flow from one state to another.                                                                                                                                                                                                                                                                                             |

| 2.2 | Stages of the Prime+Probe attack assuming a 4-way set associative cache. In the first stage, the attacker primes the cache by making memory accesses from their address space whose addresses map to the cache lines of a set. This invalidates all entries in a cache set. In the second stage, the victim executes, resulting in an evicted cache line. Finally, the attacker times the same memory accesses to determine information about which address the victim accessed |

| 2.3 | Stages of a speculative attack                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

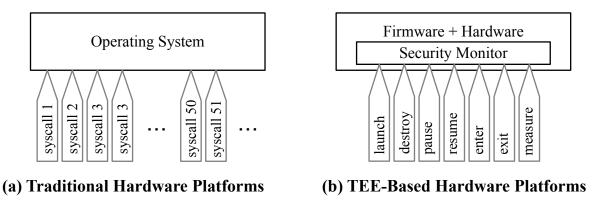

| 2.4 | Tradition hardware platforms vs. TEE-based hardware platform isolation boundaries represented by the vertical bars                                                                                                                                                                                                                                                                                                                                                              |

| 2.5 | The number of operations in the traditional hardware platform is comparatively more than that of the TEE-based hardware platforms.                                                                                                                                                                                                                                                                                                                                              |

| 3.1 | Formal verification allows one to prove that a system $M$ composed with adversary $\mathcal{A}$ either satisfies $\phi$ or not                                                                                                                                                                                                                                                                                                                                                  |

| 3.2 | Illustration of the assumptions and proof obligations for the non-interference property depicted by the execution of two traces of the system. The initial assumption of low equivalence is shown in blue ( $\approx_L$ ) and the proof obligation is shown in green ( $\approx_L$ )                                                                                                                                                                                            |

| 3.3 | Illustration of the assumptions and proof obligations for observational determinism. Low equivalence is checked at each intermediate state ( $\approx_{L}$ ) and assumed in the initial state ( $\approx_{L}$ )                                                                                                                                                                                                                                                                 |

| 3.4 | Victim program in C                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3.5 | Platform model in UCLID5                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.6 | Continued platform model in UCLID5 defining the victim program                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.7 | Continued platform model in UCLID5 defining the adversary observation                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.8<br>3.9<br>3.10<br>3.11 | Main proof module in UCLID5                                                                                                                                                                                                                             | 29<br>30<br>31<br>32 |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

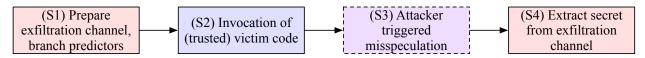

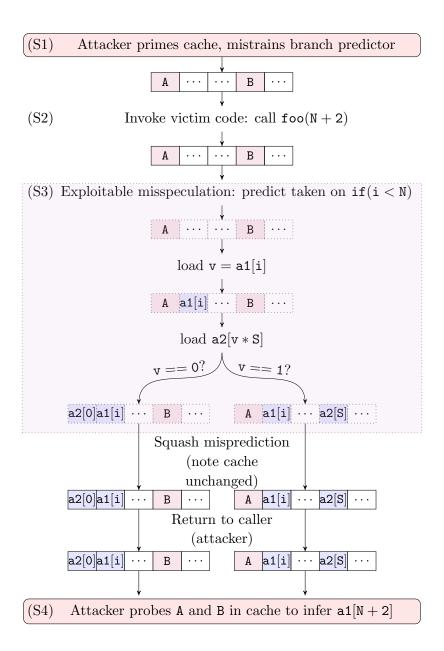

| 4.1                        | Four stages of a speculative execution attack. The execution of untrusted code is shown in red, while the execution of trusted code is in blue. We show the attacker-triggered misspeculation in the trusted code in the violet dotted box              | 37                   |

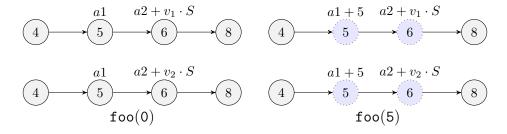

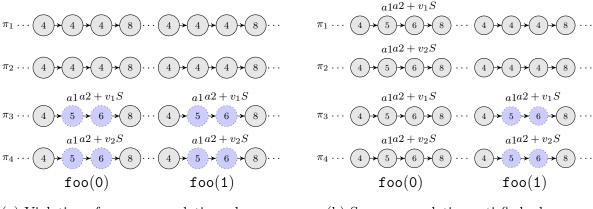

| 4.2<br>4.3                 | Spectre v1 vulnerability                                                                                                                                                                                                                                | 38                   |

| 4 4                        | code are blue. For simplicity, we show the attack on a direct-mapped cache                                                                                                                                                                              | 40                   |

| 4.4<br>4.5                 | Illustrative examples of fixes to vulnerable snippet in Figure 4.2                                                                                                                                                                                      | 41<br>41             |

| 4.6                        | Illustrating observational determinism in the context of the low attacker and high (trusted) program: low instructions are labeled $L$ , while high instructions are labeled $H_1$ and $H_2$ , proof obligations are shown in green and assumptions are | 41                   |

|                            | shown in blue                                                                                                                                                                                                                                           | 44                   |

| 4.7                        | Illustrating the strawman observational determinism property for Figure 4.2. Numbers within each state refer to program counter values (shown as line numbers). Labels above each state indicates the data memory address accessed (if                  |                      |

| 4.8                        | any). States shown in dotted circles are specuative states                                                                                                                                                                                              | 44                   |

| 4.9                        | proof obligations are shown in green and assumptions are shown in blue The Assembly Intermediate Representation (AIR). $\Diamond_u$ and $\Diamond_b$ are typical unary                                                                                  | 45                   |

|                            | and binary operators respectively                                                                                                                                                                                                                       | 49                   |

| 4.10                       | Semantics of expression evaluation                                                                                                                                                                                                                      | 49                   |

|                            | Operational Semantics for Statements in AIR                                                                                                                                                                                                             | 50<br>57             |

| 4.13                       | Example 1: Original Spectre BCB (bounds check bypass) example                                                                                                                                                                                           | 62                   |

|                            | Example 5: BCB with a for loop                                                                                                                                                                                                                          | 63                   |

| 4.15                       | Example 7: BCB with unsafe static variable check                                                                                                                                                                                                        | 63                   |

|                            | Example 8: BCB with the ternary conditional operator                                                                                                                                                                                                    | 63                   |

| 4.17                       | Example 10: BCB using an additional attacker-controlled input                                                                                                                                                                                           | 64                   |

| 4.19 | Example 11: BCB using the memory comparison function                                                                                                                                                                                                                                                                                                                                                                         | 64<br>64   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.1  | Victim program executing in the trusted user's domain with input x which is adversary controlled. This function is vulnerable to Spectre V1 (BCB), Spectre V4 (store-bypass), their combination and leakage from segment B                                                                                                                                                                                                   | 71         |

| 5.2  | Instruction level translation of lines 4-6 of the program in Figure 5.1                                                                                                                                                                                                                                                                                                                                                      | 71         |

| 5.3  | Different levels of modeling detail                                                                                                                                                                                                                                                                                                                                                                                          | 72         |

| 5.4  | A simple platform model                                                                                                                                                                                                                                                                                                                                                                                                      | 74         |

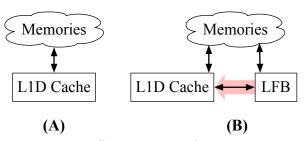

| 5.5  | Information flow in the Lazy-FP vulnerability                                                                                                                                                                                                                                                                                                                                                                                | 75         |

| 5.6  | Modified platform model from Figure 5.4 with a partitioned cache                                                                                                                                                                                                                                                                                                                                                             | 78         |

| 5.7  | Proof rules for joint symbolic-taint judgments                                                                                                                                                                                                                                                                                                                                                                               | 80         |

| 5.8  | CPU, cache, and branch prediction components of the SAP model                                                                                                                                                                                                                                                                                                                                                                | 84         |

| 5.10 | Branch prediction in the SAP model                                                                                                                                                                                                                                                                                                                                                                                           | 85         |

| 5.9  | Continued cache model from Figure 5.6 with the load operation and guard                                                                                                                                                                                                                                                                                                                                                      | 85         |

| 5.11 | Program composed with the SAP model                                                                                                                                                                                                                                                                                                                                                                                          | 86         |

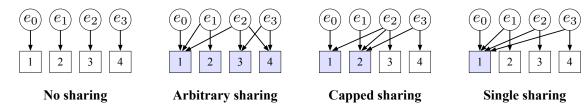

| 6.1  | Memory sharing models with varying flexibility. Blue (and white) boxes indicate shareable (and non-shareable) physical memory regions, and circles indicate enclaves. An edge from an enclave to physical memory is an <i>access relation</i> stating that an enclave can access the memory it points to. The figure only depicts cases where the number of memory regions $m$ is the same as that of enclaves $n$ , but $m$ |            |

| 6.2  | can be greater than $n$ in practice                                                                                                                                                                                                                                                                                                                                                                                          | 97         |

|      | and objZ are the large libraries or objects that enclaves want to share. Enclave 10 and 11 relies on libX and libY, while Enclave 12 relies on libY and objZ.                                                                                                                                                                                                                                                                | 98         |

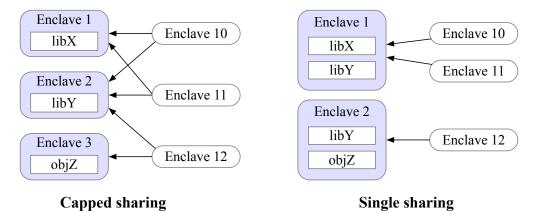

| 6.3  | A user provisions their (protected) enclave $e$ in the remote enclave platform iso-                                                                                                                                                                                                                                                                                                                                          | <i>J</i> C |

| 0.0  | lated from untrusted software. Green/red boxes indicate trusted/untrusted com-                                                                                                                                                                                                                                                                                                                                               |            |

|      | ponents                                                                                                                                                                                                                                                                                                                                                                                                                      | 101        |

| 6.4  | Illustrating the execution of two traces of the platform in the secure measurement, integrity and confidentiality proofs. Proof obligations for each property are checked as indicated by $\approx_{\mathcal{L}}$ and equal initial condition indicated as $\approx_{\mathcal{L}}$ . $op^i$ indicates enclave execution of an operation from $\mathcal{O}$ at step $i$ and $\mathcal{A}$ indicates an                        |            |

|      | adversary execution                                                                                                                                                                                                                                                                                                                                                                                                          | 106        |

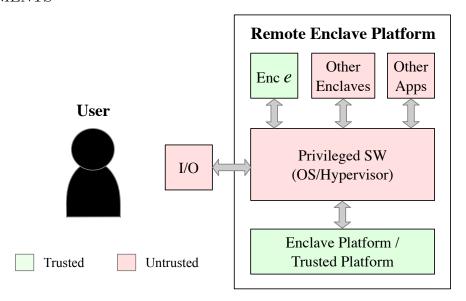

| 6.5  | The physical memory layout of the three scenarios: using (a) Snapshot-only, (b)                                                                                                                                                                                                                                                                                                                                              | - 0        |

|      | Clone-only, and (c) Clone-after-Snapshot. Each column represents a region of memory allocated to enclave $e_0$ , enclave $e_1$ , or the operating system (OS). Each region either respects the permissions based on the regular platform semantics or                                                                                                                                                                        |            |

|      | is snapshot memory which is writable only using the copy-on-write scheme                                                                                                                                                                                                                                                                                                                                                     | 107        |

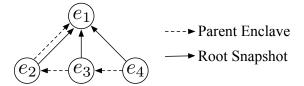

| 6.6  | Parent-child relationship and root snapshot-child relationship of four enclaves in       |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | Cerberus. Enclave $e_1$ is a snapshot and the parent enclave of $e_2$ , which is the     |     |

|      | parent of $e_3$ , which is the parent of $e_4$ . Despite the nested parent relationship, |     |

|      | the root snapshot of $e_2, e_3$ , and $e_4$ are $e_1, \ldots, e_4$                       | 110 |

| 6.7  | Model Statistics and Verif. Times                                                        | 116 |

| 6.8  | C code to measure fork latency                                                           | 117 |

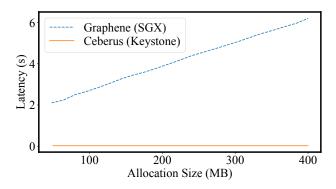

| 6.9  | The latency of fork with respect to the size of the allocated memory                     | 117 |

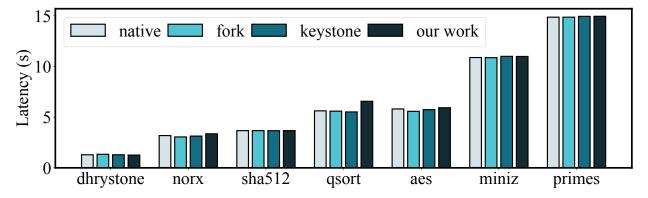

| 6.10 | Computation Overhead on RV8. native: native execution of the original RV8,               |     |

|      | fork: native execution of the modified RV8 with fork, keystone: enclave execu-           |     |

|      | tion of the original RV8, and our work: enclave execution of the modified RV8            |     |

|      | with Cerberus.                                                                           | 118 |

# List of Tables

| 4.1 | find vulnerabilities and 1 step induction to prove correctness after inserting a memory fence. These experiments were run on a machine with an 2.20GHz Intel(R) Core(TM) i7-2670QM CPU with 5737MiB of RAM                                              | 65  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.1 | The execution column indicates whether the adversary is allowed to execute asynchronously or only before and after the victim program (at entry points). $V_O$ , $V_T$ and $F$ represent the observable states, tamperable states and the flow transmit |     |

|     | pairs (§5.3.2) of the adversary                                                                                                                                                                                                                         | 87  |

| 5.2 | Time (in seconds) to verify OD using the 2-safety encoding with BMC, the trace property encoding of OD (TOD) with BMC and TOD with interpolants. Examples are checked using UCLID5, and marked with TLE (time limit exceeded) if it                     |     |

|     | takes longer than 15 minutes                                                                                                                                                                                                                            | 88  |

| 6.1 | $\mathrm{TAP}_C$ State Variables $V.\ldots\ldots\ldots\ldots\ldots\ldots$                                                                                                                                                                               | 104 |

| 6.2 | Record of TAP <sub>C</sub> enclave metadata $\mathcal{E}_M$ . Additional state variables were added to                                                                                                                                                  |     |

|     | the TAP model support Snapshot & Clone, as indicated by the † superscript                                                                                                                                                                               | 105 |

#### Acknowledgments

Throughout the years, I have had the privilege of crossing paths with numerous researchers, mentors, and individuals, each of whom added unforgettable moments to my life. Whether it was chatting with colleagues both inside and outside the office, pulling countless all-nighters alongside my co-authors and classmates, having discussions with researchers at conferences and workshops, or simply spending time with friends who were always there for me, each one of them contributed to my growth and filled my life with an overwhelming amount of gratitude and meaning. It is only proper that I express my gratitude to everyone who played such a significant role, that ultimately led to this monumental moment in my life.

First and foremost, I thank my advisor Sanjit A. Seshia, for his life-changing guidance and support, for which I am eternally grateful. Among the myriad of things that he has done for me, there are a few that stand out that I would like to acknowledge here. When I first entered the lab, I was a rather reserved individual. Sanjit immediately took note of this with empathy, and over the years, he consistently encouraged me to engage with fellow researchers, taught me how to promote my research and emphasized its importance, and gave me opportunities that propelled my growth as a researcher and on a personal level. I feel very fortunate to have worked with Sanjit and give him my deepest gratitude. I also thank the other members of my qualifying exam and thesis committee for providing invaluable guidance along the way: Krste Asanović, Alvin Cheung, and David Dill.

I thank my co-authors, all of whom I had a great deal of pleasure working with. First, I thank Pramod Subramanyan. From his contributions to the formalism of *TPOD* and development of UCLID5, to all the graduate student advice he gave me when I first started, his influence is what made much of my research possible. I thank Cameron Rasmussen, Pranav Gaddamadugu, Dayeol Lee, and Adwait Godbole for all the intellectually stimulating conversations and fruitful discussions that led to a lot of writing, paper submissions, conferences, and never-ending laughter. I also thank the folks in the UCLID5 team for all UCLID5 related collaborations: Federico Rocha, Elizabeth Polgreen, Yatin A. Manerkar, and Shaokai Lin. I also need to thank many of my lab mates (who were not already mentioned above), Ben Caulfield, Tomasso Dreossi, Daniel Fremont, Shubham Goel, Markus Rabe, Sumukh Shivakumar, Edward Kim, Shiv Kushwah, Hazem Torfah, Marcell Vazquez-Chanlatte, Sahil Bhatia, Pei-Wei Chen, Niklas Lauffer, Shaokai Lin, Ameesh Shah, Victoria Tuck, Justin Wong, and Beyazit Yalcinkaya, for making my time in the office *never* a dull moment.

During the course of my time here, I was also fortunate to have met many great industry mentors and colleagues that have given me indispensable graduate student advice while also teaching me a vast amount in my research area. From my internships at Facebook/Novi, I thank David Dill (again), Shaz Qadeer, Clark Barrett, Wolfgang Grieskamp, Evan Cheng, Sam Blackshear, and Jingyi Emma Zhong. From my internship at Intel, I thank Robert Jones and Amit Goel. I also extend my gratitude to the folks at Intel who provided insightful feedback on my work in our monthly meetings.

Naturally, I could not have done this without the folks back at home. I thank my parents for the countless sacrifices they made over the decades and for their unwavering

support which helped pave the way for this moment. I also thank my brother for taking care of our parents while I was away for all these years. Additionally, I owe a debt of thanks to Alan J. Hu and Mark R. Greenstreet, as it was their initial support and encouragement that led me to start my journey here at Berkeley.

Finally, to all the individuals (including those unnamed for the sake of privacy) who have blessed me with the strength to persevere through this degree, thank you.

# Chapter 1

# Introduction

#### 1.1 The Rise of Insecure Hardware Platforms

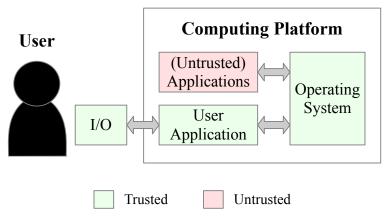

Hardware platforms such as the microprocessors in our phones, laptops, and web servers, aim to provide strong memory isolation guarantees to protect a user's confidential data from being leaked to untrusted entities (Figure 1.1). For example, a user interacting with a web application from their phone would involve using an input/output (I/O) interface to control how their application executes and responds. In this interaction, the user may provide sensitive data to their application such as credit card numbers or information about their identity. Naturally, a user would hope that untrusted entities executing on the same hardware platform, such as other applications, are unable to infer any information about their confidential data. However, the discovery of a number of hardware-based security flaws—in particular, transient execution vulnerabilities such as Spectre [116] and Meltdown [133]—in widely-used present-day microprocessors, has raised major security concerns about the memory isolation guarantees between programs running on these platforms. If we are

Figure 1.1: User executing their application on a platform with untrusted applications and the operating system.

not careful, untrusted entities that share the platforms where we store our data have the potential to exploit these newly found attack vectors in order to gain access to our confidential information.

One approach to counter these attacks is by using formal methods to establish formal proofs of memory isolation on the platform. Formal methods is an area of computer science that relies on rigorous mathematical proofs to provide system correctness through specification, modeling, and verification. Over the last several decades, formal methods have made great advances in becoming practical and have become extensively used in the industry for proving system correctness. One prominent technique in formal methods is model checking, which is used to mechanically prove properties about finite state machines. We refer to these proofs as formal guarantees, which is often a reliable measure of system correctness.

Unfortunately, it is becoming increasingly difficult to ensure that hardware platforms are secure due to their growing complexity. To exacerbate the situation, new vulnerabilities are discovered every year, requiring non-trivial changes to the hardware platform [63] in order to protect against new attacks. Even without the added complexity, formal guarantees of security such as memory isolation for hardware platform designs often lag years behind their commercial releases. The reason for this lies predominantly in the reliance on manual effort when applying formal methods to hardware platform designs, as exemplified by work such as seL4 [114] and Komodo [70]. It is immensely challenging and costly to manually apply formal verification to a hardware platform because of the sheer size of the design.

On the other hand, secure computation on secure hardware platforms [53, 101, 112, 127, 141, 161, 200] has been of growing interest for security-critical applications in recent years. For instance, machine learning inference models [91], blockchain technology [67, 232, 234], and serverless computing [71, 160] have become ubiquitous, and many of these applications require a high degree of confidentiality for the underlying data used for computation. These applications execute on hardware platforms and require that they provide strong memory isolation guarantees. Unfortunately, the only viable hardware platforms that we can rely on to provide memory isolation have become a prime target for transient execution attacks and more generally, what we refer to as hardware attacks [29, 116, 133, 174, 186, 189, 215, 216, 224, 225]. As a result, the gap between the demand for secure hardware platforms and the actual level of security provided has been widening. This has led to a noticeable disparity that leaves security-critical applications with no other option but to resort to less performant alternatives for enforcing memory isolation, such as cryptographic-based methods [74].

Mitigations proposed [89] for hardware attacks have mostly been hardware- or software-based, yet there is a barrier to adoption. Hardware mitigations are often regarded as too intrusive and vulnerability-specific. On the other hand, the security of software mitigations depends on the hardware it runs on. This frequently leads to platform-specific software mitigations (e.g., using x86 serializing instructions [102]) and warrants more precise analysis that includes details about the hardware, which are often lacking in many analysis methodologies. In addition, new side-channel attacks [40] have repeatedly found a way to circumvent proposed mitigations. Time has proved that this class of attacks is difficult to overcome with hardware- and software-based mitigations alone.

Alternatives to secure computation include cryptographic-based alternatives and hardware-based isolation techniques. The former includes techniques such as secure multi-part computation and homomorphic encryption, however, these techniques have been shown to be computationally expensive, even with hardware accelerators [182]. On the other hand, hardware-based isolation techniques implemented by platforms such as *trusted execution environments* (TEEs) [52, 53, 127] have been of growing research interest [67] to the community as they are more performant. Unfortunately, they lack maturity in feature richness and assume a very restrictive programming and memory-sharing model which severely limits usability.

The culmination of these barriers to secure computation on hardware platforms leads to one possible solution: to develop and improve existing formal techniques that can provide hardware platforms with formal guarantees in a practical manner. However, this direction comes with major challenges that we discuss in the next section. Broadly speaking, with the current advances in secure computation technology and the discovery of new vulnerabilities, the *trusted computing base* of hardware platforms, the part of a system that is critical to security, has grown to include both software and hardware components. We refer to these mixed component systems as *heterogeneous* systems, which because of their complexity, are inherently difficult to both model and analyze using traditional methods.

For the remainder of this chapter, an overview of the problems addressed in this thesis is presented. Specifically, section §1.2 discusses the formal methods-based approaches used and section §1.3 outlines the challenges of applying formal methods to hardware platforms. Section §1.4 presents the thesis statement and summarizes the contributions of this thesis. Lastly, we conclude with acknowledgments in section §1.5 to thank those who have funded my work and played a crucial role in making this research possible.

### 1.2 Secure Information Flow

The security of hardware platforms relies on a core component that defines the behavior of the software programs that they execute: the microprocessor. To safeguard against the attacks mentioned earlier using formal methods, we need to both model and verify properties defined over microprocessor designs. Specifically, we target speculative microprocessor and TEE models where strong memory isolation is essential. To get a better sense of how one can model these platforms and use them to prove memory isolation, it is important to understand the types of components in these systems that are exploited and how they are exploited in hardware attacks to even bypass the more resilient security measures.

Microprocessors and TEEs are types of heterogeneous systems that rely heavily on both software and hardware for security. Perhaps unsurprisingly, hardware attacks exploit both of these components of the platform to leak secrets, explaining the elusiveness of these vulnerabilities. For instance, in transient execution vulnerabilities, a microprocessor implements speculative features to increase throughput, but these features inadvertently cause unintended executions of instructions that lead to secrets being leaked to covert channels such as the data cache. Clearly, proof of memory isolation needs to include the cache along with the

exploited program. Similarly for TEEs, even though they rely on specialized hardware to enforce memory isolation, speculation can be exploited to break security [215, 224]. Thus, in addition to the exploited components in a microprocessor model, one also needs to consider the hardware mechanisms specific to TEEs that are used to strengthen memory isolation.

Integrating both hardware and software components into a single model requires them to share the same programming model. As a result, a significant challenge in formalizing a hardware platform model is precisely defining this unified programming model. First, one needs to determine the level of abstraction at which the models are described at. Ideally, the abstraction level should be capable of describing both the hardware and software components being exploited. For instance, one such level of abstraction is the instruction level. Second, one needs to determine the operations of the model and the granularity at which they execute to change the system state. For example, updates to hardware components are typically driven by a clock signal that concurrently and atomically updates the components connected to that clock signal. On the other hand, software does not have a notion of a clock signal and thus the atomicity of program execution that should be modeled is less obvious. In light of these differences, it is natural to consider a transition system-styled model in which each atomic operation of the system can be chosen to suit the assumptions of the application and the associated attacker model. The work presented in this thesis assumes this modeling style. We now turn to the type of attacker model needed to model these attacks and the security properties we need to prove.

A general attacker model. The rate of discovery of new vulnerabilities is concerning as it has implications for the attacker model. Historically, attacker models have been fixed for a given vulnerability of a hardware platform. However, this approach has proven to be increasingly limited in its productivity and effectiveness. Often, checking for the security of a single adversary model is not sufficient for sound guarantees of security on a hardware platform. To scale, we must consider models that are parameterized and allow us to capture classes of attacks. For that reason, the attacker models considered throughout the thesis is one that is general and has the following two major characteristics. One, we assume that it can execute an unbounded number of steps whenever the platform allows it to execute. Two, we assume that it has access to an abstract observation function and tamper function which defines the components that it can observe and modify when it executes.

Enforcing secure information flow. Finally, in order to verify memory isolation for hardware platforms, it is necessary to prevent any information leakage from secret states to observable states, irrespective of the adversary's actions. One way to capture this notion of security is by using the standard *non-interference* [76] security property based on information flow. Non-interference is used to restrict the information flow of a system; it states that a group of users executing a set of commands on a system does not affect what another group of users (on the same system) can see. This thesis presents extensions of the non-interference

property, which we collectively refer to as secure information flow (SIF). We will describe these properties briefly in Chapter §2.3 and define them formally in Chapters §4, §5 and §6.

#### 1.2.1 A Workflow that Guarantees Secure Information Flow

While we have already mentioned the applications that motivate our work, the central focus of this thesis is really motivated by the vision of a workflow that provides secure information flow of programs executing on hardware platforms. Naturally, explaining this workflow will provide insight into the research directions of our work.

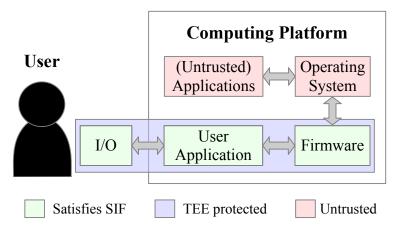

The workflow begins with the consideration of using a prominent hardware platform that aims to enforce memory isolation without incurring a large performance penalty: trusted execution environments. TEEs use hardware primitives to ensure that enclave program memory is protected from untrusted entities executing on the platform. Examples of TEEs include Intel SGX [141] and Trust Domain Extensions [101], ARM TrustZone [10], Keystone [127], MIT Sanctum [53], and AMD SEV [112], many of which exist in the processors of major computer hardware manufacturers. However, existing TEEs have been discovered to be vulnerable to various side-channel attacks such as Foreshadow [215, 224]. Moreover, TEEs have a restrictive programming model that limits how they can share memory. Without memory sharing, enclave programs are very limiting for typical user applications. Thus, it is crucial that these issues are first addressed for the widespread adoption of TEEs. This leads us to the following observation. If we have a methodology to prove that a class of enclave programs is protected against hardware attacks (i.e., by proving SIF) and if we can extend the functionality of enclaves to capture a wider family of applications, then TEEs can become a practical approach for enforcing memory isolation of more general applications. This is depicted in Figure 1.2.

Figure 1.2: Application protected by the TEE and formal guarantees of secure information flow.

To better understand the complexity of developing such a methodology and extending TEEs securely, we describe the models needed to prove SIF on such a workflow in more detail.

At the core of these hardware platforms, there is an architectural model that describes how the platform state evolves at a functional level as it executes. However, the extent of security that a purely architectural model can provide is limited to functional correctness. Naturally, it is not unless we also consider the other component of the heterogeneous system — the implementation-based microarchitectural model — that we can reason about hardware-based attacks such as transient execution vulnerabilities. Below, we discuss some key aspects that should be taken into account when verifying hardware platforms.

**Microprocessors.** A microprocessor design consists of the computer architecture, on which an instruction set architecture (ISA) [9, 103, 221, 222] is used to define the semantics of how a program controls the CPU and the microarchitecture which implements these semantics. Historically, methodologies have often focused on verifying the functional correctness of microprocessor designs [36, 70, 199] and thus only modeled the architectural state of a microprocessor. However, with transient execution attacks, new formal models of processors have been increasingly microarchitecture-aware [45, 125, 153, 204]. Microarchitectural buffers and caches such as the pattern history table, page tables, reorder buffer, translation lookaside buffer, caches, store, and load buffers have become intrinsic to the formal analysis of hardware platform security, and there is an increasing trend toward unifying program semantics and hardware behavior as a monolithic model. As one can imagine, direct translations or implementation-accurate models of hardware implementations in hardware description languages (HDL) such as RTL or Verilog are often too complex and requires complete remodeling whenever the hardware design is changed. Thus, our work considers a middle-ground model that abstractly models microarchitectural components. This allows the model to capture a class of microarchitectures while also being amenable to changes due to its simplicity. As a transition system, this translates to modeling each instruction from the ISA as an operation that atomically updates the architectural and microarchitectural components according to the ISA semantics and hardware design.

Trusted execution environments. Instead of relying on the operating system to isolate memory, a trusted execution environment provides a set of operations for users to manage and execute their *enclave* program within a protected area of the platform [10, 101, 127, 141]. From a modeling standpoint, one may extend the microprocessor model described above to execute the set of enclave operations. Similar to microprocessors, enclave platforms modeled without hardware components have left it open to speculative attacks [215].

## 1.3 Challenges

As alluded to in the previous section, verifying non-interference properties on hardware platforms presents several challenges. To better understand these challenges, it is useful to examine the desired characteristics of a formal approach that checks non-interference on

hardware platforms against a class of attacks. Three key requirements emerge in verifying these platforms: accuracy, reusability, and scalability. Accuracy is needed to precisely explain the underlying cause of a vulnerability, while reusability and scalability allow an approach to adapt to changes and scale to realistic problems. While we desire our approach to incorporate these aspects, it is challenging to have all three. Thus, the crux of this thesis is also about finding the right balance of abstractions and developing techniques to satisfy these requirements for hardware platforms.

#### 1.3.1 Accuracy

Accuracy is imperative to any formal approach. We refer to two types of accuracy in an approach. The first type of accuracy is about precisely capturing the desired property, such as the class of attacks or vulnerabilities. The second type refers to the soundness and completeness of the procedures used to determine security.

Formalizing secure information flow. Proving security requires one to first define a security criterion. The first part of this criterion is the attacker model. The second and more subtle part is how one specifies a property to capture the vulnerabilities or attacks of interest. For example, checking that a program satisfies non-interference is not as informative as checking for a violation of non-interference due to optimizations in a platform. A more informative property is desirable because it can more precisely capture and explain the violation of a given property. In addition, the standard non-interference property is often too strong to be practically enforced and is violated by most programs whether or not they are vulnerable to hardware attacks.

Soundness and Completeness. As in any standard decision procedure for determining the security of a system, we require soundness at a minimum, which states that if the procedure says the system is secure, then the system is truly secure. While soundness is necessary and fundamental in our approaches, an approach is only practical when it has a minimal number of false positives. That is, it cannot be too overapproximate and return an excessive number of incorrect results. Overly abstract models in formal verification, for instance, are often prone to resulting in false positives. Thus, one challenge of writing abstractions is determining the right level of detail. Conversely, completeness states that the procedure returns an answer whenever one exists. We acknowledge that while completeness is desirable, this thesis does not address this aspect.

### 1.3.2 Reusability

With the rapidly growing number of hardware attacks discovered every year and the growing complexity of the systems on which they exploit, an approach needs to be reusable and scale to the growing pace of the system. These challenges can be alleviated by considering parameterizability and automation.

Parameterizability. In writing models, we must also consider how various hardware attacks can be expressed because the security of a hardware platform design (e.g., a microprocessor [108]) is dependent on the individual components and optimizations implemented. Ideally, formalisms are defined in a way that allows models to check a range of attacks beyond a single variant that it was designed for so they can be reused whenever there are slight changes to the attack vector or design. Thus, modeling and specification formalisms should be compositional and easily parameterizable. Additionally, this would allow the models to adapt to new changes, which is crucial for formal models that would often take an expert, months to write.

**Automation**. While parameterizability enables us to scale to a range of attacks and platforms, automation is typically necessary to maintain the usage of the approach practically. Hardware platforms contain thousands of lines of code at a minimum, either as firmware or as part of the application that we are verifying. As a result, our approaches should ideally automatically generate models and proofs from the implementation.

### 1.3.3 Proof Scalability

Lastly, parameterizability brings issues with proof scalability because of the complexity of the platform. This is commonly addressed through model abstraction and compositional reasoning.

Reducing model complexity with abstraction. Formal models can still be fragile when used with state-of-the-art formal method-based engines, which may not always terminate. A model of a complex system must have the right level of abstraction. For starters, this can help alleviate the modeling effort required to compose different components of a system together. Determining which parts of the model to abstract away is also important for reducing the runtime of these engines [32, 33]. Second, the encoding of these models needs to be efficient. Formal models are often written as logical formulas in Satisfiability Modulo Theories [17, 18] (SMT). The SMT problem is the problem of determining whether a given logical formula is satisfiable. This problem is solved in practice by using SMT solvers, which are often used in formal method engines [57, 129, 169]. The formulas compiled from the security questions we ask, often contain a range of theories in SMT and can have alternative encodings that are equivalent or approximate, each of which can vary drastically in runtime when given to the solvers. As such, an efficient encoding [30, 177, 211] with a suitable logic or set of theories for complex models is imperative in preventing state explosion and avoiding undecidable logical encodings [27]. We acknowledge that there is an obligation to check that the abstract model is a sound abstraction of the implementation model [49], however, this is not within the scope of this thesis.

Scaling proofs by composition. Lastly, the method of proof needs to be efficient. For example, executing bounded model checking on a large model will likely result in state explosion for symbolic model-checking techniques. Thus, designing a methodology that can take advantage of assumptions and security criteria to construct compositional proofs is often necessary to scale to realistic programs.

To that end, we present the thesis statement and a list of contributions that overcome these challenges to address the problems presented in §1.1. Through this thesis, we aim to take a step towards realizing what we can call *secure hardware platforms*.

#### 1.4 Thesis Statement

We develop methodologies to prove secure information flow by formalizing abstract models of hardware platforms, formalizing trace property-dependent observational determinism to precisely capture classes of hardware attacks, and introducing an interpolant-based proof methodology to efficiently verify heterogeneous systems against hardware attacks.

#### 1.4.1 Contributions

A summary of the research contributions to address this thesis statement includes the following:

- 1. Chapter §2 provides background on secure hardware platforms and the applications of this thesis.

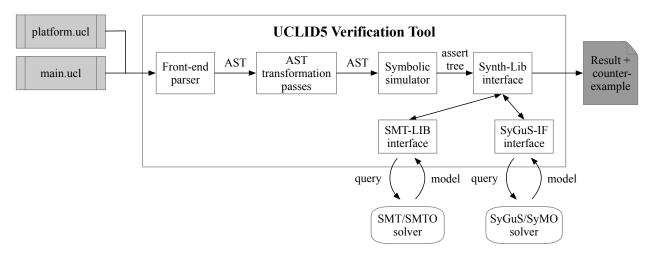

- 2. Chapter §3 provides background on the general approaches used, relevant concepts from formal methods, and a primer for the verification toolkit used throughout this thesis, UCLID5 [169, 193].

- 3. Chapter §4 presents the *secure speculation* property, used to capture information flow leaks caused by transient execution attack vulnerabilities. Furthermore, we generalize this property as *trace property-dependent observation determinism*.

- 4. Chapter §5 generalizes the approach from the previous chapter to efficiently verify information flow-based properties using the *SymboTaint* proof system and *information flow state machines*.

- 5. Chapter §6 returns to the problem of hardware-based secure computation and provides a methodology for combined design and verification of secure and efficient trusted execution environments.

- 6. Chapter §7 concludes with discussions about the existing work and future directions.

## 1.5 Acknowledgements

Over the years I have had the honor of publishing work with collaborators who have been immensely helpful, insightful, and a pleasure to work with. This thesis is a compilation of these works that we wrote together jointly. In this section, I describe their contributions and acknowledge the sources of funding which made this thesis possible.

#### 1.5.1 Collaborative Work

Chapter §3 presents a primer to UCLID5 and is partially based on the paper "UCLID5: Multi-Modal Formal Modeling, Verification, and Synthesis" [169], which is a joint contribution with Elizabeth Polgreen, Pranav Gaddamadugu, Adwait Godbole, Kevin Laeufer, Shaokai Lin, Yatin A. Manerkar, Federico Mora, and Sanjit A. Seshia who designed and developed the UCLID5 verification tool, whose initial version were created by Pramod Subramanyan and Sanjit A. Seshia [193].

Chapter §4 is based on "A Formal Approach to Secure Speculation" [46]. Cameron Rasmussen contributed by having countless discussions with me and by helping out with the experiments. Pramod Subramanyan contributed by proposing TPOD, in addition to providing lots of guidance and feedback with Sanjit A. Seshia.

Chapter §5 is based on "Compositional Proofs of Information Flow Properties for Secure Platforms" [44]. Adwait Godbole contributed by having countless discussions with me and by helping formalize the SymboTaint proof system and information flow state machines. Yatin A. Manerkar and Sanjit A. Seshia contributed by providing invaluable guidance and feedback throughout this project as well.

Chapter §6 is based on "Cerberus: A Formal Approach to Secure and Efficient Enclave Memory Sharing" [125]. Dayeol Lee contributed by having countless discussions with me, designing Cerberus, and implementing it in Keystone. Pranav Gaddamadugu contributed by translating the TAP model from Boogie to UCLID5 and attempting to formally verify the initial version of Cerberus [72]. Alexander Thomas and Catherine Lu for making significant contributions to the experimental sections and the implementation of Cerberus. Anjo Vahldiek-Oberwagner, Mona Vij, Dawn Song, Sanjit A. Seshia, and Krste Asanović contributed by providing invaluable guidance and feedback.

### 1.5.2 Funding

The research described in this thesis was supported in part by SRC tasks 2867.001 and 2854.001, the iCyPhy Center, NSF grants CNS-1739816 and CNS-1646208, the Science and Engineering Research Board, a gift from Microsoft Research, the Qualcomm Innovation Fellowship, Amazon, Intel under the SCAP and Scalable Assurance program, and by RISE, ADEPT, and SLICE Lab industrial sponsors and affiliates.

# Chapter 2

# Hardware Platforms

Hardware platforms consist of many layers, from the I/O layer and networking layer to data buses and individual hardware intellectual properties, but the core component that is generally responsible for security is the microprocessor that executes the application software on our devices. Consequently, our primary focus is *soley* directed towards ensuring security for microprocessor-based designs. Although microprocessor security has been extensively studied, it wasn't until recently that reasoning about hardware and software together has become more conventional for security [135, 204, 209] on hardware platforms. In this section, we provide background for microprocessor models and TEE models to illustrate how modeling has changed, the vulnerabilities of the respective platforms, and briefly discuss the attacker models.

# 2.1 Speculative Microprocessors

Ever since processors began to adopt out-of-order execution, speculation, and superscalar optimizations [164, 195, 200], microprocessors became increasingly complex. We describe this complex architecture below and explain how it has become increasingly vulnerable over the years.

### 2.1.1 Breaking Down The Microprocessor Design

A microprocessor design can be thought of as a dyadic of abstraction layers: the architectural and the microarchitectural designs. The former can be used to describe how a program is computed and the latter how the underlying computation engine is implemented. We describe each of these layers below.

Architectural design. A microprocessor is designed to adhere to what is called the architectural model, which includes a set of registers such as the program counter, general purpose integer registers, control status registers, and floating point (FP) registers, in addi-

tion to an *instruction set architecture* (ISA) [9, 11, 103] that defines the semantics of how these registers change values as an instruction executes through the processor pipeline.

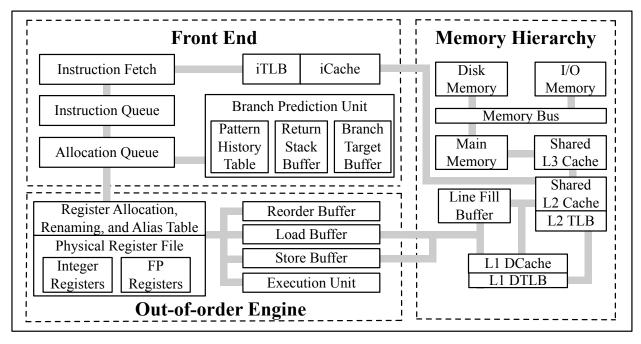

Figure 2.1: Example speculative microprocessor design [104] with a front-end component, the memory hierarchy, and an out-of-order engine. Arrows represent data flow from one state to another.

Microarchitectural design. Buffers, caches, arithmetic logical units, and other digital logic blocks constitutes the actual implementation of the processor. As each instruction is executed by the processor pipeline, each component is used to compute the next architectural state. More precisely, the microarchitecture includes all the components that implement the logic of how an executed instruction affects the registers, memory, arithmetic logic and other states defined in the architecture. As an example, Figure 2.1 depicts a design of a microprocessor (described at some arbitrary level of abstraction) with three main parts consisting of the front end, the memory hierarchy, and the out-of-order engine. The front end deals with anything related to instruction fetch, instruction decode, and register allocation, which includes logic used to determine the next instruction to execute such as the branch predictors. The out-of-order engine is part of the microprocessor that deals with asynchronous events that may occur out-of-order such as the reorder buffer and load/store buffers. Lastly, the memory hierarchy optimizes the speed at which memory accesses and writes are made using caches.

#### 2.1.2 A Decades-Old Flaw: Transient Execution Vulnerabilities

Unfortunately, the introduction of optimizations and buffers mentioned in the previous section has led to numerous *side channels* that can be used by an attacker as a data extraction channel of a victim process. On top of that, extraction is made simpler because of speculation.

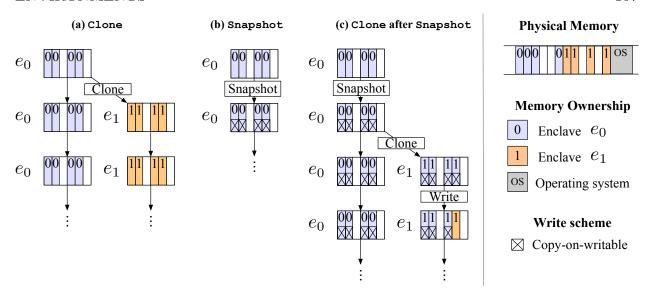

| Stage 0:<br>Before Prime+Probe       |                     |                         | Stage 1:<br>Attacker primes |                     |                         | Stage 2:<br>Victim executes |                                  |                     |                         | Stage 3:<br>Attacker probes |                               |                        |                         |

|--------------------------------------|---------------------|-------------------------|-----------------------------|---------------------|-------------------------|-----------------------------|----------------------------------|---------------------|-------------------------|-----------------------------|-------------------------------|------------------------|-------------------------|

| Index0<br>Index1<br>Index2<br>Index3 | Tag0 Tag1 Tag2 Tag3 | Data0 Data1 Data2 Data3 | Index0 Index1 Index2 Index3 | Tag0 Tag1 Tag2 Tag3 | Data0 Data1 Data2 Data3 | In                          | idex0<br>idex1<br>idex2<br>idex3 | Tag0 Tag1 Tag2 Tag3 | Data0 Data1 Data2 Data3 | Inc                         | dex0<br>dex1<br>dex2/<br>dex3 | Tag0 Tag1 //Tag2/ Tag3 | Data0 Data1 Data2 Data3 |

|                                      | Not e               | victed                  |                             | Evicted             | 1                       |                             | Fas                              | ter acces           | S                       |                             | Slow                          | er access              | S                       |

Figure 2.2: Stages of the Prime+Probe attack assuming a 4-way set associative cache. In the first stage, the attacker primes the cache by making memory accesses from their address space whose addresses map to the cache lines of a set. This invalidates all entries in a cache set. In the second stage, the victim executes, resulting in an evicted cache line. Finally, the attacker times the same memory accesses to determine information about which address the victim accessed.

Creating a side channel for an attacker. The discovery of new side-channel retrieval techniques has enabled attackers to retrieve information about sensitive data more efficiently over the years. Attackers can use these techniques to break address space layout randomization techniques and retrieve information about the execution paths of programs to break encryption schemes. For example, Flush+Reload [228] and Prime+Probe [134] are prominent techniques that reveal the address of a victim's memory accesses to an attacker. The attacker accomplishes this in three stages as shown in Figure 2.2, which depicts the Prime+Probe attack for a given set of the cache. We describe these three stages below.

- Stage 1. In the first stage of the attack, the attacker first constructs an eviction set using a buffer that is accessible in their own address space. The attacker uses this set to evict every cache line from the cache set with their data. In a later step, the attacker uses the eviction set to determine which addresses the victim has accessed.

- Stage 2. In the second stage of the attack, context switches to the victim which executes their code. As they execute, they make memory accesses whose contents are eventually cached at some level of the memory hierarchy.

- Stage 3. In the final stage of the attack, the attacker makes memory accesses using the same eviction set constructed in the first stage and times each access. If access to a particular

memory address in the eviction set is *fast*, then this corresponds to accessing a cache line that was previously accessed during the prime stage and nothing is learned. However, if the access to a memory address in the eviction set is *slow*, this means that the corresponding cache line was evicted during victim execution. Consequently, this reveals to the attacker information about the address that was accessed by the victim. The attacker can then use this information to infer the secret-dependent execution path taken in algorithms such as square-and-multiply and AES, revealing information about secrets.

We note that this attack has been shown to be effective even for the last-level cache, thus it is even easier for attackers to retrieve information from the L1D cache if the attacker and victims execute on the same physical core.

**Speculation**. The remaining element that is fundamental to reproducing transient execution attacks is speculation in a processor. Speculation allows a microprocessor to guess the value of a particular result currently being computed in the pipeline and proceeding without knowing what the actual value is. In the event that the speculated value is incorrect, the processor reverts its state to a former state before it made the speculation. This technique allows the microprocessor to increase instruction throughput and ultimately improves the processor's performance. Examples of speculation include branch prediction, value prediction, and store-to-load forwarding [195].

Combining speculation with side channels. Together, side channels and speculation in microprocessors form a new class of vulnerabilities called transient execution vulnerabilities that existed for over a decade before it was discovered. Unfortunately, the focus of formal verification for hardware has mainly been on verifying functional correctness. When out-of-order and superscalar processors became widely adopted, the trend of using the ISA as a correctness criterion persisted, giving birth to techniques such as the *Burch-Dill flushing technique* [37, 88, 185, 199, 217] which has been used as a general correctness criterion for leading semiconductor chip companies. Software-based formal verification, on the other hand, only reasons at the instruction level, without details about the hardware which is fundamental to these attacks. Consequently, many existing techniques that reason about hardware only or software only, have become inadequate for security.

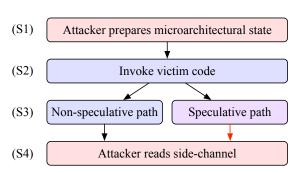

A transient execution vulnerability typically follows four stages as shown in Figure 2.3. In the first stage of the attack (S1), the attacker prepares the side channel similar to the Prime+Probe attack and executes code gadgets to trick the microprocessor into speculating in a later stage. In the second stage (S2), the attacker calls the victim function, which speculatively executes code that wouldn't have otherwise been executed under non-speculative execution. In the

Figure 2.3: Stages of a speculative attack.

third stage (S3), the victim's program accesses secret information and propagates it to a side channel as indicated by the red arrow. At that point, all the attacker needs to do is initiate the probe stage (S4) to infer information about the secret. While this may seem similar to an attack using the Prime+Probe attack, we will later see in Chapter §4, the difference in the extent to which secrets can be revealed.

#### 2.1.3 Attacker Model

For a majority of hardware-based attacks [116, 133], the attacker model is assumed to be executing on the same physical core so that it shares the same resources such as the L1D cache, branch prediction buffers, etc. However, this is not always the case, and the attacker has been shown to effectively observe leakage even across cores [134]. The attacker is also typically assumed to have access to user space and can execute for an unlimited duration, use system calls, and execute instructions to accurately time programs (e.g., using an instruction such as rdtsc in x86 architectures).

#### 2.2 Trusted Execution Environments