# Feedforward MLSE Equalization for High Speed Serial Links

Paul Kwon

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2023-215 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2023/EECS-2023-215.html

August 11, 2023

Copyright © 2023, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Feedforward MLSE Equalization for High Speed Serial Links

By

#### Paul Kwon

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

- •

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vladimir Stojanovic, Co-chair Professor Elad Alon, Co-chair Professor Ali Niknejad Professor Martin White

Summer 2023

## Feedforward MLSE Equalization for High Speed Serial Links

Copyright 2023 by Paul Kwon

#### Abstract

#### Feedforward MLSE Equalization for High Speed Serial Links

by

#### Paul Kwon

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vladimir Stojanovic, Co-chair

Professor Elad Alon, Co-chair

An ever-increasing demand for high data rate wireline links must be met to support the continual scaling of computing and communication systems. Typical serial link architectures use feedback-based channel equalization schemes, which can be challenging and even infeasible to realize for data rates beyond 100 GBaud/s. To alleviate this feedback-induced latency bottleneck, this thesis explores feedforward equalizers inspired by the maximum likelihood sequence estimation (MLSE) algorithm. Targeting short-reach, die-to-die links, a 1-tap fully feedforward MLSE architecture is shown to achieve comparable error statistics with the conventional 1-tap decision feedback equalizer (DFE).

A 160 Gb/s NRZ receiver implementing the 1-tap MLSE equalizer is taped out in a 16 nm FinFET process to evaluate the future promise of the proposed approach. The feedforward MLSE is time-interleaved to achieve the desired throughput. Current integration techniques provide energy-efficient analog latches used in the MLSE datapath. The datapath is designed using the Berkeley Analog Generator (BAG) framework. Both the top level datapath and its subblocks are created using parameterizable circuit schematic and layout generators. Measurement and design scripts identify the impact of inter-subblock routing parasitics, facilitating agile subblock design iteration with top level floorplanning in mind.

As the channel characteristics are unknown a priori, the coefficient settings of the MLSE must be adapted in real time. An adaptation scheme for the feedforward MLSE equalizer is proposed with separate loops for each interleaved MLSE slice to account for process variation. The receiver is taped out along with a corresponding 160 Gb/s NRZ transmitter and tested over an on-package loopback channel of 8.5 mm, which incurs 3 dB of loss at the Nyquist frequency. The receiver is simulated to operate at an energy efficiency of 2.08 pJ/bit, with the datapath itself consuming 0.72 pJ/bit.

To my family

# Contents

| Contents |                  |                                                      |     |

|----------|------------------|------------------------------------------------------|-----|

| Li       | $\mathbf{st}$ of | Figures                                              | iv  |

| Li       | st of            | Tables                                               | vii |

| 1        | Intr             | roduction                                            | 1   |

|          | 1.1              | Background                                           | 1   |

|          | 1.2              | Channel Equalization                                 | 2   |

|          |                  | 1.2.1 Continuous Time Linear Equalizer (CTLE)        | 4   |

|          |                  | 1.2.2 Feedforward Equalizer (FFE)                    | 5   |

|          |                  | 1.2.3 Decision Feedback Equalizer (DFE)              | 6   |

|          | 1.3              | Thesis Organization                                  | 7   |

| <b>2</b> | Stat             | tistical Analysis and Architecture Exploration       | 8   |

|          | 2.1              | Maximum Likelihood Sequence Estimation               | 8   |

|          |                  | 2.1.1 Overview                                       | 8   |

|          | 2.2              | Statistical Analysis Framework                       | 11  |

|          | 2.3              | Explored Architectures                               | 16  |

|          |                  | 2.3.1 Window Length 1                                | 16  |

|          |                  | 2.3.2 Window Length 2                                | 18  |

|          |                  | 2.3.2.1 Majority Vote                                | 22  |

|          |                  | 2.3.2.2 Single Window                                | 24  |

|          |                  | 2.3.3 Window Length 3                                | 26  |

|          | 2.4              | Equalizer Comparison and Conclusions                 | 28  |

| 3        | Des              | ign Techniques for a 160 Gb/s 1-Tap MLSE Datapath    | 31  |

|          | 3.1              | Overview                                             | 31  |

|          | 3.2              | Analog Datapath Architecture                         | 32  |

|          | 3.3              | Current Integrating Circuits                         | 34  |

|          |                  | 3.3.1 Intersymbol Interference Design Considerations | 36  |

|          |                  | 3.3.2 Output Linearity Design Considerations         | 37  |

|    |      | 3.3.3 Integrating Latch Design Flow                 |

|----|------|-----------------------------------------------------|

| 9  | 3.4  | 8-Way Interleaved T&H                               |

| 9  | 3.5  | 8:16 Deserializer                                   |

| 9  | 3.6  | Integrating Latched Summer                          |

|    | 3.7  | Backend Sampler                                     |

| 9  | 3.8  | Backend Deserializer                                |

| į  | 3.9  | Simulation Results and Conclusions                  |

| ]  | 160  | Gb/s Receiver Integration                           |

| 4  | 1.1  | Receiver Design                                     |

|    |      | 4.1.1 Clocking                                      |

| 4  | 1.2  | On-Chip Testing Features                            |

|    |      | 4.2.1 Snapshot Engine                               |

|    |      | 4.2.2 Pattern Checker                               |

| 4  | 1.3  | Off-Chip Testing Software                           |

|    |      | 4.3.1 Equalizer Adaptation                          |

|    |      | 4.3.2 Offset Calibration                            |

|    |      | 4.3.3 Pulse Response Characterization               |

| 4  | 1.4  | Test Setup                                          |

| 4  | 1.5  | Simulation and Measurement Results                  |

| 4  | 1.6  | Conclusions                                         |

| (  | Con  | clusion                                             |

|    | 5.1  | Thesis Summary                                      |

| ٦  | 5.2  | Future Works                                        |

| ib | liog | graphy                                              |

| 1  | Deta | ailed Error Statistical Analysis of MLSE Equalizers |

|    |      | MLSE Window Length 1: Lower Bound BER               |

# List of Figures

| 1.1  | Link data rate trends $ 1 $                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Optical Internetworking Forum (OIF) Common Electrical I/O (CEI) standards                                                                                                 |

|      | for different reach applications [2]                                                                                                                                      |

| 1.3  | Chiplet interconnects [4]                                                                                                                                                 |

| 1.4  | Low-loss channel frequency response (a) and pulse response (b)                                                                                                            |

| 1.5  | CTLE: active (a) and passive (b) topologies                                                                                                                               |

| 1.6  | FFE with $M$ pre-cursor and $N$ post-cursor taps                                                                                                                          |

| 1.7  | DFE                                                                                                                                                                       |

| 1.8  | 1-tap loop-unrolled DFE                                                                                                                                                   |

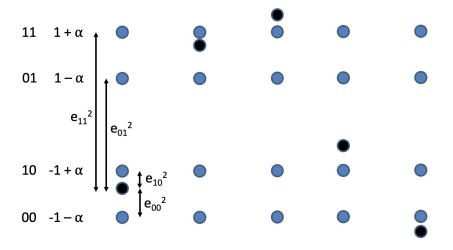

| 2.1  | Ideal voltage states (blue) and received voltage samples (black) for a channel with coefficients $[h_0, h_1] = [1, \alpha]$ and NRZ signaling with data levels of $\pm 1$ |

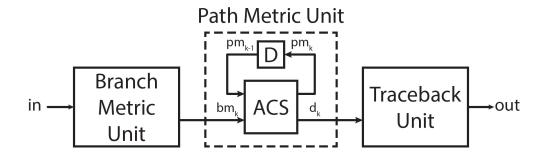

| 2.2  | Viterbi equalizer                                                                                                                                                         |

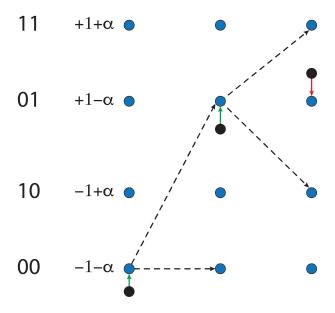

| 2.3  | Window conflict example. Received voltage samples (black), with expected state transitions (dashed lines)                                                                 |

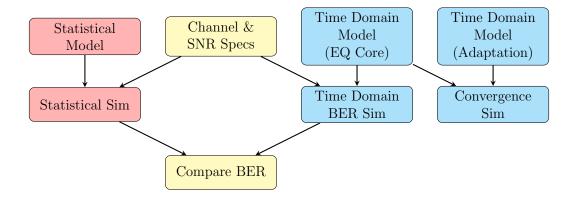

| 2.4  | Framework flow for statistical (red) and time-domain (cyan) verification                                                                                                  |

| 2.5  | Discretization of a Gaussian distribution for $n_{\sigma} = 3, b_{\sigma} = 4$                                                                                            |

| 2.6  | Window length 1 decoding with $+1/0/-1$ thresholds (dashed)                                                                                                               |

| 2.7  | Decoded window conditions for $W(n)$ (red) and $W(n+1)$ (green) for lower-bound BER                                                                                       |

| 2.8  | Error statistics comparison between DFE and lower-bound MLSE (window length 1)                                                                                            |

| 2.9  | Window length 2 decoding with labeled thresholds (dashed)                                                                                                                 |

| 2.10 | A partition of the window length 2 decoding into horizontal and vertical lines (green, dashed)                                                                            |

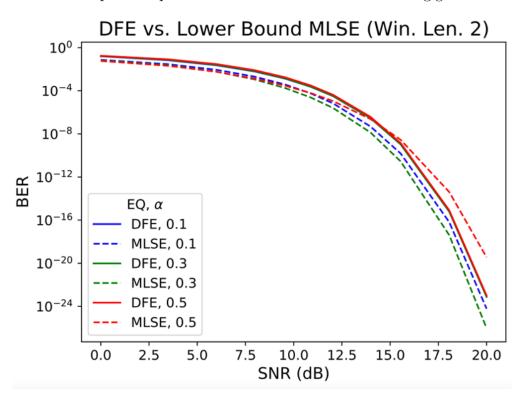

| 2.11 | Error statistics comparison between DFE and lower-bound MLSE (window length 2)                                                                                            |

| 2.12 | Error statistics comparison between DFE and majority vote MLSE (window length 2)                                                                                          |

| 2.13 | Single window decoding for window length 2. A single bit is decoded: 1 if the                                                                                             |

| 0.14 | received samples are in the red region, 0 if the green region                                                                                                             |

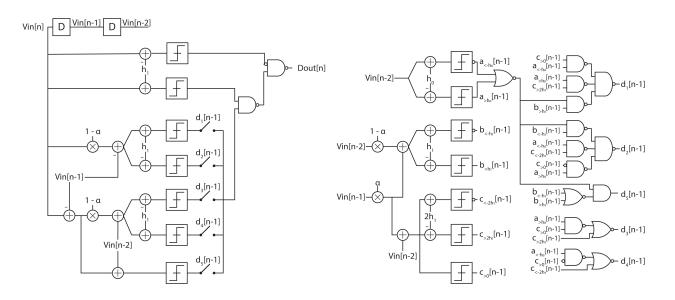

| 2.14 | Single window length 2 block diagram                                                                                                                                      |

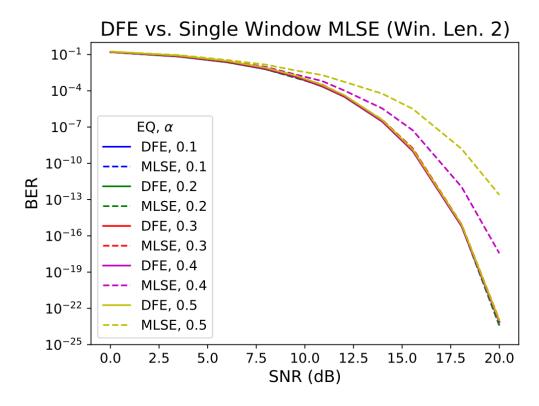

| 2.15         | Error statistics comparison between DFE and single window MLSE (window length 2)                                                                                                  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | Single window length 3 block diagram                                                                                                                                              |

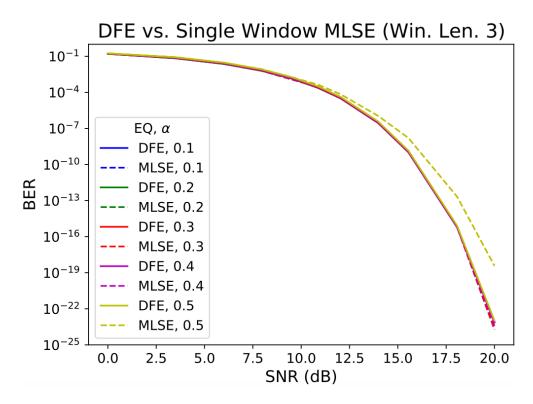

| 2.17         | Error statistics comparison between DFE and single window MLSE (window length 3)                                                                                                  |

| 2.18         | Equalizer tradeoffs                                                                                                                                                               |

| 3.1          | RX MLSE block diagram                                                                                                                                                             |

| 3.2          | MLSE analog datapath block diagram                                                                                                                                                |

| 3.3          | Datapath design flow                                                                                                                                                              |

| 3.4          | Current integration operation                                                                                                                                                     |

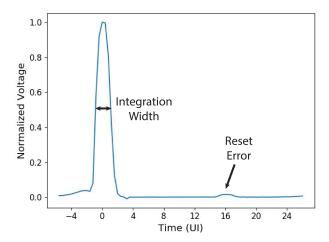

| 3.5          | Impulse response of integrating amp showing different sources of ISI                                                                                                              |

| 3.6          | Latch model during integration                                                                                                                                                    |

| 3.7<br>3.8   | Waveforms for current- integrating input                                                                                                                                          |

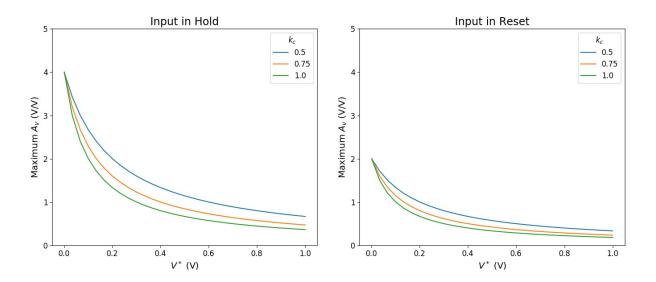

| 5.0          | Maximum voltage gain $(A_v)$ vs. current efficiency $(V^*)$ tradeoffs for stable input (left) and input resetting to $V_{DD}$ (right); assuming $V_{DD} = 1$ V, $v_{ic} = 0.7$ V, |

|              | $V_{th} = 0.2 \text{ V}$ , maximum $v_{id} = 0.2 \text{ V}$                                                                                                                       |

| 3.9          | Current integrating latch design flow                                                                                                                                             |

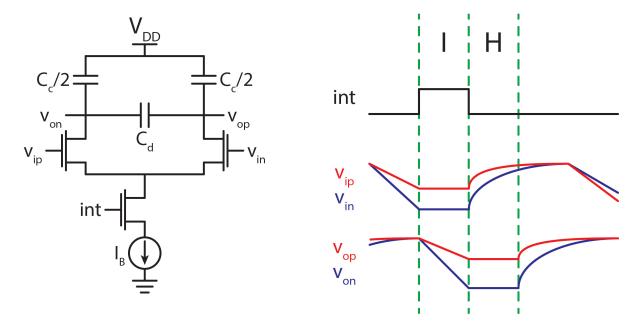

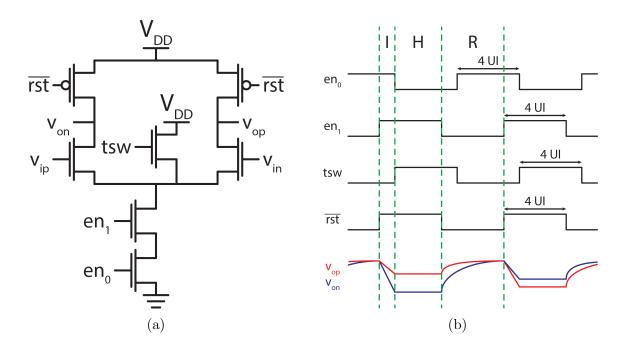

| 3.10         | T&H topology (a) and timing (b)                                                                                                                                                   |

| 3.11         | BAG optimization flow                                                                                                                                                             |

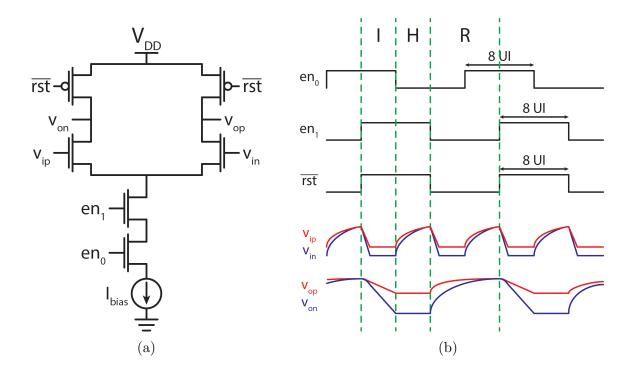

|              | Integrating 8:16 descrializer unit cell topology (a) and timing (b)                                                                                                               |

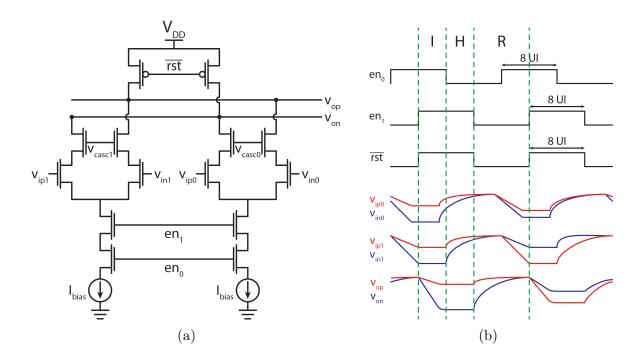

| 3.13         | Integrating latched summer topology (a) and timing (b)                                                                                                                            |

|              | Summer input path tracing between $v_{i1}$ (green) and $v_{i0}$ (red)                                                                                                             |

|              | StrongArm flop                                                                                                                                                                    |

|              | StrongArm latch                                                                                                                                                                   |

|              | Symmetric SR latch                                                                                                                                                                |

|              | Coarse retimer                                                                                                                                                                    |

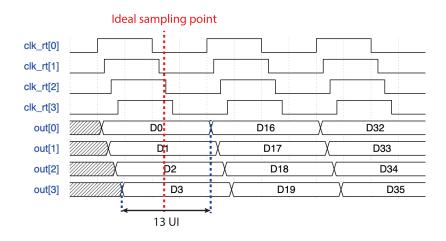

|              | Coarse retiming                                                                                                                                                                   |

|              | Fine retiming                                                                                                                                                                     |

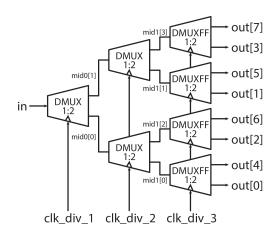

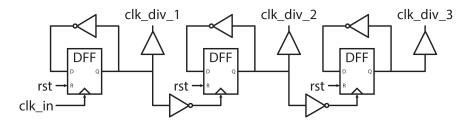

|              | Clock divider chain                                                                                                                                                               |

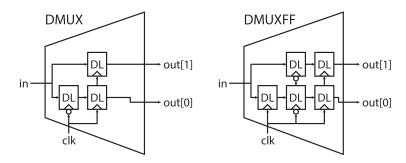

|              | 1:2 demultiplexer: latch (left) and flip flop (right)                                                                                                                             |

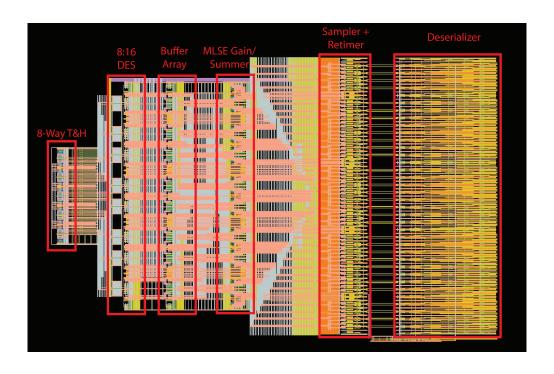

|              | Generated MLSE analog datapath layout                                                                                                                                             |

| J 1          |                                                                                                                                                                                   |

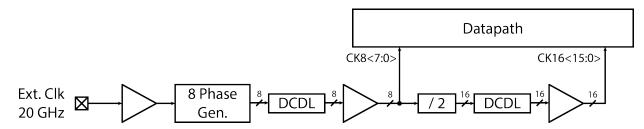

| 4.1          | Receiver clocking path                                                                                                                                                            |

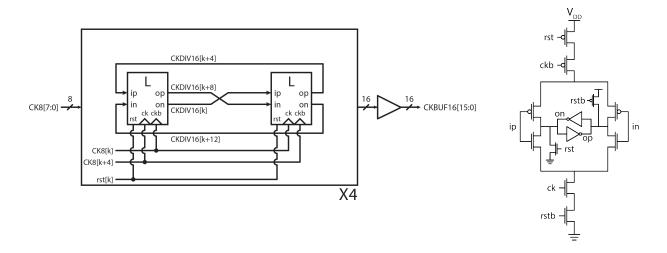

| 4.2          | 20 GHz to 10 GHz clock dividers                                                                                                                                                   |

| 4.3          | Differential $C^2MOS$ latches                                                                                                                                                     |

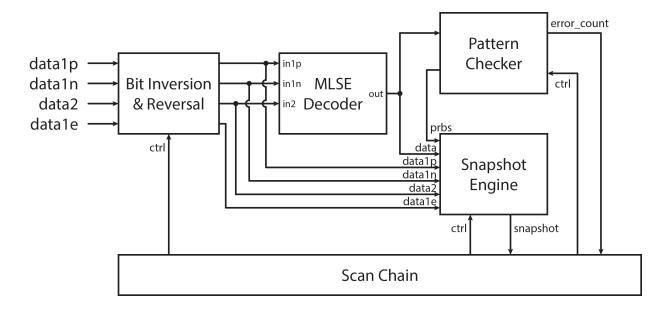

| 4.4          | Digital backend block diagram                                                                                                                                                     |

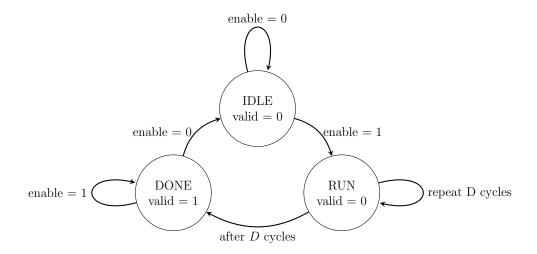

| 4.5          | Snapshot engine FSM                                                                                                                                                               |

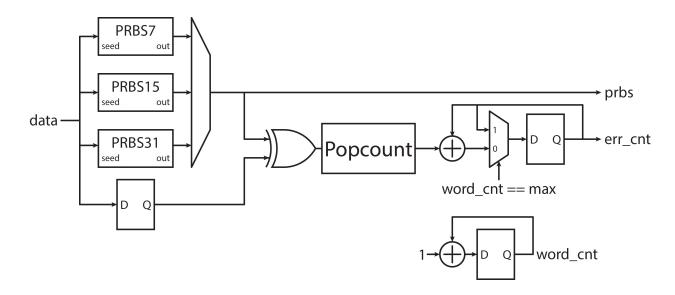

| $4.6 \\ 4.7$ | Pattern checker block diagram                                                                                                                                                     |

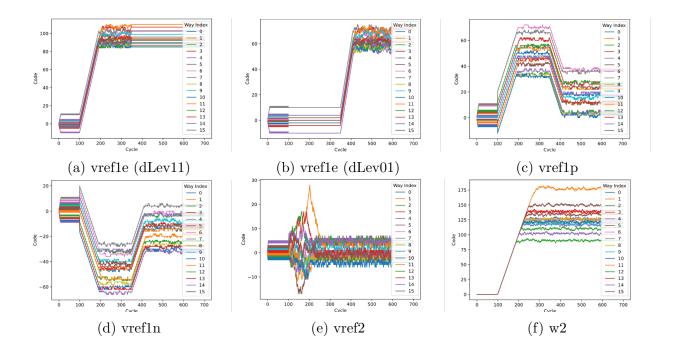

| 4.8          | Simulated equalizer adaptation and offset calibration waveforms                                                                                                                   |

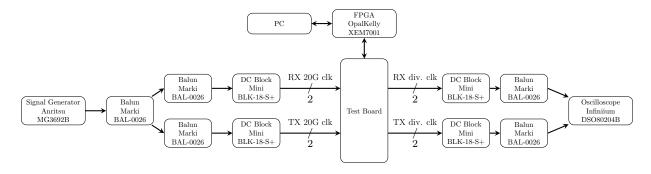

| 4.9  | Testing options                                                                | 6 |

|------|--------------------------------------------------------------------------------|---|

| 4.10 | Test setup                                                                     | ( |

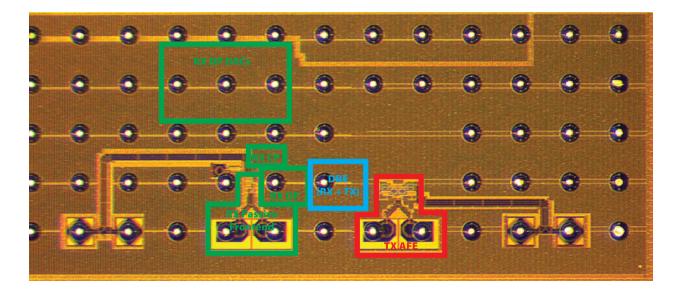

| 4.11 | Die photo                                                                      | ( |

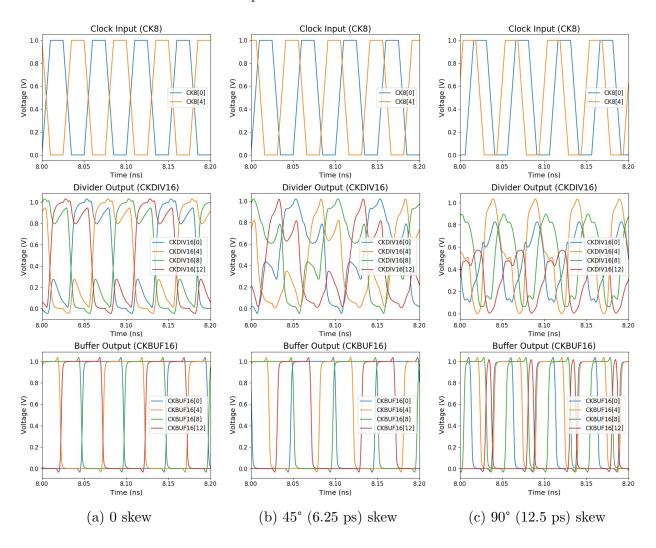

| 4.12 | Simulated clock divider waveforms with varying skew between input differential |   |

|      | clock phases                                                                   | 6 |

# List of Tables

| 3.1 | Datapath power (simulated) breakdown          | 51 |

|-----|-----------------------------------------------|----|

| 4.1 | Summer gain and offset update                 | 59 |

| 4.2 | Receiver area and power (simulated) breakdown | 63 |

| 4.3 | Performance table                             | 65 |

#### Acknowledgments

When I started my undergraduate program at UC Berkeley, I thought I'd be out of here in 4 years. Little did I know that Berkeley would give me a decade of opportunities and growth.

I would first like to thank my advisors: Professors Elad Alon and Vladimir Stojanović. I've had the privilege to engage in many technical conversations with Professor Elad throughout my Ph.D. education. His sharp circuit intuition never ceases to amaze me. He's also motivated to not focus on just my project, but rather on the larger narrative of which my research is a small piece. Professor Vladimir has been instrumental in broadening my perspectives. His visions for the future of wireline communications and design methodologies inspire me to pursue big dreams.

I also thank Professors Ali Niknejad and Martin White for serving on my qualifing exam and dissertation committees. I'm grateful for their guidance on my work. I would also like to thank Professor Borivoje Nikolić for his technical advice during design reviews.

I appreciate the opportunity to share my research progress with Farhana Sheikh, Jahnavi Sharma, and many others from Intel. It's always great to receive feedback from industry for their unique, non-academic perspectives.

I'm thankful for the wonderful support I've received from the BWRC staff: Jeff Anderson-Lee, Brian Richards, Candy Corpus, and Mikaela Cavizo-Briggs. Special thanks to Anita Flynn for her assistance with PCB design reviews and chip testing options.

Over the years, I've been fortunate to work with and learn from many brilliant peers. As an undergraduate fledgling unsure of what to pursue, I thank Seobin Jung for the opportunity to assist in her research, as well as Jaeduk Han for providing my first exposure to wireline circuits. I would like to thank other senior students and postdocs who I've learned a lot from both in and beyond my area of expertise: Eric Chang, Minsoo Choi, Greg LaCaille, Richard Lin, Pengpeng Lu, Ali Moin, Nathan Narevsky, Emily Naviasky, Antonio Puglielli, Nick Sutardja, Konstantin Trotskovsky, Zhongkai Wang and Bonjern Yang. I'm grateful for the opportunities to closely work together with Ayan Biswas, Kunmo Kim, Yi-Hsuan Shih, Bob Zhou, Wahid Rahman, and Antroy Chowdhury for the SerDes project. I'd also like to thank Zhaokai Liu, Kwanseo Park, Zhenghan Lin, Sean Huang, Sunjin Choi, Aviral Pandey, Dan Fritchman, and Meng Wei, and Rebecca Zhao.

I would like to thank my parents and my brother for their continual support over the years. I'm thankful for the times of rest I could share with my church community. Finally, I thank my girlfriend, Lucy Choi, for her steadfast love. Surviving 10 years of Berkeley, as rewarding as it is, is no easy task. I'm glad that I've been blessed with friends and family that I can lean on during this journey and whatever comes next.

# Chapter 1

## Introduction

## 1.1 Background

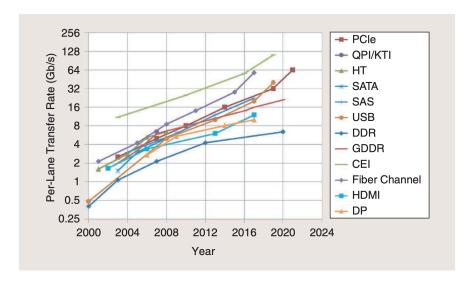

Ultra-high throughput, energy-efficient wireline links are key to enabling the next generation of computing and communication systems. Serializer-Deserializer (SerDes) transceivers form the backbone of many applications, ranging from high performance computing to artificial intelligence and Internet of Things. These systems scale over time, increasing the demand for higher rate serial links. In fact, the per-lane data rates for common I/O standards have doubled every 3-4 years (Figure 1.1).

Figure 1.1: Link data rate trends [1]

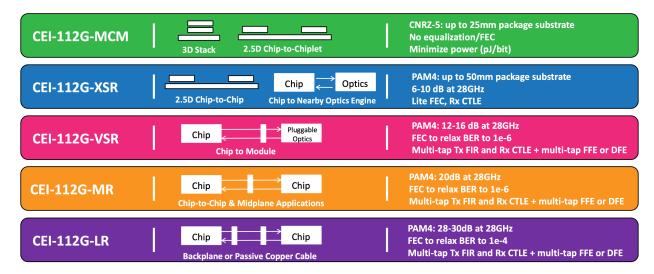

To support the wide variety of applications, serial interfaces are often classified to different reaches. For example, networking systems typically require data to travel over a backplane with connectors. Wireline transceivers for such board-to-board communication must be able to operate with long reach (LR) channels, which can introduce significant loss at high frequencies. On the other end of the spectrum, chip-to-chip interfaces require low-latency SerDes to transmit data over short, multi-chip module (MCM) links, with minimal channel loss.

Figure 1.2: Optical Internetworking Forum (OIF) Common Electrical I/O (CEI) standards for different reach applications [2]

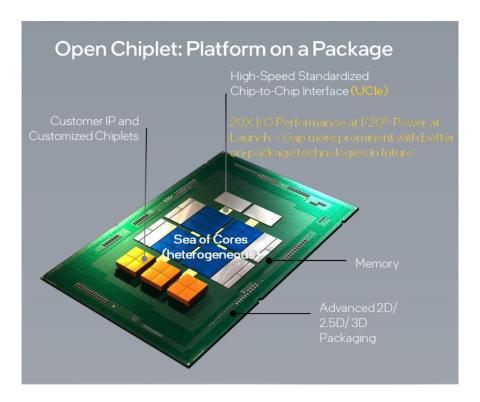

In recent years, a new application for wireline links has emerged. Whereas the traditional system-on-chip (SoC) approach places all integrated circuits on a monolithic die, growing transistor and design costs are pushing for these systems to be partitioned into smaller dies, or chiplets. The multi-chiplet, heterogeneous integration approach allows for higher yield due to smaller die sizes, and chiplets can be optimally designed in different technology nodes. This is best summed up by Gordon Moore's prediction in 1965: "It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected." [3] To take advantage of multi-chiplet systems, die-to-die links must provide excellent bandwidth and energy efficiency.

## 1.2 Channel Equalization

Designing robust links requires equalization to counteract the loss of the wireline channel. Electrical channels often have low-pass filtering behaviors due to the skin effect and dielectric loss of the material. In addition, any impedance mismatches along the channel (e.g., between the connector and backplane) causes reflections, which further worsens the signal integrity.

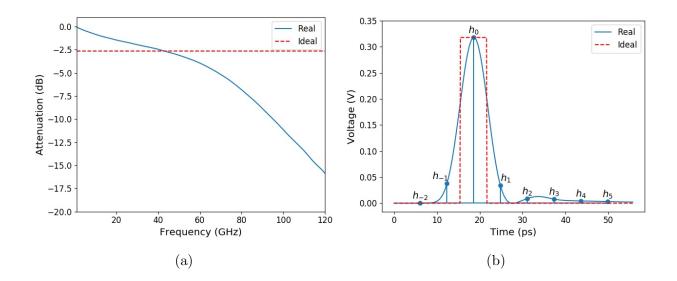

The loss characteristics of the channel can be visualized in both frequency and time domain (Figure 1.4). Suppose the channel is modeled as a finite impulse response (FIR) filter, whose inputs are the symbols transmitted at each unit interval (UI). If modeled as an

Figure 1.3: Chiplet interconnects [4]

FIR with M precursor taps, N postcursor taps, and 1 main tap, the channel will output y as a convolution of the FIR taps h and the input signal x:

$$y[n] = (h * x)[n] = \sum_{k=-\infty}^{\infty} h_k x[n-k] = \sum_{k=-M}^{N} h_k x[n-k]$$

(1.1)

The channel coefficients can be measured using a pulse response, where the output waveform is observed for a 1 UI-wide input pulse. The resulting time-domain response reveals the channel FIR taps spaced 1 UI apart (Figure 1.4b). Note that  $h_0$  represents the main channel tap (the desired pulse). All other taps degrade signal integrity through intersymbol interference (ISI), where neighboring symbols are superpositioned onto the current receiver sample to varying degrees. ISI introduces data-dependent error terms which increase the link's bit error rate (BER). The goal of equalization thus is to flatten out the frequency response of the channel such that the time-domain pulse response shows little to no residual ISI.

With increasing data rates, more powerful equalization is required to maintain signal integrity. To the first order, the channel loss tends to increase linearly in dB with respect to frequency. In addition, the effective channel seen by the transceiver must include not only the physical routing channel, but also the transceiver circuits themselves. This becomes

Figure 1.4: Low-loss channel frequency response (a) and pulse response (b)

especially important as data rates are pushed to the limits of the technology, since frontend circuits will face bandwidth limitations and contribute to more loss in the signal chain. The following sections will introduce conventional wireline receiver equalization techniques which may have disadvantages at high data rates.

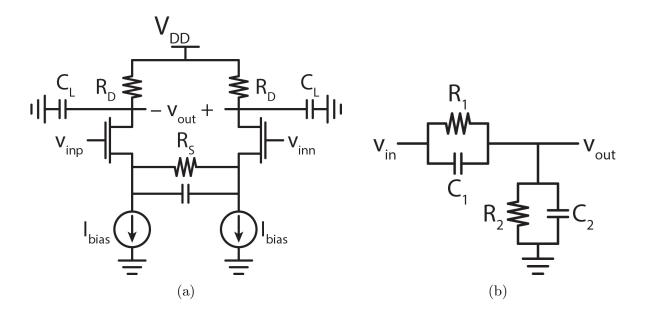

## 1.2.1 Continuous Time Linear Equalizer (CTLE)

To counteract the channel's low-pass behavior, continuous time linear equalizers (CTLE) provide peaking gain. Typical implementations have a zero-pole pair, and the peaking gain is set by the ratio of the pole to zero frequencies. Active, transistor-based topologies attenuate low frequency signals through the resistive source degeneration. As frequencies increase, the source capacitance  $C_s$  begins to dominate, creating a low source impedance and reducing the effect of source degeneration. The peaking gain is set by the source degeneration effect  $(1 + g_m R_s/2)$ , and the zero and pole locations are computed below:

$$\omega_z = \frac{1}{R_s C_s} \tag{1.2}$$

$$\omega_p = \omega_z \cdot (1 + g_m R_s/2) \tag{1.3}$$

Active CTLE designs also suffer from an additional pole at the output, which causes a 20 dB per decade roll-off in gain for frequencies above  $\frac{1}{R_DC_L}$ . Passive CTLE topologies are designed with parallel RC structures, where the resistive divider determines low-frequency gain and the capacitive divider determines high-frequency gain. The zero and pole are

Figure 1.5: CTLE: active (a) and passive (b) topologies

computed below:

$$\omega_z = \frac{1}{R_1 C_1}$$

$$\omega_p = \frac{1}{(R_1 \parallel R_2)(C_1 + C_2)}$$

(1.4)

$$\omega_p = \frac{1}{(R_1 \parallel R_2)(C_1 + C_2)} \tag{1.5}$$

Being a frequency-domain equalizer, the CTLE is often used to cancel long-tail postcursor ISI that would otherwise be challenging for time-domain equalizers (whose complexity scales with number of taps). Equalizing near-tap ISI with the CTLE poses circuit design challenges due to how high the poles and zeros would need to be placed. Because the CTLE is a frequency-domain equalizer, it must be placed at the datapath frontend and operate at full bit rate. With increasing data rates, parasitics are likely to limit the bandwidth and equalizing capabilities of the CTLE. Furthermore, the CTLE suffers from noise enhancement, as both the noise and signal are equally boosted at high frequencies.

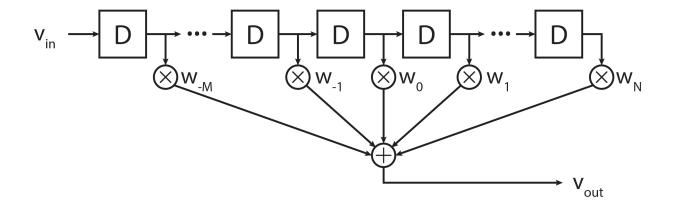

#### 1.2.2Feedforward Equalizer (FFE)

The feedforward equalizer (FFE) is an FIR whose tap coefficients are set to cancel pre- or postcursor ISI taps from the channel. The FFE can be implemented at either the transmitter or the receiver. Like the CTLE, the receiver FFE also amplifies noise because the inputs to the FIR are analog samples. At the transmitter, the FFE is robust to noise as its inputs are digital symbols. However, headroom constraints on the transmitter output swing require a normalization of the FFE tap coefficients, reducing the effective signal amplitude. Despite

Figure 1.6: FFE with M pre-cursor and N post-cursor taps

its data rate scalability as a parallelizable equalizer scheme, the FFE is usually combined with other equalizers for low BER applications due to noise enhancement and headroom issues.

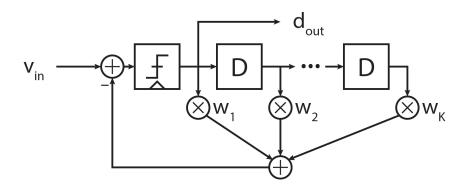

#### 1.2.3 Decision Feedback Equalizer (DFE)

Figure 1.7: DFE

The decision feedback equalizer (DFE) is another FIR-based equalizer which cancels ISI based on previous decisions. The main advantage of the DFE is its robustness to noise because the FIR takes digital symbols as inputs. The DFE is limited to equalizing postcursor taps as it operates on previously decoded bits. Any past incorrect decisions can also propagate through the FIR, potentially generating additional errors. From a frequency scalability perspective, the DFE is bottlenecked by its feedback loop, where the tap coefficient weighting, analog summation, and symbol resolution all must be completed in 1 UI.

To reduce the critical path, loop-unrolling techniques have been applied to the DFE. A 1-tap loop-unrolled DFE structure is shown in Figure 1.8. In practice, loop-unrolling is

Figure 1.8: 1-tap loop-unrolled DFE

limited to 1-tap because this technique causes the complexity to scale exponentially with the number of loop-unrolled taps, and loop-unrolling increases the delay associated with later non-unrolled taps. Nevertheless, a feedback loop still exists and limits the speed of this equalizer.

## 1.3 Thesis Organization

Given the limitations of traditional SerDes equalization algorithms, a noise-robust, feedforward equalizer architecture is critical to building power-efficient links at 100+ GBaud/s rates. Short die-to-die links do not require heavy equalization, but must deal with noiselimited channels where noise amplification could limit the achievable BER of the transceiver. In such applications, the DFE is particularly attractive as its robustness to noise, but its feedback-induced timing constraint becomes challenging, if not feasible, to meet for such high data rates. Consequently, Chapter 2 explores new feedforward architectures inspired by the classical Maximum Likelihood Sequence Estimation (MLSE) algorithm as alternatives to the DFE. Tradeoffs between computational complexity and error statistics of proposed algorithms are discussed, along with statistical analysis strategies for sequence-detection equalizers. Targeting a data rate of 160 Gb/s NRZ, Chapter 3 presents a receiver datapath utilizing the feedforward MLSE equalizer. Circuit design techniques and methodologies are introduced to achieve energy efficient links as communication speeds approach limits of the technology. Next, Chapter 4 describes the remaining receiver features needed to verify the datapath, including the clocking path and on- and off-chip calibration loops. Simulation results show that the receiver can achieve 160 Gb/s at 2.08 pJ per bit under a 3 dB loss on-package channel. Chapter 5 concludes the thesis with a summary of the proposed work and potential directions for future research.

# Chapter 2

# Statistical Analysis and Architecture Exploration

## 2.1 Maximum Likelihood Sequence Estimation

#### 2.1.1 Overview

As its name suggests, the MLSE algorithm chooses the most likely sequence of data symbols by comparing all possible sequences within a defined window. When dealing with additive white Gaussian noise (AWGN) channels, the most probable sequence is that which has the smallest Euclidean, or L2, norm [5].

The MLSE has a few key differences when compared to typically used equalizers like the FFE, DFE, and CTLE. First, such conventional equalizers often aim to reduce or cancel ISI energy, whereas MLSE retains and uses that ISI energy to help decode the transmitted sequence. Second, while typical equalizers often perform symbol-by-symbol detection, the MLSE inherently recovers a sequence of symbols by applying the redundant information embedded in the ISI.

An example is shown in Figure 2.1. Suppose that symbols are transmitted through NRZ signaling with voltages of  $\pm 1$ , and that the channel of interest is a 1-tap postcursor channel, with main cursor  $h_0 = 1$  and first postcursor  $h_1 = \alpha$ . The channel is effectively a 2-tap finite impulse response (FIR) filter, whose noiseless outputs are  $\pm 1 \pm \alpha$  depending on the data pattern. At unit interval (UI) n, the received sample  $v_r[n]$  deviates from the 4 noiseless expected states with the following error magnitudes:

$$e_{11}[n]^{2} = [v_{r}[n] - (1 + \alpha)]^{2}$$

$$e_{01}[n]^{2} = [v_{r}[n] - (1 - \alpha)]^{2}$$

$$e_{10}[n]^{2} = [v_{r}[n] - (-1 + \alpha)]^{2}$$

$$e_{00}[n]^{2} = [v_{r}[n] - (-1 - \alpha)]^{2}$$

(2.1)

Note that each received sample provides information about 2 consecutive symbols because

the channel memory spans 2 taps.

Figure 2.1: Ideal voltage states (blue) and received voltage samples (black) for a channel with coefficients  $[h_0, h_1] = [1, \alpha]$  and NRZ signaling with data levels of  $\pm 1$

Let the window length L be the number of consecutive UI over which we observe to compute the most likely sequence. In other words, L becomes the number of UI over which errors are accumulated in an L2-norm fashion.

Considering the same 1-tap post-cursor channel, the most likely sequence for a window length L contains L+1 symbols and can be computed as

$$W(n) = \begin{bmatrix} d_r[n-L] & \cdots & d_r[n-1] & d_r[n] \end{bmatrix} = \underset{x \in \{0,1\}^{L+1}}{\arg\min} \left\{ \sum_{i=1}^{L} e_{x_i x_{i+1}}[n+i-L]^2 \right\}$$

(2.2)

Most classic implementations of the MLSE use the Viterbi algorithm, which recursively decodes the most likely window. Suppose the path metric  $P_b[n]$  is defined as the minimum L2 norm across all sequences whose current bit is  $b \in \{0, 1\}$ :

$$P_b[n] \equiv \min_{x \in \{0,1\}^L} \left\{ \left( \sum_{i=1}^{L-1} e_{x_i x_{i+1}} [n+i-L]^2 \right) + e_{x_L b}[n]^2 \right\}$$

(2.3)

The path metric equation can be re-defined using its previous value:

$$P_{b}[n] = \min_{x \in \{0,1\}^{L-1}} \left\{ \left( \sum_{i=1}^{L-2} e_{x_{i}x_{i+1}}[n+i-L]^{2} \right) + e_{x_{L-1}0}[n-1]^{2} + e_{0b}[n]^{2} \right.$$

$$= \min \left\{ \left[ \min_{x \in \{0,1\}^{L-1}} \left\{ \left( \sum_{i=1}^{L-2} e_{x_{i}x_{i+1}}[n+i-L]^{2} \right) + e_{x_{L-1}1}[n-1]^{2} + e_{1b}[n]^{2} \right] + e_{0b}[n]^{2} \right.$$

$$= \min \left\{ \left[ \min_{x \in \{0,1\}^{L-1}} \left\{ \left( \sum_{i=1}^{L-2} e_{x_{i}x_{i+1}}[n+i-L]^{2} \right) + e_{x_{L-1}0}[n-1]^{2} \right] + e_{0b}[n]^{2} \right.$$

$$= \min \left\{ \left[ P_{0}[n-1] + e_{0b}[n]^{2} + e_{1b}[n]^{2} \right] \right.$$

$$= \min \left\{ \left[ P_{1}[n-1] + e_{1b}[n]^{2} \right] \right.$$

$$(2.4)$$

The Viterbi algorithm applies this principle to simplify the most likely sequence estimation (Figure 2.2). For each cycle, the branch metrics are computed, which represent the squared error terms  $e_{11}[n]^2$ ,  $e_{01}[n]^2$ ,  $e_{10}[n]^2$ ,  $e_{00}[n]^2$  for the current sample n. Then, the path metrics are updated using an add-compare-select (ACS) unit with the branch metric as new single-UI error terms. By using feedback, the number of comparisons needed to decode the sequence increases linearly with window length. This advantage is unfortunately incompatible with feedforward designs that are scalable with data rate.

Figure 2.2: Viterbi equalizer

To architect an energy-efficient MLSE-based equalization algorithm at ultra-high data rates, one must address a few key challenges. First, the complexity of the MLSE algorithm scales exponentially with the number of taps and window length. For an N-tap feedforward MLSE (i.e., one that will equalize a total of N precursors and postcursors) with a window length of L and a PAM-M modulation scheme, the number of states for a given sample is  $M^N$ , and the number of possible sequences in the window is  $M^{N+L}$ . In contrast, the FFE and DFE increase linearly in complexity with respect to the number of taps. For low-power applications, the receiver can employ an MLSE with a low (1-2) number of taps, with additional equalization like FFE or DFE as necessary to cover the span of the channel. Decreasing the window length reduces the complexity as well, at the cost of higher error rates, as will be discussed in later sections.

Second, one must consider how to resolve conflicting interactions between overlapping windows. For example, let's take a 1-tap postcursor MLSE with window length = 1. (2.2) simplifies to

$$W(n) = \begin{bmatrix} d_r[n-1] & d_r[n] \end{bmatrix} = \underset{x \in \{0,1\}^2}{\arg \min} \begin{cases} e_{11}[n]^2 & \text{if } x = [1,1] \\ e_{01}[n]^2 & \text{if } x = [0,1] \\ e_{10}[n]^2 & \text{if } x = [1,0] \\ e_{00}[n]^2 & \text{if } x = [0,0] \end{cases}$$

$$(2.5)$$

Thus, for the received samples shown in Figure 2.3, we would get the following decoded sequences:

$$W(1) = [0, 0] \Rightarrow d_r[0] = 0, d_r[1] = 0$$

(2.6)

$$W(2) = [0, 1] \Rightarrow d_r[1] = 0, d_r[2] = 1$$

(2.7)

$$W(3) = [0, 1] \Rightarrow d_r[2] = 0, d_r[3] = 1$$

(2.8)

The decoded sequences from UIs 1 and 2 yield a consistent bit for  $d_r[1]$ . However, the sequences from UIs 2 and 3 yield different bits for  $d_r[2]$ . This conflict results from these windows independently decoding bits. This problem could be avoided if the previous window's decision could be used to decode the current window. In the above example, if  $d_r[2] = 1$  was known from decoding of window 2, the possible states in the decoding of window 3 would be limited to [1,0] and [1,1], corresponding to voltages  $-1 + \alpha$  and  $1 + \alpha$ , and the conflicting scenario [0, 1] would never be considered. However, this would introduce feedback to the algorithm. A feedforward MLSE equalizer must thus decode each window independently while resolving any conflicts.

#### 2.2Statistical Analysis Framework

Error statistics are key to evaluating the effectiveness of a MLSE equalizer. For conventional symbol-by-symbol equalizers in NRZ signaling, a slicer compares the input differential signal to differential zero to determine the decoded bit. Ideally, this input signal is just  $\pm h_0$ , depending on whether the transmitted bit was a 1 or 0. In reality, the input contains error terms as well, such as any residual ISI post-equalization, and voltage noise. If the absolute sum of these error terms is enough to swap the polarity of the differential input, an error would occur. The BER can thus be written as

Figure 2.3: Window conflict example. Received voltage samples (black), with expected state transitions (dashed lines)

$$BER = P(d_t = 1 \cap h_0 + v_n + v_{ISI} < 0) + P(d_t = 0 \cap -h_0 + v_n + v_{ISI} > 0)$$

$$= P(d_t = 1)P(h_0 + v_n + v_{ISI} < 0) + P(d_t = 0)P(-h_0 + v_n + v_{ISI} > 0)$$

$$= \frac{1}{2}[P(v_n + v_{ISI} < -h_0) + P(v_n + v_{ISI} > h_0)]$$

$$= \frac{1}{2}[2P(v_n + v_{ISI} < -h_0)] = P(v_n + v_{ISI} < -h_0)$$

where  $v_{ISI}$  is a discrete random variable that represents residual ISI, and  $v_n$  is a normally distributed continuous random variable representing voltage noise.

As noted in [6], the probability mass function of  $v_{ISI}$  can be derived by convolving the individual distributions of ISI cursors. Since ISI is independent of noise, the bit error rate can be computed as the following:

$$BER = \sum_{x} P(v_{ISI} = x \cap v_n < -h_0 - x)$$

$$= \sum_{x} \left[ P(v_{ISI} = x) \cdot P(v_n < -h_0 - x) \right]$$

$$= \sum_{x} \left[ p_{ISI}(x) \cdot F_n(-h_0 - x) \right]$$

(2.9)

where  $p_{ISI}$  is the PMF of the ISI and  $F_n$  is the CDF of the noise distribution. For an ideal, noise-limited channel that has no residual ISI post-equalization, (2.9) simplifies to

$$BER_{symbol,ideal} = F_n(-h_0) (2.10)$$

Now, consider the proposed MLSE algorithm, which is a sequence detection equalizer. The bit error rate can generally be split into 2 components: the probability of all overlapping windows decoding the incorrect bit, and the probability that some windows decode incorrect bits and the conflict resolution mechanism chooses the wrong bit. Let e represent an incorrect bit, and let C represent the conflict resolution function. Then, the BER can be expressed as

$$BER = P\left(\bigcap_{i=1}^{N} [W_{N+1-i}(i) = e]\right) + P\left(\bigcup_{i=1}^{N} [W_{N+1-i}(i) = e] \cap \bigcup_{i=1}^{N} [W_{N+1-i}(i) \neq e] \cap C(W(1), \dots, W(N)) = e\right)$$

The first term is a error term that only depends on the window length and number of taps, whereas the second term indicates the effectiveness of a particular conflict resolution mechanism. Another perspective is that given some number of taps and window length, the first term represents the lower-bound BER for all variants. This lower-bound limit on the BER serves as an initial metric of whether the window length and/or the number of taps should be increased to meet the desired bit error rate.

Note that each decoded window is some function f of the consecutive noise samples, which are assumed to be independent and identically distributed according to a Gaussian distribution:

$$W(i) = f(v_n[i-L+1], v_n[i-L+2], \dots, v_n[i])$$

This results in a dependence between events of overlapping decoded windows, except for the trivial case when L=1. Given such dependencies involving Gaussian random variables, BER equations for these MLSE algorithms often lack closed-form expressions. To tackle this issue, a statistical analysis framework was created as a means for the user to codify the error statistics of different equalizers, thereby allowing machines to handle all the computations.

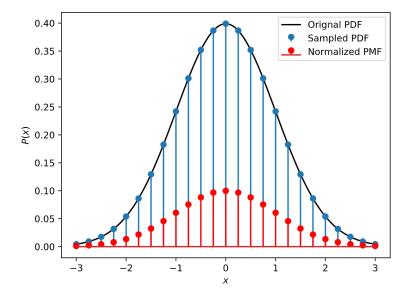

Since this framework must support the modeling of diverse equalization schemes, a few key features are implemented. First, real-world, continuous distributions like thermal noise are discretized or sampled into different bins at regular intervals, and then normalized to have a summed probability of 1. This "binning" results in a probability mass function (PMF), which can be used in-place of the continuous PDF to ease computation, especially for operations that involve multiple distributions like convolution or conditioning.

To control the range and resolution of the discretization, two parameters are introduced, respectively: the number of standard deviations  $(n_{\sigma})$ , and the number of bins per standard deviation  $(b_{\sigma})$ . Users can choose values based on their application (specifically, the BER of

Figure 2.4: Framework flow for statistical (red) and time-domain (cyan) verification

Figure 2.5: Discretization of a Gaussian distribution for  $n_{\sigma} = 3, b_{\sigma} = 4$

interest). For example, to capture error rates of  $\sim 10^{-12}$ ,  $n_{\sigma}$  should at least be 7, which results in a one-sided tail probability of  $1.28 \times 10^{-12}$  for Gaussian distributions. Increasing  $n_{\sigma}$  and  $b_{\sigma}$  improve the accuracy of the statistical results at the cost of analysis runtime. To the first order, if one is interested in how L random variables affect the probability of an event (as is the case with window decoding), an approach that iterates through all possible combinations of variable values results in a runtime  $\sim (2n_{\sigma}b_{\sigma})^{L}$ . Practically, choosing  $n_{\sigma}, b_{\sigma}$ to be around 10-15 was a reasonable compromise between statistical accuracy and runtime for low ( $< 10^{-12}$ ) BER rate applications.

Second, utility functions are implemented to deal with conditional distribution functions. For instance, consider the probability expression  $P(X > Y \cap X > Z)$ , where X, Y, and Z are arbitrary, independent, discretized random variables. A brute-force approach to this calculation would involve a 3-dimensional iteration over the domains of each variable  $\mathcal{F}_X$ ,  $\mathcal{F}_Y$ , and  $\mathcal{F}_Z$ :

$$P(X > Y \cap X > Z) = \sum_{x \in \mathcal{F}_X} \sum_{y \in \mathcal{F}_Y} \sum_{z \in \mathcal{F}_Z} \left[ P(X = x) P(Y = y) P(Z = z) \begin{cases} 1 & \text{if } x > y \cap x > z \\ 0 & \text{otherwise} \end{cases} \right]$$

If X, Y, and Z have  $B_X$ ,  $B_Y$ , and  $B_Z$  bins, respectively, then the above would take  $\sim B_X B_Y B_Z$  time to compute. However, the runtime can be significantly reduced by applying conditionality. If we define X' to be the distribution of X conditioned on the event that X > Y, then the probability can be rewritten as

$$P(X > Y \cap X > Z) = P(X > Y) \cdot P(X > Z | X > Y) = P(X > Y) \cdot P(X' > Z)$$

The individual components can be computed as follows, where  $\mathcal{F}_{X'}$  represents the domain of X':

$$\begin{split} P(X > Y) &= \sum_{x \in \mathcal{F}_X} [P(X = x) \cdot P(Y < x)] = \sum_{x \in \mathcal{F}_X} [P(X = x) \cdot F_Y(x)] \\ P(X' = x) &= \frac{P(X = x) \cdot F_Y(x)}{P(X > Y)} \\ P(X' > Z) &= \sum_{x \in \mathcal{F}_{X'}} [P(X' = x) \cdot P(Z < x)] \end{split}$$

Note the common term between P(X > Y) and the probability mass function of X'. If we define this common term as a "weight" function  $W_{X'}$ , we can re-define the above equations:

$$W_{X'}(x) \equiv P(X=x) \cdot F_Y(x) \tag{2.11}$$

$$P(X > Y) = \sum_{x \in \mathcal{F}_X} W_{X'}(x) = \sum_{x \in \mathcal{F}_{X'}} W_{X'}(x)$$

(2.12)

$$P(X' = x) = \frac{W_{X'}(x)}{\sum_{x \in \mathcal{F}_{X'}} W_{X'}(x)}$$

(2.13)

In other words,  $W_{X'}$  represents an unnormalized "probability" distribution of X', whose sum is the conditioned event P(X < Y). If the CDF of  $Y(F_Y)$  is pre-computed, the overall runtime of this approach is on the order of  $B_X$ , which is a significant improvement over the initial approach.

In addition to the statistical modeling, the analysis framework supports time-domain simulation. Time-domain analysis achieves two core purposes. Because statistical models of equalizers are more equation-driven and prone to modeling errors, time-domain behavioral models serve as a reference to sanity check that the statistical model yields equivalent error rates across different values of SNR. However, since the minimum BER detectable by a

time-domain simulation scales inversely linearly with the number of simulation cycles, timedomain models typically are only useful to estimate error rates as low as  $\sim 10^{-6}$ . The second advantage of time-domain support is to verify closed-loop adaptation schemes, as each equalizer will need to have its own dedicated adaptation engine that should account for any circuit-induced non-linearities.

#### 2.3 Explored Architectures

The feedforward MLSE algorithm would be proposed as an energy-efficient alternative to the DFE in the receiver equalization. To manage the MLSE's exponentially growing complexity, the design space was limited to one-tap post-cursor equalizers. Then, different window lengths and conflict resolution mechanisms were considered to develop different MLSE designs.

For each design, its error statistics were computed assuming a one-tap postcursor channel with main cursor  $h_0 = 1$  and first post-cursor  $h_1 = \alpha$ . The noise variance  $\sigma_n$  was varied to generate a BER vs. SNR curve, where SNR is calculated as  $\left(\frac{h_0}{\sigma_n}\right)^2$ . The proposed design's BER vs. SNR curves were then compared with those of the DFE for different values of  $\alpha$  to determine viability from an error statistical perspective.

The effect of error propagation was ignored in the statistical modeling of the DFE as it has minimal impact on the BER at low error rates [7]. Neglecting error propagation and residual ISI, the DFE error rate is simply  $F_n(-h_0) = F_n(-1)$ . Note that this is just the ideal BER for symbol-by-symbol equalizers from (2.10) because DFE does not enhance noise.

#### 2.3.1Window Length 1

Error terms in (2.5) can be substituted with the definitions from (2.1):

$$W(n) = \underset{x \in \{0,1\}^2}{\operatorname{arg min}} \begin{cases} (v_r[n] - (1+\alpha))^2 & \text{if } x = [1,1] \\ (v_r[n] - (1-\alpha))^2 & \text{if } x = [0,1] \\ (v_r[n] - (-1+\alpha))^2 & \text{if } x = [1,0] \\ (v_r[n] - (-1-\alpha))^2 & \text{if } x = [0,0] \end{cases}$$

$$(2.14)$$

$$= \underset{x \in \{0,1\}^2}{\operatorname{arg\,min}} \begin{cases} \alpha - (1+\alpha)v_r[n] & \text{if } x = [1,1] \\ -\alpha - (1-\alpha)v_r[n] & \text{if } x = [0,1] \\ -\alpha + (1-\alpha)v_r[n] & \text{if } x = [1,0] \\ \alpha + (1+\alpha)v_r[n] & \text{if } x = [0,0] \end{cases}$$

(2.15)

Expanding and removing common terms in the arg min arguments allows one to simplify (2.14) to (2.15). Then, one can inspect conditions in which one sequence results in a smaller error than another. For example, consider the comparison between  $e_{11}[n]^2$  and  $e_{01}[n]^2$ :

$$e_{11}[n]^{2} \stackrel{?}{<} e_{01}[n]^{2}$$

$$\alpha - (1+\alpha)v_{r}[n] \stackrel{?}{<} -\alpha - (1-\alpha)v_{r}[n]$$

$$2\alpha \stackrel{?}{<} 2\alpha v_{r}[n]$$

$$v_{r}[n] \stackrel{?}{>} 1$$

One can apply the same approach to other sequences to further simplify the window function:

$$W(n) = \begin{cases} [1,1] & \text{if } v_r[n] > 1\\ [0,1] & \text{if } 0 < v_r[n] < 1\\ [1,0] & \text{if } -1 < v_r[n] < 0\\ [0,0] & \text{if } v_r[n] < -1 \end{cases}$$

$$(2.16)$$

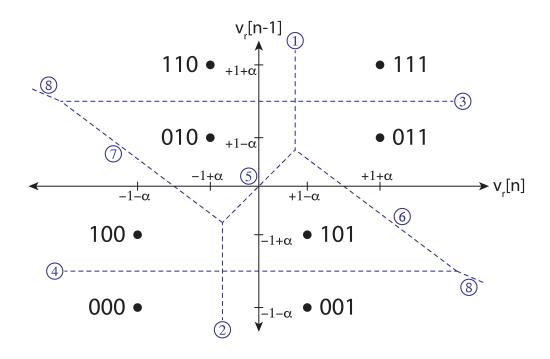

Another way to arrive at (2.16) is by graphically visualizing equidistant lines between the 4 noiseless expected states, as shown in Figure 2.6. Since the MLSE attempts to minimize the Euclidean distance, the equidistant lines represent thresholds between different sequences.

Figure 2.6: Window length 1 decoding with +1/0/-1 thresholds (dashed)

Figure 2.7: Decoded window conditions for W(n) (red) and W(n+1) (green) for lower-bound BER

As mentioned earlier, the error statistics depend on the exact conflict resolution mechanism. However, a lower-bound BER for all window length 1 designs can be calculated to sanity check whether a window length 1 equalizer is viable to begin with. The lower-bound BER can be computed by considering the ideal case that the conflict resolution mechanism always decides the correct bit when a conflict between overlapping windows arises. Thus, the BER in this case is simply the probability that all windows decode the incorrect bit.

Without loss of generality, assume that at sample n, the transmitted data symbol  $d_t[n]$  is 1. Then, the lower-bound BER (as illustrated in Figure 2.7) can be expressed as

$$BER = P(W_2(n) = 0 \cap W_1(n+1) = 0)$$

$$= P(W_2(n) = 0) \cdot P(W_1(n+1) = 0)$$

$$= P(v_r[n] < 0) \cdot P(v_r[n+1] < -1 \cup 0 < v_r[n+1] < 1)$$

(2.17)

Recall that with for a window length of 1, decoding the overlapping windows is independent. This expression simplifies to<sup>1</sup>

$$BER \approx \frac{1}{4} [F_n(-1-\alpha) + F_n(-1+\alpha)] [2F_n(-\alpha) + F_n(2-\alpha) - F_n(1-\alpha)]$$

(2.18)

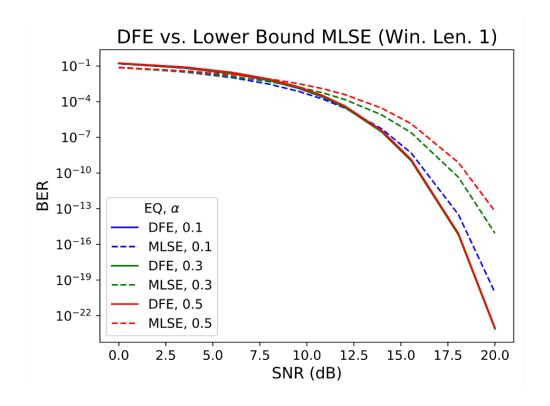

As shown in Figure 2.8, the lower-bound BER of the window length 1 MLSE is higher than that of the DFE across a wide range of  $\alpha$  values, which correspond to different channel losses. The DFE would out-perform any window length 1 architecture, as any realizable window length 1 architecture would have greater error probabilities than the lower-bound model. To find a viable alternative to the DFE, longer window lengths should be considered.

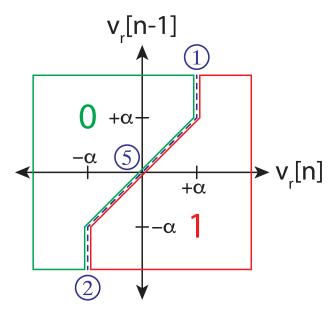

### 2.3.2 Window Length 2

Applying the same graphical approach as in the previous section, one can reduce the window decoding function for window length 2 architectures to the following set of lines, as shown in Figure 2.9. Since the decoding is a function of two adjacent voltage samples, the plot shows the current sample on the x-axis and the previous sample on the y-axis. The black dots represent ideal voltage states for each possible data pattern and form a subset of the space  $(\pm 1 \pm \alpha, \pm 1 \pm \alpha)$ . The dashed lines represent equidistant lines between the ideal states, where the exact linear equation for each threshold is expressed below:

① :

$$v_r[n] = \alpha$$

② :  $v_r[n] = -\alpha$

③ :  $v_r[n-1] = 1$

④ :  $v_r[n-1] = -1$

⑤ :  $v_r[n] = v_r[n-1]$

⑥ :  $v_r[n] = -\frac{1-\alpha}{\alpha}v_r[n-1] + 1$

⑦ :  $v_r[n] = -\frac{1-\alpha}{\alpha}v_r[n-1] - 1$

⑧ :  $v_r[n] = -\frac{1}{\alpha}v_r[n-1]$

<sup>&</sup>lt;sup>1</sup>Refer to Appendix A.1 for the full derivation.

Figure 2.8: Error statistics comparison between DFE and lower-bound MLSE (window length 1)

Computing the lower-bound error statistics of the window length 2, however, is trickier than those of the window length 1 due to the dependence in decoded windows. For a 1-tap window length 2 architecture, there are 3 overlapping windows for  $d_t[n]$ :

$$W(n) = f(v_r[n], v_r[n-1]) = g(d_t[n], d_t[n-1], d_t[n-2], v_n[n], v_n[n-1])$$

$$W(n+1) = f(v_r[n+1], v_r[n]) = g(d_t[n+1], d_t[n], d_t[n-1], v_n[n+1], v_n[n])$$

$$W(n+2) = f(v_r[n+2], v_r[n+1]) = g(d_t[n+2], d_t[n+1], d_t[n], v_n[n+2], v_n[n+1])$$

A brute-force approach would require 9 nested loops—5 for the transmitted data  $d_t[n [4], ..., d_t[n]$  and 4 for the noise  $v_n[n-3], ..., v_n[n]$ . For a discretized Gaussian distribution of B bins, the total number of iterations would be  $2^5B^4$ , which results in 100B to 1T iterations for typical number of bins. To reduce computational complexity, conditioning is applied to the noise distributions by partitioning the window decoding space, as illustrated in Figure 2.10. If the decoding is broken up at horizontal and vertical lines of threshold  $0, \pm \alpha, \pm 1$ , each rectangular region has at most 2 possible sequences that can be decoded.

Let the one-dimensional partitioning be represented by the following set of intervals  $A \in$  $\{(-\infty, -1), (-1, -\alpha), (-\alpha, 0), (0, \alpha), (\alpha, 1), (1, \infty)\}$ , where each tuple contains the lower and upper bounds of the interval. Suppose again without loss of generality that the transmitted

Figure 2.9: Window length 2 decoding with labeled thresholds (dashed)

data symbol  $d_t[n]$  is 1. As the transmitted data spans 5 UI across all overlapping windows, the 5-bit transmitted sequence  $d_x$  can be expressed as

$$d_x = [d_t[n-2], d_t[n-1], d_t[n], d_t[n+1], d_t[n+2]] = [x_1, x_2, 1, x_3, x_4]$$

where  $x = [x_1, x_2, x_3, x_4]$  represents a random vector of neighboring transmitted bits.

The lower-bound BER can be rewritten as a summation across all possible interval and data pattern combinations:

$$BER = P(W_3(n) = 0 \cap W_2(n+1) = 0 \cap W_1(n+2) = 0)$$

$$= \frac{1}{16} \sum_{x \in \{0,1\}^4} \sum_{(y_{min}, y_{max}) \in A^4} p_{r,1} p_{r,2} p_{r,3} p_{r,4} p_{w,0,0} p_{w,1,0} p_{w,2,0}$$

(2.19)

For  $i \in \{1, 2, 3, 4\}$ ,  $p_{r,i}$  represents the probability that the received voltage  $v_r[n+i-2]$  falls in the given interval  $(y_{min,i}, y_{max,i})$ :

$$p_{r,i} = P(v_r[n+i-2] \in (y_{min,i}, y_{max,i}) | d_t[n+i-2] = d_{x,i+1}, d_t[n+i-3] = d_{x,i})$$

For  $j \in \{0, 1, 2\}$ ,  $p_{w,j,b}$  represents the probability that  $W_{3-j}(n+j)$  (the overlapping bit in a decoded window) is the binary value  $b \in \{0, 1\}$ :

$$p_{w,j,b} = P(W_{3-j}(n+j) = b|d_t[n+j] = d_{x,j+3}, d_t[n+j-1] = d_{x,j+2}, d_t[n+j-2] = d_{x,j+1},$$

$$v_r[n+j] \in (y_{min,j+2}, y_{max,j+2}),$$

$$v_r[n+j-1] \in (y_{min,j+1}, y_{max,j+1}))$$

Figure 2.10: A partition of the window length 2 decoding into horizontal and vertical lines (green, dashed)

Since  $d_t$  is treated as a constant,  $v_r[n+i-2] = v_n[n+i-2] + v_{ideal}$ , where  $v_{ideal}$  is a direct function of the transmitted bits  $(\pm 1 \pm \alpha)$ .  $(y_{min}, y_{max})$  are also treated as constants, so  $p_{r,i}$  are all independent probabilities that condition the distribution of the received voltage according to the inequality  $y_{min,i} \leq v_r[n+i-2] \leq y_{max,i}$ . Once the conditional distributions of  $v_r$  are computed, they can be used to determine  $p_{w,j,b}$ .

Due to the partitioning strategy, computing  $p_{w,j,b}$  is fairly simple. Recall that  $p_{w,j,b}$  is related to the decoding of (3-j)th bit in window W(n+j), which depends on  $v_r[n+j]$  and  $v_r[n+j-1]$ . Based on which interval is currently being operated on, there are the following 3 scenarios:

- 1. Only 1 sequence can be decoded. If the bit of interest is b, then  $p_{w,j,b} = 1$  and the received voltage distributions remain unchanged. Otherwise,  $p_{w,j,b} = 0$ , zeroing out the whole term in the (2.19) summation.

- 2. 2 sequences can be decoded, but the bit of interest is same for both sequences. Then, this reduces to the above scenario where  $p_{w,j,b}$  is either 1 or 0.

- 3. 2 sequences can be decoded, and the bit of interest is different for the sequences. In this case, this region is linearly split between the two possible sequences by an inequality in the form of  $v_r[n+j] < A \cdot v_r[n+j-1] + B$ . Using the weight function approach from (2.11) (2.12) (2.13),  $p_{w,i,b}$  can be computed with conditional distributions on the received voltages.

However,  $p_{w,j,b}$  are not all independent of each other.  $p_{w,0,b}$  and  $p_{w,2,b}$  are independent since the former depends on  $v_r[n]$  and  $v_r[n-1]$  while the latter depends on  $v_r[n+2]$  and  $v_r[n+1]$ .  $p_{w,1,b}$  shares a dependence with the other 2 terms because it shares a dependence of  $v_r[n+1]$  with  $p_{w,2,b}$  and a dependence of  $v_r[n]$  with  $p_{w,0,b}$ . By first computing  $p_{w,0,b}$  and  $p_{w,2,b}$ , the resulting conditioned distributions of  $v_r[n]$  and  $v_r[n+1]$  can then be directly applied to  $p_{w,1,b}$ .

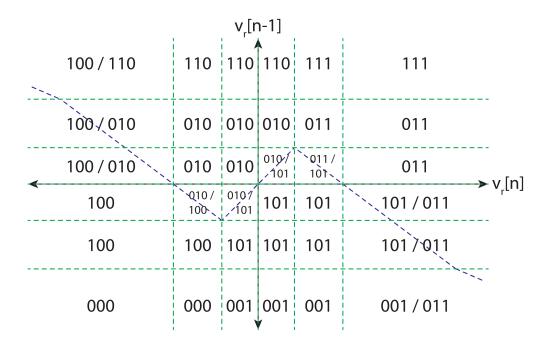

Compared to the DFE, "lower-bound" window length 2 MLSE has better or comparable error rates for most values of  $\alpha$  (Figure 2.11). Thus, window length 2 architectures could be promising alternatives to the DFE, but the key challenge is to develop a conflict resolution mechanism that is simple to implement in hardware while still retaining good error statistics.

Figure 2.11: Error statistics comparison between DFE and lower-bound MLSE (window length 2)

#### 2.3.2.1Majority Vote

Note that for window length 2, there are an odd number of overlapping windows that give information about the same bit. In the event of a conflict, the majority vote is the simplest approach since it only requires a few additional logic gates to resolve the conflict.

The error statistics of the majority vote design can be computed similarly to the lower bound case. Whereas the lower bound version required all windows to give the wrong bit, the majority vote design would error if at least 2 windows gave the wrong bit. In other words, the BER of the majority vote is

$$BER = P(W_3(n) = 0 \cap W_2(n+1) = 0 \cap W_1(n+2) = 0)$$

$$+ P(W_3(n) = 1 \cap W_2(n+1) = 0 \cap W_1(n+2) = 0)$$

$$+ P(W_3(n) = 0 \cap W_2(n+1) = 1 \cap W_1(n+2) = 0)$$

$$+ P(W_3(n) = 0 \cap W_2(n+1) = 0 \cap W_1(n+2) = 1)$$

$$= \frac{1}{16} \sum_{x \in \{0,1\}^4} \sum_{(y_{min}, y_{max}) \in A^4} p_{r,1} p_{r,2} p_{r,3} p_{r,4} (p_{w,0,0} p_{w,1,0} p_{w,2,0} + p_{w,0,1} p_{w,1,0} p_{w,2,0} + p_{w,0,0} p_{w,1,1} p_{w,2,0} + p_{w,0,0} p_{w,1,0} p_{w,2,1})$$

$$+ p_{w,0,0} p_{w,1,1} p_{w,2,0} + p_{w,0,0} p_{w,1,0} p_{w,2,1})$$

$$(2.20)$$

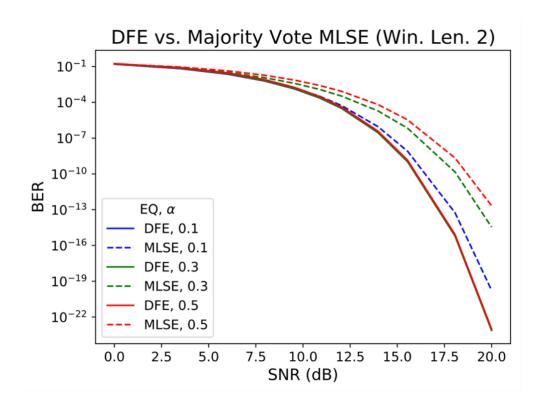

Figure 2.12: Error statistics comparison between DFE and majority vote MLSE (window length 2)

As shown in Figure 2.12, the majority vote design yields a higher BER than the DFE across all values of  $\alpha$ . The main disadvantage of the majority vote method is that all overlapping windows are weighted equally. However, lower loss channels typically have  $\alpha < 0.5$ , so each voltage sample at the receiver naturally retains more information about the currently transmitted bit than the previous bit. As  $\alpha$  decreases toward 0, the earliest window W(n) would contain most information about the current bit to be resolved, while the latest window W(n+2) contains least information and is more error-prone. In fact, of the 4 error cases in the majority vote analysis, the the dominant error term is  $P(W_3(n) = 1 \cap W_2(n+1) = 0 \cap W_1(n+2) = 0).$

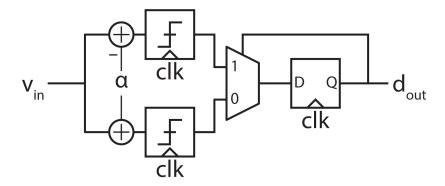

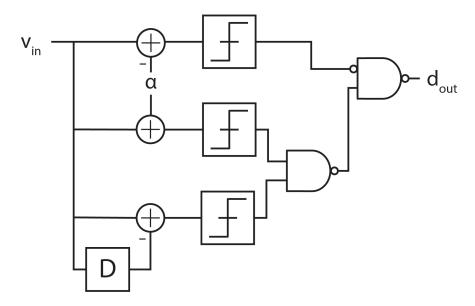

#### 2.3.2.2Single Window

The above phenomenon suggests that for lower loss channels, the earlier windows should be weighed more heavily than later windows when resolving conflicts. As a result, the proposed "single window" design resolves conflicts by always using the bit decoded by the earliest window. Doing so entirely removes interaction between overlapping windows, which simplifies both the statistical analysis and complexity of this equalizer. Since overlapping windows are no longer considered, each window only needs to decode its last bit, not the entire sequence. In other words, the window decoding reduces from Figure 2.9 to Figure 2.13.

Figure 2.13: Single window decoding for window length 2. A single bit is decoded: 1 if the received samples are in the red region, 0 if the green region

Suppose we define a slice function to mimic a comparator or slicer function:

$$\operatorname{slice}(x) \equiv \begin{cases} 1 & \text{if } x > 0 \\ 0 & \text{otherwise} \end{cases}$$

(2.21)

Then, the 3-line piecewise window decoding function  $W_{sing}(n)$  can be mathematically

represented as

$$W_{sing}(n) = \begin{cases} 1 & \text{if } v_r[n] > h_0 \\ 0 & \text{if } v_r[n] < -h_0 \\ \text{slice}(v_r[n] - v_r[n-1]) & \text{otherwise} \end{cases}$$

(2.22)

This function can be realized by using minimal circuitry consisting of a few comparators, adders, and logic gates shown in Figure 2.14. The  $\pm \alpha$  slicer thresholds are similar to those of the 1-tap loop-unrolled DFE, but an additional 2-tap FIR path is added. As a result, the adaptation algorithm of  $\pm \alpha$  thresholds is reused from that of the 1-tap loop-unrolled DFE, where the data thresholds are interpolated from an additional error slicer that adapts for  $1 \pm \alpha$  data levels (dLevs) based on 11/01 pattern filtering. The adaptation scheme will be discussed in more detail in Section 4.3.1.

Figure 2.14: Single window length 2 block diagram

With the reduced decoding function and lack of interaction between overlapping windows, the bit error rate can be computed as the following (again assuming the transmitted bit is 1):

$$BER = P(W_3(n) = 0) = P(v_r[n] < -\alpha \cup (-\alpha < v_r[n] < \alpha \cap v_r[n-1] > v_r[n]))$$

$$= \frac{1}{4} \sum_{x \in \{0,1\}^2} [P(v_r[n] < -\alpha | d_t[n-2] = x_1, d_t[n-1] = x_2, d_t[n] = 1)$$

$$+ P(-\alpha < v_r[n] < \alpha \cap v_r[n-1] > v_r[n] | d_t[n-2] = x_1,$$

$$d_t[n-1] = x_2, d_t[n] = 1)] \quad (2.23)$$

As shown in Figure 2.15, this design achieves comparable error rates to the DFE for  $\alpha < 0.3$  but falls off for larger values of  $\alpha$ .

Figure 2.15: Error statistics comparison between DFE and single window MLSE (window length 2)

#### 2.3.3 Window Length 3

The window decoding function showed a drastic increase in complexity from window length 1 to window length 2 architectures. Given the MLSE's known tendency for exponentially increasing complexity, window length 3 architectures seemed infeasible at first. However, with the discovery of the single window architecture, which could greatly simplify the decoding function, the single window approach was extended to window length 3 to determine whether the error statistics would improve for  $\alpha$  values beyond 0.3.

The window decoding function for the single window is shown below:

$$W_{sing}(n) = \begin{cases} 1 & \text{if } v_r[n] > h_1 \\ 0 & \text{if } v_r[n] < -h_1 \\ f(v_r) & \text{otherwise} \end{cases}$$

Note that the general form is the same as the window length 2 version (2.22). However, the "otherwise" condition is now replaced by a much more complex function f, as shown below:

$$f(v_r) = \begin{cases} f_1(v_r) & \text{if } (a_{(-\infty,-h_0)} \cap c_{>0}) \cup (a_{(h_0,\infty)} \cap c_{(2h_1,\infty)}) \cup (a_{(-h_0,h_0)} \cap b_{(h_1,\infty)}) \\ f_2(v_r) & \text{if } (a_{(h_0,\infty)} \cap c_{(-\infty,0)}) \cup (a_{(-\infty,-h_0)} \cap c_{(-infty,-2h_1)}) \cup (a_{(-h_0,h_0)} \cap b_{(-\infty,-h_1)}) \\ f_3(v_r) & \text{if } (a_{(h_0,\infty)} \cap c_{(0,2h_1)}) \\ f_4(v_r) & \text{if } (a_{(-\infty,-h_0)} \cap c_{(-2h_1,0)}) \\ f_5(v_r) & \text{if } (a_{(-h_0,h_0)} \cap b_{(-h_1,h_1)}) \end{cases}$$

$$f_1(v_r) = \text{slice}((1-\alpha)v_r[n] - v_r[n-1] + h_1)$$

$$f_2(v_r) = \text{slice}((1-\alpha)v_r[n] - v_r[n-1] - h_1)$$

$$f_3(v_r) = \text{slice}((1-\alpha)(v_r[n] - v_r[n-1]) + v_r[n-2] - h_1)$$

$$f_4(v_r) = \text{slice}((1-\alpha)(v_r[n] - v_r[n-1]) + v_r[n-2] + h_1)$$

$$f_5(v_r) = \text{slice}(v_r[n] - v_r[n-1] + v_r[n-2])$$

$$a_{(x,y)} \equiv v_r[n-2] \in (x,y)$$

$$b_{(x,y)} \equiv \alpha v_r[n-1] + (1-\alpha)v_r[n-2] \in (x,y)$$

$$c_{(x,y)} \equiv \alpha v_r[n-1] + v_r[n-2] \in (x,y)$$

Figure 2.16: Single window length 3 block diagram

The equivalent block diagram is depicted in Figure 2.16. Compared to the window length 2 version, the new decoding function requires > 4x comparators, which tend to be the most power-hungry.

The error statistics of the window length 3 variant is shown in Figure 2.17. This MLSE design now achieves similar BER as the DFE for  $\alpha < 0.5$ . However, this comes at a significant design complexity tradeoff.

Figure 2.17: Error statistics comparison between DFE and single window MLSE (window length 3)

#### 2.4 Equalizer Comparison and Conclusions

The MLSE algorithm is a powerful equalization algorithm that can theoretically achieve excellent error statistics. On the other hand, applying MLSE for ultra-high-throughput, energy-efficient links requires a simplification of the algorithm and removal of feedback loops, both of which degrade the statistical performance. Several variants of the feedforward MLSE were explored for different window lengths and conflict resolution mechanisms. Of these, the most promising designs were the single window architectures.

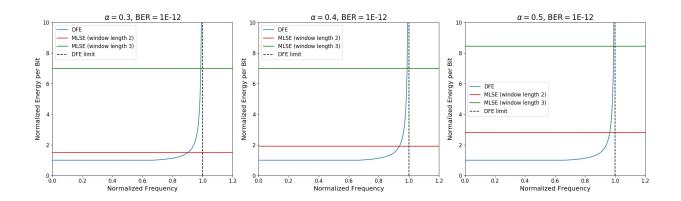

For given target channels and bit error rates, the energy-delay tradeoffs are compared across three equalizer designs: 1-tap loop-unrolled DFE, single window MLSE for length 2,

Figure 2.18: Equalizer tradeoffs

and single window MLSE for length 3 (Figure 2.18). The DFE's energy efficiency is modeled to asymptotically reach a maximum frequency limit, which is set by the critical path of the feedback loop and is technology-dependent. At high frequencies, self-loading effects dominate the overall power, resulting in the asymptotical behavior. The impact of self-loading on power consumption for similar circuits is analyzed in more detail in [8]. In contrast, the feedforward MLSE equalizers can be parallelized as needed and are approximated to be constant over frequencies.

Let  $C_{DFE}$ ,  $C_{MLSE,2}$ , and  $C_{MLSE,3}$  represent the base complexity of the three designs without pushing the design to its limits. In other words,  $C_{DFE}$  is normalized to 1 as in Figure 2.18. Assuming that comparators are the dominant source of power consumption,  $C_{MLSE,2} \approx 1.5$  and  $C_{MLSE,3} \approx 7$ .

Then, one can compute the SNR required to achieve the target BER. In particular, the SNR requirements of the MLSE designs can be computed relative to the DFE SNR reference. For error rates of  $10^{-12}$ , the MLSE designs may need anywhere from 0 to 3 dB higher SNR compared to the DFE. Assuming noise is dominated by kT/C noise, MLSE designs would need to be upsized to meet the required SNR. The additional power penalty due to noise considerations can be computed as follows:

$$P \propto C \propto \frac{1}{v_n^2} \propto SNR$$

$$N_{MLSE,2} \equiv \frac{P_{MLSE,2}}{P_{DFE}} = \frac{SNR_{MLSE,2}}{SNR_{DFE}}$$

$$N_{MLSE,3} \equiv \frac{P_{MLSE,3}}{P_{DFE}} = \frac{SNR_{MLSE,3}}{SNR_{DFE}}$$

(2.24)

The nominal power consumption of the MLSE designs are

$$P_{MLSE,2} = C_{MLSE,2} N_{MLSE,2} = 1.5 \times \frac{SNR_{MLSE,2}}{SNR_{DFE}}$$

$$P_{MLSE,3} = C_{MLSE,3} N_{MLSE,3} = 7 \times \frac{SNR_{MLSE,3}}{SNR_{DFE}}$$

Based on the energy-delay tradeoffs, the window length 2 is a better choice than the window length 3 across all cases. Although the window length 3 has superior error statistics for higher loss channels, its base complexity offsets much of its SNR advantages when it comes to evaluating the energy efficiency. This simple comparison, however, assumes that the receiver power is mainly dominated by the equalizer. If the MLSE is not the dominant source of power, the window length 3 could be more attractive in higher loss channels, as the entire receiver would usually need to be upsized to meet the SNR requirement. Furthermore, the asymptotic behavior of the DFE energy efficiency indicates that past its maximum achievable data rate, the feedforward MLSE could be key to implementing the wireline receiver.

# Chapter 3

# Design Techniques for a 160 Gb/s 1-Tap MLSE Datapath

### 3.1 Overview

A 160 Gb/s NRZ wireline receiver was designed in a 16 nm FinFET process to evaluate the energy efficiency and future promise of the feedforward MLSE equalizer. As discussed in the last chapter, the single window length 2 MLSE design is chosen for its lower power consumption over the window length 3 version.

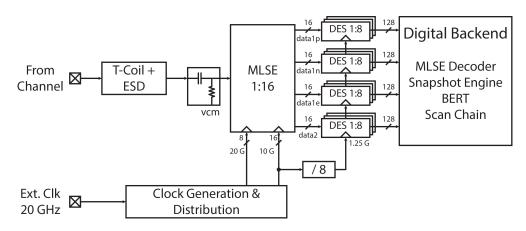

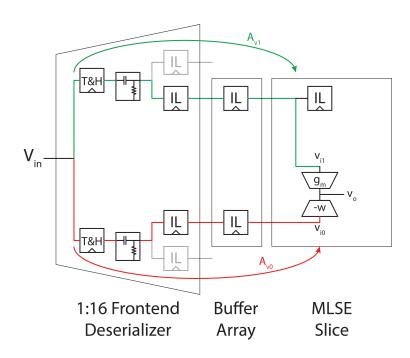

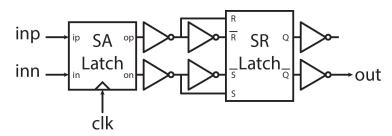

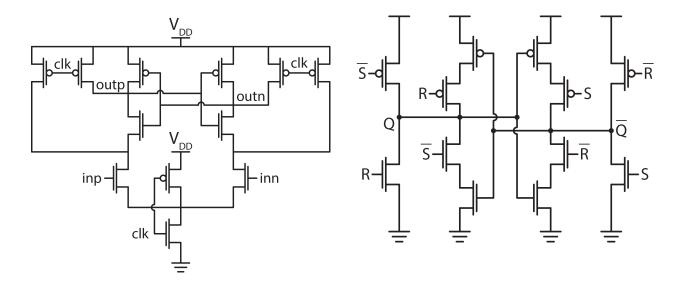

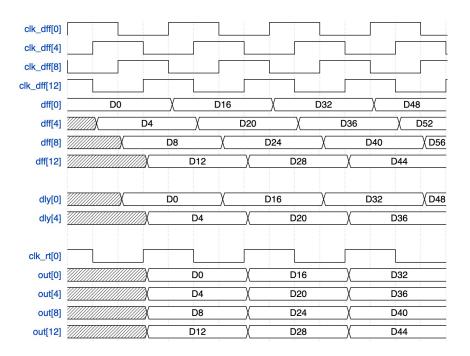

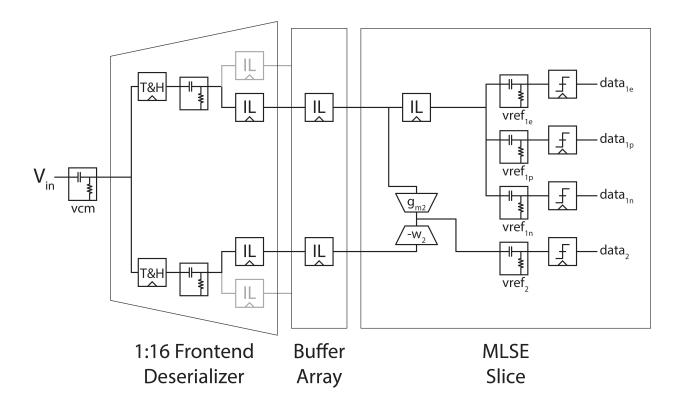

Figure 3.1: RX MLSE block diagram

The receiver block diagram is shown in Figure 3.1. To further reduce power, the equalization is primarily implemented in the analog and mixed-signal (AMS) domain, removing the need for a high-speed ADC. To achieve the desired throughput, the MLSE equalizer is implemented as 16 time-interleaved slices, each effectively working at 10 GS/s. Recall from Figure 2.14 that one slice consists of 3 comparator outputs ("data1p", "data1n", "data2" in Figure 3.1), which are passed into some digital logic for decoding. As is the case with the

1-tap loop-unrolled DFE, an additional error slicer must be added to adapt the  $1 \pm \alpha$  dLev. For the MLSE, this is added as a 4th comparator with output "data1e". These signals are then describilized by an additional factor of 8 and connected to the synthesized logic, which consists of the MLSE decoder and testing modules. A custom-digital decoder operating at 10 GS/s would halve the number of describilizers required, as each slice would only need to output 2 signals—one data and one error for datapath calibration. In addition, the decoder latency would be reduced from  $\sim$ 128 UI to  $\sim$ 16 UI. However, latency was not critical to this design, and having all comparator outputs simultaneously available for off-chip testing procedures increased visibility and debug capability for the test chip.

Although parallelism eases the implementation of the feedforward MLSE equalizer, the frontend circuits must still operate at full bit rate and can be the bottleneck to link performance. Inductive peaking circuits have thus been used in SerDes frontend designs to improve bandwidth and return loss performance [9, 10]. In particular, this work's passive frontend was designed by Kunmo Kim and features a T-coil design, whose detailed analysis can be found in [11, 12].

As data rates approach the limits of the process node, device and routing parasitic effects can significantly degrade the link performance. Building such a high-speed link requires numerous design iterations, from device sizing to floorplanning. To improve designer productivity, the receiver was designed using a generator framework called Berkeley Analog Generator (BAG) [13, 14]. Once a user codifies a circuit's design process into a configurable generator, this design methodology enables an agile workflow through the automatic creation and post-layout characterization of parameterized instances. Furthermore, complex design rules in advanced process nodes require greater physical design effort to pass design rule checking (DRC). Generated instances will often be DRC-clean with little to no manual changes, making BAG attractive for advanced-node IC designs.

Developing a robust circuit generator, however, can take significant time. If one does not yet exist for the desired circuit, designers must consider the upfront effort of generator development. As a result, the generator-based design flow is most effective for circuits which must be critically optimized for power performance area (PPA) and thus is used extensively in the proposed receiver.

# 3.2 Analog Datapath Architecture

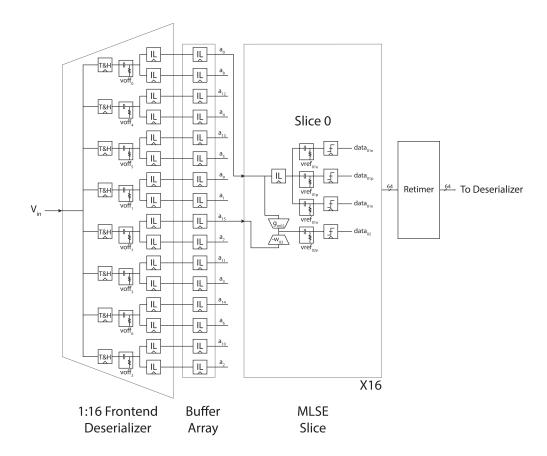

A 16-way interleaved MLSE equalizer requires a 1:16 frontend deserializer. This deserializer is implemented in 2 stages to reduce loading at the input. Instead of equal 4x deserialization for each stage, the first stage interleaving ratio is set as 8 because distributing octa-rate (20 GHz) clocks would be more energy-efficient than quad-rate (40 GHz) clocks in the given technology node.

The MLSE slice contains 2 parallel integrating paths. The first path consists of a gain stage, which drives the  $\pm \alpha$ -threshold data comparators. Because the error slicer on this path must compare its input against  $1 + \alpha$ , the gain stage must have enough linear range to drive

Figure 3.2: MLSE analog datapath block diagram

large signals. The second path consists of the 2-tap FIR, where the previous analog sample is subtracted from the current sample. The output linearity constraints on this FIR/summer path are much more relaxed, as the slicer compares against differential zero.

Due to the 2-tap FIR structure, the descrialized 16-way signals must be shuffled around the slices in the array. The 16 slices are physically tiled in a specific order to minimize the longest routing distance, but the routing tends to increase linearly with number of interleaved ways. The routing parasitics increase the load capacitance driven by the 8:16 descrializer. To manage the larger fanout, an additional gain stage is inserted between the descrializer and MLSE slice as an analog buffer.

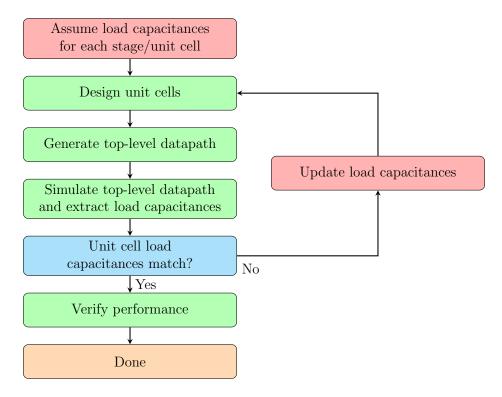

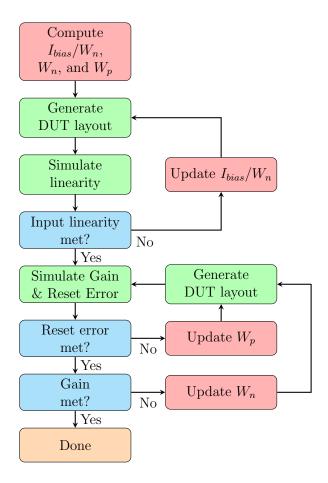

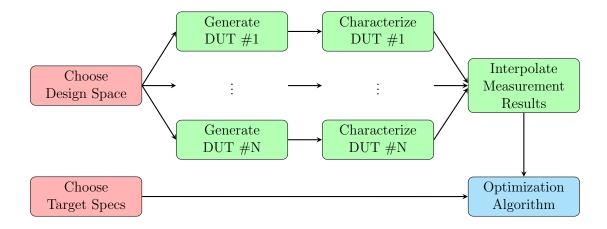

Because routing parasitics can often dominate load capacitances and limit circuit performance, the datapath design and floorplaning must be iterated with post-layout simulations. The entire datapath was written as a BAG generator, which allowed for quick design iteration as parameters like device sizing and wire spacing were updated. The design flow is shown in Figure 3.3. First, load capacitances are estimated for each stage of the signal chain. The unit cells are independently optimized with these loading constraints, and the top-level datapath is generated based on each unit cell design. A post-layout transient simulation of

the datapath can be used to extract total load capacitances seen by each stage, which are compared with the original estimates. If there is a difference between the assumed and actual load conditions, the unit cells are re-designed with the new loads and the design process repeats. Once this loop converges and the top-level load capacitances match the unit cell load specifications, a final sign-off check is run and the datapath design is complete.

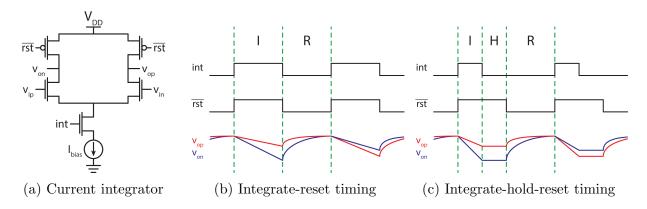

Figure 3.3: Datapath design flow