## **Building Trusted Execution Environments**

Dayeol Lee

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-96 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-96.html

May 13, 2022

Copyright © 2022, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### **Building Trusted Execution Environments**

by

### Dayeol Lee

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Krste Asanović, Chair Professor Dawn Song Professor Sanjit A. Seshia Professor Chia-Che Tsai

Spring 2022

## **Building Trusted Execution Environments**

Copyright 2022 by Dayeol Lee

#### **Abstract**

#### **Building Trusted Execution Environments**

by

#### Dayeol Lee

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Krste Asanović, Chair

Trusted Execution Environments (TEEs) offer hardware-based isolation, which protects the integrity and confidentiality of the in-use data of programs against various threats. Many hardware vendors have produced various TEE-enabled chips. However, there has been only a little public research on building TEEs. Building a TEE with different threat models and functionalities relies on design-space exploration. For example, a TEE must quickly adapt to various evolving threat models. In addition, a TEE can have different functionality requirements, which should not impact security guarantees. This thesis discusses research challenges in exploring the TEE design space. First, this thesis motivates why a TEE should not have a fixed threat model by demonstrating a novel off-chip side-channel attack on a TEE. Next, this thesis proposes Keystone, a software framework that enables building TEEs based on various needs, such as threat models and functionality requirements. Furthermore, this thesis discusses how to extend TEE functionality without breaking security guarantees using incremental verification.

To my family and my wife.

In loving memory of my grandmother,

Soonkeum Ko (1934-2021),

who will be very proud of me.

## **Contents**

| C  | Contents                 |                                                    |                       |

|----|--------------------------|----------------------------------------------------|-----------------------|

| Li | st of ]                  | Figures                                            | iv                    |

| Li | st of                    | Tables                                             | vii                   |

| 1  | 1.1<br>1.2<br>1.3<br>1.4 | Trusted Execution Environments (TEEs)              | 1<br>1<br>2<br>3<br>4 |

| 2  | Bac                      | kground                                            | 6                     |

|    | 2.1<br>2.2<br>2.3        | The History of TEEs                                | 6<br>8<br>10          |

| 3  | Wh                       | y Your Threat Model Might Be Wrong                 | 13                    |

|    | 3.1                      | Introduction                                       | 13                    |

|    | 3.2                      | Why an Off-Chip Side Channel Matters?              | 17                    |

|    | 3.3                      | Membuster: an Off-Chip Side-Channel Attack on SGX  | 19                    |

|    | 3.4                      | Increasing Critical Cache Misses                   | 26                    |

|    | 3.5                      | Extracting Sensitive Access Patterns               | 32                    |

|    | 3.6                      | Attack Results                                     | 34                    |

|    | 3.7                      | Implications and Limitations                       | 40                    |

|    | 3.8                      | Summary                                            | 42                    |

| 4  | Key                      | stone: An Open Framework for Building TEEs         | 43                    |

|    | 4.1                      | Introduction                                       | 43                    |

|    | 4.2                      | What is a Common Base for Diverse TEEs?            | 45                    |

|    | 4.3                      | Keystone Design Overview                           | 49                    |

|    | 4.4                      | Security Monitor Design for Multiple Threat Models |                       |

|    | 4.5                      | Modular Runtime Design for Extensive Functionality | 60                    |

|    | 4.6              | Security Analysis                           | 62        |

|----|------------------|---------------------------------------------|-----------|

|    | 4.7              | Evaluation                                  | 64        |

|    | 4.8              | Related Work                                | 73        |

|    | 4.9              | Summary                                     | 74        |

| 5  | Agil             | e and Secure Implementation of New Features | <b>76</b> |

|    | 5.1              | Introduction                                | 76        |

|    | 5.2              | Formal Reasoning about TEE                  |           |

|    | 5.3              | Enabling Enclave Memory Sharing             | 79        |

|    | 5.4              | Formal Model                                | 84        |

|    | 5.5              | Proving Formal Security Guarantees          | 94        |

|    | 5.6              | Implementation in RISC-V Keystone           | 98        |

|    | 5.7              | Evaluation                                  | 98        |

|    | 5.8              | Implications and Limitations                | 103       |

|    | 5.9              | Summary                                     | 103       |

| 6  | Con              | clusion and Future Work                     | 104       |

|    | 6.1              | Contributions                               | 104       |

|    | 6.2              | Future Work                                 | 105       |

| Bi | Bibliography 107 |                                             |           |

# **List of Figures**

| 1.1        | A 2-Dimensional Design Space of TEEs                                                                                                                                                                                                                                                                                      | 2      |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2.1<br>2.2 | The history of Trusted Execution Environments from mobile devices to cloud computing Traditional vs. TEE based software stacks                                                                                                                                                                                            | 7<br>9 |

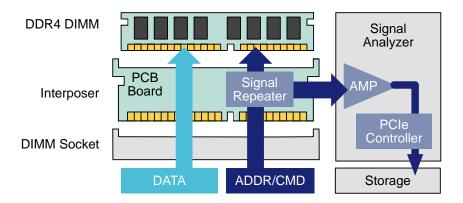

| 3.1        | On-chip side channels compared to Membuster. The cache side-channel attack leaks addresses through a shared cache, whereas the controlled-channel attack uses adversarial memory management. Membuster leaks addresses directly through the off-chip memory bus. The photo shows an example hardware setup for the attack | 14     |

| 3.2        | Hardware setup for a memory bus side-channel attack. DIMM interposer collects the bus signals and sends them to the signal analyzer. The attacker can use the analyzed                                                                                                                                                    |        |

| 2.2        | signals to learn the memory access pattern of the victim                                                                                                                                                                                                                                                                  | 20     |

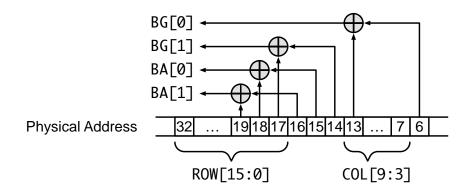

| 3.3        | The reverse engineered addressing function of the i5-8400 CPU. The function translate a physical address to the Bank Group (BG), Bank Address (BA), Row (ROW) and Column                                                                                                                                                  |        |

|            | (COL) within the DRAM                                                                                                                                                                                                                                                                                                     | 23     |

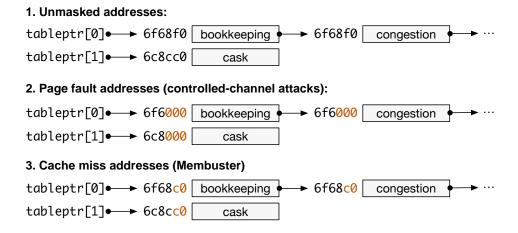

| 3.4        | The Hunspell code with a data-dependent access pattern                                                                                                                                                                                                                                                                    | 24     |

| 3.5        | Observable address patterns in Hunspell by different attacks. Controlled-channel attacks only see page-fault addresses without the lower 12 bits, whereas Membuster can                                                                                                                                                   |        |

|            | see LLC-miss addresses without the lower 6 bits.                                                                                                                                                                                                                                                                          | 24     |

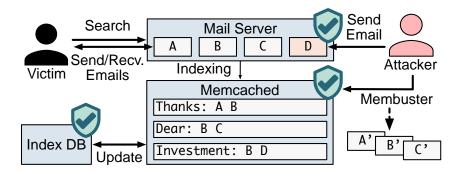

| 3.6        | An example attack scenario where a mail server uses Memcached as an index database.                                                                                                                                                                                                                                       |        |

|            | A, B, C and D are the emails                                                                                                                                                                                                                                                                                              | 26     |

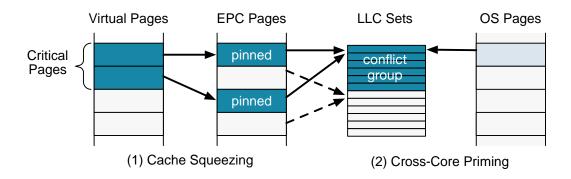

| 3.7        | Techniques used to increase the cache miss rate with minimal performance overhead                                                                                                                                                                                                                                         | 29     |

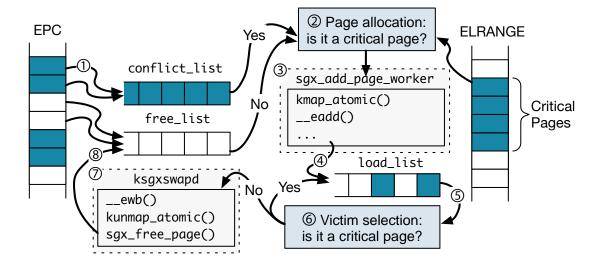

| 3.8        | Implementation of critical page whitelisting and cache squeezing in a modified SGX                                                                                                                                                                                                                                        |        |

|            | driver. To ensure no swapping in the sensitive memory range, EPC pages are set aside                                                                                                                                                                                                                                      |        |

|            | in a separate queue. The attackers can further select the EPC pages based on set indexes                                                                                                                                                                                                                                  |        |

| 2.0        | or other logistics.                                                                                                                                                                                                                                                                                                       | 31     |

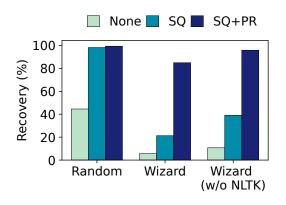

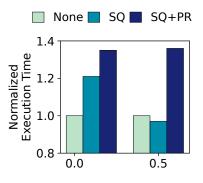

| 3.9        | Hunspell document recovery rate (left) and normalized execution time (right) on two documents: Random document (Random) and Wizard of Oz (Wizard). The compar-                                                                                                                                                            |        |

|            | ison is between without any techniques (None); with cache squeezing(SQ); and with                                                                                                                                                                                                                                         |        |

|            | cache squeezing and cross-core priming (SQ+PR). The Wizard of Oz results also show                                                                                                                                                                                                                                        |        |

|            | the recovery rate of uncommon words only (w/o NLTK)                                                                                                                                                                                                                                                                       | 37     |

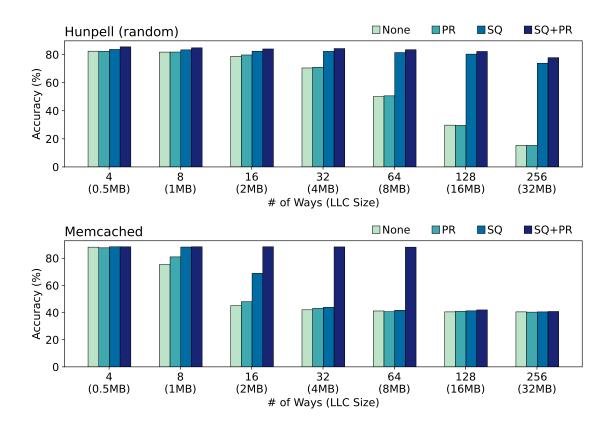

| 3.10       | Simulation results of the attack on Hunspell (top) and Memcached (bottom)                                                                                                                                                                                                                                                 | 39     |

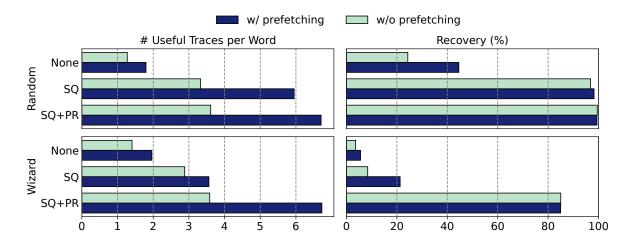

| 3.11 | The number of useful traces per word and the document recovery rate for each experiment (with or without the hardware prefetcher)                                                                                                                                                                                                                                                                                           | 9 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

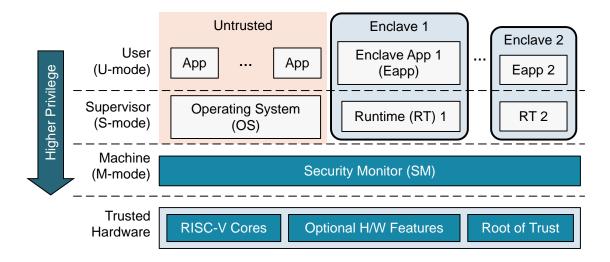

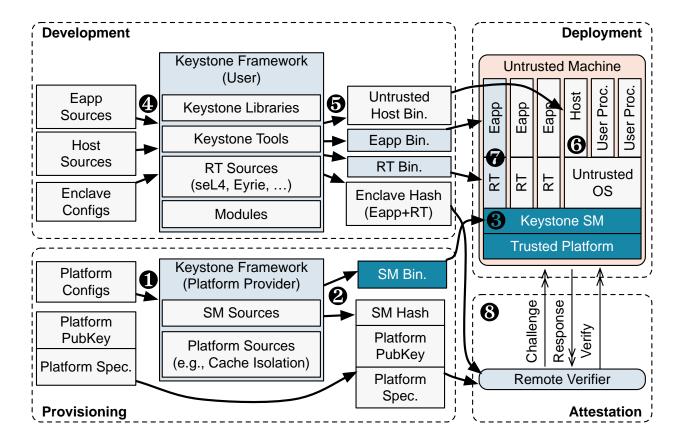

| 4.1  | Keystone system with host processes, untrusted OS, security monitor, and multiple enclaves (each with runtime and eapp)                                                                                                                                                                                                                                                                                                     | 7 |

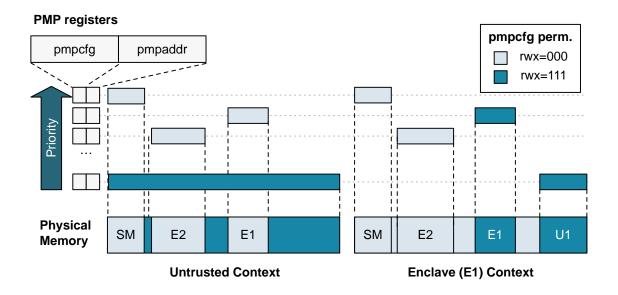

| 4.3  | attest based on known platform specifications, keys, and SM/enclave measurements 5 How Keystone uses RISC-V PMP for the flexible, dynamic memory isolation. pmpaddr and pmpcfg control and status registers (CSRs) are used to specify PMP entries. The SM uses a few PMP entries to guard its own memory (SM) and enclave memories (E1, E2). Upon enclave entry, the SM will reconfigure the PMP such that the enclave can |   |

| 4.4  | only access its own memory (E1) and the untrusted buffer (U1)                                                                                                                                                                                                                                                                                                                                                               | 4 |

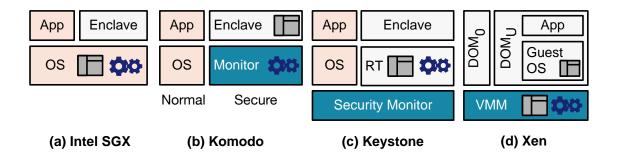

| 4.5  | page table. (d) Hypervisor for page management, 2 page tables                                                                                                                                                                                                                                                                                                                                                               |   |

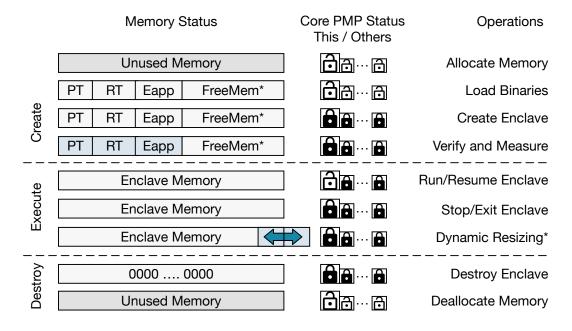

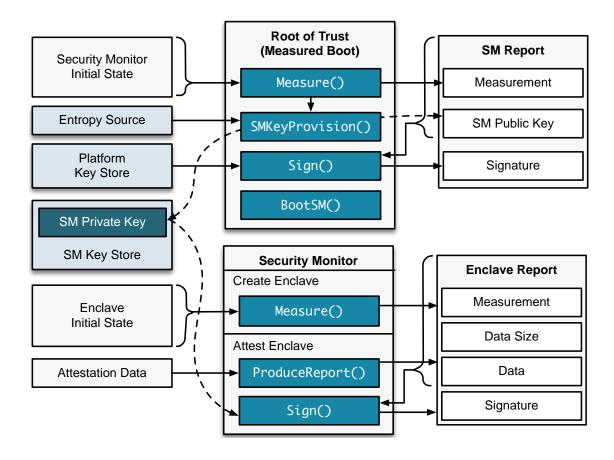

| 4.6  | status of the core performing the operation and <i>Others</i> is PMP of other cores 50 Measured boot and attestation in Keystone. All of the root-of-trust functions are trusted, whereas the security monitor functions are trusted given the SM report ver-                                                                                                                                                               | 5 |

| 4.7  | ification succeeds                                                                                                                                                                                                                                                                                                                                                                                                          | 8 |

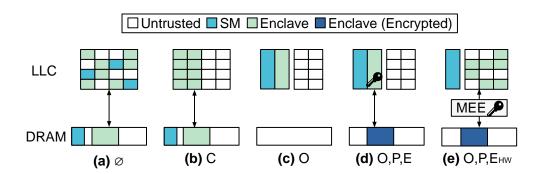

| 4.8  | ware memory encryption                                                                                                                                                                                                                                                                                                                                                                                                      | 8 |

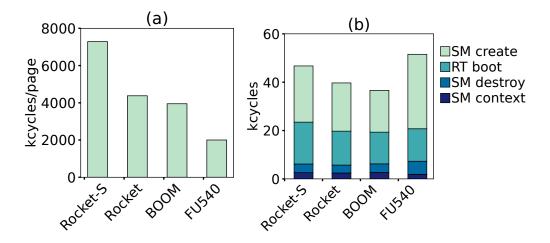

| 4.9  | in (a)) and memory cleaning in destroy (4K-11K cycles/page)                                                                                                                                                                                                                                                                                                                                                                 | 7 |

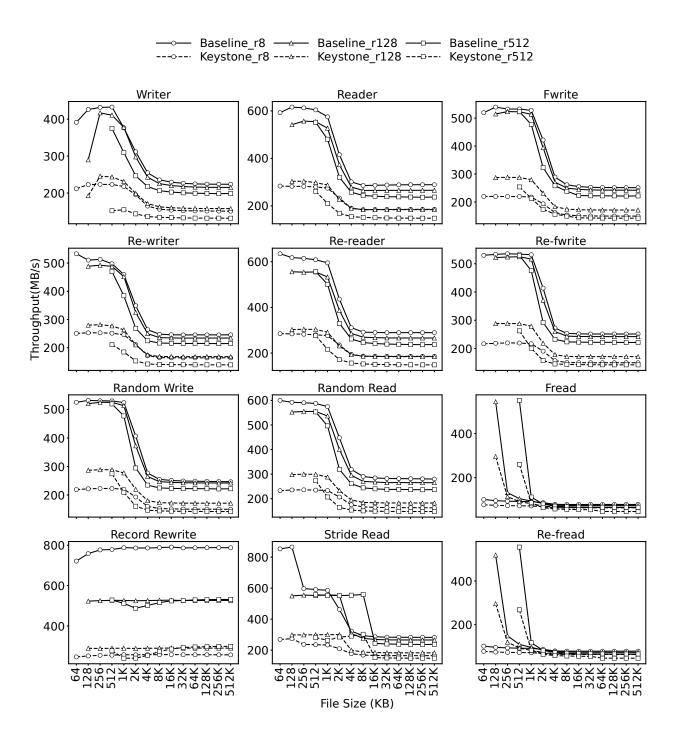

|      | 8KB record)                                                                                                                                                                                                                                                                                                                                                                                                                 | 9 |

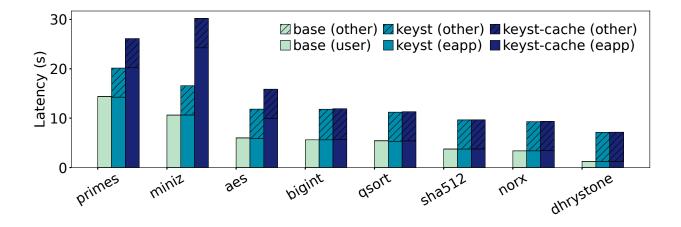

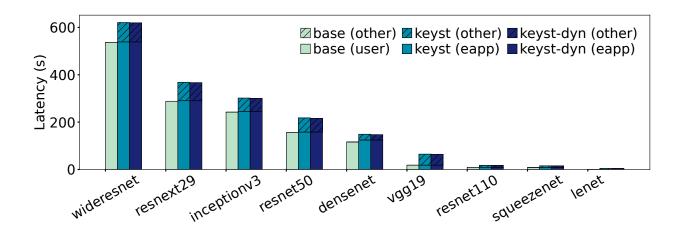

| 4.11 | stone with cache partitioning (keyst-cache) compared to native execution (base) 70 Inferencing time for various Torch models. Each bar consists of the duration of the application (user or eapp), and the other overheads (other). Keystone (keyst) and                                                                                                                                                                    | 0 |

|      | Keystone with the dynamic resizing (keyst-dyn) compared to native execution in (base)                                                                                                                                                                                                                                                                                                                                       | 2 |

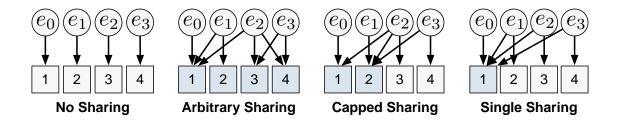

| 5.1 | Memory sharing models with varying flexibility. Blue (and white) boxes indicate                                                     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|

|     | shareable (and non-shareable) physical memory region, and circles indicate enclaves.                                                |

|     | An edge from an enclave to a physical memory is an access relation stating that an                                                  |

|     | enclave can access the memory it points to                                                                                          |

| 5.2 | A user provisions their (protected) enclave $e$ in the remote enclave platform isolated                                             |

|     | from untrusted software. Green/red boxes indicate trusted/untrusted components 85                                                   |

| 5.3 | Illustrating the execution of two traces of the platform in the secure measurement,                                                 |

|     | integrity and confidentiality proofs. Proof obligations for each property are checked                                               |

|     | as indicated by $\approx_{\mathcal{L}}$ and equal initial condition indicated as $\approx_{\mathcal{L}}$ . $op^i$ indicates enclave |

|     | execution of an operation from $\mathcal{O}$ at step $i$ and $\mathcal{A}$ indicates an adversary execution 89                      |

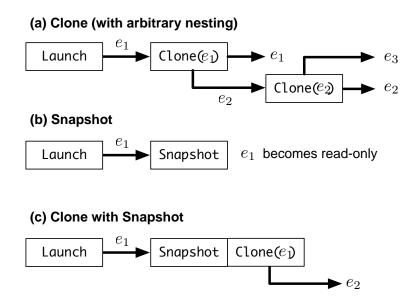

| 5.4 | Clone, Snapshot, and Clone with Snapshot                                                                                            |

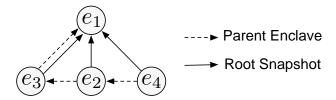

| 5.5 | Parent-child relationship and root snapshot-child relationship of four enclaves in Cer-                                             |

|     | berus. Enclave $e_1$ is a snapshot and parent enclave of $e_2$ , which is the parent of $e_3$ ,                                     |

|     | which is the parent of $e_4$ . Despite the nested parent relationship, the root snapshot of                                         |

|     | $e_2, e_3$ , and $e_4$ are $e_1$                                                                                                    |

| 5.6 | Model Statistics and Verification Times                                                                                             |

| 5.7 | C code to measure fork latency                                                                                                      |

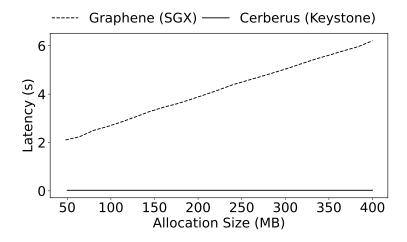

| 5.8 | The latency of fork with respect to the size of the allocated memory                                                                |

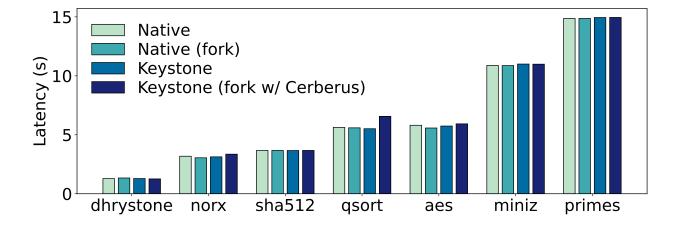

| 5.9 | Computation Overhead on RV8. Native: native execution of the original RV8, Native                                                   |

|     | (fork): native execution of the modified RV8 with fork, Keystone: enclave execu-                                                    |

|     | tion of the original RV8, and Keystone (fork w/ Cerberus): enclave execution of the                                                 |

|     | modified RV8 with Cerberus                                                                                                          |

## **List of Tables**

| 3.1        | This work (Membuster) compared to previous side-channel attacks on SGX. The two boldface rows illustrate the most important distinctions. The colored cell indicates the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.0      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.2        | attacker has the advantage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16       |

| 3.2<br>3.3 | Hardware specification for the experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35<br>37 |

| 4.1        | Trade-offs in existing TEEs/extensions. •, •, •, •: best to worst respectively. C3-6: resilience to software adversary, hardware adversary, side-channel adversary, controlled-channel adversary respectively. indicates complete protection; confidentiality only; no protection. C7: zero; thousands LoC; millions LoC. C8: zero; non-zero hardware; micro-architectural modifications. C9: enclave self resource management; partial; no flexibility. C10: range of apps supported are maximum; specific class; only written from scratch. C11: expressiveness includes forking, multi-threading, syscalls, shared memory; partial; none of these. C12: dev-effort for porting is unmodified binaries; |          |

|            | compiling and/or configuration files; re-writing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46       |

| 4.2        | The SBI functions the SM provides, *SM can provide additional functions (e.g., dy-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 4.0        | namic resizing) depending on the platform.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54       |

| 4.3<br>4.4 | TCB Breakdowns for the Eyrie RT and SM features in LoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66       |

| 4.5        | estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67<br>70 |

| 4.6        | Torch model specification, workload characteristics, binary object size, and total en-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70       |

| 4.0        | clave memory usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72       |

| 5.1        | Glossary of Symbols used for Chapter 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83       |

| 5.2        | Description of TAP State Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88       |

| 5.3        | Description of TAP $\mathcal{E}_M$ enclave metadata record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88       |

### Acknowledgments

My journey toward a Ph.D. has been full of excitement, but also there were lots of challenges and difficulties. I would not have completed the journey successfully without immeasurable support and assistance from my colleagues, friends, and family.

First, I would like to express my sincere appreciation to my advisor, Krste Asanović. Krste allowed me to be a part of a great research group and provided his best advice that immensely helped me. He always encouraged me to do research I am passionate about. Thankful for the advice, I was able to explore many different exciting topics, including security, architecture, and systems. I am also deeply indebted to Dawn Song. Dawn was my unofficial adviser, who constantly motivated and encouraged me throughout my Ph.D. Dawn always inspired me whenever I felt demotivated or frustrated. Without her encouragement, I would not have gone through the difficulties. I would like to thank Sanjit A. Seshia and Raluca Ada Popa for providing their best guidance and helpful feedback on many research projects. Sanjit never hesitated to spend his time giving very detailed feedback, which helped me gain a lot of insights into formal methods. Raluca made me fascinated by my first security research project and provided her full support. Without her, I may not have started security research. I would like to appreciate all faculty for their profound belief in my work and unparalleled support.

I also would like to thank David Kohlbrenner, Shweta Shinde, and Chia-Che Tsai for being my academic mentors when they were at UC Berkeley. I was very fortunate to work with them and learn many things. For example, I learned about coloring diagrams for colorblindness, academic integrity, and rigorous security analysis from David; writing techniques, presentation skills, and stress management from Shweta; and engineering skills, critical thinking, and systems knowledge from Chia-Che. As those who have already gone through Ph.D., David, Shweta, and Chia-Che shared knowledge and provided valuable advice, not to mention their invaluable contributions to the papers.

It was a great pleasure to work closely with many great people. I wish to thank Kevin Cheang for collaboration throughout the writing of the dissertation. He was very dedicated to all of the projects we collaborated on and provided insightful suggestions and unwavering assistance. He also prevented my Ph.D. life from being boring. I thank Alexander Thomas, Catherine Lu, Gui Andrade, and Stephan Kaminsky for contributing to the Keystone project, Ian Fang for contributing to the Membuster project, and Pranav Gaddamadug and Cameron Rasmussen for contributing to the formal verification projects. Special thanks to Alex and Cathy for contributing so much to Keystone and helping me submit a paper during their busiest times.

I would also like to extend my gratitude to incredible people in the ADEPT, RISE, and other labs, including Alon Amid, David Biancolin, Aditya Chopra, Hasan Genc, Abraham Gonzalez, Ameer Haj Ali, Qijing Jenny Huang, Adam Izraelevitz, Sagar Karandikar, Hansung Kim, Jack Koenig, Kyle Kovacs, Seah Kim, Donggyu Kim, Kevin Laeufer, Eric Love, Martin Maas, Albert Magyar, Howard Mao, Albert Ou, Nathan Pamberton, Arya Reais-Parsi, Colin Schmidt, Edward Wang, Lisa Wu, and Jerry Zhao. I thank all lab administrators and staff at the EECS department for creating inclusive and productive working environments.

My internships at Intel and Google have also helped me write this dissertation. I would like to thank Mona Vij, Anjo Vahldiek-Oberwagner, and Dmitrii Kuvaiski for having me at Intel Labs and providing me with challenging research projects for TEEs. Special thanks to Mona and Anjo for continuing collaboration after the internship and giving constructive advice. I thank Satnam Singh, Jade Philipoom, and Ben Blaxill for having me at Google and allowing me to participate in the SilverOak project. I could learn a lot about the formal reasoning of low-level software. I also thank my internship buddy Samuel Gruetter, who spent his valuable time teaching me Coq.

Finally, I dedicate my thesis to my family and my wife. I thank my parents, Gwanhee and Jeongsook, and my sister, Hajung, for supporting me and believing in me. My parents taught me to always live my own life and do my best, which made me who I am today. My wife, Seoyeon, has been standing by me throughout all my struggles, difficulties, and accomplishments. I love you, I am grateful to have you in my life.

## **Chapter 1**

## Introduction

### 1.1 Trusted Execution Environments (TEEs)

Remote computation has gained popularity along with the digitalization of everything. A massive amount of user data is generated every second, transferred to the cloud, and processed to create new values. In the last decade, the shift toward cloud computing [14, 25] has also been amplified not only by its cost efficiency, reliability, and programmability, but also by many resource-hungry applications such as machine learning and data analytics. The remote computation pandemic has raised one of the most challenging research problems: protecting remote data during computation.

Researchers have put an immense effort into protecting data in use. Traditionally, privileged software such as the operating system (OS) protects the in-use data by isolating virtual address spaces. However, such software-based isolation is not sufficient for remote computation for two reasons. First, the software could have been modified by someone who can physically access the remote device. For example, a cloud provider can install an arbitrary OS on their machines and provide them to customers. Second, even if software is trusted, it could have been compromised by other tenants or attackers. In either case, the data owners are unable to detect the software compromise, leading to the complete loss of control over their data. A few promising solutions are to use cryptographic technologies such as homomorphic encryption (HE) [69] or multi-party computation (MPC) [71, 223], which allow remote computation while keeping inputs and outputs encrypted. As they rely on mathematically hard problems, they offer near-perfect confidentiality and integrity of remote data. However, they are often a few orders of magnitude slower than native computation, even with state-of-the-art hardware acceleration [170].

Alternatively, *Trusted Execution Environments* (TEEs) [126, 53, 65, 13, 96, 110, 50] can fill the gap by combining hardware-based isolation mechanisms with efficient cryptographic schemes. TEEs are isolation technology that uses various hardware mechanisms, usually combined with low-level trusted software, to evict unnecessary code from the trusted computing base (TCB). In a nutshell, TEEs aim to protect code integrity, data integrity, and data confidentiality from various software adversaries, including a compromised OS. In general, TEEs provide a program with an exclusive memory region where the program can reside. TEEs use hardware mechanisms

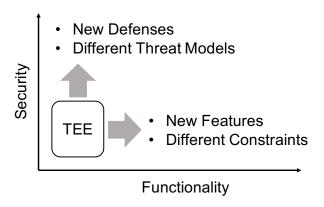

Figure 1.1: A 2-Dimensional Design Space of TEEs

to protect the memory so that even privileged software cannot arbitrarily read from or write to the memory. TEEs also arbitrate all context switches of the program, making the execution context entirely obscure to the rest of the system. Additionally, most TEEs offer remote attestation, which allows the user of the TEE to cryptographically verify that the program has been initialized and isolated. Remote attestation allows the user to securely launch remote programs and provision secrets without trusting privileged software.

All major CPU vendors have introduced TEE-equipped processors (e.g. ARM Confidential Compute Architecture [12], Intel SGX [126], and AMD SEV [6]). They differ in some design decisions, yet share the same idea: hardware-based isolation for a small TCB. Recent years have seen a wide range of efforts to migrate existing programs into those TEEs [209, 158, 160, 142, 146]. Many studies have also shown that TEEs can protect cloud services [24, 15], databases [160], big-data computations [178, 57, 33], secure banking [114], blockchain consensus protocols [116, 130, 161], smart contracts [228, 47, 26], machine learning [142, 202, 232, 156, 106], and network middleboxes [72, 73], to mention a few. The demand for confidential remote computation will continue to grow and necessitate TEEs in almost all processors in the next decade.

## 1.2 Challenges of Building TEEs

Although many hardware vendors have already built TEEs in their commercial products, there has been little public research on designing and building them. On the other hand, building TEEs involves rigorous security analysis and design-space exploration, which involves many research questions. How to build a trustworthy TEE without relying on a single company? What is a reasonable threat model? How to build a TEE resilient to side-channel attacks? How to reduce the cost of building TEEs? The thesis focuses on a few research challenges in the TEE design space exploration (Figure 1.1).

**Threat Model.** Each vendor TEE has a particular threat model that fits a specific use case. However, there is no industrial or academic consensus on what minimum adversary capabilities to consider for a TEE. Early decisions on the threat model can influence the design for a long time. For example, Intel SGX [126] insists on not defending against side-channel attacks. As a result, SGX is broken every year by side-channel attacks, including destructive ones [35, 219, 109, 212, 176, 135, 177, 175].

**Customizability.** Existing TEEs are delicate to customize, as they do not allow programmers to customize their TEE based on workload. It is difficult to analyze the trade-offs of different design decisions. Many workload characteristics, such as memory access pattern, working-set size, and concurrency, affect workload performance. Thus, a TEE must provide a modular and flexible design that can benefit wide-ranging workloads.

A Lack of Open Implementation. The lack of research on designing and building TEEs can be attributed to the lack of open implementation. Most vendor TEEs leverage proprietary hardware implementations, which prevents researchers from analyzing or modifying the design. Thus, many studies have relied on a few public documents published by the companies to gain only little knowledge of internal details. Therefore, exploring the design space is often limited to modifying a small part of TEE [218, 113] or software around TEE [209, 24, 184, 146]. In addition, a lack of open implementation means a lack of trust; it is precarious to fully trust a proprietary TEE implementation driven by a single company.

**Secure Modification.** Exploring the design space of TEEs involves not only threat models but also functionality and performance requirements. However, a patch for new functionality or performance improvement should not affect TEE security. Thus, a TEE needs to support an efficient modification and verification flow to support various workloads and platforms.

## 1.3 Summary of Research Contributions

The summary of contributions of this thesis are as follows:

- Chapter 2 provides the relevant background of TEEs. The chapter begins with a brief history, explains the main characteristics, and describes a few limitations.

- Chapter 3 shows that a TEE should not overlook side-channel threats, which are not present in the threat models of the major vendor TEEs to date. The chapter presents an off-chip side-channel attack on Intel SGX that is powerful enough to recover most of the sensitive data in a program. The demonstration of the attack motivates why a TEE design should not disregard side channels.

- Chapter 4 presents Keystone, which is an open framework for building TEEs. The framework is based on RISC-V instruction set architecture, enabling full transparency of software

and hardware. Keystone shows how one can separate security and functionality in a TEE design to enhance *customizability*. The chapter presents how Keystone can help explore various memory protection techniques against different threat models. Keystone is now used by hundreds of researchers for different prototypes and experiments.

- Chapter 5 proposes an efficient way to formally reason about a TEE modification by showing how TEE can support simple memory sharing. The chapter shows that *incremental verification* on a high-level specification enables an agile formal verification of a specification, which can be easily implemented by existing TEEs.

- Chapter 6 concludes the thesis by presenting the implications and potential future work.

## 1.4 Acknowledgment of Collaborative Work and Funding

I have authored most of the content and figures in this thesis and have adapted some parts from jointly authored publications or submissions. The detailed contributions of the collaborators follow.

Chapter 3 is based on the submission "An Off-Chip Attack on Hardware Enclaves via the Memory Bus." [109] Chia-Che Tsai wrote a fuzzy pattern-matching algorithm to extract sensitive access patterns from the trace. He also collaborated on modifying and debugging QEMU [164], Graphene [209], and SGX driver for the attack. Dongha Jung collected the trace from the experiments using the memory interposer and the signal analyzer. Ian T. Fang helped with the experiments and participated in discussions to share his brilliant ideas. Raluca Ada Popa and Chia-Che Tsai provided insightful guidance and feedback throughout the duration of the project.

Chapter 4 is based on the submission "Keystone: an Open Framework for Architecting Trusted Execution Environments." [110] David Kohlbrenner contributed to Keystone implementation, including cache partitioning, edge call interface, fixing many bugs, and improving code quality. Shweta Shinde extensively analyzed existing TEEs and compared their trade-offs. Both Shweta Shinde and David Kohlbrenner contributed to making critical design decisions for Keystone and writing the paper. Krste Asanović and Dawn Song provided valuable feedback throughout the project.

Chapter 5 is based on the submission "Cerberus: A Formal Approach to Secure and Efficient Enclave Memory Sharing." Kevin Cheang contributed to formalizing the  $TAP_C$  model and proving the SRE property. Pranav Gaddamaduguav contributed to translating the TAP model from Boogie to UCLID5. His thesis [67] describes the contribution in detail. Alexander Thomas modified the Darkhttpd benchmark to use Cerberus. Catherine Lu wrote a program with Sqlite3 that uses Cerberus. Both Alex and Cathy have significant contributions to the implementation of Cerberus. Anjo Vahldiek-Oberwagner, Mona Vij, Dawn Song, Sanjit A. Seshia, and Krste Asanović provided guidance and feedback.

The submissions were in part based on work supported and funded by National Science Foundation (NSF) grants CNS-1228839, CNS-1405641, CNS-1700512, NSF CISE Expeditions Award

CCF-1730628, TWC-1518899, Center for Long-Term Cybersecurity; DARPA grant N66001-15-C-4066; ADEPT Lab industrial sponsors and affiliates Intel, HP, Futurewei, Seagate, NVIDIA, and SK Hynix; and RISE Lab insdustrial sponsors and affiliates Sloan Foundation, Alibaba, Amazon Web Services, Ant Financial, ARM, Captial One, Ericsson, Facebook, Google, Microsoft, Scotiabank, Splunk, and VMware. I was partly supported and funded by the Kwanjeong Educational Foundation throughout the writing of this thesis. Any opinions, findings, conclusions, or recommendations in this thesis are solely those of the author and do not necessarily reflect the position or the policy of the sponsors.

## **Chapter 2**

## **Background**

## 2.1 The History of TEEs

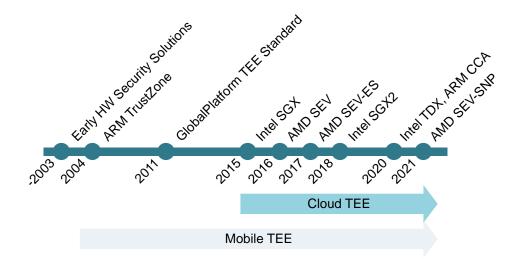

TEEs first appeared in the mobile device industry, where the network operators wanted to put restrictions on mobile devices and prevent users from exploiting their networks. Now, TEEs are more popular for confidential computing in the cloud, where the users want to protect their data against cloud service providers or other companies while using cloud services. This section describes a brief history of TEEs by starting with early security solutions based on hardware.

### 2.1.1 Early Security Solutions Based on Hardware

The early TEEs appeared for mobile platform security in around 2000. The network operators needed restrictions and protection on end-user devices, which drove the development of hardware-aided security solutions from mobile chip vendors such as Nokia or Texas Instruments. The initial TEEs – although they were not named "TEE" back then – leveraged hardware support to protect International Mobile Equipment Identity (IMEI) or a set of parameters for radio frequency transmission in mobile devices [17, 120]. By relying on hardware that is immutable and has a narrow interface, mobile systems were able to effectively reduce the attack surface of the security functions in mobile devices.

On the server-side, commercial products such as Trusted Platform Modules (TPMs) [21, 99] or crypto co-processors like IBM 4758 [58] had also adopted the idea of leveraging trusted hardware. They were mainly supplementary pieces of hardware that provided some security functions but did not have a general computation capability. TPMs implement an attestation protocol to validate the integrity of the privileged software, which is in charge of most of the security. Thus, any generic program running on the server can rely on the privileged software and its integrity. Crypto co-processors have enabled the secure computation of specific operations such as random-number generation or public-key cryptography.

Figure 2.1: The history of Trusted Execution Environments from mobile devices to cloud computing

#### 2.1.2 Rise of Mobile TEEs

In 2004, Arm introduced TrustZone [200], which is a system architecture that separates two parallel *execution worlds* (i.e., secure and non-secure worlds) within a single processor [200]. TrustZone isolated the secure world from the non-secure world using an additional bit in the system address bus and allowed a general program to run in the secure world's address space with access to the non-secure world. Interestingly, the first white paper of TrustZone describes the secure execution world as a *trusted execution environment*.

The term TEE had been widely used in the industry for marketing purposes but was not defined until Open Mobile Terminal Platform (OMTP) first did it in 2009 [1, 145, 207]. The OMTP-defined role of TEEs is to protect the copyrights of code and data of mobile applications. In 2011, the term was developed and standardized by GlobalPlatform [198]. GlobalPlatform standardized the TEE API and described that the TEE offers digital contents protection, authentication of security-critical code (e.g., digital payments), and integrity of system code (e.g., firmware). Along with the exponential growth of the mobile market through the mid-2010s, ARM TrustZone-based TEEs became popular in mobile devices such as smartphones and embedded devices [208, 20, 172]. In 2014, Linaro and ST-Ericsson open-sourced OP-TEE [146], a TEE based on ARM TrustZone that complies with the GlobalPlatform TEE standard.

#### 2.1.3 Intel SGX and Advances in Academic Research

While industry-driven mobile TEEs were widespread, there was less academic work, presumably due to a lack of public resources and the limited usage of TEE [17]. In 2013, Intel revealed Secure Guard Extensions (SGX), consisting of additional instructions in Intel processors to support

TEE [126]. The architecture for SGX was substantially different from mobile TEEs. First, instead of separating secure and non-secure worlds in the entire system, SGX separates secure and non-secure address spaces within a single process. SGX referred to the secure address space as an *enclave*, which became a popular alternative terminology for SGX-like TEEs. SGX allowed mutually distrusting enclaves to run on the same system with the same security guarantees. Also, SGX targets generic trusted computing in Intel processors, which means that virtually anyone can develop any programs using their TEE.

SGX became publicly available in the sixth-generation Intel processors in 2015, and has inspired several open-source software frameworks such as Haven (2014) [24], SCONE (2016) [15], and Graphene-SGX (2017) [209] to support generic computation with SGX. Also, a large body of research on applications, vulnerabilities, functional or security extensions of SGX emerged.

### 2.1.4 Confidential Computing with Cloud TEEs

The last few years have seen a rise of cloud TEEs, especially for *confidential computing* in the cloud. Most vendors produce chips with various TEEs for confidential computing and cloud services. AMD introduced Secure Encrypted Virtualization (SEV) and a series of extensions including SEV-ES (Encrypted State) and SEV-SNP (Secure Nested Paging) [6, 96, 7]. SEV technologies focus on isolating a virtual machine from the rest of the system including the hypervisor installed by the cloud service provider (CSP). Intel enabled a larger SGX memory size to accommodate more cloud TEE usage. Intel has also developed Trust Domain Extensions (TDX) [89], which aims to isolate and encrypt cloud VMs sililar to SEV. The trend shows that both the major server-class CPU vendors are focusing on the cloud TEE market <sup>1</sup>.

Building on this support, TEEs are becoming a popular option for various remote computations at scale. Many startups such as Opaque <sup>2</sup>, Anjuna <sup>3</sup>, and Fortanix <sup>4</sup> have started to build practical TEE-based software systems such as databases, data analytics, and machine learning. Confidential Computing Consortium (CCC) under the Linux Foundation <sup>5</sup> has initiated an industry-wide collaboration on standardizing and encouraging TEE-based confidential computing.

## 2.2 The Key Characteristics of TEEs

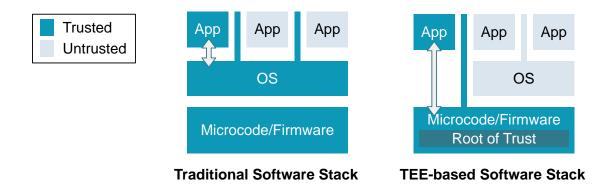

This section describes the key characteristics of TEEs. Figure 2.2 compares a TEE-based software stack with a traditional one to highlight a few promising aspects of TEEs.

<sup>&</sup>lt;sup>1</sup>Intel announced that they are dropping SGX from PCs [206]

<sup>&</sup>lt;sup>2</sup>https://opaque.co/

<sup>&</sup>lt;sup>3</sup>https://www.anjuna.io/

<sup>&</sup>lt;sup>4</sup>https://fortanix.com/

<sup>&</sup>lt;sup>5</sup>https://confidentialcomputing.io/

Figure 2.2: Traditional vs. TEE based software stacks

### 2.2.1 Hardware-aided Memory Isolation

A key idea of TEEs is to isolate a part of the physical memory by using hardware mechanisms rather than using software-managed virtual memory. Such techniques are *hardware-aided* memory isolation as they use non-traditional hardware components. For example, Intel SGX reserves Processor Reserved Memory (PRM) in the main memory, which is access-controlled and managed entirely by the microcode and a hardware extension in the memory controller. ARM TrustZone isolates the secure world from the non-secure world by adding one bit to the system bus and filtering out memory transactions. Some TEEs also perform encryption on the isolated memory contents with hardware-owned keys. The hardware-aided memory isolation techniques offer powerful protection against both software and hardware adversaries depending on the threat model.

#### 2.2.2 Narrow Interface

In a traditional software stack, each of the user programs cannot directly interact with various hardware resources. Instead, the operating system virtualizes them and provides the user with an interface, which ends up becoming very wide and includes hundreds of system calls, device drivers, and shared memory. In contrast, a TEE can be viewed as vertical integration of software and hardware for security as the program directly interacts with various hardware-level components such as microcode or firmware via a narrow interface (Figure 2.2). A TEE platform only provides tens of functions to the user program, to which it is easier to apply strict rules to monitor and sanitize execution.

### 2.2.3 Minimized Trusted Computing Base

The *trusted computing base (TCB)* is the set of all components in a computer system critical to security. The size of TCB usually refers to the number of lines of code, the number of functions, or the number of external interfaces. A large TCB does not necessarily but empirically mean a large attack surface. Thus, reducing the size of TCB usually helps reduce the number of potential

vulnerabilities. TEEs can reduce the size of TCB from an OS with millions of lines of code to firmware or microcode with only thousands of lines of code. Thus, a program has a smaller attack surface in TEEs than in the traditional software stack. In addition, minimizing the complexity of TCB provides the ease of formal reasoning. For example, applying automated formal reasoning to a program involves removing unbounded loops or model refinement, which are demanding with complex TCB [136, 101, 65].

#### 2.2.4 Remote Attestation

Many cloud TEEs support *remote attestation* to provide cryptographic proof that the program inside the TEE is in a known state expected by a remote verifier. The remote attestation leverages the *chain of trust* constructed by a few cryptographic primitives. The chain of trust is backed by a *silicon root of trust*, which contains a tamper-proof secret key or identifier fused in hardware. The silicon root of trust usually measures the firmware or the boot loader and uses the key to sign the measurement. The measurement and the signature pair act as cryptographic evidence of the integrity of the firmware certified by the root of trust. In addition to the remote attestation, the root of trust often provides trusted functions such as a true random number generator (TRNG), a monotonically increasing counter, a trusted timer, or side-channel resilient crypto accelerators.

## 2.3 Limitations of Existing TEEs

This thesis will address the research challenges of building TEEs. However, the TEEs themselves also have some limitations related to their challenges. This section discusses the limitations of TEEs and explains how they are related to the later sections.

### 2.3.1 Missing Common Threat Model

Historically, TEEs have been driven mainly by the industry, with leading companies using the same term to indicate different technologies. For example, SGX, TDX, SEV, and TrustZone are all referred to as TEE, whereas their threat models are significantly different from each other. Each vendor TEE has a specific threat model that fits the product's business model. For this reason, means there is no common threat model that everyone should expect from all of the TEEs. This makes it hard for the users to assess how secure the TEE is and to what extent. Moreover, a company can change its TEE threat model even within a single line of products. For example, the early version of Intel SGX has integrity protection on the physical memory, but it was later dropped to allow larger Enclave Page Cache (EPC) sizes in the Ice Lake server generation [190]. Another example is AMD's SEV, where they gradually added protections on register states (SEV-ES) and physical memory integrity (SEV-SNP) over the course of a few years.

Different threat models have different trade-offs among security, performance, and functionality. However, it is hard to explore them with the vendor TEE, as their implementations are proprietary and assume a fixed threat model (at least within one generation of products). Chapter 4

discusses why we need a framework to explore different threat models and proposes a flexible memory-management technique that enables various memory protections modularly added to the shared codebase. The proposed Keystone framework allows the TEE programmers to analyze various trade-offs on different threat models and workloads.

#### 2.3.2 Side-Channel Attacks

Although many recent studies unveiled destructive side-channel attacks, vendor TEEs still exclude side-channel attacks from their threat models. Some of the justifying claims are that side-channel attacks have a higher bar in practice, and the program can self-mitigate them in many cases [94, 195]. However, a series of side-channel attacks have hinted that some side channels have a lower bar and higher impact than the claims [35, 219, 212, 176, 135, 177, 175].

Chapter 3 demonstrates Membuster, an off-chip side-channel attack on Intel SGX. With physical access to the machine, the attacker can snoop on the external memory bus to observe the memory access pattern of a program and recover the secret data from the access pattern. The attack suggests that it is not ideal to completely exclude side-channel attacks from the threat model of a TEE.

#### 2.3.3 Vulnerabilities and Patches

Unknown vulnerabilities can still compromise TEEs despite their small TCB. A TEE compromise could be more detrimental than a typical software compromise as they are likely protecting more security-critical software. Thus, patches should promptly mitigate any vulnerabilities. However, as a large portion of TEE implementation is in hardware, it is hard or even impossible to fix the vulnerabilities in a short time.

Moreover, hardware vendors usually dictate such patches. For example, both SGX and SEV implementations are in proprietary hardware components such as microcode, which only allows authenticated updates issued by the vendors. Thus, it is hard to fix the vulnerability before the TEE vendors release the patches. Also, the patches are not open-source, preventing them from being publicly reviewed or modified, thus making them less credible than how open-source software ecosystems handle vulnerabilities.

Keystone (Chapter 4) consists of high-privilege software written in common programming languages like C. As the chapter will discuss, RISC-V allows Keystone to leverage hardware-based memory protection while implementing the other features in software. Keystone is fully open source, significantly lowering the bar of the reviews and the modifications.

## 2.3.4 Limited Programability

Section 2.2.2 discusses how a narrow interface in TEE helps security. However, this is at the cost of programmability. A narrow interface means that only a few functions are available to a program. Thus, many rich functionalities provided by the OS via system calls are likely unavailable in TEEs.

Thus, many software projects [209, 146] implement the key functionalities via a software wrapper on top of the TEE.

Chapter 5 will discuss how such an approach can end up with a suboptimal implementation. The chapter will show a formal approach that enables an agile modification of the TEE interface to support secure and efficient memory sharing.

## **Chapter 3**

## Why Your Threat Model Might Be Wrong

This chapter shows how an attacker can break the confidentiality of a hardware enclave using *Membuster*, an off-chip side channel attack. Membuster shows that even a carefully designed TEE can be broken by a side channel, which motivates why a TEE design should consider various threat models including side-channel attacks.

#### 3.1 Introduction

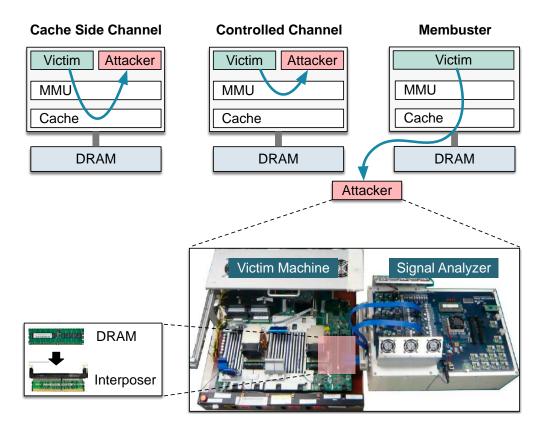

As Section 2.3.2 discusses, many side-channel attacks against TEEs have been discovered [35, 215, 32, 180, 132, 36]. Side-channel attacks leak sensitive information from enclaves via architectural or microarchitectural states. For instance, controlled-channel attacks [220] use the OS privilege to trigger page faults for memory access on different pages, to reconstruct secrets from page-granularity access patterns inside the victim program. These attacks are categorized as *on-chip side-channel attacks*, where the attacker uses adversarial or shared on-chip components to reveal memory addresses accessed by the victim (Figure 3.1).

An attacker who can *physically* access the machine can perform an *off-chip side-channel attack* that directly observes the memory addresses on the *memory bus*. The memory bus, which consists of a *data bus* and an *address bus*, delivers memory requests from a CPU to an off-chip DRAM. Although the CPU encrypts the data of an enclave, all the addresses still leave the CPU unencrypted, allowing the attacker to infer program secrets from the access patterns. Since off-the-shelf DRAM interfaces do not support address bus encryption, no existing hardware enclave can prevent physical attackers from observing the memory address bus.

Several studies have hinted at the possibility of attacks based on the memory address bus [119, 49, 85]. Costan *et al.* [49] suggest the possibility of tapping the address bus, but acknowledge that they are not aware of any successful example of the attack. Maas *et al.* [119] suggest that an attacker who can collect physical memory traces of a database server can distinguish two different SQL queries operating on the same dataset. However, no work has shown how such a side channel can be exploited to break the confidentiality of an enclave.

This chapter presents Membuster, an off-chip side-channel attack on the memory address bus.

Figure 3.1: On-chip side channels compared to Membuster. The cache side-channel attack leaks addresses through a shared cache, whereas the controlled-channel attack uses adversarial memory management. Membuster leaks addresses directly through the off-chip memory bus. The photo shows an example hardware setup for the attack.

Membuster can be a substantial threat to hardware enclaves because of its unique traits compared to the existing on-chip attacks (Section 3.2.2). The need for off-chip access, despite being a disadvantage, advantages the attacker as it makes Membuster much harder to mitigate with *protected-access* solutions (Table 3.1). Recently, a wide range of tools [143, 42, 75, 185, 43] have been developed for mitigating on-chip side-channel attacks for enclaves with a reasonable overhead. These tools either partition the resources (e.g., cache) to prevent an attacker from learning information via shared resources or intercept actions (e.g., page faults) to prevent an attacker from observing the side channels. At their core, these solutions attempt to protect the memory accesses from an attacker's sight.

However, these protected-access solutions do not prevent Membuster, which observes the memory addresses off-chip and thus can bypass the protection of any on-chip solutions. To prevent Membuster on the current hardware enclave design, one must *hide* the accessed memory addresses, by making the enclave execution *oblivious* to the secret data. This requires either using oblivious algorithms [216] inside the enclave or running the enclave atop an ORAM [194, 131]. Both mechanisms bring significant performance overhead to the enclave. An alternative is to change the CPU and DRAM design to encrypt the address bus, but implementing a decryption module in DRAM can be expensive [3, 19].

The challenges to perform a robust off-chip attack are as follows:

- 1. **Address Translation.** The attacker needs to translate the DRAM requests into the physical addresses by reverse-engineering the mapping and to further translate them into virtual addresses of the victim enclave:

- 2. **Lossy Channel.** The attacker only sees DRAM requests when cache misses or write-back occurs. Since most modern CPUs have a large last-level cache (LLC), a significant portion of memory accesses do not issue any DRAM requests. Section 3.4 shows why simple methods such as *priming* the cache does not incur sufficient cache misses needed for the attack;

- 3. **Unusual Behaviors in SGX.** SGX has unique memory behaviors which increase the difficulty of the attack. For example, common architectural features such as disabling the cache do not work in SGX, and *paging* in SGX hides most of the memory accesses.

Section 3.3 shows how an attacker can translate the DRAM requests, and can filter out irrelevant addresses to leave only the *critical* addresses that are useful for the attack. Section 3.3.6 shows examples of applications that are susceptible to the attack. Then, Section 3.4 introduces two techniques, *critical page whitelisting* (Section 3.4.2) and *cache squeezing* (Section 3.4.4), to increase useful cache misses by thwarting page swaps and shrinking the effective cache for the critical addresses. With more cache misses, the attacker can observe more DRAM requests. These techniques do not cause detectible interference to the victim, and can be combined with cache priming to make more memory accesses visible to the attacker. The *oracle-based fuzzy matching algorithm* (Section 3.5) can create an *oracle* of the secret-to-access-pattern mapping, to identify the sensitive accesses from a sizable memory bus trace. The attacker extracts the sensitive data from the noisy memory accesses by fuzzy-matching the accesses against the oracle.

|                                                    | Brasser et al. [32] | Schwarz et al. [180] | CacheZoom [132] | FLUSH-based [36] | Controlled [220] | Membuster |

|----------------------------------------------------|---------------------|----------------------|-----------------|------------------|------------------|-----------|

| Software-Only                                      | 1                   | 1                    | 1               | ✓                | ✓                | X         |

| <b>Protected-Access Fix</b> [143, 42, 75, 185, 43] | 1                   | 1                    | 1               | <b>√</b>         | ✓                | X         |

| Root Adversary                                     | 1                   | Х                    | 1               | ✓                | /                | <b>√</b>  |

| Noiseless                                          | Х                   | X                    | Х               | ✓                | ✓                | <b>√</b>  |

| Lossless                                           | X                   | Х                    | X               | ✓                | /                | X         |

| Fine-Grained (64B vs. 4KB)                         | 1                   | 1                    | 1               | Х                | Х                | 1         |

| No Interference (e.g., AEX)                        | 1                   | 1                    | X               | X                | X                | 1         |

| Low Overhead                                       | 1                   | 1                    | Х               | Х                | X                | ✓         |

Table 3.1: This work (Membuster) compared to previous side-channel attacks on SGX. The two boldface rows illustrate the most important distinctions. The colored cell indicates the attacker has the advantage.

The attack is demonstrated by attaching Dual In-line Memory Module (DIMM) interposer to a production system with an SGX-enabled Intel processor and a commodity DDR4 DRAM. The memory bus signals are captured to perform an off-line analysis. The attack is demonstrated by two applications, Hunspell and Memcached. Finally, the scalability of the techniques is shown by simulating the attack in modified QEMU [164].

To summarize, this chapter describes the following contributions:

- The setup of an off-chip side-channel attack on hardware enclaves and identification of the challenges for launching the attack robustly.

- Effective techniques for maximizing the side-channel information with no detectible interference nor order-of-magnitude performance overhead to the victim program.

- A fuzzy comparison algorithm for converting the address trace collected on the memory bus to program secrets.

- Demonstration and experimentation of the attack on an actual Intel SGX CPU. It is the first work that shows the practicality of the attack.

The security implications of the off-chip side-channel attacks can be pervasive because such a channel exists on almost every secure processor with untrusted memory.

## 3.2 Why an Off-Chip Side Channel Matters?

This section begins with the background on Intel SGX, and discusses how Membuster can be a substantial threat to hardware enclaves because of its unique traits. Table 3.1 compares Membuster with various on-chip side-channel attacks on SGX [32, 132, 180, 36, 220].

#### **3.2.1 Intel SGX**

Intel SGX has the most mature implementation and the strongest threat model against untrusted DRAM. SGX is a set of instructions for supporting hardware enclaves introduced in the Intel sixth-generation processors. SGX assumes that only the processor package is trusted; all the off-chip hardware devices, including the DRAM and peripheral devices, are considered potentially vulnerable or compromised. The threat model of SGX also includes physical attacks such as Cold-Boot Attacks [80], which can observe sensitive data from residuals inside DRAM.

An Intel CPU with SGX contains a memory encryption engine (MEE), which encrypts and authenticates the data stored in a dedicated physical memory range called the *enclave page cache* (EPC). The MEE encrypts data blocks and generates authentication tags when sending the data outside the CPU package to be stored inside the DRAM. To prevent roll-back attacks, the MEE also stores a version tree of the protected data blocks, with the top level of the tree stored inside the CPU. For Intel SGX, EPC is a limited resource; the largest EPC size currently available on an existing Intel CPU is 93.5 MB, out of 128 MB Processor's Reserved Memory (PRM). The physical pages in EPC, or EPC pages, are mapped to virtual pages in enclave linear address ranges (ELRANGEs) by the untrusted OS. If all concurrent enclaves require more virtual memory than the EPC size, the OS needs to swap the encrypted EPC pages into regular pages.

However, even with MEE, Intel SGX does not encrypt the addresses on the memory bus. As previously discussed, changing the CPU to encrypt the addresses requires implementing the encryption logic on DRAM, and thus requires new technologies such as Hybrid Memory Cube (HMC) [3, 19].

The unencrypted address bus opens up a universal threat to hardware enclaves with external encrypted memory. Komodo [65], ARM CryptoIsland [52], Sanctum [50], and Keystone [110] do not encrypt data for an external memory by default. AMD SEV [6] allows hypervisor-level memory encryption, but also does not encrypt addresses.

#### 3.2.2 Side Channel Attacks on SGX

#### PRIME+PROBE

A shared cache hierarchy allows an adversary to infer memory access patterns of the victim using known techniques such as PRIME+PROBE [150, 118]. However, in PRIME+PROBE, the attacker usually cannot reliably distinguish the victim's accesses from the *noise* of other processes. The PRIME+PROBE channels are also *lossy*, as the attacker may miss some of victim's accesses while probing.

Brasser *et al.* [32] demonstrate PRIME+PROBE on Intel SGX without interfering with the enclave, but the attack requires running the victim program repeatedly to compensate for its noise and signal loss. Schwarz *et al.* [180] show that the attacker can alleviate the noise by identifying cache sets that are critical to the attack. This technique can be applied to applications that have data-dependent accesses in a small number of cache sets. CacheZoom [132] also uses PRIME+PROBE but minimizes the noise by inducing Asynchronous Exits (AEXs) every few memory accesses in the victim. This incurs a significant overhead on enclaves, and also makes the attack easily detectable [43].

#### **Flush-based Side Channels**

Other flush-based techniques such as FLUSH+RELOAD [224] and FLUSH+FLUSH [76] use a shared cache block between the attacker and the victim to create a noiseless and lossless side channel. However, these techniques cannot be directly applied to enclave memory, because an enclave does not share the memory with other processes. However, these techniques can still be used to observe the page table walk for enclave addresses [36]. Specifically, the attacker can monitor the target page tables with a tight FLUSH+RELOAD loop. As soon as the loop detects page table activities, the attacker interrupts the victim and infers page-granularity addresses. Similar to CacheZoom, this attack incurs a significant AEX overhead and thus can be detected by the victim.

#### **Controlled Channels**