## RDMA-Based Distributed Data Structures for Large-Scale Parallel Systems

Benjamin Brock

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-93 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-93.html

May 13, 2022

Copyright © 2022, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### RDMA-Based Distributed Data Structures for Large-Scale Parallel Systems

by

### Benjamin Brock

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Katherine Yelick, Co-chair Adjunct Assistant Professor Aydın Buluç, Co-chair Professor Joseph Hellerstein Associate Professor Zachary Pardos

Spring 2022

## RDMA-Based Distributed Data Structures for Large-Scale Parallel Systems

Copyright 2022 by Benjamin Brock

#### Abstract

#### RDMA-Based Distributed Data Structures for Large-Scale Parallel Systems

by

#### Benjamin Brock

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Katherine Yelick, Co-chair

Adjunct Assistant Professor Aydın Buluç, Co-chair

Running programs across multiple nodes in a cluster of networked computers, such as in a supercomputer or commodity datacenter system, is increasingly important across multiple domains, including data science, machine learning, and scientific computing. This is brought on by a combination of increasing data sizes, which push beyond the memory capacity of a single node, and increasing computational demands from new, more elaborate simulations, models, and applications.

However, writing parallel programs for clusters of computers remains a difficult task, particularly for programs that are irregular in terms of data distribution or access pattern. Many parallel programs today are still written using communication libraries like MPI or OpenSH-MEM, which require users to explicitly manage low-level details. While high-level parallel programming languages and libraries do exist, and these can make implementing certain types of programs much easier, developers often have to expend significant effort building custom infrastructure and data structures for their applications.

This thesis argues that a large part of the reason why parallel programming remains difficult is a lack of high-level distributed data structures analogous to the data structures that have become ubiquitous in sequential programming environments like C++ and Python. These especially include irregular data structures like hash tables and queues that may require fine-grained memory accesses along with synchronization. This thesis examines techniques for building high-level, cross-platform distributed data structures using one-sided remote memory operations like remote put, remote get, and remote atomics. These memory access primitives allow for a high degree of asynchrony, enabling better performance by removing synchronization bottlenecks and allowing a high degree of overlap between communication and computation. They can also be efficiently executed directly by the network hardware in

modern supercomputer and commodity datacenter networks, removing the need to synchronize with remote processes.

This thesis examines several RDMA-based distributed data structures, including hash tables, Bloom filters, queues, and dense and sparse matrices. We provide a performance model for evaluating the cost of RDMA-based distributed data structure methods in terms of their component remote memory operations, and demonstrate how this model can be extended to support GPUs in addition to conventional CPUs.

To Grandmom, who let my cousin and me take apart her computer.

# Contents

| C  | ontents                                                                 | ii              |

|----|-------------------------------------------------------------------------|-----------------|

| Li | st of Figures                                                           | iv              |

| Li | st of Tables                                                            | vi              |

| 1  | Introduction                                                            | 1               |

| 2  | Background and Related Work  2.1 Execution Models for Parallel Programs | <b>4</b> 4 6    |

| 3  | Building Distributed Data Structures                                    | 13              |

|    | 3.1 RDMA-Based Communication Primitives                                 | 13<br>19        |

|    | 3.3 BCL ObjectContainers                                                | $\frac{20}{22}$ |

|    | 3.5 Building Distributed Data Structures                                | 22<br>23        |

|    | 3.7 Buffers                                                             | 24              |

| 4  | Experimental Setup and Methodology                                      | 25              |

| 5  | RDMA-Based Queues 5.1 Asynchronous All-to-All Pattern                   | 28<br>33<br>34  |

|    | 5.3 Experimental Evaluation                                             | 35              |

| 6  | Set Data Structures                                                     | 42              |

|    | 6.1 Hash Tables                                                         | 42              |

|    | 6.2 Bloom Filters                                                       | 47<br>49        |

|    | - V.J L'AUGHHGHGH L'VAHAHAHUH                                           | 4.              |

| 7  | Mat   | trix Data Structures                                   | 55  |

|----|-------|--------------------------------------------------------|-----|

|    | 7.1   | Introduction                                           | 55  |

|    | 7.2   | Distributed Matrix Data Structure                      | 56  |

|    | 7.3   | Distributed Sparse Matrix Data Structure               | 61  |

|    | 7.4   | Sparse Matrix Multiplication                           | 70  |

|    | 7.5   | Background                                             | 74  |

|    | 7.6   | Performance Model                                      | 78  |

|    | 7.7   | Implementation                                         | 81  |

|    | 7.8   | Evaluation                                             | 83  |

|    | 7.9   | Related Work and Conclusions                           | 89  |

| 8  | Con   | nparing RDMA and RPC-Based Distributed Data Structures | 92  |

|    | 8.1   | Introduction                                           | 92  |

|    | 8.2   | Background                                             | 94  |

|    | 8.3   | Experimental Design                                    | 99  |

|    | 8.4   | Results                                                | 102 |

|    | 8.5   | Conclusions                                            | 108 |

| 9  | Con   | nclusion                                               | 109 |

| Bi | bliog | graphy                                                 | 111 |

# List of Figures

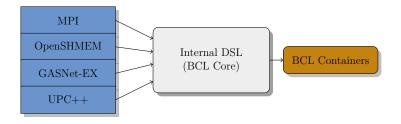

| 3.1        | Organizational diagram of BCL                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

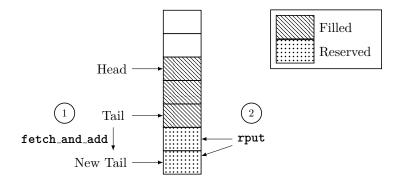

| 5.1        | Process for pushing values to a BCL FastQueue. First (1) a fetch_and_add operation is performed, which returns a reserved location where values can be inserted. Then (2) the values to be inserted are copied to the queue                                                                                                                                                                                                                                        | 33       |

| 5.2        | Our bucket sort implementation in BCL for the ISx benchmark                                                                                                                                                                                                                                                                                                                                                                                                        | 34       |

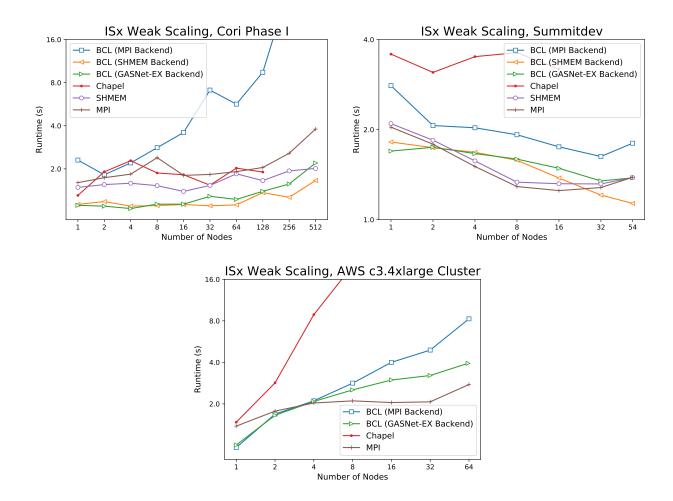

| 5.3        | Performance comparison on the ISx benchmark on three different computing sys-                                                                                                                                                                                                                                                                                                                                                                                      |          |

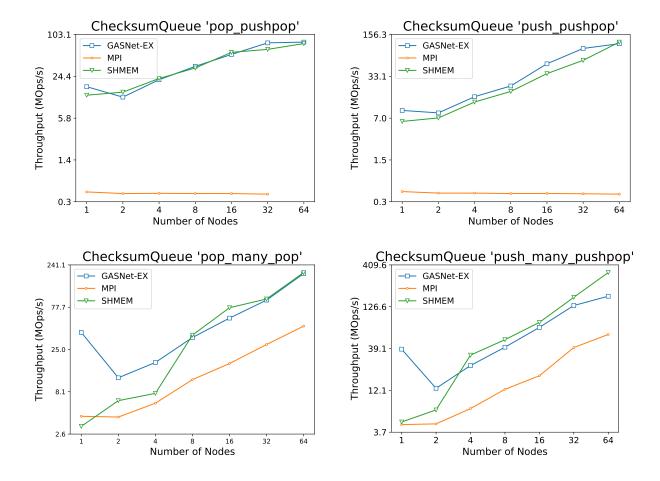

| 5.4        | tems. All runs measure weak scaling with $2^{24}$ items per process Microbenchmarks for CircularQueue. Benchmarks with "many" in the title are performed with one queue per node, while benchmarks without "many" are performed with all processes accessing a single queue. The label before the underscores indicates the operation performed, while the label after the underscore indicates the concurrency promise used. For example, "pushpop" indicates the | 36       |

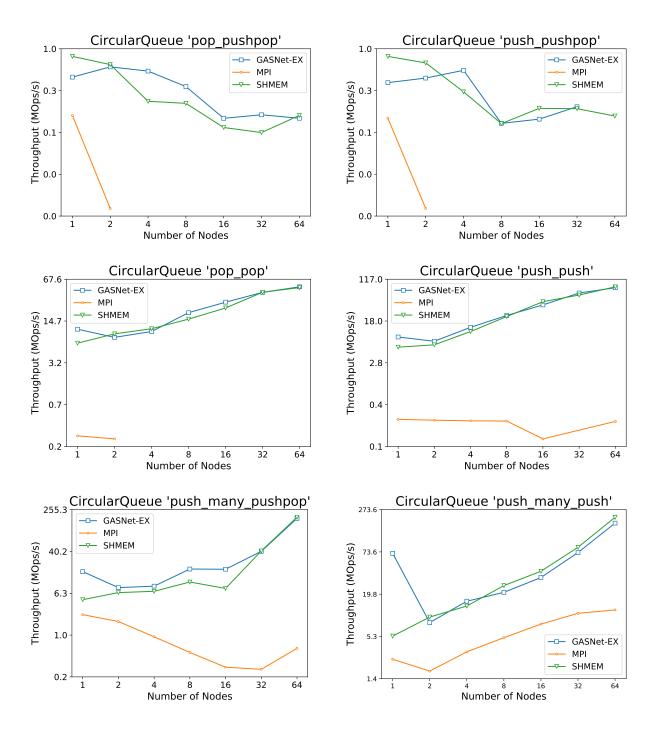

|            | concurrency promise push   pop                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39       |

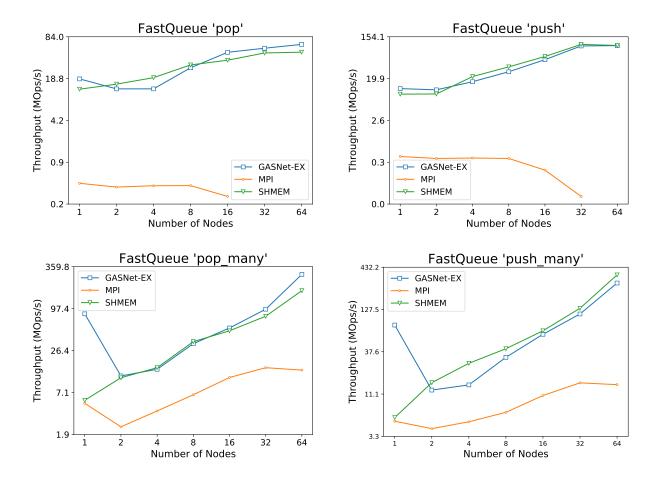

| 5.5        | Microbenchmarks for FastQueue. Benchmarks with "many" in the title are performed with one queue per node, while benchmarks without "many" are per-                                                                                                                                                                                                                                                                                                                 |          |

| 5.6        | formed with all processes accessing a single queue                                                                                                                                                                                                                                                                                                                                                                                                                 | 41       |

| 6.1        | A small change to user code—inserting into the HashMapBuffer instead of the                                                                                                                                                                                                                                                                                                                                                                                        | 4-       |

| c o        | HashMap—causes inserts to be batched together                                                                                                                                                                                                                                                                                                                                                                                                                      | 47       |

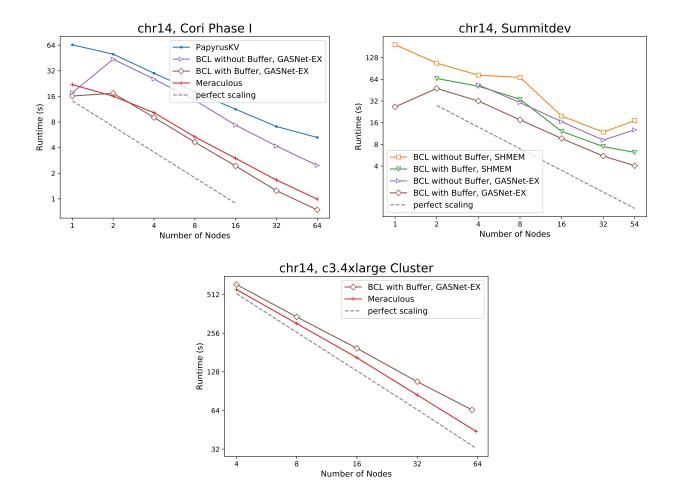

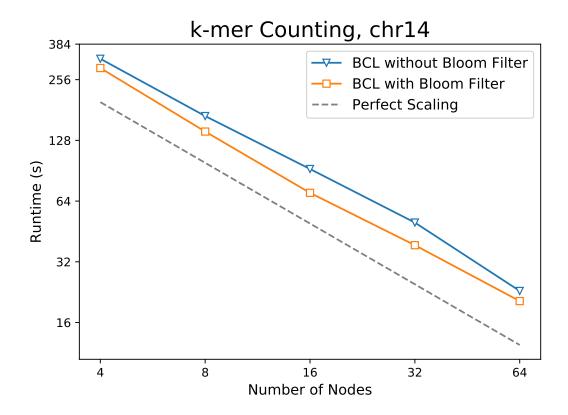

| 6.2        | Performance comparison on the Meraculous benchmark on the <i>chr14</i> dataset                                                                                                                                                                                                                                                                                                                                                                                     | 49       |

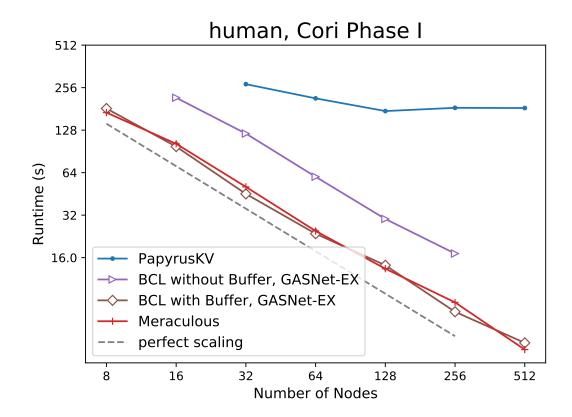

| 6.3        | Performance on the Meraculous benchmark                                                                                                                                                                                                                                                                                                                                                                                                                            | 50       |

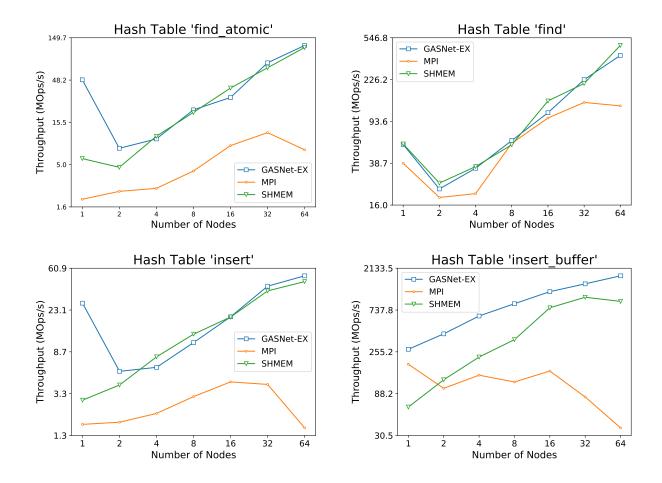

| 6.4<br>6.5 | Strong scaling for our $k$ -mer counting benchmark using dataset $chr14$ . Microbenchmarks for the hash table                                                                                                                                                                                                                                                                                                                                                      | 52<br>53 |

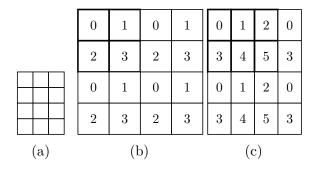

| 7.1        | A collection of matrix tile grids and distributions.                                                                                                                                                                                                                                                                                                                                                                                                               | 60       |

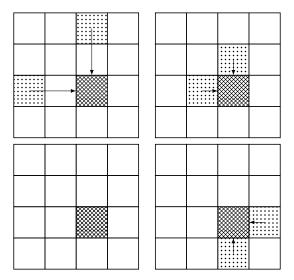

| 7.2 | Illustration of the local matrix multiplications necessary to compute one block of      |     |

|-----|-----------------------------------------------------------------------------------------|-----|

|     | the output matrix. All submatrices in the block row of A are multiplied by the          |     |

|     | corresponding submatrices in the block column of B                                      | 64  |

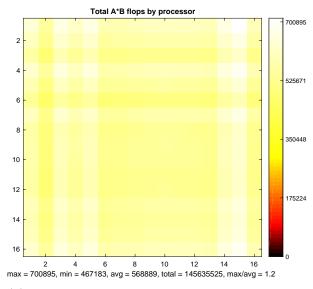

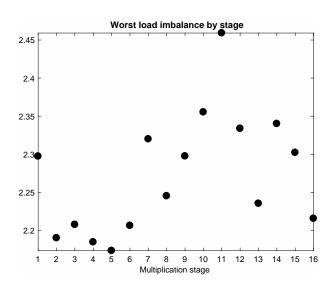

| 7.3 | Total (end-to-end) vs. per-stage load balance multiplying a R-MAT model-                |     |

|     | generated sparse matrix with a sparse 2D algorithm. Simulated on a $16 \times 16$       |     |

|     | process grid                                                                            | 74  |

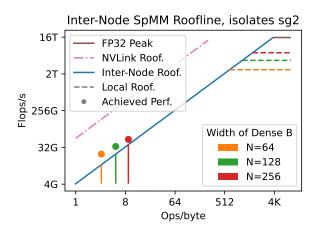

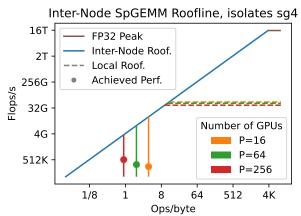

| 7.4 | Inter-node roofline plots for SpMM and SpGEMM with a 2D distribution. SpMM              |     |

|     | plot models performance for different widths of the dense B matrix at a fixed           |     |

|     | scale (24 GPUs), while SpGEMM models performance at different scales. Dashed            |     |

|     | horizontal lines represent <i>local roofline peaks</i> for SpMM and SpGEMM operations,  |     |

|     | while vertical lines represent <i>inter-node</i> roofline peaks for particular problems | 80  |

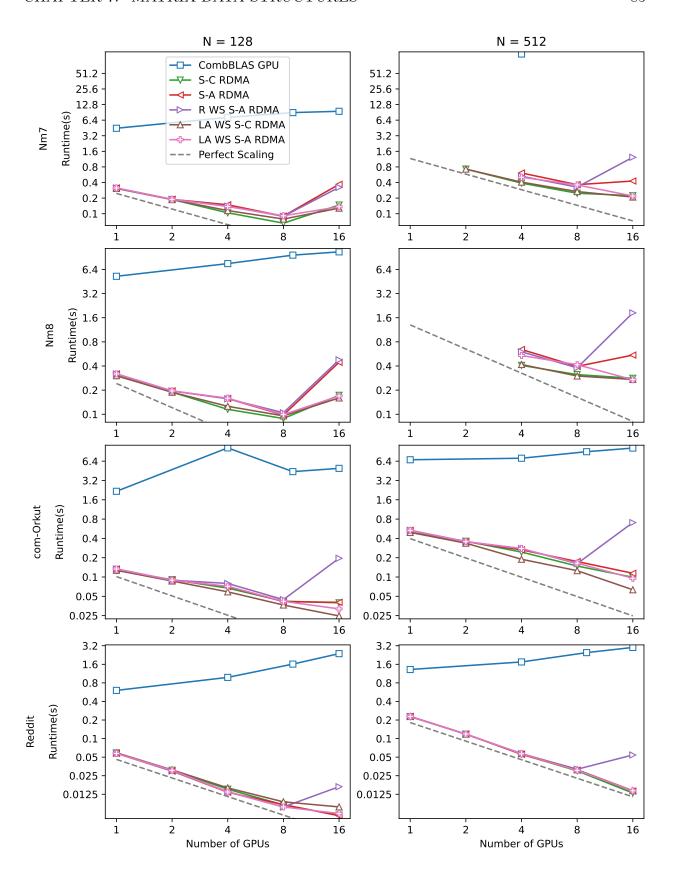

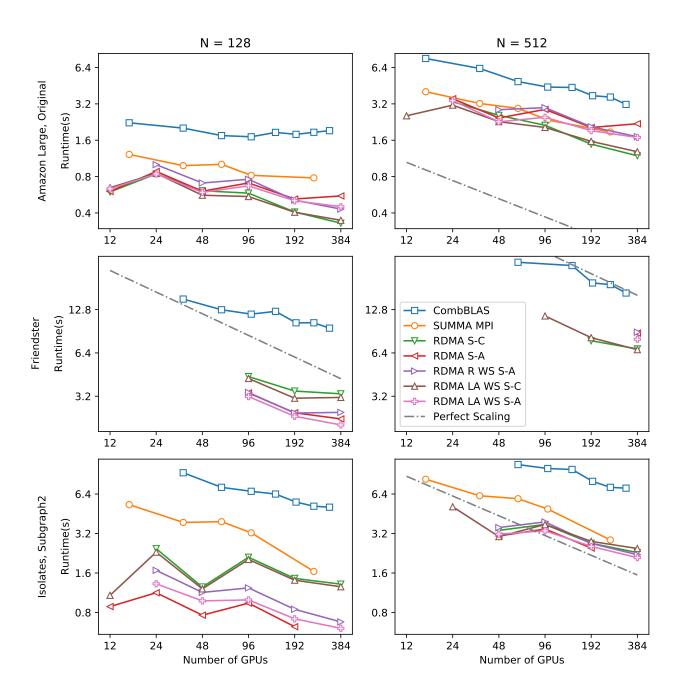

| 7.5 | Single-node runtimes for SpMM, with different numbers of columns $N$ in the             |     |

|     | dense matrix B                                                                          | 85  |

| 7.6 | Multi-node runtimes for SpMM, with different numbers of columns $N$ in the dense        |     |

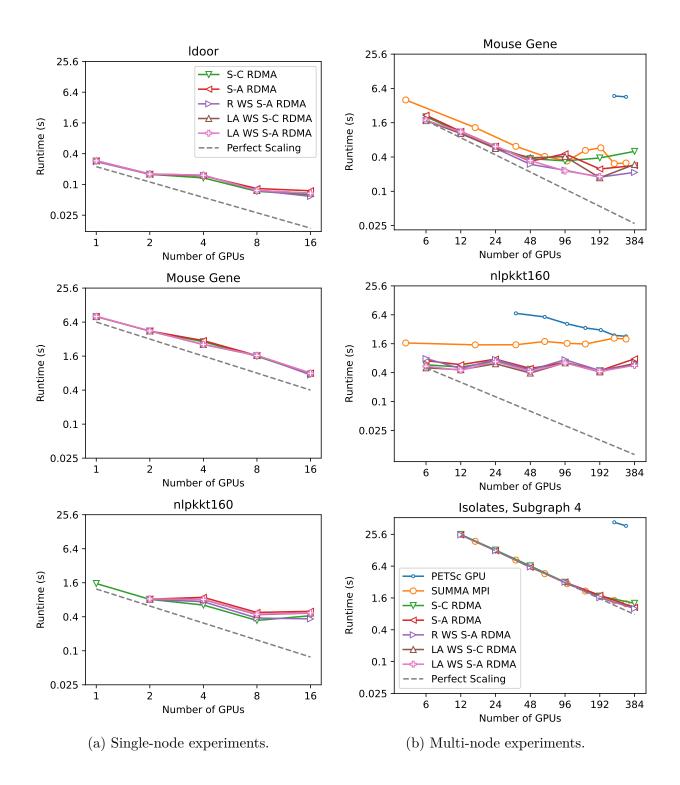

|     | matrix B                                                                                | 87  |

| 7.7 | SpGEMM strong scaling experiments                                                       | 91  |

| 8.1 | Modifying a hash table using one-sided RDMA operations                                  | 95  |

| 8.2 | Modifying a hash table using an RPC                                                     | 96  |

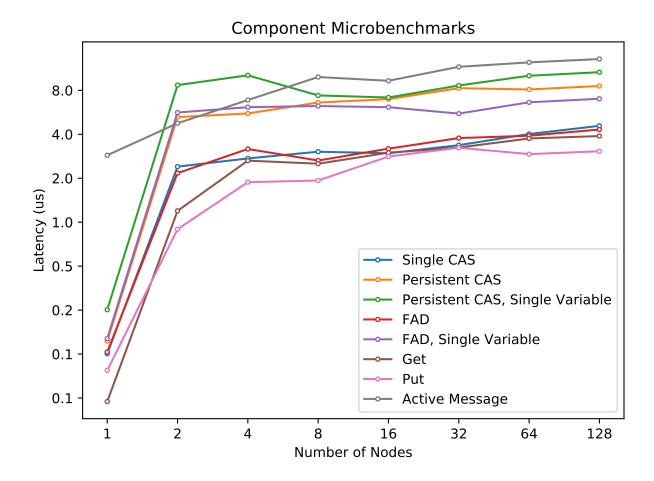

| 8.3 | The component latencies for RDMA operations and AMs on Cori                             | 104 |

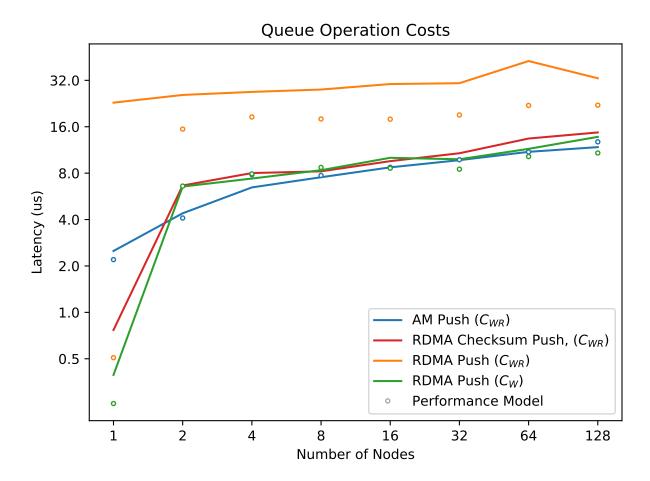

| 8.4 | Latencies for RDMA- and RPC-based queue push operations                                 | 105 |

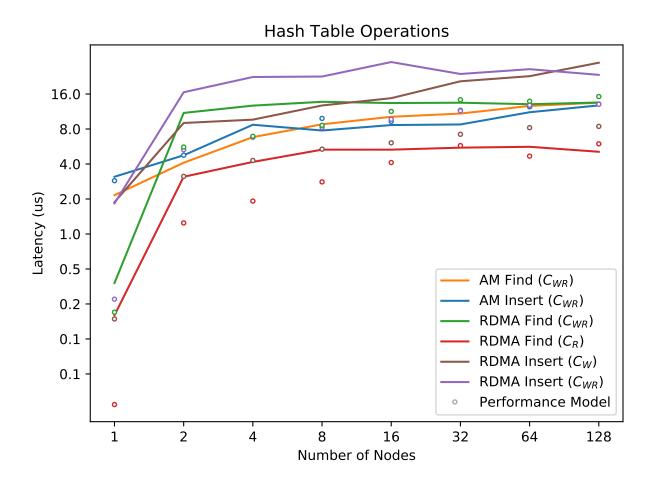

| 8.5 | Latencies for RDMA- and RPC-based hash table operations                                 | 106 |

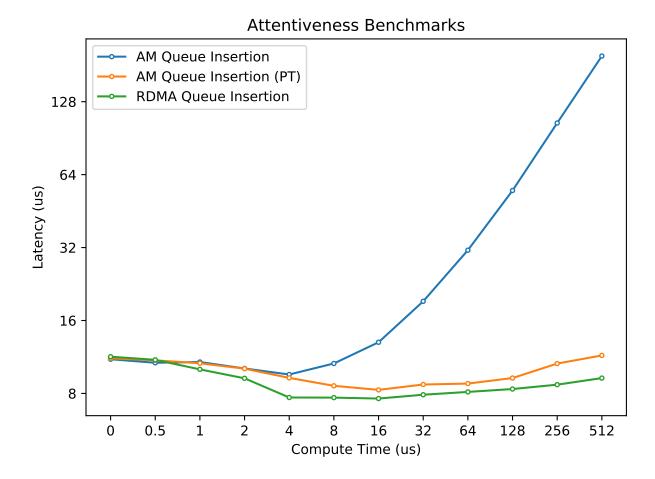

| 8.6 | Measuring the cost of a queue insertion as remote processes become less attentive       | - 0 |

|     | due to intermixed computation                                                           | 107 |

|     | 1                                                                                       |     |

# List of Tables

| 4.1                               | Summary of systems used in evaluation throughout this work                                                                                                                                                                                                                                                                                                                                                                                                          | 25                   |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| <ul><li>5.1</li><li>5.2</li></ul> | A selection of methods from BCL queues. Costs are best case, using implementation chosen with no concurrency promises. $R$ is the cost of a remote read, $W$ the cost of a remote write, $A$ the cost of a remote atomic memory operation, $B$ the cost of a barrier, $\ell$ the cost of a local memory operation, and $n$ the number of elements involved. $c$ is the number of bytes in a checksum divided by the number of bytes per element (usually $\leq 1$ ) | 313                  |

| 6.1                               | Implementations of data structure operations for BCL's hash table data structure.                                                                                                                                                                                                                                                                                                                                                                                   | 45                   |

| 7.1<br>7.2                        | Matrix block descriptors, which describe different tiling strategies for a distributed matrix                                                                                                                                                                                                                                                                                                                                                                       | 57                   |

| 7.3<br>7.4<br>7.5                 | nonzeros per tile                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60<br>63<br>84<br>89 |

| 8.1<br>8.2<br>8.3                 | Latency of various RDMA operations, measured on Cori with 64 nodes RDMA-based hash table method implementations considered in this paper Implementations for circular queue methods                                                                                                                                                                                                                                                                                 | 97<br>98<br>99       |

## Acknowledgments

First and foremost, I would like to thank my advisors, Kathy Yelick and Aydın Buluç, for their mentorship and support throughout my PhD.

Kathy was always quick to make time for me, despite her impossibly busy schedule, and she was always eager to connect me with potential collaborators and contacts, both within the university and at Lawrence Berkeley National Laboratory. Her depth and breadth of expertise, on an array of topics, including parallel computing, compilers, domain science, and more, was invaluable to me, particularly as a fledgling graduate student. Kathy was always gracious enough to recognize of her students that, "While they didn't always seem to do what [she] said, they tended to end up doing good things anyway," and for that freedom I owe her a large debt of gratitude.

Aydın joined on as my advisor during my second year, and was instrumental in helping me find a central direction for my research, and what eventually became the core of this thesis. His passion and enthusiasm during our research discussions provided motivation both to start new and exciting research projects, but also to push through the grind in order to finish them. Aydın's practical experience implementing large-scale sparse linear algebra codes with CombBLAS was extremely useful to me as I set off on my own journey to implement RDMA-based data structures, and his deep understanding of algorithms on a theoretical level as well as performance analysis has shaped how I think about writing, implementing, and evaluating my own data structures and algorithms.

I must also extend my thanks to the other members of my dissertation committee, Joe Hellerstein and Zachary Pardos, whose feedback has greatly improved the quality of this thesis. In particular, Joe's insightful comments during my qualifying exam and dissertation writing process helped me view my work through a much wider and clearer lens, and as a result this thesis has been significantly improved.

I have had the great fortune throughout my PhD to work with a number of excellent collaborators and co-authors, and much of the work in this thesis, as well as the researcher I have become today, would not be possible without them. Yuxin Chen has been a longtime colleague and collaborator, and much of the work that I have done with building data structures for GPUs would not have been possible without the many discussions we have had about building communication libraries for GPUs. Jiakun Yan, who interned with us during the Fall of 2019, worked with me on an aggregation runtime for RPCs, and our many research discussions, as well as much of the work that Jiakun did with us, helped shape the work in Chapter 8. I must extend a deep thanks to Nathan Pemberton, Howard Mao, and Jenny Huang, my colleagues from the computer architecture lab. They were gracious enough to collaborate with me on a number of projects combining my distributed data structures work with experimental hardware they were developing, and I also learned a great deal from our interactions. I also owe a great deal of thanks to Michael Driscoll, my academic older brother, who took me under his wing as a second year graduate student. Working with Michael taught me a great deal about writing good software and good papers, as well as brewing good beer.

I had the opportunity to work with a number of collaborators and colleagues at Lawrence Berkeley National Laboratory, and special thanks go out to Taylor Groves, John Bachan, Paul Hargrove, Dan Bonachea, and others.

I also had the pleasure of working with the GraphBLAS Languages Committee on the GraphBLAS C and C++ APIs during my PhD. Many enlightening conversations on sparse and irregular data structures as well as API design helped shape my views on how to build high-level data structures, so my thanks go out to Aydın Buluç, Tim Mattson, Scott McMillan, and José Moreira.

I have received support, both academic and personal, from so many graduate students throughout my PhD that they are too numerous to all name here. I have been lucky enough to have Kevin Läufer as both a friend and colleague from the start of my PhD. Kevin and I would always bounce ideas off of each other, and he did not hesitate to bounce many of my less brilliant ideas back in my direction. A number of older graduate students gave me wonderful advice and helped orient me to graduate school life, and my thanks go out to Marquita Ellis, Michael Driscoll, Yang You, Penporn Koanantakool, Evangelos Georganas, Grace Dinh, Albert Magyar, Orianna DeMasi, Becca Roelofs, Nathan Pemberton, and others. I was also blessed to have a lively cohort of PhD students to go through the experience of grad school with, and my thanks go out to Rohan Bavishi, Michael Dennis, Cristina Teodoropol, Alex Reinking, Kristina Monakhova, Rachel Chen, Erin Grant, Esther Rolf, David Gaddy, Giulia Guidi, Alok Tripathy, and Vivek Bharadwaj, and many others. Specific thanks, also, to Eric Love, author of the Ressort programming language, for his priceless advice to "perhaps not make a new programming language during your PhD, if you can avoid it."

Special thanks go to my girlfriend Caroline Lemieux for her companionship throughout both of our PhD journeys. Graduate school life can be hectic and frustrating at times, and it has been made so much more pleasant by having you there to share it with. Outside of grad school, we climbed mountains, went on long runs and bike rides, and visited new countries and continents together. For all of the adventures and trivialities, for all the hills and bayous, for cutting my hair during the pandemic, and for teaching me French, you have my sincerest gratitude. C'était, en fait, le mieux d'être avec toi.

A sincere thank you must go to my family, without whom none of this would have been possible. My parents have always been an inspiration to me, both in their own academic pursuits and in the attitudes they encouraged in me and my sister toward knowledge and personal growth. From when I was very young, learning was not an activity only performed in the classroom, and we were surrounded by good books and by interesting places and people. From nature walks in the Great Smoky Mountains to trips to bustling markets in the most densely populated city on Earth, my sister and I were always surrounded with the best learning environment. Thanks to my father, who passed on to me his love of reading and his gift of gab, as well as my mother, who homeschooled my sister me while we lived abroad, and who passed on to me her love for music and her love of learning. Thanks to my sister, who has always been there for me, and whose will to follow her dreams and adventurous spirit have always served as an inspiration. And finally, a big thanks goes to my grandparents, who always nurtured my curiosity, particularly toward computers.

The work presented in this thesis was supported in part by the National Science Foundation Graduate Research Fellowship Program under Grant No. GE 1752814, as well as under National Science Foundation Award No. 1823034. It used resources of the National Energy Research Scientific Computing Center at Lawrence Berkeley National Laboratory, as well as the Oak Ridge Leadership Computing Facility at Oak Ridge National Laboratory, which are supported by the Department of Energy's Office of Science under Contract Nos. DE-AC02-05CH11231 and DE-AC05-00OR22725, respectively. This work used the Extreme Science and Engineering Discovery Environment (XSEDE), which is supported by National Science Foundation Grant No. ACI-1548562. This work used the Extreme Science and Engineering Discovery Environment (XSEDE) Bridges-2 at the Pittsburgh Supercomputing Center through allocation ASC180051. This work also used computational resources obtained through the AWS Cloud Credits for Research Program.

## Chapter 1

## Introduction

Due to a number of trends across data science, machine learning, scientific computing, and computer architecture, parallel computing has become more and more ubiquitous and important. Ever-growing datasets are pushing data and graph analytics workloads beyond the limits of a single computer's memory [104]. More and more sophisticated machine learning models require more computational resources as well as more memory in order to be trained and deployed in reasonable amounts of time [119]. In scientific computing, computational demands in fields like genomics, climate science, and medical imaging mean that new scientific advances often require ever-increasing amounts of computational resources [8, 46, 116]. At the same time, the breakdown of important trends in computer architecture like Dennard scaling and Moore's law mean that we can no longer depend on exponential gains in the computational performance of individual conventional processors [109]. All of this means that parallel computing has become an increasingly important tool across much of computer science and adjacent fields [8, 75, 100]. However, writing parallel programs, or programs that run on clusters of computers, remains notoriously difficult, particularly for applications which have irregular data layouts or access patterns.

The software tools at the disposal of the average parallel programmer today are little different than they were a decade ago. The most commonly used communication libraries, such as the Message Passing Interface (MPI) [110] and OpenSHMEM [20], all have interfaces that were crystallized in the late 90s or early 2000s. While these low-level communication libraries can serve as excellent platforms for applications that are closely compatible to the interfaces they supply, such as applications that can easily conform to bulk synchronous parallel communication model [37], where discrete phases of local computation are separated from communication operations by global synchronization. For applications that are irregular, either because their data layouts do not conform to a regular block distribution or because their data access patterns require sparse or random access, implementation can be particularly difficult, with users having to explicitly manage the details of synchronization and memory management across nodes [83, 117].

Dedicated programming languages and libraries do exist for writing parallel programs, and these can somewhat ease the burden of parallel programming by introducing dedicated

abstractions for communication and data distribution. However, these dedicated parallel programming environments have seen relatively little uptake in the broader HPC community. One of the primary reasons for this is that it can be difficult for developers to take the leap to a new programming language, with new, often immature toolchains. This may be exacerbated by the fact that developers often have pre-existing code in conventional programming languages like C, C++, Python, or Fortran that they need to integrate with, adding further barriers to adopting new languages. In addition, when developers are able to use dedicated parallel programming languages, they often must spend time implementing application-specific data structures, since most parallel programming environments lack expressive data structures that have become ubiquitous in sequential programming environments. Before a parallel programmer can implement their application, it is not uncommon to first have to implement the necessary data structures such as distributed hash tables, matrices, or queues. While parallel programming environments may simplify the process of writing these data structures, users are generally left to implement custom data structures on their own. This leads to a situation in which application developers must spend significantly more time implementing their parallel application than developing their parallel algorithms.

This thesis argues that one of the primary reasons that writing parallel programs for supercomputers and commodity datacenter environments remains difficult is because of this lack of high-level data structures. High-level data structures such as arrays, hash tables, and matrices have become ubiquitous in sequential programming environments like C++ and Python and as a result have greatly reduced programmer burden. In parallel programming environments and communication libraries, however, distributed data structures have remained largely absent, even in many high-level parallel programming environments like UPC [41] and UPC++ [17]. When they have provided data structures, most high-level parallel programming environments have focused on regular data structures, such as multidimensional dense arrays or regular grids. While these regular data structures are no doubt useful for applications which fit them, they are of limited use for applications that are irregular, meaning that either their data is not structured in a way that allows it to be fit into a data structure like a multi-dimensional array, hierarchical grid, or structured sparse matrix, or their data access patterns are fine-grained or irregular. In fact, Kennedy, et al. [72] cite a lack of support for irregular and sparse data distributions as one of the primary reasons for the decline of High Performance Fortran (HPF), saying that the data distribution mechanisms in HPF were not sufficiently expressive to efficiently handle sparse or irregular data. This caused many performance-conscious users to switch to low-level libraries like MPI, which gave them more granular control over performance [73].

In this thesis, I argue that providing high-level distributed data structures can reduce the burden on parallel application developers, particularly for irregular applications. I present a design for building distributed data structures using *one-sided* communication operations, remote get, remote put, and remote atomic operations that allow processes to access and manipulate data resident on a remote process. These operations can be executed directly by the network hardware on modern supercomputer and commodity datacenter platforms using remote direct memory access (RDMA). This allows processors to access and manipulate re-

mote data at very low latencies, since the operations can be completed in hardware and also there is no need to wait on a remote process to handle requests. This RDMA-based design also allows for a greater level of asynchrony, since processes can retrieve data independently, without needing to synchronize with other processors. This model of RDMA-based access maps well onto the data structure interfaces that users are familiar with from sequential programming environments, where inserting an element into a hash table or writing to an element in an array is a fundamentally one-sided operation. I discuss the design and implementation of several high-level distributed data structures, including hash tables, Bloom filters, queues, and dense and sparse matrices, along with algorithmic and implementation benefits that can be achieved by using an RDMA-based design. I demonstrate how this design can be extended to support GPUs. Finally, I build a performance model to evaluate the cost of various RDMA-based data structure operations in terms of their component RDMA operations, comparing these costs to a remote procedure call (RPC) implementation.

The rest of the thesis is as follows. Chapter 2 discusses background and related work. Chapter 3 presents our general framework for building cross-platform, high-level distributed data structures in C++ that can be used natively inside applications written using different communication libraries. Chapter 4 discusses the supercomputer systems and experimental setup used in experiments throughout this thesis. Chapter 5 presents and analyzes a number of different designs for RDMA-based queues. Chapter 6 discusses the design of distributed set-based data structures, including hash tables and Bloom filters. Chapter 7 discusses the design of RDMA-based dense and sparse matrix data structures, along with new RDMA-based algorithms for sparse matrix multiplication that are enabled by one-sided access. Finally, Chapter 8 presents a performance model for RDMA-based data structure operations, comparing the costs to RPC-based implementations, and Chapter 9 presents overall conclusions.

## Chapter 2

## Background and Related Work

We begin this chapter with a brief overview of background necessary for the rest of this thesis, beginning with execution models for parallel programs, which define how a program can be executed across many nodes in a supercomputer or cluster. We then discuss different communication models, along with their advantages and disadvantages. Finally, we discuss related work in parallel programming environments, including dedicated programming languages as well as libraries, before providing an overview of related work in distributed data structures and high-level programming models for parallel programs in general.

## 2.1 Execution Models for Parallel Programs

In order to execute a program in parallel across multiple computers, we need some model for how the code will be executed across multiple computers. In a distributed memory context, execution models roughly fall into two categories, single program multiple data (SPMD), and task-based models. In this thesis, we assume a SPMD execution model, although the RDMA-based data structures discussed here are applicable regardless of execution model.

#### SPMD Execution Model

In the SPMD execution model, a single program is run by multiple processes. Typically, when users execute a program, they select the number of processes that it should be started with (often stylized as nprocs). nprocs copies of the program will then be started on different processes, with different processes possibly being executed on different nodes in a cluster. Parallel execution frameworks will usually provide programmers with a mechanism for each process to obtain its process ID (often stylized as rank) as well as the total number of processes nprocs. These processes may then communicate with each other using a variety of mechanisms, depending on the communication model in use.

A simple example of a parallel program written using the SPMD execution model is shown in Figure 1. When the user starts the program, as with mpirun -n 4 ./spmd example in the

execution printout, multiple copies of the program will be executed on different processes based on the number of processes specified by the user. Each statement in the program will be executed by each process, as with the printf statement, unless an explicit branch prevents it, as with the if statement. Each process has access to its process ID and the total number of processes. The program in Figure 1 is written using BCL [26], the framework described in this thesis, but in most other communication frameworks, including MPI [110], OpenSHMEM [34], GASNet-EX [24], and others, the corresponding programs would be written with only slightly modified syntax.

**Algorithm 1** Simple example of a program using the SPMD execution model, with an observed execution output in the comment below. Note that the lines could print in different orders, depending on the order in which processes execute the program.

```

#include <bcl/bcl.hpp>

int main(int argc, char** argv) {

BCL::init();

printf("Hello, World! I am rank number %lu out of %lu\n",

BCL::rank(), BCL::nprocs());

if (BCL::rank() == 0) {

printf("Special hello from rank %lu\n",

BCL::rank());

}

BCL::finalize();

return 0;

}

Execution output:

$ mpirun -n 4 ./spmd example

Hello, World! I am rank number 1 out of 4

Hello, World! I am rank number 2 out of 4

Hello, World! I am rank number 3 out of 4

Hello, World! I am rank number 0 out of 4

Special hello from rank O

*/

```

The SPMD execution model is the dominant execution model used for batch computing jobs on supercomputers. This is likely due to scalability concerns, since as the number

of processes in a distributed execution increases, the overhead associated with spawning additional tasks increases. The SPMD model reduces the overhead of spawning tasks inside the actual program execution by taking care of this with one large execution at program startup.

### Task-Based Models

In task-based execution models, programs are expressed as a collection of discrete tasks, where each task is to be executed by a single processor. These tasks may either be dynamically spawned on demand at runtime, as is the case in systems like Parallel Virtual Machine (PVM) [49] and Ray [81], or, if the complete task graph is known ahead of time, they may be spawned by a runtime system with an intelligent scheduler, as is the case with systems like Legion [21]. The core difference between the SPMD execution model and task-based models is how users express their programs, with users needing to segment their programs into tasks in a task-based model and users needing to think about different processes or groups of processes in the SPMD model. One of the advantages of task-based models is that the user does not necessarily have to explicitly define how their program should be distributed, but a static or dynamic scheduler can instead make the decision about how to partition tasks across nodes in a cluster. An intelligent scheduler can then make optimal decisions for any particular number of processors, partitioning tasks in such a way as to maximize parallelism.

Some frameworks that support remote procedure calls (RPCs), such as UPC++ [17], can be viewed as a hybrid approach that blend aspects of task-based models into a SPMD execution model. For example, while UPC++ programs are executed across a set number of processes chosen by the user at runtime, UPC++ allows users to describe their programs in terms of tasks, and users can compose these tasks into arbitrarily complex task graphs using futures and continuations. Unlike traditional task-based models however, the user must explicitly specify on which process each RPC task should be executed, which requires the user to determine how the computation should be split up amongst the available processes in the distributed execution.

## 2.2 Communication Models for Parallel Programs

Given a particular execution model, there are multiple mechanisms that can be used to communicate between processes. These are roughly split into variants of the bulk synchronous model, which separates communication and local computation into discrete phases partitioned by global synchronization, and models that use asynchronous forms of one-sided communication with primitives like remote memory operations and RPC.

Before we dive into the different communication models, let's first discuss the underlying mechanisms that can be used to send messages over the network. Message passing, also called *two-sided communication*, is one of the primary methods used for sending data between processes. When using two-sided communication, processes have the ability to send or receive

messages using send or receive calls. In order for a process to send a message to another process, the corresponding process must issue a matching receive call in order to complete the message. Blocking send and receive calls inherently incur some synchronization cost, since two processes must synchronize together in order for the message to be passed between them. If one of the processes is delayed getting to its send or receive call, the other process will be forced to wait, incurring some overhead. Asynchronous versions of send and receive calls do exist, and these can be used to implement asynchronous runtime systems, as is the case with YGM [93] or indeed MPI's own implementation of one-sided remote memory access primitives when RDMA hardware is not available [52].

One-sided communication, by contrast, requires the involvement of only one process to complete. Primary examples include remote get, remote put, and remote atomic operations that are supported by RDMA hardware. In order for a process to access or manipulate another process' shared memory segment, the remote process need not be involved. Instead, the only requirement is that that process' shared segment have been made available to the origin process through some registration process before the remote operation is issued. On systems without native network hardware support for RDMA, one-sided remote operations can be emulated within the communication library in software, although this may incur a runtime cost [44]. In terms of the user-facing communication model, operations are still onesided, since the user does not need to direct the remote process to take part in the operation. Instead, a runtime system will ensure that the remote process performs the remote memory operation at some point. In this vein, remote procedure calls (RPCs) may be considered another form of one-sided operation, since a remote process' involvement will at some point be required to actually run the RPCs, with this typically taking place inside a runtime system. However, this is generally invisible to the user, with the RPC library's runtime system ensuring that each process handles any waiting RPC requests, either using dedicated progress threads that handle requests in the background, or by checking for waiting RPC requests each time a library function is invoked [14].

## **Bulk Synchronous Model**

One of the most dominant paradigms for distributed memory communication in use today is the bulk synchronous parallel model [37]. The bulk synchronous model typically segments applications into alternating phases of communication and computation. These phases are separated from each other by barrier operations which ensure global synchronization between all the processes. During a computation phase, processes independently perform local computation on local data. During a communication phase, these processes work together to communicate data using collective communication operations such as broadcast, allreduce, or all-to-all. Collective communication operations have a number of advantages, such as that they provide a clear boundary for the programmer between local computation and global communication. Not least of collective communication operations' advantages is that they provide a standardized interface for performing communication. This allows communication library implementers to implement a set of standard communication collectives, possibly

with different implementations for different network architectures, messages sizes, and data distributions, and for users to automatically reap the benefits of new algorithms and optimizations once they are implemented. These collective communication operations can be implemented in a topology-aware manner, which allows for them to achieve better performance on low-radix network architectures, where latency between pairs of nodes that are far away from each other may be quite high, and bandwidth quite low. In addition, library implementations of collectives are able to use techniques like recursive doubling and pipelining to achieve asymptotically better performance compared to point-to-point versions [106]. In a high-performance computing context, the MPI communication library [110, 54] is commonly used to implement programs in a bulk synchronous style. MPI implements a number of fundamental primitives for performing bulk synchronous communication, including broadcast, reduce, allreduce, and many others. While these collective operations may be implemented using either one-sided or two-sided operations, the primitives themselves follow the bulk synchronous model, with the corresponding advantages and disadvantages.

It is important to note that while there do exist asynchronous versions of collective operations such as asynchronous broadcast and asynchronous allreduce, and these can allow for greater overlap of communication and computation, these do not allow the same degree of asynchrony as a fully one-sided approach. In general, it is not possible for a process to exit an asynchronous broadcast until at least some other processes have entered the broadcast. In broadcast operations that use low radix topologies along with aggressive pipelining, as is done in collective operations for GPUs in nccl [69], which uses a ring topology, no process can exit the collective operation until all processes have entered it, since the collective's performance depends on pipeline parallelism gained from having all processes send messages simultaneously. This is also true regardless of topology for collectives like reduce and allreduce, where inputs from multiple processes must be accumulated together.

## Partitioned Global Address Space Model

In contrast to the bulk synchronous model, the Partitioned Global Address Space (PGAS) communication model is based around allowing asynchronous one-sided communication operations. In the PGAS model, each process is equipped with a special region of memory called a shared segment. The shared segments are typically allocated once at program startup, with each process having an equally sized shared segment, where the size of the shared segments is configurable at runtime. Processes can use global pointers, which reference memory that lives in the shared segment of some process, to issue one-sided remote get, put, and atomic operations to access and manipulate the memory of other processes. In this way, the shared segments together form a globally addressable memory space. However, this memory space is partitioned across all of the different processes. The PGAS model can allow for more asynchronous algorithms than the bulk synchronous model, since processes do not necessarily need to synchronize with other processes in order to access data. For instance, if a process needs to access part of a distributed data structure, using the PGAS model, the process can simply access that data directly using remote memory operations into the memory of the

remote process. One of the other advantages of the PGAS model is that its communication primitives correspond directly to RDMA primitives that are available in the hardware. This means that when PGAS programs are executed on modern supercomputer or commodity datacenter systems, these one-sided communication operations can be completed with very low latencies, and without requiring the involvement of remote processes.

Examples of parallel programming environments that provide support for PGAS include parallel programming languages such as UPC [41] and Chapel [111], as well as communication libraries such as OpenSHMEM [34], MPI's remote memory access primitives [52], and GASNet [23]

### **RPC-Based Models**

As discussed above, remote procedure calls (RPCs) may be viewed as an extended form of remote memory access that is able to handle more complex control flow. In fact, this was the original vision for active messages (AMs) [47], which are a restricted form of RPC that sends messages carrying a fixed-size data payload along with a pointer to a user space function to be executed. Because of their low-latency design, active messages come with restrictions, namely that their payloads are fixed size and that they cannot issue additional AMs [47, 23]. Active messages can be a very powerful tool, allowing programmers and library developers to implement new, low-latency operations that include more complex control flow than is possible with the current generation of RDMA operations.

Unlike active messages, remote procedure calls in general do not have these restrictions. In most frameworks, RPCs are free to issue additional RPC operations and to carry payload arguments of unlimited size. This creates additional latency due to the additional overhead associated with maintaining an additional RPC queue of potentially unbounded length with variable-size arguments [58].

While both RPC and the more restricted active messages have advantages over RDMA operations in terms of expressiveness, they suffer from performance degradation due to lack of attentiveness. When a process issues an RPC to be executed on a remote process, it must wait until that process finishes any local computation or other communication operations it is involved with, enters a progress function, and dequeues and runs the RPC. When RPCs are interspersed with computation, this may cause a dramatic increase in latency unless resources are dedicated to maintain progress threads. We discuss this tradeoff in further detail in Chapter 8.

## High-Level Parallel Programming Environments

A significant amount of the high-performance computing literature, as well as engineering effort in the HPC space, has been devoted to alleviating the burden on programmers who develop and optimize applications that run in large-scale distributed memory supercomputer as well as commodity datacenter environments.

## Parallel Programming Languages

Most early approaches to developing high-level programming environments for parallel application developers focused on developing new programming languages. A number of dedicated programming languages or language extensions provide language-level support for one-sided remote memory access primitives, almost all using a Partitioned Global Address Space (PGAS) programming model. UPC [41], Titanium [118], X10 [36], High Performance Fortran [72], and Chapel [111, 32] are parallel programming languages which offer a PGAS distributed memory abstraction. There are a number of advantages associated with using a dedicated programming language that has a semantic understanding of a distributed memory space. Chief among them is the ability to perform static optimizations using global program knowledge. This can allow an optimizing compiler to automatically relax synchronization, to convert remote operations into local ones, or to aggregate many small messages together to improve network performance [71]. Language builders also have the ability to restrict the syntax that users have access to, in order to encourage them to write easily parallelizable programs. However, due to the complexities associated with developing and implementing a new programming language, a compiler, and the libraries needed to make it usable, developing parallel programming languages can be a difficult task, and they have historically had difficulties increasing adoption [72, 73].

## High-Level Parallel Programming Libraries

UPC++ is a C++ library which offers a PGAS distributed memory programming model as well as the ability to issue remote procedure calls (RPCs) [121, 16, 17]. UPC++ has a heavy focus on asynchronous programming that is absent from BCL, including futures, promises, and callbacks. UPC++'s RPCs can be used to create more expressive atomic operations, since all RPCs are executed atomically in UPC++. However, these operations require interrupting the remote CPU, and thus have slower throughput than true RDMA atomic memory operations. The current version of UPC++ also lacks a library of data structures, and UPC++ is closely tied to the GASNet communication library, instead of supporting multiple backends.

Global Arrays provides a portal shared memory interface, exposing globally visible array objects that can be read from and written to by each process [86]. While many application-specific libraries have been built on top of Global Arrays, it lacks the kind of high-level generic data structures that are the focus of this work.

#### Distributed Data Structures

DASH is another C++ library that offers a PGAS distributed memory programming model [48]. DASH has a large focus on structured grid computation, with excellent support for distributed arrays and matrices and an emphasis on providing each process with fast access to its local portion of the distributed array. While DASH's data structures are generic, they do

not support storing objects with complex types. DASH is tied to the DART communication library, which could potentially offer performance portability through multiple backends, but is currently limited to MPI for distributed memory communication.

HPX is a task-based runtime system for parallel C++ programs [70]. It aims to offer a runtime system for executing standard C++ algorithms efficiently on parallel systems, including clusters of computers. Unlike BCL, which is designed to use coordination-free RDMA communication, HPX's fundamental primitives are remote procedure calls used to distribute tasks.

STAPL, or the standard adaptive template library, is an STL-like library of parallel algorithms and data structures for C++ [105]. STAPL programs are written at a much higher level of abstraction than BCL, in a functional style using special higher-order functions such as map, reduce, and for-each which take lambda functions as arguments. From this program description, STAPL generates a hybrid OpenMP and MPI program at compile time. Some versions of STAPL also include a runtime which provides load balancing. The current version of STAPL is only available in a closed beta and only includes array and vector data structures [103].

PETSc, Chombo, and AMReX provide data structures for sparse and dense matrices and structured and unstructured grids, but do not focus on the types of irregular, generic data structures discussed here [1, 40, 120].

Aguilera, et al. have proposed various hardware extensions to RDMA specifically to allow for the efficient execution of operations on remote data structures in NIC hardware [3]. These include an indirect access primitive that can be used to access a value at an offset from a pointer on a remote node, allowing for a dynamically resizing remote vector; various scatter and gather primitives, and a form of notifications. We believe that the performance model presented here, in Chapter 8, is good fit for evaluating potential new RDMA instructions, and that similar microbenchmark analysis can help hardware and software developers to design and evaluate new hardware and data structures.

## **RPC-Based Programming Models**

AM++ is C++ library built on top of MPI that provides a high-level active message API similar to that discussed in this paper [113]. Active Pebbles extends AM++ by adding support for message aggregation and more sophisticated termination detection mechanisms [112]. You've Got Mail (YGM) is an MPI-based system that provides an active message-like API with message- and node-level aggregation [93].

The Multipol library provided a set of concurrent data structures on top of active messages, including dynamic load balancing and optimistic task schedulers [31]. However, it was non-portable and did not have the rich set of hash table data structures discussed here nor the notion of concurrency promises.

The Python-based parallel programming frameworks Ray [81] and Dask [95] expose parallelism using RPCs. However, both of them use a scheduler to automatically determine

where to place RPCs within a cluster, rather than requiring users to explicitly declare where tasks should be executed.

## Libraries for Aggregation

Message aggregation is an important technique for optimizing the execution of parallel applications that perform a large number of fine-grained operations. By bundling up many small messages together into larger aggregated messages, the latency costs associated with sending many small messages over the network can be eliminated. Aggregation systems that automatically bundle communication operations together can thus transform what would otherwise be latency-bound problems into bandwidth-bound ones.

Significant work has been done on using aggregation within some of the parallel programming environments already discussed, such as UPC and UPC++ [51, 17], but some libraries have been specifically developed to support aggregation. Bale is a C library designed to support aggregation, offering the core abstraction of *conveyors*, which are dedicated streams shuttling data between processes [79]. Each process can pull data from a conveyor or push data to a particular process using a conveyor. The Bale system will automatically aggregate pieces of data that need to be transferred across the conveyor, and parameters such as target message size can be tuned independently after a program has been written.

Many RPC-based programming environments also offer tools to automatically aggregate RPC requests together, sending them over the network in larger bundled messages. The previously mentioned Active Pebbles [112] implements aggregation automatic aggregation of RPCs on top of the AM++ [113] programming environment, while YGM [93] implements an RPC-like with node-level aggregation directly over MPI. The library ARL [114] implements a future-based RPC interface with automatic node-level aggregation on top of GASNet.

## Chapter 3

## Building Distributed Data Structures

This chapter introduces the overall design used to develop RDMA-based distributed data structures in this work, starting with a discussion of the hardware capabilities of modern RDMA-based networks in regards to building distributed data structures. We follow with a detailed introduction of the *BCL Core*, which is the cross-platform communication API, based on global pointers, that we use to implement distributed data structures. We then discuss how this API can be augmented to support complex user-defined types and extended to support addressing other types of remote memory, such as memory resident on GPUs. We then continue with an overview of the general user-side interface for constructing and manipulating distributed data structures as well two mechanisms for allowing user-guided control of data structure optimizations, concurrency promises and buffers.

## 3.1 RDMA-Based Communication Primitives

This chapter discusses the BCL Core, which is a set of RDMA-based communication primitives for implementing distributed data structures. The BCL Core provides a core abstraction of global pointers, which are pointer-like C++ objects that can be used to reference memory residing in the shared segment of another process. Users can interact with global pointers in a similar manner to how they would interact with regular pointers, such as dereferencing them to access individual data elements, issuing bulk data copies, or invoking atomic operations such as compare-and-swap. Operations on global pointers correspond directly to Remote Direct Memory Access (RDMA) primitives supported by most modern supercomputer interconnects, as well as in many commodity datacenter environments. This means that operations on global pointers can be executed directly in the network hardware, which helps reduce latency and prevents the need for direct synchronization between remote processes. In addition, the one-sided nature of RDMA network communication corresponds directly to the one-sided nature of most traditional data structures, which typically involve one thread of executing manipulating a data structure using operations like insertions, retrievals, pushes or pops.

## RDMA-Based Network Communication Capabilities

Before discussing a specific software API, it is important to consider the RDMA hardware capabilities of modern Network Interface Cards (NICs). While the precise capabilities of different RDMA NICs varies, we can identify a common subset of RDMA operations supported by the vast majority of RDMA-supporting networks, as well as their general synchronization models and performance characteristics. When describing RDMA operations on remote memory, we will refer to two processes, the *local* or origin process that is issuing the RDMA operation and the *remote* process whose memory is being accessed. *Remote get* and *remote put* are the two most fundamental operations supported by RDMA.

Remote put operations copy a block of data from a local buffer into a region of a destination process' memory. Typically, one or more network packets are sent across the network to the remote NIC. As these packets are received at the destination, a DMA (Direct Memory Access) engine on the NIC copies them directly into DRAM memory. To signal to the origin process that the remote put operation has completed, the destination NIC must send a signal back to the origin, completing the roundtrip. The origin process can wait on this message in order to synchronize on the completion of the put operation. In order to access remote memory using RDMA operations, the memory must be registered with the NIC, allowing the NIC to directly read or write into that memory when it receives an RDMA request over the network. It is also important to note that before a put operation is completed, RDMA-based networks do not necessarily check the validity of data that arrives in the buffer, nor do they guarantee the order in which data may arrive in the buffer. This is because it is possible for packets to arrive out of order or even with corrupted data when they are initially copied into the destination buffer. Only when the operation fully completes is the data guaranteed to be fully copied.

Remote get operations copy data from the memory of a remote process into a local buffer on the origin process. Remote get operations typically operate by signaling to the remote NIC to issue a remote put operation copying the desired remote data back into a buffer on the local process. In order for the data to be copied back onto the origin process, the local receive buffer must be registered with the NIC. This can either happen on-demand at the time the remote get is issued, in which case the registration of the local output buffer will incur a fixed cost, or it can be done beforehand using a bounce buffer of pre-registered memory [78]. Typically, the bounce buffer is used for small, fine-grained transfers where the cost of an additional copy is minimal, while the local output buffer is registered for larger transfers where the cost of the registration is amortized by the time to copy the data over the network [77].

In addition to remote get and remote put operations, the vast majority of RDMA networks offer remote *atomic operations*, which perform a restricted set of read-modify-write operations atomically to locations in remote memory. These atomic operations include atomic operations common in the CPU domain such as compare-and-swap on 32 and 64 bit value, as well as basic integer arithmetic, including fetch-and-add, fetch-and-AND, fetch-and-OR, etc. on 32 or 64-bit integers. Some networks support a broader set of atomic or other synchro-

nization primitives, such as extended size atomics, which can operate on larger word sizes, or signaling puts, which signal when a put has completed by updating an additional memory location. However, due to a lack of portability, these extended atomics are not widely supported by communication libraries. Thus, in this work, we largely restrict ourselves to remote get, remote put, and 64-bit atomic operations.

Since RDMA get, put, and atomic operations can all be executed directly in the NIC, they can be completed with very low latency, typically on the order of 2 to 4 microseconds on modern supercomputer and commodity Ethernet networks. Atomic operations sometimes take slightly longer, particularly if many processes are modifying the same value. However, even under high contention, a single remote atomic operation is unlikely to take longer than 6-8 microseconds, even at high concurrencies. Note that this hardware latency of a single atomic operation is distinct from the overall latency of, for example, obtaining a lock if multiple retries over the network are required.

Small RDMA transfers, for example an RDMA put of 512 bytes or smaller, are entirely bound by latency. As the transfer size grows, however, RDMA transfers quickly achieve better performance, becoming bound by network bandwidth once reaching a transfer size of around 4 KB on Cray Aries networks, although the optimal message sizes do vary by network [24]. In microbenchmarks, RDMA-based communication libraries like GASNet-EX are able to reach peak bandwidth at lower message sizes compared to two-sided communication primitives [24].

## An API for Building RDMA-Based Data Structures

One of the main goals of this work is to provide a collection of high-level data structures that are cross-platform, meaning that they can be used within programs written using a variety of different communication libraries. To accomplish this, BCL uses a small cross-platform internal API called the BCL Core. The BCL Core is supported by a number of different communication backends which implement a limited number of fundamental communication operations, typically using low-level communication libraries. These include an initialize function, which initializes the communication library including a shared segment of globally accessible memory on each process, as well as basic communication functions manipulating these shared segments such as remote puts, gets, and atomic operations. One of these communication backends is chosen at compile time using compiler directives. There are three primary advantages to this approach. First, supporting a variety of communication libraries aids integration of high-level data structures into an already-existing library. Since the BCL library only consists of code that calls functions in the backend communication library, BCL typically can be included as a header-only library without modifications to the compiler toolchain. Second, this allows more opportunity for portability and performance tuning for programs that only use BCL programs, since they can be compiled with any of the supported communication libraries. This is particularly useful when dealing with a collection of varied supercomputer or commodity cluster environments whose optimized communication libraries may not intersect. Third, implementing data structures on top of an internal DSL allows for new communication libraries to be supported more easily, including both traditional distributed memory communication libraries as well as communication libraries that target new or experimental hardware, such as communication between GPUs or with custom hardware.

While the BCL Core is a full-fledged distributed programming environment and can be used to implement complex distributed programs, such as the data structures discussed in this work, users need not learn or use any of the BCL Core functionality discussed here—outside of the BCL::initialize(), BCL::finalize(), and BCL::barrier() functions—in order to use them. The main contribution of the BCL Core is that it provides a minimal set of communication functionality for implementing RDMA-based distributed data structures.

The BCL Core provides a high-level PGAS memory model based on *global pointers*, which are C++ objects that allow the manipulation of globally accessible regions of remote memory. During initialization of the BCL library, each process creates a *shared memory segment* of a fixed size, and throughout the program every process can read and write from or to any location within any process's shared segment using global pointers.

Global pointers are C++ objects that keep track of (1) the rank, or process ID number of the process on which the memory being pointed to is located, as well as (2) a particular offset within that process' shared memory segment. Together, these two parameters uniquely identify an address in global memory. Global pointers are regular, trivially copyable C++ objects and can be passed around between BCL processes using communication primitives, or indeed themselves be stored using global memory. Global pointers support pointer arithmetic operations, comparison, dereference, and other operators and methods, making them analogous to local pointers. They also fulfill the std::random\_access\_iterator concept in the C++ standard library.

An important limitation of global pointers is that they may only be used to reference trivially copyable objects, which are objects which can be copied by copying their byte level representation, as would be done with memcpy. If a type has a trivial copy constructor, it means we can byte copy that object into and out of remote memory. Types that do not have trivial copy constructors often use dynamic memory management or perform other operations that would cause their internal representations to be invalid if byte copied over the network. We discuss a low-overhead mechanism for storing non trivially copyable types using serialization in Section 3.3.

Global pointers can be used in a number of basic communication functions that implement primitives such as *remote get* and *remote put*, which read from or write to remote memory. They can also be used with atomic operations such as *fetch-and-op* (with support various operators such as addition, subtraction, and bitwise operations) as well as the more fundamental *compare-and-swap*.

#### Communication Primitives

### Writing and Reading

The BCL Core's primary memory operations involve writing and reading to and from global pointers. Remote get operations read from a global pointer and copy the result into local memory, and remote put operations write the contents of an object in local memory to a shared memory location referenced by a global pointer. Remote gets and remote puts can be done with a number of different communication functions, including BCL::memcpy(), which functions similarly to the standard std::memcpy(), as well as various versions of BCL::rput() and BCL::rget(), which can transfer individual elements as well as arrays of data.

### **Memory Allocation**

The BCL Core provides methods that allow each process to allocate and deallocate memory within its own shared segment. This is implemented by the BCL Core itself using the shared segment allocated by the BCL backend. Remote memory allocation is the ability for processes to asynchronously allocate memory resident in the shared segment of another In PGAS environments that also support remote procedure calls (RPC), remote memory allocation can be trivially supported by invoking an RPC on a remote process that then allocates memory in the desired shared segment, returning a global pointer to the newly allocated memory [16]. However, in the absence of RPC, adding support for remote memory allocation using only RDMA primitives must rely on remote atomics. This would require either adding a significant performance penalty for allocation operations performed in local shared segments or bifurcating memory to allow remote allocations using remote atomics in a special region, reducing the size of the largest possible memory allocation and fragmenting memory. In addition, freeing and compacting remote memory introduces significant challenges. Thus, this work does not assume remote memory allocation as a fundamental primitive, and instead relies on processes using coordination to communication pointers to remote memory. This is usually done using broadcast operations to communicate pointers to newly allocated memory during collective data structure construction or resize operations.

## Synchronization and Memory Model

The BCL Core's communication primitives follow a relaxed consistency model shared by most low-level communication libraries, which allows remote put operations to be completed lazily in a "nonblocking" manner. When a remote put operation returns, the local buffer whose data is to be copied to a remote location is free to be modified without interrupting the operation. However, the data is not necessarily finished copying in place at the remote location until a barrier or flush operation has been completed, which serves as a memory fence and ensures that all previous remote memory operations are completed before the

program continues. Remote get operations are completed synchronously—the data is copied from the remote memory location to the local memory buffer immediately, and when the call returns the local memory buffer with the copied data is available to be read. Remote atomic operations are completed immediately, but do not necessarily force completion of any previous memory operations, necessitating the addition of a flush if an atomic is to signal the completion of some other remote memory operation.

## **Asynchronous Operations**

BCL also supports asynchronous remote get, put, and atomic operations, which must be synchronized using individual request objects to ensure completion. Unlike regular remote put operations, when an asynchronous put operation returns, the local input buffer cannot be modified without interfering with the operation until after waiting on the operation's completion handle. Similarly, for remote get operations and atomic operations, the local output buffer is not guaranteed to be ready with the results of the operation until after waiting on the corresponding completion request. Request objects have two methods, check, which returns whether or not the request has been completed, and wait, which waits until the request has been completed. Since each communication library may have different synchronization handles and mechanisms, the request class is implemented by the backend. Each request handle implementation typically requires around 20 lines of code.