# Disruptive Research on Distributed Machine Learning Systems

Guanhua Wang

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-83 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-83.html

May 12, 2022

Copyright © 2022, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Disruptive Research on Distributed Machine Learning Systems

by

#### Guanhua Wang

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ion Stoica, Chair Professor Joseph Gonzalez Professor Alexandre Bayen Professor Michael Mahoney

Spring 2022

### Disruptive Research on Distributed Machine Learning Systems

Copyright 2022 by Guanhua Wang

#### Abstract

Disruptive Research on Distributed Machine Learning Systems

by

#### Guanhua Wang

Doctor of Philosophy in Computer Science

University of California, Berkeley

Professor Ion Stoica, Chair

Deep Neural Networks (DNNs) enable computers to excel across many different applications such as image classification, speech recognition and robotic control. To accelerate DNN training and serving, parallel computing is widely adopted. System efficiency is a big issue when scaling out. High communication overheads and limited on-device memory are two major causes for system inefficiency in distributed machine learning.

This dissertation studies possible ways to mitigate communication bottlenecks and achieve better on-device memory utilization in data and model parallelism for distributed machine learning workloads.

On the communication side, our Blink project mitigates communication bottleneck in data parallel training. By packing spanning trees rather than forming rings, Blink achieves higher flexibility in arbitrary networking environments and provides near-optimal network throughput. To eliminate the communication in model parallel training and inference, we go above from system layer to application layer. Our sensAI project decouples a multi-task model into disconnected subnets, where each subnet is responsible for decision making of a single task or a subset of the original task-set.

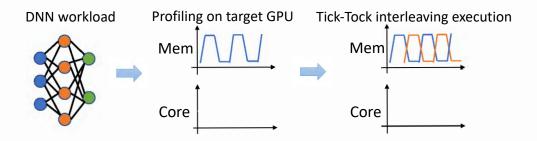

Towards better utilization of on-device memory, our Wavelet project intentionally adds task launching latency to interleave peak memory usage across different waves of training tasks on the accelerators. By packing multiple training waves on the same accelerator, it improves both computation and on-device memory utilization.

To my parents, Ying Han and Xin Wang.

### Contents

| Co | contents |                                             |                 |

|----|----------|---------------------------------------------|-----------------|

| Li | st of    | Figures                                     | $\mathbf{v}$    |

| Li | st of    | Tables                                      | ix              |

| 1  | Intr     | oduction                                    | 1               |

|    | 1.1      | Motivation                                  | 1               |

|    | 1.2      | Thesis Contributions                        | 2               |

|    | 1.3      | Thesis Organization                         | 3               |

| 2  | Bac      | kground                                     | 5               |

|    | 2.1      | Deep Learning Models                        | 5               |

|    |          | 2.1.1 Training                              | 6               |

|    |          | 2.1.2 Serving                               | 7               |

|    | 2.2      | Data Parallelism                            | 8               |

|    | 2.3      | Model Parallelism                           | 10              |

| 3  | Fast     | ter Collective Communication                | 12              |

|    | 3.1      | Background                                  | 12              |

|    |          | 3.1.1 Ring-based Collectives                | 12              |

|    |          | 3.1.2 Topology Heterogeneity                | 13              |

|    | 3.2      | Motivation                                  | 15              |

|    |          | 3.2.1 Trees vs Rings                        | 16              |

|    |          | 3.2.2 Micro-benchmarks                      | 18              |

|    | 3.3      | Blink Design                                | 21              |

|    |          | 3.3.1 System Overview                       | 22              |

|    |          | 3.3.2 Packing Spanning Trees                | 22              |

|    |          | 3.3.3 Approximate Tree-Packing              | 23              |

|    |          | 3.3.4 Extending to Many-to-many Collectives | $\frac{-3}{24}$ |

|    |          | 3.3.5 Hybrid Communication                  | $\frac{1}{25}$  |

|    |          | 3.3.6 DGX-2 and Multi-machine Settings      | 25              |

|   | 3.4  | Implementation                                      | 2  |

|---|------|-----------------------------------------------------|----|

|   |      | 3.4.1 Automatic Chunk Size Selection                | 27 |

|   |      | 3.4.2 Link Sharing                                  |    |

|   | 3.5  |                                                     |    |

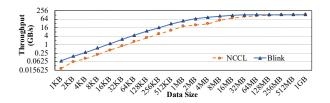

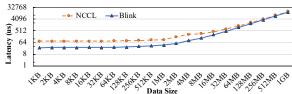

|   |      | 3.5.1 Broadcast and AllReduce Micro-benchmarks      |    |

|   |      | 3.5.1.1 NVLink Broadcast                            |    |

|   |      | 3.5.1.2 NVLink AllReduce                            |    |

|   |      | 3.5.1.3 NVSwitch AllReduce                          |    |

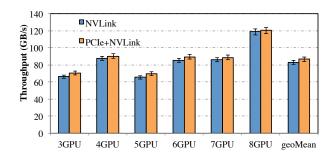

|   |      | 3.5.2 Hybrid Transfer                               |    |

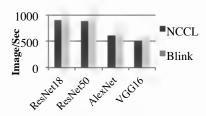

|   |      | 3.5.3 End-to-end DNN Training                       |    |

|   |      | 3.5.3.1 Single Machine                              |    |

|   |      | 3.5.3.2 Multiple Machine                            |    |

|   | 3.6  | 6 Related Work                                      | 32 |

|   | 3.7  | 7 Summary                                           |    |

|   |      | v                                                   |    |

| 4 | Elir | iminating Communication in Model Parallelism        | 34 |

|   | 4.1  | 0                                                   |    |

|   | 4.2  |                                                     |    |

|   | 4.3  |                                                     |    |

|   |      | 4.3.1 Overview                                      |    |

|   |      | 4.3.2 Class-specific Pruning                        |    |

|   |      | 4.3.2.1 Binary Classifiers                          |    |

|   |      | 4.3.2.2 Grouped Classifiers                         |    |

|   |      | 4.3.3 Retraining                                    |    |

|   |      | 4.3.4 Combining Results Back to N-way Predictions . |    |

|   | 4.4  |                                                     |    |

|   |      | 4.4.1 Datasets and Models                           |    |

|   |      | 4.4.2 CIFAR-10 Results                              |    |

|   |      | 4.4.2.1 Pruning Policy Comparison                   |    |

|   |      | 4.4.2.2 sensAI Evaluation on VGG-19 and Res         |    |

|   |      | 4.4.2.3 sensAI vs Model Parallel Baseline           |    |

|   |      | 4.4.2.4 sensAI vs OVA                               |    |

|   |      | 4.4.2.5 sensAI Improvements on Efficient CNN        |    |

|   |      | 4.4.2.6 Binary Models Analysis                      |    |

|   |      | 4.4.3 CIFAR-100 Results                             |    |

|   |      | 4.4.3.1 sensAI vs single GPU Baseline               |    |

|   |      | 4.4.3.2 sensAI vs Model Parallel Baseline           |    |

|   |      | 4.4.4 ImageNet-1K Results                           |    |

|   |      | 4.4.4.1 sensAI vs Single GPU Baseline               |    |

|   |      | 4.4.4.2 sensAI vs Model Parallel Baseline           |    |

|   | 4.5  |                                                     |    |

|   | 4.6  | Extending to Model Training                         | 52 |

| 4.7 | Extending to Fault Tolerance, Robotic Control, and Beyond |   |

|-----|-----------------------------------------------------------|---|

| 4.8 | Summary                                                   |   |

| Imp | oving on-device memory utilization                        |   |

| 5.1 | Background                                                |   |

| 5.2 | Motivation                                                |   |

|     | 5.2.1 Zoom-in Analysis over Data Parallel Training        |   |

|     | 5.2.2 Sub-iteration Analysis on Model Parallel Training   |   |

| 5.3 | Wavelet Design                                            |   |

|     | 5.3.1 Overview                                            |   |

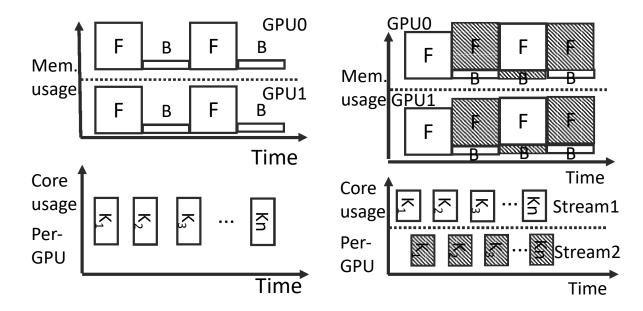

|     | 5.3.2 Wavelet in Data Parallelism                         |   |

|     | 5.3.2.1 Memory Overlapping                                |   |

|     | 5.3.2.2 Computation Overlapping                           |   |

|     | 5.3.2.3 Model Synchronization between Waves               |   |

|     | 5.3.3 Wavelet in Model Parallelism                        |   |

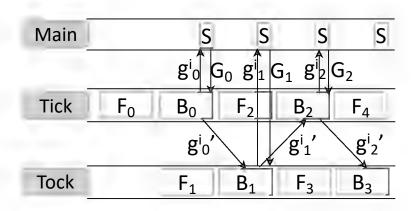

|     | 5.3.3.1 Launching Multiple Tock-wave Tasks                |   |

|     | 5.3.3.2 Model Partition Switching                         |   |

|     | 5.3.3.3 Inter-batch Synchronization                       |   |

| 5.4 | Evaluation $\ldots$                                       |   |

|     | 5.4.1 Data Parallelism                                    |   |

|     | 5.4.1.1 Single-machine Multi-GPU                          |   |

|     | 5.4.1.2 Multi-machine Multi-GPU                           |   |

|     | 5.4.2 Model Parallelism                                   |   |

|     | 5.4.2.1 Single-machine Multi-GPU                          |   |

|     | 5.4.2.2 Multi-machine Multi-GPU                           |   |

|     | 5.4.2.3 Overhead Analysis                                 |   |

| 5.5 | Related Work                                              |   |

| 5.6 | Summary                                                   | • |

| Fut | re Work and Conclusion                                    |   |

| 6.1 | Future Directions                                         |   |

## List of Figures

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | A toy example of normal deep learning model.  Forward propagation and backward propagation in DNN model training.  Data parallel training paradigm.  Model synchronization in data parallel training.  Model parallelism paradigm. | 5<br>6<br>8<br>9 |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|                                 |                                                                                                                                                                                                                                    |                  |

| 3.1<br>3.2                      | NVLink topology of DGX-1 8-GPU server (left with P100 GPUs, right with V100                                                                                                                                                        | 13<br>14         |

| 3.3                             | <b>,</b>                                                                                                                                                                                                                           | 15               |

| 3.4                             | Number of GPUs placement for each job within each 8-GPU server on a cloud                                                                                                                                                          |                  |

|                                 | cluster allocated with 40,000 multi-GPU jobs                                                                                                                                                                                       | 15               |

| 3.5                             |                                                                                                                                                                                                                                    | 16               |

| 3.6                             |                                                                                                                                                                                                                                    | 16               |

| 3.7                             | 6-GPU topology on DGX-1-P100                                                                                                                                                                                                       | 17               |

| 3.8                             | NCCL 6-GPU Rings (Broadcast from GPU3)                                                                                                                                                                                             | 17               |

| 3.9                             | Blink 6-GPU spanning trees (Broadcast from GPU3)                                                                                                                                                                                   | 17               |

| 3.10                            | Best-worst case of communication percentage regarding to end-to-end DNN train-                                                                                                                                                     |                  |

|                                 | ing iteration time (DGX-1-P100)                                                                                                                                                                                                    | 18               |

| 3.11                            | Best-worst case of communication percentage regarding to end-to-end DNN train-                                                                                                                                                     |                  |

|                                 | ing iteration time (DGX-1-V100)                                                                                                                                                                                                    | 18               |

| 3.12                            | Breadth Test: Fan-in forward                                                                                                                                                                                                       | 19               |

| 3.13                            | Breadth Test: Fan-in reduce and forward                                                                                                                                                                                            | 19               |

| 3.14                            | Breadth Test: Fan-out forward                                                                                                                                                                                                      | 19               |

|                                 |                                                                                                                                                                                                                                    | 19               |

| 3.16                            | Breadth Test Throughput: Fan-in reduce and forward                                                                                                                                                                                 | 19               |

| 3.17                            | Breadth Test Throughput: Fan-out forward                                                                                                                                                                                           | 19               |

| 3.18                            | Depth Test: chain forward                                                                                                                                                                                                          | 20               |

| 3.19                            | Depth Test: chain reduce and forward                                                                                                                                                                                               | 20               |

| 3.20                            | Depth Test: chain reduce and broadcast                                                                                                                                                                                             | 20               |

| 3.21                            | Depth Test Throughput: chain forward only                                                                                                                                                                                          | 20               |

| 3.22                            | Depth Test Throughput: chain reduce and forward                                                                                                                                                                                    | 20               |

| 3.23                            | Depth Test Throughput: chain reduce and broadcast                                                                                                                                                                                  | 20               |

| 3.24 | Multi-Input, Multi-Output (MIMO)                                                  | 20 |

|------|-----------------------------------------------------------------------------------|----|

|      | Multi-chain aggregation (MCA)                                                     | 20 |

| 3.26 | MIMO and MCA throughput                                                           | 20 |

| 3.27 | Blink workflow                                                                    | 21 |

| 3.28 | Blink's Three-phase AllReduce protocol for cross-machine settings                 | 25 |

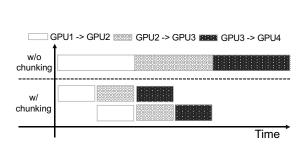

| 3.29 | Chunking data to reduce multi-hop network latency.                                | 26 |

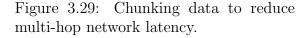

| 3.30 | Automatic chunk size selection using multiple-increase additive-decrease (MIAD).  | 26 |

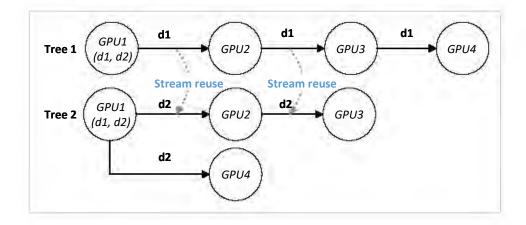

| 3.31 | Stream reuse for fair sharing of links                                            | 27 |

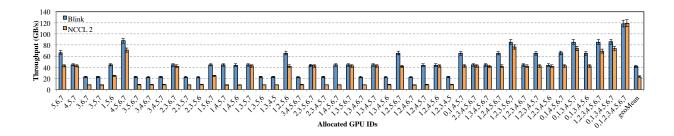

| 3.32 | Broadcast throughput comparison between Blink and NCCL for all unique topolo-     |    |

|      | gies in DGX-1-V100 machine                                                        | 28 |

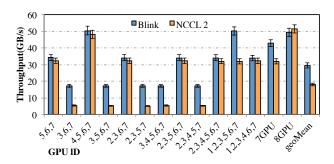

| 3.33 | Broadcast throughput comparison between Blink and NCCL for all unique topolo-     |    |

|      | gies in DGX-1-P100 machine                                                        | 28 |

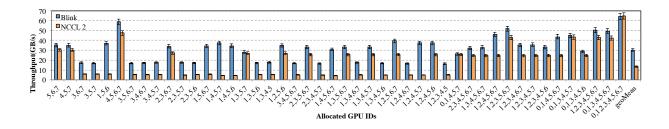

| 3.34 | AllReduce throughput comparison between Blink and NCCL for all unique topolo-     |    |

|      | gies in DGX-1-V100 machine                                                        | 29 |

| 3.35 | AllReduce throughput comparison between Blink and NCCL on a 16-GPU DGX-           |    |

|      | 2 machine                                                                         | 29 |

| 3.36 | All<br>Reduce latency comparison (in $\mu s$ ) between Blink and NCCL on a 16-GPU |    |

|      | DGX-2 machine.                                                                    | 29 |

| 3.37 | Broadcast throughput comparison between hybrid and NVLink-only with various       |    |

|      | number of GPUs on DGX-1-V100 machine                                              | 30 |

| 3.38 | Blink training time reduction for each iteration over 4 popular DNNs on ImageNet- |    |

|      | 1K dataset                                                                        | 31 |

| 3.39 | Blink communication time reduction over each iteration on ImageNet-1K dataset.    | 31 |

| 3.40 |                                                                                   |    |

|      | V100 machines                                                                     | 32 |

| 3.41 | AllReduce throughput projections given potential high bandwidth cross-machine     |    |

|      | interconnects                                                                     | 32 |

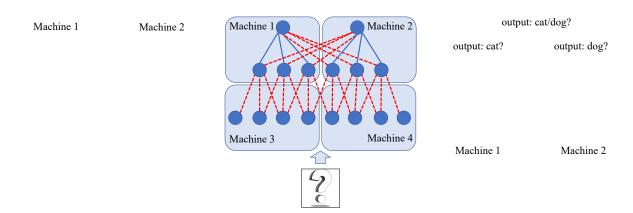

| 4.1  | Data Parallel model serving                                                       | 35 |

| 4.2  | Model Parallel model serving                                                      | 35 |

| 4.3  | Class Parallel model serving (sensAI)                                             | 35 |

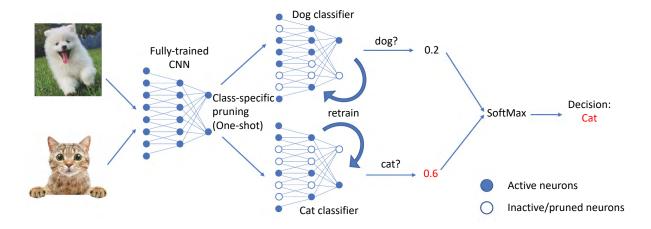

| 4.4  | sensAI's three-phase workflow for class-parallel inference                        | 36 |

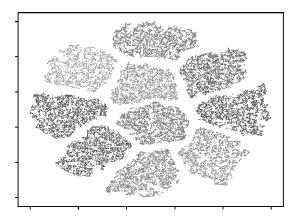

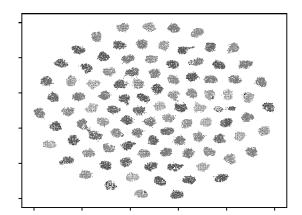

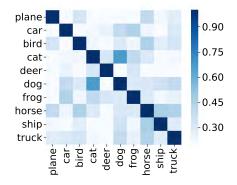

| 4.5  | t-SNE visualization for feature representation of all training images with fully- |    |

|      | trained VGG-19 on CIFAR-10 dataset                                                | 38 |

| 4.6  | t-SNE visualization for feature representation of all training images with fully- |    |

|      | trained VGG-19 on CIFAR-100 dataset.                                              | 38 |

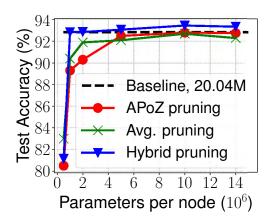

| 4.7  | Pruning method comparison among APoZ, Avg, and our hybrid solutions (VGG-         |    |

|      | 19, CIFAR-10)                                                                     | 40 |

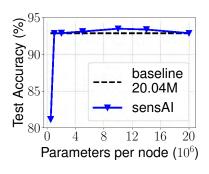

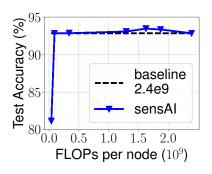

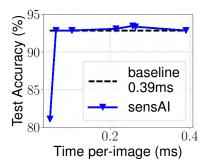

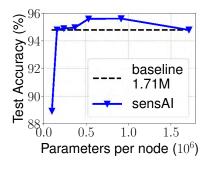

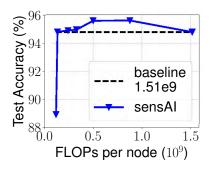

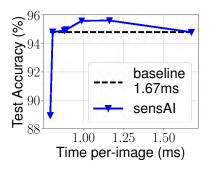

| 4.8  | Number of Parameters vs test accuracy comparison (VGG-19, CIFAR-10)               | 41 |

| 4.9  | FLOPs consumption vs test accuracy comparison (VGG-19, CIFAR-10)                  | 41 |

| 4.10 | Per-image inference time vs test accuracy comparison (VGG-19, CIFAR-10)           | 41 |

| 4.11 | Number of Parameters vs test accuracy comparison (ResNet-164, CIFAR-10)           | 42 |

|      | FLOPs consumption vs test accuracy comparison (ResNet-164, CIFAR-10)                                                                               | 42 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Per-image inference time vs test accuracy comparison (ResNet-164, CIFAR-10).                                                                       | 42 |

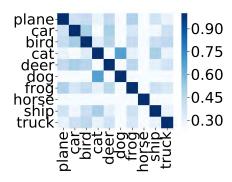

| 4.14 | Similarity comparison among binary classifiers by measuring IoU on channels (VGG-19, CIFAR-10)                                                     | 46 |

| 4.15 | Similarity comparison among binary classifiers by measuring IoU on channels (ResNet-164, CIFAR-10)                                                 | 46 |

| 4.16 | Similarity comparison among binary classifiers by measuring IoU on channels (ShuffleNet-V2, CIFAR-10)                                              | 46 |

| 4.17 | Similarity comparison among binary classifiers by measuring IoU on channels (MobileNet-V2, CIFAR-10)                                               | 46 |

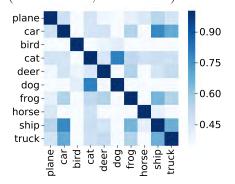

| 4.18 | Robust Class Parallelism with Cyclic Coding                                                                                                        | 54 |

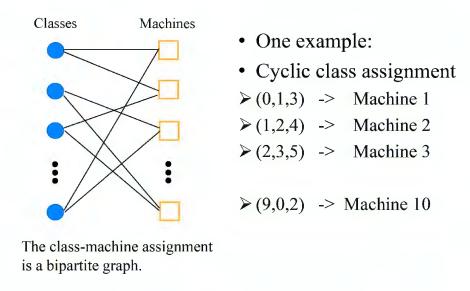

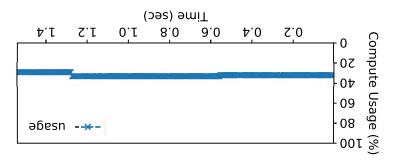

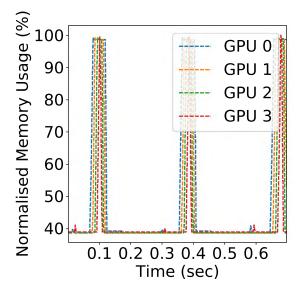

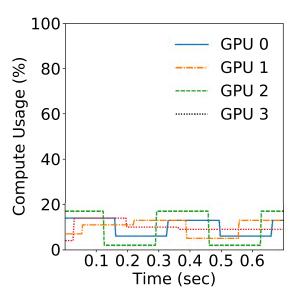

| 5.1  | Normalized on-device memory usage of data parallel training job using 2 V100 GPUs with gang-scheduling                                             | 57 |

| 5.2  | Normalized computation usage of data parallel training job using 2 V100 GPUs with gang-scheduling                                                  | 57 |

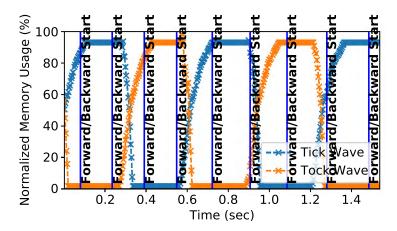

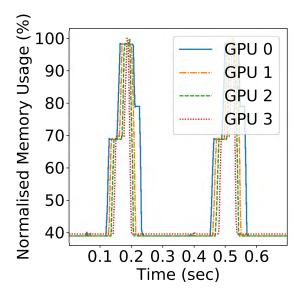

| 5.3  | Normalized on-device memory usage of data parallel training job using 2 V100 GPUs with tick-tock scheduling                                        | 58 |

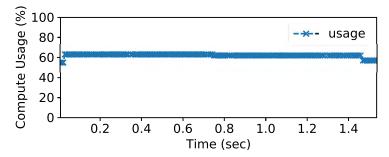

| 5.4  | Normalized computation usage of data parallel training job using 2 V100 GPUs with tick-tock scheduling.                                            | 58 |

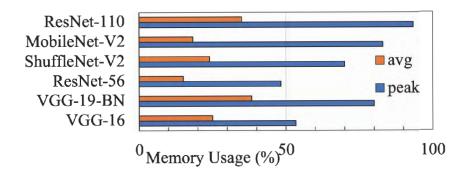

| 5.5  | Normalized peak and average GPU memory usage during data parallel training among different CNNs                                                    | 59 |

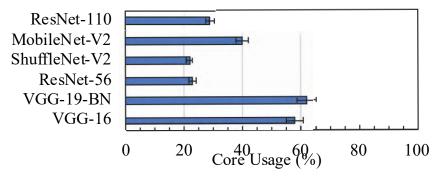

| 5.6  | Average utilization rate of computation core during data parallel training among different CNNs                                                    | 59 |

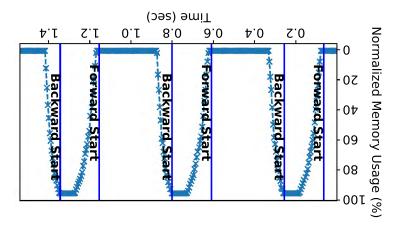

| 5.7  | GPU Memory spatiotemporal utilization pattern of BERT model training using 4 V100 with gang-scheduled model parallelism (w/o pipeline parallelism) | 61 |

| 5.8  | GPU Memory spatiotemporal utilization pattern of BERT model training using 4 V100 with gang-scheduled model parallelism (w/pipeline parallelism)   | 61 |

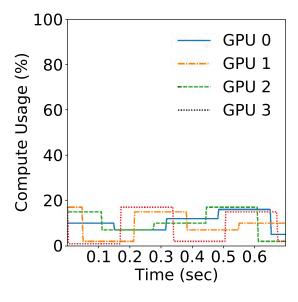

| 5.9  | GPU computation usage of BERT model training using 4 V100 with gang-scheduled model parallelism (w/o pipeline parallelism)                         | 62 |

| 5.10 | GPU computation usage of BERT model training using 4 V100 with gang-scheduled model parallelism (w/ pipeline parallelism)                          | 62 |

| 5.11 | Wavelet workflow overview                                                                                                                          | 63 |

|      | Data parallel training via gang scheduling                                                                                                         | 64 |

|      | Data parallel training via tick-tock scheduling                                                                                                    | 64 |

|      | Wavelet model synchronization between tick and tock waves on GPU-i during data parallel training                                                   | 66 |

| 5.15 | Model parallel training with Wavelet in 4-GPU setting                                                                                              | 68 |

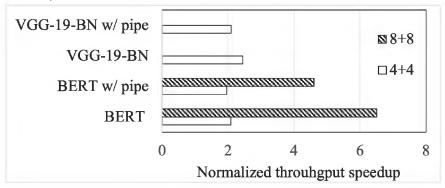

|      | Wavelet's throughput speedup over data parallel training baseline (single-machine multi-GPU)                                                       | 70 |

| 5.17 | Wavelet's throughput speedup over data parallel training baseline (multi-machine multi-GPU)                                                        | 70 |

| 5.18 | Wavelet's throughput speedup over model parallel training baseline (single-machine |    |

|------|------------------------------------------------------------------------------------|----|

|      | multi-GPU)                                                                         | 72 |

| 5.19 | Wavelet's throughput speedup over model parallel training baseline (multi-machine  |    |

|      | multi-GPU)                                                                         | 72 |

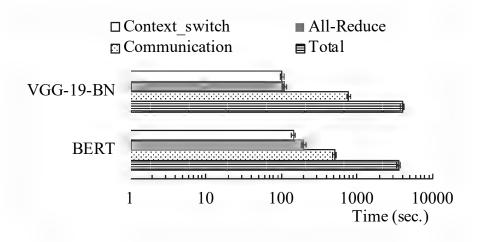

| 5.20 | Wavelet overhead breakdown in the 4+4 cross-machine case                           | 74 |

### List of Tables

| 4.1 | Comparison between baseline with model parallelism (MP) and sensAI using 10                                                                                                                                                 |        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|     | GPUs                                                                                                                                                                                                                        | 43     |

| 4.2 | Comparison between OVA and sensAI with 10 GPUs on CIFAR-10                                                                                                                                                                  | 44     |

| 4.3 | Comparison between efficient baseline models and sensAI                                                                                                                                                                     | $4\xi$ |

| 4.4 | Comparison between sensAI with two grouping methods (random and nearby grouping) with 5-group (5 GPUs) 10-group (10 GPUs) v.s. baselines of Single GPU and model parallelism (MP) using same amount of GPUs (5, 10 GPUs) on |        |

|     | CIFAR-100                                                                                                                                                                                                                   | 47     |

| 4.5 | Comparison between sensAI of 10-group (10 GPUs) and 20-group (20 GPUs) v.s.                                                                                                                                                 |        |

|     | baselines of Single GPU and model parallelism (MP) with 10 GPUs and 20 GPUs                                                                                                                                                 |        |

|     | on ImageNet-1K                                                                                                                                                                                                              | 40     |

#### Acknowledgments

First and foremost, I would like to express my gratitude and appreciation to my academic advisor Professor Ion Stoica. This dissertation would not be possible without the guidance and support from him. Ion was the primary reason I started my PhD at UC Berkeley. One big thing I learnt from Ion is to do fundamentally novel research, either finding new problems or proposing new solutions to old problems. These principles guide me through my whole PhD. For my first few years, even though I did not make good progress, Ion still believed in me. For example, he thought Blink was a good project even after it had been rejected for several years across multiple good venues. I want to thank Professor Joseph Gonzalez for insightful feedback and helping me connect with machine learning folks at Berkeley. I also want to thank Professor Dawn Song for offering me the chance to learn how an early-stage startup operates in the blockchain area. I am also thankful to my dissertation committee members Professor Alexandre Bayen, Professor Michael Mahoney, and my prelim committee Professor Scott Shenker. All of them are role models and I took much inspirations from their works in this dissertation.

I was fortunate to work with excellent mentors during my PhD. I would like to especially thank both Amar Phanishayee (MSR) and Shivaram Venkataraman (UW–Madison). Amar was my mentor during my internship at MSR, who leaded me into the research area of machine learning systems. Shivaram was a final-year PhD student in the AMPLab, who also joint our Blink project later on. Amar, Shivaram and I worked on Blink project for almost 3 years. I learnt a lot from both of them, such as how to set proper baby steps, how to write more readable code, how to make good presentations.

I am grateful to Zhuang Liu for helping me understand concepts and theories in computer vision models. I still miss the days when Zhuang, Brandon Hsieh and I sitting together to solve the problems we encountered in the sensAI project. I learnt a lot from Zhuang during our 2 years collaboration. For instance, anytime we got stuck at some point, he was the person to help us verify the theory and debug the code. We then become good friends. And now I am trying to convince Zhuang to move to Seattle for work, so that we can still meet in-person frequently.

I want to thank all my other collaborators and friends. I would like to thank Dequan Wang, Gur-Eyal Sela, Zhewei Yao, Fisher Yu (ETH) and Professor Kannan Ramchandran for helping us revise our previous paper drafts. I really enjoy having interesting discussions with Paras Jain, Fangyu Wu, Hong Zhang (UWaterloo), Siyuan Zhuang on various topics like deep learning, blockchain, robotic control, computer networks. For my prelim exam preparation, Chang Lan and Peter Xiang Gao helped me a lot. I also enjoy long-distance running with Haoran Tang, Renyuan Xu (USC) from Berkeley to Oakland during the weekends. I am particularly thankful to Wei Bai (MSR), Zhe Cao (Facebook), Wenyu Wang (UIUC), Keyu Wang (Google) for useful tips during my job hunting. I would like to also thank Kenan Jiang, Kehan Wang, Yaoqing Yang, Jichan Chung, Balaji Veeramani, Vipul Gupta, Adarsh Karnati, Zihao Fan, Praveen Batra, Hank O'Brien, Yingxin Kang, Sahil Rao, Aleksander Ficek, Xiangjun Li, Jorgen Thelin (MSR), Nikhil Devanur (Amazon) for contributing to

our code repositories. I also want to thank our administrative staff Kattt Atchley, Boban Zakovich, Shane Knapp, Jon Kuroda, Dave Schonenberg in the AMPLab/RISELab. I cannot list all the people who are important to me. But I would like to thank all the folks who spending time with me during my PhD.

Last but not least, I would like to thank my parents Ying Han and Xin Wang for their unconditional support and selfless love throughout my whole life.

### Chapter 1

### Introduction

#### 1.1 Motivation

Machine learning (ML) becomes one of the paramount technologies in recent decades [1]. Machine learning [2] and Artificial Intelligence (AI) [3] in general are regarded as major components for the fourth Industrial revolution in the human history [4].

To handle complicated tasks in computer vision [5][6][7], speech recognition [8][9] and robotic control [10], deep neural networks (DNNs) stands out and becomes the main force in machine learning area over the last decade. Influential models like AlexNet [5], BERT [8], AlphaGo [11] enable computers to excel over human in a broad spectrum of tasks like image classification, natural language processing and game playing.

To achieve better intelligence and higher model serving accuracy, both the input data size [12] and deep learning model size [13] are growing drastically. Taking computer vision area as an example, from CIFAR-10/100 [14] to ImageNet-1K [15] dataset, the number of images increase from 60k to over 1.2 million. In addition, the image resolution also grows a lot from CIFAR's 32x32 pixels to ImageNet's 256x256 pixels. On the model side, from GoogLeNet [16] to recent AmoebaNet series [17], the number of parameters almost increase 200 times. More astonishing numbers can be found in the Natural Language Processing (NLP) domain [18][19]. Taking transformer-based model GPT-3 [13] as an example, the number of parameters can be up to 175 billions. And the model is trained for around 300 billion tokens.

Given these giant models and enormous amount of input data, it is almost impossible to conduct model training or serving on a single accelerator. Thus, distributed model training and serving paradigms are widely adopted [20][21]. These distributed machine learning systems mainly focus on collectively using multiple accelerators (e.g., GPUs) to execute in-parallel model training and serving tasks [22][23]. System efficiency is a big issue when scaling out to tens, hundreds or even thousands of accelerators. More specifically, high communication overhead and limited on-device memory are two major causes of system inefficiency in large-scale machine learning systems.

In this thesis, we study possible ways to improve system efficiency in both communication and on-device memory aspects. We aim to mitigate network communication bottleneck and improve on-device memory usage for distributed machine learning workloads. We next summarize the goals and contributions of this dissertation.

### 1.2 Thesis Contributions

For distributed DNN training and serving, two main parallel paradigms are data parallelism and model parallelism. In data parallelism, each machine or accelerator holds a full copy of the model and conduct local training or serving on a dis-joint subset of the input data [24][25]. In model parallelism, each device only maintains one partition of the whole model and executes training or serving on the same shared input data [26][20][27].

Model synchronization is a major communication overhead in data and model parallel training. In data parallelism, since all the workers are trained on separate input data partitions, model synchronization is needed to synchronize model parameters among all the workers involved. In recent model parallel training system like Megatron-LM [28], synchronization using collectives (e.g., All-Reduce) is also required to aggregate partial matrix-multiplication results. Collective communication is the main-stream scheme for model synchronization in modern distributed machine learning frameworks [29][23][30]. Different companies provide their own collective communication libraries, such as NCCL [31] from Nvidia, Horovod [32] from Uber and Gloo [33] from Facebook. All of them focus on building rings in the given network topology to conduct collective communication. Our Blink project [34] adopts a different approach with topology-awareness. By packing maximum number of spanning trees in the topology, we achieve higher link utilization than ring-based schemes. Our Blink solution can also achieve near-optimal network throughput performance given arbitrary network topology and heterogeneity.

In model parallel training and serving, different workers also need to communication intermediate results like activations and gradients [20][35][36] in each iteration. To elimiate the communication among different nodes holding different model partitions, we propose sensAI project [37]. By applying a divide-and-conquer paradigm, we split a multi-task model into a bunch of disconnected subnets, where each is responsible for decision making of a single task.

Lots of DNN training and serving jobs are memory bounded [38][39]. To achieve higher accelerator utilization, previous literature propose to multiplex multiple jobs on each accelerator [38][40]. However, job-multiplexing on the same device introduces extra overheads, such as frequent context switching [41] or data loading from disk storage [42], inter-job interference [38], extra memory footprints for holding multiple models inside device memory [40]. More importantly, these job-multiplexing schemes cannot speed-up the training progress of a single job. Our Wavelet project [43] provides an generic and efficient way to improve accelerator utilization in the single job case. By intentionally adding task launching latency,

we interleave peak memory usage among different training waves of a single job. Thus we can improve both computation and on-device memory usage in the single job case.

In this thesis, we incorporate our previous research work in distributed machine learning systems, namely Blink [34], sensAI [37] and Wavelet [43]. For accelerators, we limit our discussion to Nvidia GPUs [44]. And our approaches should be generally applicable to other hardware accelerators like TPUs [45], FPGAs [46] and other ASIC chips [47][48].

Contributions: We summarize the main contributions of this thesis as follows:

- By packing spanning trees rather than forming rings, Blink achieve higher throughput than ring-based solutions given arbitrary network environments.

- To eliminate the communication in model parallelism, we propose sensAI as an divideand-conquer approach. By decoupling a multi-task model into multiple disconnected single-task subnets, we remove the communication among these subnets.

- By interleaving peak memory usage among multiple training waves of a single job, Wavelet improves accelerator utilization on both computation side and on-device memory side.

### 1.3 Thesis Organization

This thesis is organized as follows. Starting with Chapter 1, we discuss the motivation of this dissertation and our main contributions.

Chapter 2 provides more detailed explanations of deep learning models, distributed paradigms. We first describe training and serving stages of deep learning models. Then we discuss two main distributed methods as data parallelism and model parallelism.

Chapter 3 studies collective communication schemes, which is the modern model synchronization method for both data and model parallel training. The key issue of existing ring-based solution is some hardware links would be wasted if these links cannot form a new ring. We develop Blink [34] to tackle this issue. We abandon ring-based solution and use spanning trees to achieve higher flexibility and provide near-optimal performance given arbitrary network environments.

Following that Chapter 4 presents a new technique to decouple DNN model into disconnect subnets. Thus, we can eliminate communication in model parallel training and inference. Here we mainly explain our sensAI [37] approach in Convolution Neural Networks (CNNs) setting.

We next study how to improve GPU memory utilization in single DNN training job case as Chapter 5. We argue that gang scheduling policy [49][50][51] may under-utilize the limited on-device memory. In Wavelet project [43], we propose a novel yet simple scheduling policy called tick-tock. We profile and interleave peak memory usage among multiple training waves on the same group of GPUs. Thus, it can achieve near-optimal device memory usage and consequently increase the computation core usage.

Finally, Chapter 6 discusses future research directions for distributed machine learning systems. We then conclude this thesis with a summary of our main results.

### Chapter 2

### Background

### 2.1 Deep Learning Models

Deep learning becomes the hottest topic in machine learning research for the last decade. Deep learning models in computer vision, natural language processing and reinforcement learning enable machine to excel across a wide range of difficult tasks such as object detection [52][53], question answering [8][54] and robotic control [10][55].

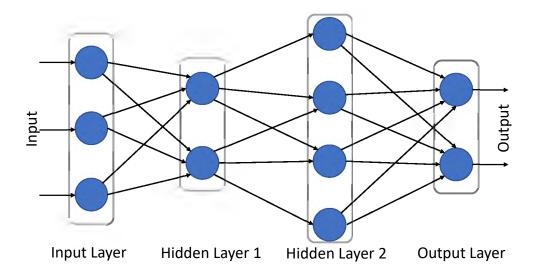

As shown in Figure 2.1, A normal DNN model consists of input layer, several hidden layers and an output layer. And each layer includes several neurons, where each neuron can often be regarded as a weight matrix. Communication is usually needed between adjacent layers of the model. And normally no communication is needed among neurons within each layer.

Figure 2.1: A toy example of normal deep learning model.

Figure 2.2: Forward propagation and backward propagation in DNN model training.

For instance, in CNN models, the model layers are mainly convolution layers [56] with Max-Pooling and ReLU (Rectified Linear Unit) layers in between [57]. And the models usually end with several fully-connected (FC) layers. To solve the internal covariate shift issue, modern ConvNets adopt Batch Normalization (BN) [58] to improve model serving accuracy. In deep Reinforcement Learning (RL) domain, deep RL models are mainly composed of fully-connected layers [10], but can also incorporate other layers like convolution layers [59], recurrent layers [60] and transformer layers [61][62].

Besides data pre-processing like tokenization [63] or image padding [57], deep learning models usually have two main stages, namely training and serving. We next explain each of them in Section 2.1.1 and Section 2.1.2 respectively.

### 2.1.1 Training

Given a specific model structure, the model parameters are initialized with random weights values. Then the training iterations start by consuming batches of input data and pass it into the model.

For a single batch of input, the training iteration mainly contains two steps: forward propagation and backward propagation [64].

As depicted in Figure 2.2, forward propagation [64] follows the blue arrows on the upper half of the figure. And backward propagation is shown as the grey arrows of the bottom half in Figure 2.2. Here L1, L2, L3, L4 refer to the DNN model layers from 1 to 4.

In forward propagation shown in Figure 2.2, given one training input batch, the data first go through L1. After L1 generates local activations, it passes its layer outputs to L2 and then triggers L2's forward propagation, and so on and so forth. After L4 finishes forward propagation, its output values  $\hat{y}$  go through the loss function module.

The goal of model training is to find proper weights and biases  $\theta$  given a loss function on the training data. If the model serving task is classification, cross entropy loss or negative log-likelihood is often used. Our training target is to minimize cross entropy loss function as:

$$\mathcal{L}(\theta) = -\sum_{i}^{n} y_{i} log(\hat{y}_{i})$$

(2.1)

As illustrated in Equation 2.1,  $y_i$  are the true labels whereas  $\hat{y}_i$  are the prediction probabilities.

For regression problems, mean square error (MSE) loss is commonly used. And our target is trying to minimize MSE loss function as:

$$\mathcal{L}(\theta) = \frac{1}{n} \sum_{i}^{n} (y_i - \hat{y}_i)^2 \tag{2.2}$$

Similar as Equation 2.1, in Equation 2.2,  $y_i$  are truly observed values whereas  $\hat{y}_i$  are predicted values.

After loss calculation, we can conduct backward propagation [64] in the reverse direction (i.e., grey arrows in Figure 2.2). The backward propagation starts from L4. After L4 generates its local gradients, it pass its gradient outputs back to L3, and so on and so forth. Then we can use gradients generated in each layer to update model weights in order to minimize our loss function.

For each batch of input, a training iteration is completed after one forward pass followed by one backward pass.

### 2.1.2 Serving

Compared with model training in Section 2.1.1, model serving stage is much simpler. Basically it only conducts the forward propagation shown in Figure 2.2 and generates prediction values for model serving.

Latency is the key performance indicator at the model serving stage [65][66][67][68]. Big tech companies try to reduce model serving latency by providing specific frameworks. For example, Google proposes TensorFlow Runtime [69] for low-latency model inference. Facebook/Meta's PyTorch incorporates ONNX runtime [70] to reduce model serving latency. Nvidia also provides TensorRT [71] SDK for accelerating model serving on the GPU hardware.

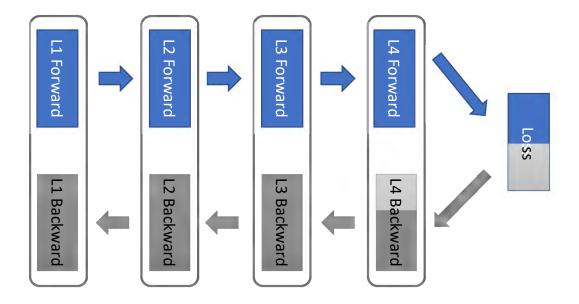

Figure 2.3: Data parallel training paradigm.

### 2.2 Data Parallelism

Above we describe basic concepts in deep learning models, such as model training and serving. Now we discuss two major distributed paradigms for deep learning models, namely data parallelism (Section 2.2) and model parallelism (Section 2.3). We explain data parallelism in this section.

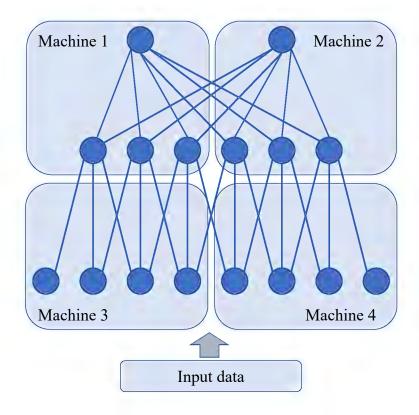

The data parallel training paradigm is depicted as Figure 2.3. In data parallelism, both machine 1 and machine 2 hold a full copy of the model parameters. In each iteration, they conduct local model training on separate input data, which is shown in Figure 2.3 as input data (partition 1) on machine 1 and input data (partition 2) on machine 2.

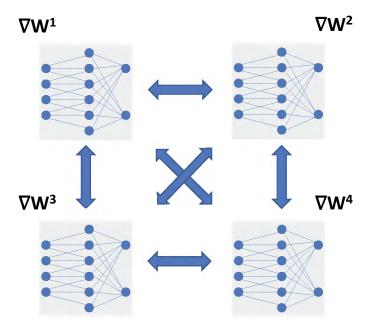

After each local training iteration finishes, all the GPUs involved in the same data parallel training job need to conduct model synchronization, which is denoted as the double-headed arrow in Figure 2.3. We illustrate model synchronization with a 4-GPU example, which is shown as Figure 2.4. In data parallel training, after each GPU generating its local gradients (i.e.,  $\nabla W^1$ ,  $\nabla W^2$ ,  $\nabla W^3$ ,  $\nabla W^4$  in Figure 2.4), it triggers model synchronization to aggregate all the local gradients together as:

Figure 2.4: Model synchronization in data parallel training.

$$\nabla W = \sum_{i=1}^{n} \nabla W^{i} \tag{2.3}$$

With the aggregated gradients as  $\nabla W$ , we broadcast this  $\nabla W$  to all the GPUs in use, and allow all the GPUs to update their local model parameters based on  $\nabla W$ .

Model synchronization is the main communication overhead in data parallel training [72]. There are mainly two schemes for model synchronization in data parallel training [73], namely Parameter Server (PS) [24][74][75][76] and Collective Communication [22][31][32][33]. Modern deep learning frameworks [23][29] adopt collective communication as the main scheme for model synchronization, due to its simplicity and scalability [77][78][34][79][80][81]. More specifically, collective communication treats all machines as workers uniformly whereas PS architecture needs to specify two different roles as parameter server and worker. In addition, PS also need to manually assign the ratio between parameter servers and workers among all the nodes involved. And there is no optimal solution on what ratio should be used given arbitrary number of nodes. Thus, in collective communication paradigm, it is much easier to insert or delete worker nodes than parameter server architecture.

Data parallel serving is simpler. Basically, each machine/GPU consumes separate input data partition and generates output predictions in-parallel. No communication is needed during data parallel inference.

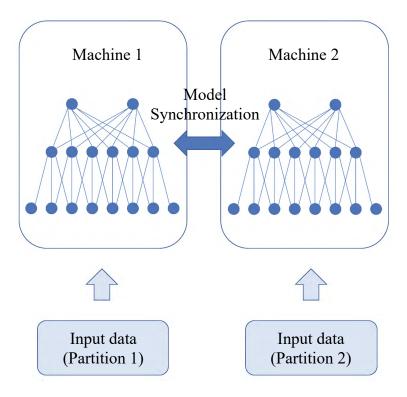

Figure 2.5: Model parallelism paradigm.

### 2.3 Model Parallelism

In this section, we discuss another distributed deep learning paradigm called model parallelism [82][83][84][28]. Different from data parallelism, in model parallelism, each machine or GPU only holds a portion of the full model parameters.

A 4-node model parallelism setting is shown as Figure 2.5. The model is split into 4 disjoint subsets and each machine holds roughly a quarter of the whole model parameters. As depict in Figure 2.5, all the machines share the same input data during both model training and serving stages.

However, during both model training and serving, they need to transfer lost of intermediate results among each other, which are highlighted as the bold lines across the model partition boarders in Figure 2.5. More specifically, during model parallel training, all the machines need to communication activations during forward propagation and gradients during backward propagation. In model parallel inference, all the machines communication activations in the forward pass only.

In addition, model parallelism naturally creates synchronization barriers due to the sequential dependency of DNN layers [85]. For example, in Figure 2.5, machine 1 and machine 2 cannot start forward propagation until completely receive all the intermediate results from

machine 3 and machine 4. Breaking each input batch in micro-batches and conducting data pipelining over micro-batches [35][36] can mitigate this sequential blocking issue.

### Chapter 3

### **Faster Collective Communication**

### 3.1 Background

As discussed in Section 2.2, collective communication is the main data transfer scheme used in data parallel training [21], which allows GPUs to frequently exchange and synchronize model parameters. It is also used in some modern model parallel training systems like Megatron-LM [28] from Nvidia.

To mitigate collective communication overhead, different companies provide their own solutions, such as Collective Communications Library (NCCL) [31] from Nvidia, Uber's Horovod [32], and Gloo [33] from Facebook/Meta. Incorporated with techniques like wait-free backward propagation that hides communication under computation [86], these collective communication libraries are specially designed to speed-up model synchronization.

### 3.1.1 Ring-based Collectives

State-of-the-art collective solutions like NCCL and Horovod focus on building rings within the network topology of a single job, and pipeline data transfer over rings they build.

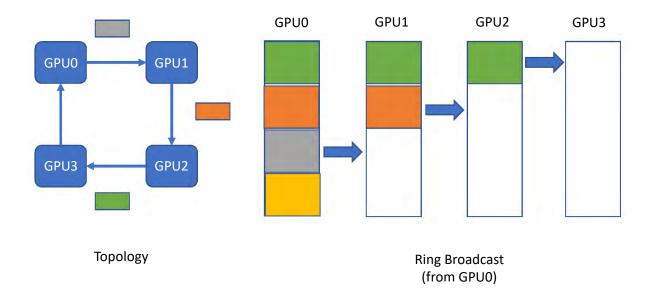

Figure 3.1 shows a toy example of ring-based broadcast in a 4-GPU setting. On the left side of Figure 3.1, it shows a formed ring within the topology. GPU0 want to broadcast its local data to GPU1, GPU2 and GPU3. Before data transfer, GPU0 first partition its local data into small chunks, which are shown as 4 chunks with different colors in Figure 3.1. Assuming the link is unidirectional, GPU0 can pipeline the data transfer over the ring in clockwise direction, which is shown as the right side of Figure 3.1. In reality, all links are bi-directional [87][88][89][90]. Besides this clockwise ring, GPU0 can easily create another ring in counter-clockwise direction using the same group of links in the topology but in the reverse direction.

Ring-based All-Reduce [91][92] follows similar protocol as Ring broadcast described above. The main difference from broadcast is that, current node need to aggregate local results with data received from predecessor before sending it to its successor.

Figure 3.1: Ring-based Broadcast from GPU0.

### 3.1.2 Topology Heterogeneity

We target on the state-of-the-art multi-GPU hardware with NVLink [88] and NVSwitch [90] like Nvidia's DGX-1 [93] and DGX-2 [94]. We find that, despite incorporate these advanced hardware (e.g., DGX-1 and DGX-2), modern collective communication libraries (e.g., NCCL) still cannot fully mitigate the communication bottleneck in data parallel training. The key issue is ring-based collectives under-utilize hardware links due to topology heterogeneity. We define topology heterogeneity in following three aspects:

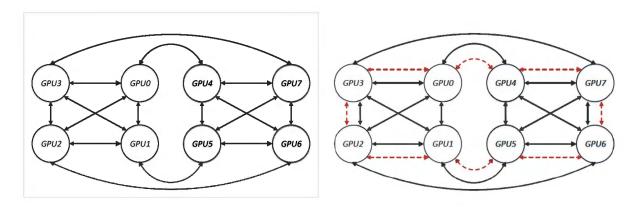

First, topology heterogeneity may occur because of different server configurations. As shown in Figure 3.2, for the same DGX-1 8-GPU box, it may have two different versions of network topology. If the DGX-1 server is embedded with P100 GPUs [95], the NVLink topology among GPUs is shown as the left side of Figure 3.2, which is called a hyper-cube topology. Each link here is the first generation NVLink, which provides around 18GB/s. If the DGX-1 box is incorporated with V100 GPUs [96], besides that hyper-cube topology in P100 version DGX-1, there is an additional ring added into the topology of DGX-1 V100 version, which is denoted as red dashed arrow-lines on right side of Figure 3.2. Therefore, in order to fully utilize all the hardware links effectively in different DGX-1 versions, the collective protocols need to be topology-aware.

Second, existing solutions cannot use heterogeneous links within the system. Servers like DGX-1 mainly have two different kinds of interconnects for intra-machine communication. First, it contains point-to-point interconnects called NVLink [88], which is shown as Figure 3.2. NVLink is GPU-exclusive communication links, where each provides 18-25GB/s bi-directional communication bandwidth. DGX-1 box has traditional PCIe bus, which is a

DGX1-P100 (NVLink 1st Gen, ~18GB/s)

DGX1-V100 (NVLink 2nd Gen, ~23GB/s)

Figure 3.2: NVLink topology of DGX-1 8-GPU server (left with P100 GPUs, right with V100 GPUs).

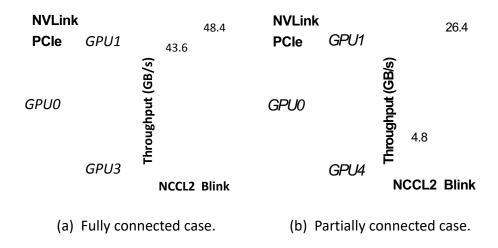

shared bus between host and devices. PCIe 3.0 [87] can reach peak throughput between 8 to 12 GB/s. PCIe bus connects multiple GPUs together via switch hierarchy within the same DGX-1 machine. Ring-based collectives such as NCCL and Horovord, they fail to use heterogeneous links. The key reason is that, the throughput of a ring is limited by the link with lowest bandwidth. For example, low bandwidth PCIe will be the communication bottleneck if it is included in a high bandwidth NVLink ring. Thus for intra-node communication, Ring-based solution like NCCL prioritizes NVLink over PCIe. Left side of Figure 3.3 shows a 3-GPU broadcast case from GPU0. Since all the GPUs are fully connected with NVLink, NCCL will build two unidirectional rings (one: GPU0->GPU1->GPU3->GPU0, the other: GPU0->GPU3->GPU3->GPU1->GPU0) over bi-directional NVLink, and abandons PCIe bus completely.

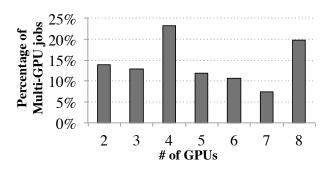

Third, in multi-tenant clusters, the job schedulers are often oblivious to hardware interconnect topologies among GPUs. And multiple jobs can be allocated within the same multi-GPU machine. In addition, topology-aware scheduler must also embrace fragmented allocation to avoid queuing delays [97][98][99]. A simple example of fragmented allocation can be: a 8-GPU job may be assigned with 3 GPUs on 1 machine, and 5 GPUs on another machine. We analyse over 40,000 multi-GPU jobs on a multi-tenant cluster in the cloud. As shown in Figure 3.4, even though ML practitioners always require GPUs in powers of two, it is fairly common that the number of GPUs assigned to jobs can be 3,5,6,7 within each 8-GPU server. Although by adopting scheduling method like Gandiva [38] that is topology-aware and job migration enabled, such schemes has a higher entry barrier since replacing all the independent scheduling frameworks is cumbersome and almost impossible. Furthermore, not every job can be placed and migrated properly given varied job arrival rates.

Ring-based collective protocols may under-utilize links given the above 3 challenges under

Figure 3.3: 3-GPU Broadcast from GPU0 using both Blink and NCCL on DGX-1-P100 server.

Figure 3.4: Number of GPUs placement for each job within each 8-GPU server on a cloud cluster allocated with 40,000 multi-GPU jobs.

the umbrella of topology heterogeneity. For instance, on right side of Figure 3.3, if a job is assigned with GPU0, GPU1 and GPU4, NVLink ring cannot be formed since there are only 2 NVlinks among these three GPUs (i.e., lack of NVLink between GPU1 and GPU4). In such a case, existing solution like NCCL will fall back to PCIe if it cannot form a NVLink ring.

### 3.2 Motivation

In this section, we first illustrate why ring-based solution may under-utilize hardware links with several case study. Then we highlight the benefits of packing spanning trees in the face of

Figure 3.5: Ring-based Broadcast from A (4-node fully connected).

Figure 3.6: Blink Broadcast from A (4-node fully connected).

topology heterogeneity. Last, we present our micro-benchmark results which characterizing the capabilities of modern GPUs (e.g., V100) that helps guide our Blink [34] design.

#### 3.2.1 Trees vs Rings

Our work is motivated by high communication overhead in data parallel training workloads on high-end multi-GPU machine like Nvidia's DGX-1 [93] and DGX-2 [94]. And this high communication overhead still exists even by setting the largest mini-batch size on each GPU and leveraging advanced collectives like NCCL with non-blocking layer-wise backward propagation [86] techniques. The communication overhead becomes more pronounced given increased model sizes and faster computation on newer GPUs like V100 [96], A100 [100] and H100 [101].

More crucially, even within a single DGX-1 machine, the communication overhead is amplified and becomes training bottleneck. The main reason is existing solutions like NCCL or Horovod fail to handle topology heterogeneity we defined in Section 3.1.2. These schemes first build rings given network topology and then pipeline data transfer over the rings. However, ring-based solution have several major structural limitations. First, for each ring, each node can only maintain one input degree and one output degree. This strong structural restriction makes it impossible for ring-based solution to fit into arbitrary and irregular network topologies. Thus it leads to link under-utilization. Second, in order to create a ring, number of links needed is equivalent to the number of GPUs (i.e., N) involved in the same training job. However, the minimum number of links to connect N GPUs is actually N-1 links.

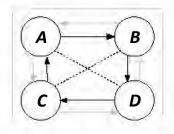

Besides the example shown on the right side of Figure 3.3, we provide more toy examples of how rings' structural constrains cause link under-utilization. Figure 3.5 shows a 4-node broadcast setting where node-A broadcast its data to all the other three nodes. These four nodes are fully connected, which is equivalent to left or right four GPUs in Figure 3.2 with P100 setting. Since links are usually bi-directional, node-A forms two rings: one in clockwise direction (i.e.,  $A \rightarrow B \rightarrow D \rightarrow C \rightarrow A$ ), the other in counter-clockwise direction (i.e.,  $A \rightarrow C \rightarrow D \rightarrow B \rightarrow A$ ). Since there are two concurrent data transfer channels, node-A can split its local data into half and half, then pass first half of data through one ring and the second

Figure 3.7: 6-GPU topology on DGX-1-P100. Figure 3.8: NCCL 6-GPU Rings (Broadcast from GPU3).

Figure 3.9: Blink 6-GPU spanning trees (Broadcast from GPU3).

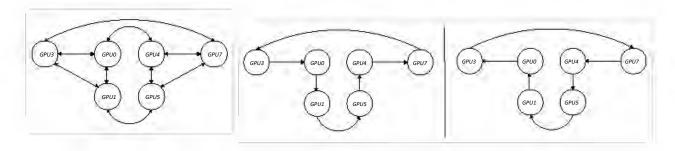

half through the other ring. However, the two links in the center are never used during this broadcast process, which are denoted as dashed lines in Figure 3.5. Another more complicated example can be found as Figure 3.8. Figure 3.7 shows the NVLink topology among 6 GPUs inside a DGX-1-P100 machine (i.e., left of Figure 3.2). Here GPU3 initialize broadcast to all the other 5 GPUs. As shown in Figure 3.8, ring-based solution like NCCL also forms two rings, one in clockwise direction and the other in counter-clockwise direction. However, the links between GPU1 <->GPU3, GPU5 <->GPU7, GPU0 <->GPU4 are never used in the 6-GPU broadcast case.

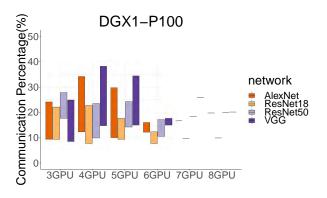

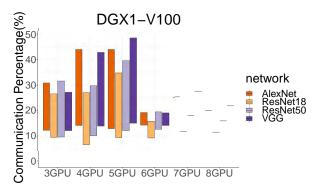

Figure 3.10 and Figure 3.11 show detailed measurements of communication overhead as percentage of end-to-end per-iteration training time. We study over four popular ConvNets as AlexNet [5], VGG [102] and ResNet [6] using NCCL as the communication backend on single DGX-1 machine with P100 GPUs and V100 GPUs. Since a fixed number of GPUs may form different NVLink topology, we measure the best-worst case as a range for each particular number of GPUs in use. As shown in Figure 3.11, the communication overhead from NCCL can be up to 50% of the end-to-end DNN training time on a DGX-1-V100 machine.

In contrast, by modeling hardware links as edges of a graph, classic graph theories [103][104] suggest that, packing spanning trees could lead to maximum network flow from a root node to all other nodes in a directed graph. Therefore, one-to-many and many-to-one primitives such as broadcast and reduce can be directly applied over these uni-directional spanning trees. Furthermore, AllReduce can be split into reduce in one direction then broadcast in

Figure 3.10: Best-worst case of communication percentage regarding to end-to-end DNN training iteration time (DGX-1-P100).

Figure 3.11: Best-worst case of communication percentage regarding to end-to-end DNN training iteration time (DGX-1-V100).

the reverse direction among the spanning trees we have.

By packing spanning trees rather than forming rings, we can achieve optimal link utilization. The advantage of trees over rings are shown in examples of Figure 3.3, Figure 3.6 and Figure 3.9. On the right of Figure 3.3, since spanning trees can be formed with just 2 NVLinks in this setting, our spanning tree solution (i.e., Blink) can leverage the high-bandwidth NVLink for broadcast in this partially connected 3-GPU case. In Figure 3.6, we can pack 3 uni-directional spanning trees from node-A, which utilize all the links available in this 4-GPU setting. In Figure 3.9, we can pack 3 spanning trees with root of GPU3 and use up all the links available in this 6-GPU irregular topology.

With spanning tree paradigm, each GPU could have various degrees of inputs and outputs. Next, we want to evaluate how close to line-rate that GPUs perform using multiple trees not rings.

#### 3.2.2 Micro-benchmarks

In this section, we measure the network throughput among our cases of having computation inline with communication over spanning trees. We present our results on DGX-1-V100 machines. We also conducted measurements over DGX-1-P100 machines, which show similar results. For the sake of brevity, we exclude those results in this thesis. We categorize our measurements into following three settings.

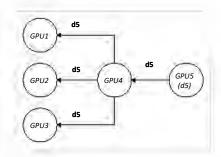

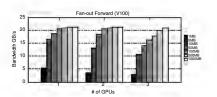

Breadth Test: First, we test fan-in, fan-out data transfer together with inline reduce operations. As shown in Figure 3.12, for fain-in forward case, a central node (i.e., GPU4) collects three input data streams from GPU1,2,3 then forwards towards GPU5. For fan-in reduce and forward defined as Figure 3.13, the central node (i.e., GPU4) aggregates incoming data with its local data by computing a reduction, and then forward aggregated results to its successor (i.e., GPU5). Our fan-out forward defined in Figure 3.14 is the reverse data

Figure 3.12: Breadth Test: Fan-in forward.

Figure 3.13: Breadth Test: Fan-in reduce and forward.

Figure 3.14: Breadth Test: Fan-out forward.

Figure 3.15: Breadth Test Throughput: Fan-in forward.

Figure 3.16: Breadth Test Throughput: Fan-in reduce and forward.

Figure 3.17: Breadth Test Throughput: Fan-out forward.

forward of our fan-in forward. Basically, GPU4 broadcasts GPU5's data to GPU1,2,3.

We test network throughput over above three breadth test cases by transferring data size ranging from 1MB to 1000MB. The corresponding results are shown as Figure 3.16, Figure 3.16 and Figure 3.17 respectively. In summary, with data size equal or larger than 50MB, all of these three breadth test can achieve near maximum network throughput. Compared with fan-in forward, fan-in reduce and forward has 1-2 GB/s lower throughput, which is mainly due to reduction computation latency. Fan-out forward has similar network throughput as fan-in forward, which is close to the line-rate of NVLink.

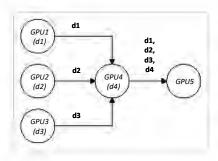

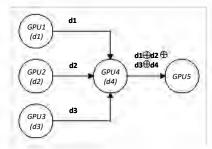

Depth Test: Next, we conduct our micro-benchmark of depth test, which creates chains for data forwarding and reduction. Here we mainly measure three kinds of chain traffic: forward (Figure 3.18), reduce and forward (Figure 3.19), then reduce and broadcast (Figure 3.20). For chain forward in Figure 3.18, GPU1 is the source with data d1. GPU2 and GPU3 forward the data to GPU4 in the end. For chain reduce and forward in Figure 3.19, for forwarding nodes like GPU2 and GPU3, they aggregates local data with data received from predecessor, and then forward aggregated results to their successors. For chain reduce and broadcast in Figure 3.20, all the nodes execute reduce and forward operation from left to right, then broadcast the final results from right to left.

We also test above three depth test cases with various data size ranging from 1 MB to 1000 MB. The length of chain we tested is ranging from 3-GPU to 8-GPU within an DGX-1-V100 server. For chain forward only results in Figure 3.21, with data size over 500

Figure 3.24: Multi-Input, Figure 3.25: Multi-chain ag- Figure 3.26: MIMO and MCA Multi-Output (MIMO). gregation (MCA). throughput.

MB, the throughput decreases from 22 GB/s in 3GPU case to around 20 GB/s in 8-GPU case. This pattern is less noticeable in the case of reduce and forward in Figure 3.22. For ore than 500 MB data, the average throughput in chain reduce and forward is around 18 GB/s in Figure 3.22. For chain reduce and broadcast shown as Figure 3.23, with more than 500 MB data, the throughput decreases from around 19 GB/s to around 16 GB/s when we increase the length of the chain from 3 to 8 GPUs. Overall, we see the throughput drops with smaller data sizes. The main reason are twofold. First, it is difficult to fully saturate high bandwidth links with small data sizes. Second, there are constant control overheads for launching CUDA [105] kernels.

Multi-transfer Test: Now we consider the case of concurrent data flow in any given network topology. We mainly test two cases: multiple-input-multiple-output (MIMO) in Figure 3.24 and multiple-chain aggregation (MCA) in Figure 3.25.

In our MIMO configuration in Figure 3.24, GPU1 and GPU2 send their local data (d1, d2) to the center node GPU3. Then GPU3 aggregates its local data d3 and d3' with d1 and

Figure 3.27: Blink workflow.

d2 separately. GPU3 sends d1+d3 to GPU4 and sends d2+d3' to GPU5 simultaneously. In our MCA setting, basically it merges two reduce-and-forward chains together. In the upper chain, GPU2 aggregates local data with GPU1's, then forwards aggregated results to GPU5. GPU4 reduce local data with GPU3's, then forward reduction values to GPU5. GPU5 aggregates both chains' input with its own local data.

The throughput result of MIMO and MCA is shown as Figure 3.26. For smaller data size like 10 MB, both MIMO and MCA can only achieve throughput around 15 GB/s, which is mainly due to the small data chunk cannot fully saturate the NVLink bandwidth. For data size in the range of 100 MB or 1000 MB, both MIMO and MCA can achieve around 18 GB/s throughput.

**Summary:** From all the micro-benchmark results above, we see that modern GPUs like V100 with NVLink interconnects could provide good support for data transfer over spanning trees with various depth and width. We also see the throughput drops a little when incorporating computation kernels like reduction with communication. In summary, these micro-benchmarks make it promising and possible for using spanning trees to implement collective communications such as broadcast and allreduce.

## 3.3 Blink Design

In this section, first we provide a brief system workflow of our Blink project. We describe Blink design and our techniques to handle heterogeneous links while achieve high link utilization. Second, we illustrate how we use uni-directional spanning trees for one-to-many and many-to-one primitives such as reduce and broadcast. Third, we also extend it into many-to-many primitives such as allreduce by leveraging the bi-directional hardware interconnects. Fourth, we provide solutions to use PCIe and NVLink together for collective communication. Last, we extend our method to DGX-2 [94] and multi-GPU multi-machine cases.

### 3.3.1 System Overview

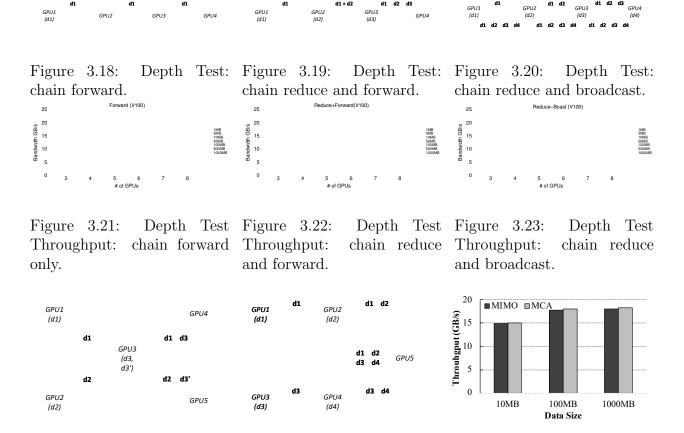

We provide the overview of Blink project in this section. Blink is a fast and generic collective communication library. The workflow of Blink is shown as Figure 3.27.

Given arbitrary network topology, Blink dynamically generates the optimal collective communication scheme by packing maximum number of non-conflicting spanning trees in the topology. Now we decribe the major components and workflow of Blink project in Figure 3.27. The workflow of Blink is composed of the followings:

- At job runtime, after the scheduler assigns a set of GPUs to the DNN training job, Blink probes the network topology and available links among these assigned GPUs.

- Once Blink collects the network topology information, we pass this topology information into our TreeGen module. Our TreeGen computes the maximum fractional packing of spanning trees in the given topology. We use these spanning trees for the implementation of our collective communication protocol.

- We then pass the spanning trees from TreeGen to our CodeGen, which generates the code for data transfer commands over these spanning trees. The code generated provides same API as NCCL, and is packed as a shared library (i.e., libBlink.so in Figure 3.27).

- Last, we use LD\_PRELOAD flag to dynamically load our Blink implementation to replace the NCCL counterpart (i.e., libNCCL.so in Figure 3.27) when the main program is invoked.

We next illustrate each module in Figure 3.27 in the following sections.

## 3.3.2 Packing Spanning Trees

We first consider one-to-many primitives such as broadcast using uni-directional spanning trees. We model the network topology information as follows. We treat each GPU as a vertex V and each hardware link as a directed edge E. Each directed edge is assigned with a bandwidth value which is proportional to its link capacity. Thus, these vertices and edges creates a directional graph.

With the above graph model, the optimal throughput for broadcast is to find the maximum weights of flows that start from a given root node and reach all other vertices in the graph. This problem is well-studied in classic graph theory [104]. Basically, the objective function is to find the maximal packing of uni-directional spanning trees or arborescences in a directed graph [103]. Thus, we formalize our optimization problem as follows:

$$\max \sum_{i} w_i \tag{3.1}$$

such that

$$\forall e \in E, \sum_{i} \kappa_i * w_i < c_e$$

(3.2)

where

$$\kappa_i = \begin{cases} 1, & \text{if } e \in T_i \\ 0, & \text{otherwise} \end{cases}$$

(3.3)

Formally speaking, our objective is that, given a directed graph G with edges E, root vertex r, vertices V and set of spanning trees T, we want to find the weights  $w_i$  so that the sum of  $w_i$  trees passing through edges in E will not exceed the capacity of any edges.

However, the search space of above formalized problem too large. For example, in a complete graph, the number of arborescences can be at the exponential scale as  $\mathcal{O}(n^{n-2})$ . Therefore, the runtime for problem solving can be insanely long. Some exact and more computational efficient algorithm has been proposed recently, which reduces the computational complexity to  $O(n^3 m \log(n^2/m))$  with m edges and n vertices [106]. However, we still abandon this exact and slightly efficient solution due to its high computational complexity. We adopt an approximate algorithm in the next section.

## 3.3.3 Approximate Tree-Packing

We adopt an approximation technique called multiplicative weight update (MWU), which is usually used in optimization in game theory. Our use of MWU follows a recent work to achieve near-linear time approximation in fractional packing problems [107]. For instance, it can solve spanning tree packing problem in  $O(m \ln m/\epsilon^2)$  where m is number of edges in the graph.

This MWU-based approach for packing spanning trees works as follows: we initialize each edge in E with capacity value and another weight indicating how much the capacity of each edge has been used. Given this setting, we can use iterative method such that, during each iteration, we find the minimum weight spanning tree in current assignment. We increase the weight by a factor of  $\epsilon$  and then update the whole graph accordingly. Therefore, this algorithm can be converged after  $O(\ln m/\epsilon^2)$  iterations. Upon the convergence, we can get a set of spanning trees  $\{T_i, i \in \mathbb{N}\}$  and corresponding weights  $\{w_i, i \in \mathbb{N}\}$ . The total bandwidth B for broadcast is as the sum of weights as follows:

$$B = \sum_{i \in \mathbb{N}} w_i \tag{3.4}$$

However, this MWU-based algorithm [107] has no bound on the number of spanning trees it generates. After solving this MWU optimization problem, we find that the number of arborescences generated can be too large. For example, the number of arborescences

generated is 181 within an 8-GPU server. Thus, it is impossible to use so many spanning trees together for concurrent data transfer. It is because the data size per each tree will be too small to fully saturate the link bandwidth.

To minimize the number of spanning trees being generated, we formulate an integer linear program (ILP). Here we limit the weights  $w_i$  can only be 0 or 1. Thus, the whole problem can be formalize as below:

$$\max \sum_{i=1}^{k} w_i \tag{3.5}$$

such that

$$\forall e \in E, \sum_{i} \kappa_i * w_i < c_e$$

(3.6)

$$\forall w_i \in \{0, 1\} \tag{3.7}$$

where

$$\kappa_i = \begin{cases} 1, & \text{if } e \in T_i \\ 0, & \text{otherwise} \end{cases}$$

(3.8)

Here k can be controlled by the number of arborescences generated from previous MWU procedure. Solving this ILP will generate  $\hat{c}$ , which may be lower than theoretical optimal as  $c^*$ . We then iteratively relax constrains until the difference between  $\hat{c}$  and  $c^*$  is under some threshold (e.g., 3%). With this integer approximation, we can reduce the number of trees from 181 to 6 in an 8-GPU DGX-1 server. With total data size as 1000 MB, now each tree is responsible for transferring around 166 MB data which could fully saturate link bandwidth.

## 3.3.4 Extending to Many-to-many Collectives

Above we discuss one-to-many or many-to-one collective primitives such as Broadcast, Gather, Reduce. In this section, we further extend it to many-to-many primitives such as AllGather and AllReduce.

We exploit the fact that all the modern hardware links are bi-directional. Thus, for each uni-directional spanning tree we have, we can run many-to-one primitive in one direction and run one-to-many primitive in the reverse direction. Taking AllReduce as an example, in Figure 3.20, we pick the root node as GPU4 on the right. For AllReduce in this 4-GPU setting, we reduce from left to right, then broadcast from right left. Thus it finishes the AllReduce operation.

This stratgy of combing two unidirectional spanning trees also guarantee we match the lower bound of number of messages passing for many-to-many primitives (e.g., AllReduce). For example, in AllReduce operation, our solution achieves the lower bound of  $2 \times \lceil \frac{N-1}{N} \rceil$  as shown in previous literature [108].

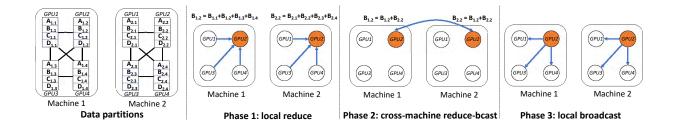

Figure 3.28: Blink's Three-phase AllReduce protocol for cross-machine settings.

## 3.3.5 Hybrid Communication

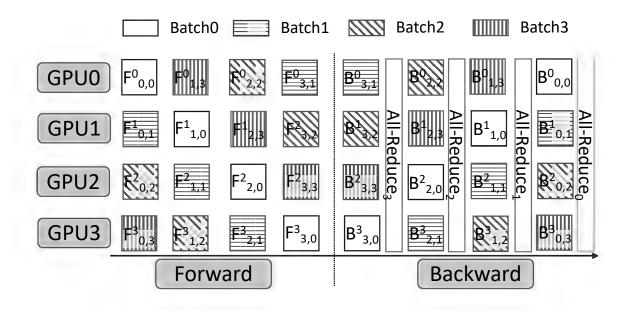

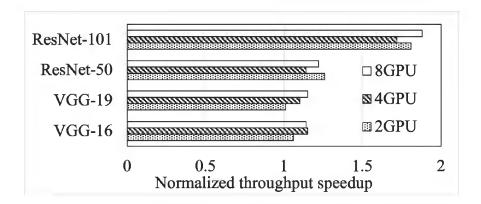

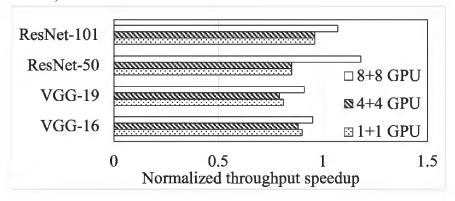

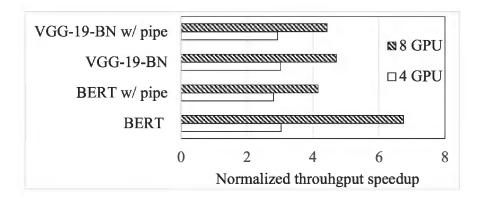

We provide concurrent data transfer over both PCIe and NVLink for intra-machine collective communication. The first challenge we faced is, there is no official way to switch between NVLink and PCIe for communication. In our experience, we find by using cudaDeviceDisablePeerAccess(), it can force data transfer on PCIe and disable NVLink communication.