# Modeling and Design of Nanoscale Ferroelectric and Negative-Capacitance Gate Transistors

Yu-Hung Liao Sayeef Salahuddin, Ed. Chenming Hu, Ed. Jungiao Wu, Ed.

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2022-32 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2022/EECS-2022-32.html

May 1, 2022

Copyright © 2022, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Modeling and Design of Nanoscale Ferroelectric and Negative-Capacitance Gate Transistors

by

#### Yu-Hung Liao

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Sayeef Salahuddin, Chair Professor Chenming Hu Professor Junqiao Wu

Fall 2021

Modeling and Design of Nanoscale Ferroelectric and Negative-Capacitance Gate Transistors

Copyright 2021 by Yu-Hung Liao

#### Abstract

Modeling and Design of Nanoscale Ferroelectric and Negative-Capacitance Gate Transistors

by

#### Yu-Hung Liao

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Sayeef Salahuddin, Chair

Integration of Hf-based ferroelectric materials into the MOSFET gate stack introduces new physics that potentially enables continued scaling for both CMOS and memory devices. The electrostatic potential amplification effect arises when the device is engineered to depolarize and hence stabilize the ferroelectric negative capacitance state, which eliminates the ferroelectric hysteresis and enhances the gate control. On the other hand, when the ferroelectric layer is thick enough to overcome the depolarization field, non-volatile memory function can be realized through the remnant polarization states. Such systems exhibit process and structural compatibility with CMOS technology and thus are of significant application relevance. Experiments have demonstrated low-voltage operations for both types of devices, showing promising prospects for next-generation logic devices with high reliability.

To harness the effects for designing the NCFET and FeFET devices, it is important to understand the behaviours of the ferroelectric layer in the relevant states. In this dissertation, the polarization responses of negative capacitance states are modeled from different aspects through self-consistent device and circuit models that are calibrated to experimental measurements. First, the 101-stage ring oscillator consisting of 14 nm FinFET devices with a ferroelectric gate layer that exhibits negative capacitance are used to study the response speed of the negative capacitance effect. The consistency of the device DC characteristics and the circuit oscillations with less than 10ps per-stage delay confirm the fast negative capacitance response. Next, NCFET device characteristics and scaling trends that are unexpected by conventional theory were explained with non-linear negative capacitance responses as described by the Landau's phenomenology. Design insights are drawn, and the observation bodes well for extending the MOSFET gate length scaling limit. Finally, high-speed NCFET RF operations are projected and designed based on experimental characterization results and Monte-Carlo transport simulations. Silicon-channel NCFETs are expected to achieve cutoff frequency over 400GHz with standard SOI device structures and over 650GHz with air-gap spacers.

The carrier dynamics of memory program and readout operations for an n-type SOI FeFET are studied through TCAD simulations. Gate-induced drain leakages during the program operation with large negative gate biases can result in excessive hole concentrations with lifetime exceeding microseconds during the hold phase. While the excess holes result in approximately 100ps delay in the readout phase before a large read margin can be detected, it benefits the program speed and the quasi-steady-state read margin. Therefore, such effects can be utilized for low-power memory applications through proper SOI FeFET designs with the awareness of excess carrier dynamics.

To my family.

# Contents

| $\mathbf{C}_{\mathbf{c}}$ | ontents                                |                                                                             | ii                               |

|---------------------------|----------------------------------------|-----------------------------------------------------------------------------|----------------------------------|

| Li                        | $\operatorname{st}$ of                 | Figures                                                                     | iv                               |

| $\mathbf{Li}$             | $\operatorname{st}$ of                 | Tables                                                                      | xi                               |

| 1                         | Intr<br>1.1<br>1.2<br>1.3<br>1.4       | Needs For Electrical Scaling of CMOS Gate Stack                             | 1<br>3<br>11<br>13               |

| 2                         | Res<br>2.1<br>2.2<br>2.3<br>2.4        | Introduction                                                                | 14<br>14<br>15<br>18<br>23       |

| 3                         | Mod 3.1 3.2 3.3 3.4 3.5                | deling of the Anomalously Beneficial Gate-Length Scaling Trend Introduction | 24<br>24<br>24<br>26<br>29<br>33 |

| 4                         | Mod<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | deling of the Near-Threshold Swing Reduction Effect Introduction            | 34<br>34<br>35<br>39<br>42<br>46 |

| 5                         | Per                                    | formance Modeling of Quasi-Ballistic NCFET                                  | 47                               |

|    | 5.1   | Introduction                                                     | 47 |

|----|-------|------------------------------------------------------------------|----|

|    | 5.2   | Device Structure                                                 | 48 |

|    | 5.3   | Modeling Methodology                                             | 50 |

|    | 5.4   | Results                                                          | 55 |

|    | 5.5   | Conclusion                                                       | 68 |

| 6  | Dyn   | namical Effect of Excess Carriers On SOI FeFET Memory Operations | 69 |

|    | 6.1   | Introduction                                                     | 69 |

|    | 6.2   | FeFET Design and Simulation Model                                | 70 |

|    | 6.3   | Results and Observations                                         | 71 |

|    | 6.4   | Design Perspectives                                              | 78 |

|    | 6.5   | Conclusion                                                       | 81 |

| 7  | Con   | clusions                                                         | 82 |

|    | 7.1   | Chapters Summary                                                 | 82 |

|    | 7.2   | Future Works                                                     | 84 |

| Bi | bliog | graphy                                                           | 86 |

# List of Figures

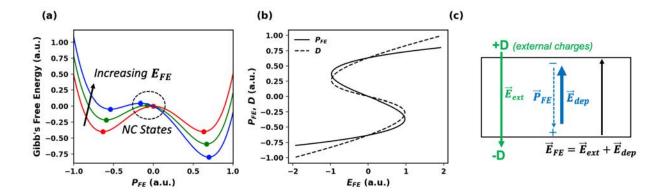

| 1.1 | Schematic (a) $\mathcal{G}_{FE} - P_{FE}$ relationships at different $E_{FE}$ . Possible steady states are marked. For the NC states, $P_{FE}$ decreases as $E_{FE}$ increases in contrast to classical trend. However, they are not stable in a bulk system because they correspond to local maxima of $\mathcal{G}_{FE}$ . (b) $E_{FE} - P_{FE}$ (solid) and $D - P_{FE}$ (dashed) relationships. Both have negative slopes for small $ P_{FE} $ , corresponding to the NC state. (c) Illustration of different fields for an NC state. $P_{FE}$ responds in the same direction as $E_{ext}$ . However, the depolarization field generated by $P_{FE}$ ( $E_{dep} = -P_{FE}/\epsilon_b$ ) is |          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2 | stronger than $E_{ext}$ , reversing the direction of the net electric field $E_{FE}$ (a) Illustration of the fields in the FE-DE stack with applied voltage when FE is in the NC state. The displacement $D$ is continuous throughout the layers, which                                                                                                                                                                                                                                                                                                                                                                                                                                        | <u> </u> |

|     | connects $E_S$ and $E_{FE}$ to V and $P_{FE}$ . (b)(c) The energy landscapes of a FE-DE stack system under different applied voltages. The system satisfies condition 1.20, so $G$ is stabilized at the low- $P_{FE}$ state, and the hysteresis is eliminated. The                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|     | overall capacitance of the system is positive, so as V increases, Q and D increases, which drives $P_{FE}$ in the same direction, while $E_{FE}$ moves in the opposite direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|     | due to the NC effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5        |

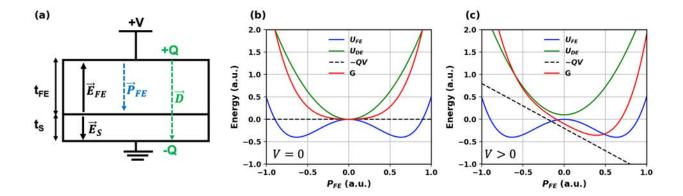

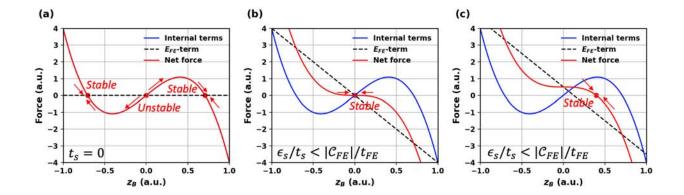

| 1.3 | Relationship between the cation displacement and the forces on the cation atom. The net force is decomposed into internal terms that are unrelated to the applied field and the $E_{FE}$ term. (a) is without a DE layer and V=0, so $E_{FE} = 0$ regardless                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|     | of $z_B$ and $P_{FE}$ . The internal terms make the NC state unstable, while only the remnant polarization states are stable. (b) and (c) are with a DE layer that is thick enough to stabilize the NC state which becomes the only steady state.                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|     | The FE polarization induces a depolarization field that restores the cation from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|     | fluctuations. When the voltage bias is changed from (b) to (c), the dashed curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|     | shifts vertically, which results in a new steady state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8        |

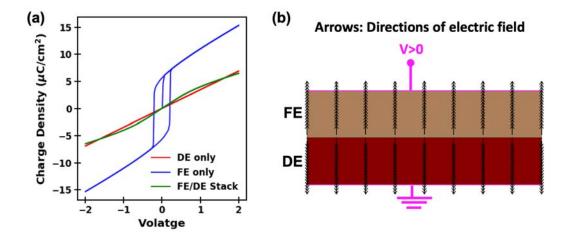

| 1.4 | (a) Simulated Q-V results for a DE capacitor, an FE capacitor, and a stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|     | structure combining both. LK model is used to simulate the $P_{FE}$ responses. (b) A snapshot of the electric field profile for the FE-DE stack structure in NC state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10       |

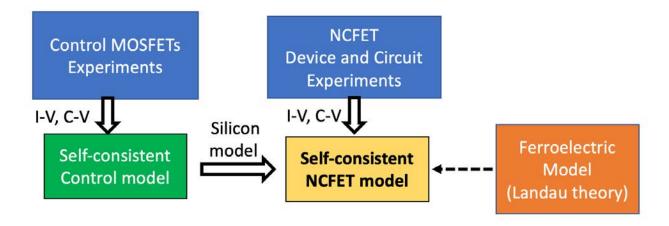

| 1.5 | NCFET modeling methodology flow with controlled experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13       |

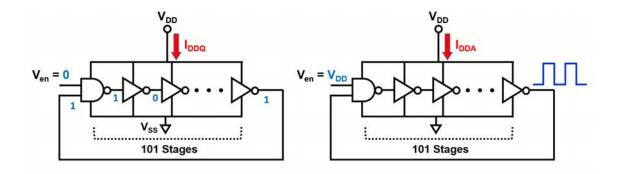

| 2.1 | Schematics of the 101-stage ring oscillator when it is disabled (left) for IDDQ measurements and when it is enabled (right) for IDDA and delay measurements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|     | Fan-out loads are not shown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16       |

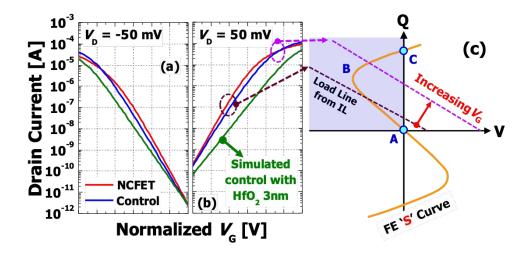

| 2.2 | (a) $V_{th}$ -matched $I_D$ - $V_G$ characteristic of Control MOSFET and NCFET. For com-                                                                         |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | parison, simulated characteristics of devices with 3 nm DE is included. (b) A                                                                                    |    |

|     | schematic 'S' curve of the ferroelectric showing the region of operation                                                                                         | 18 |

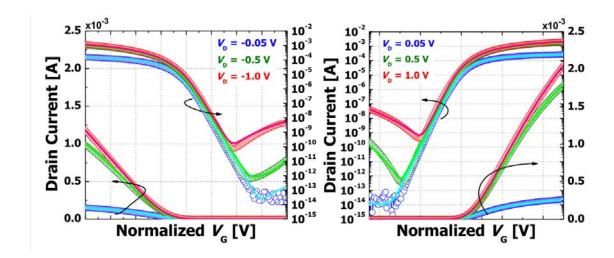

| 2.3 | Measured and modeled $I_D$ - $V_G$ for (left) an n-type NCFET and for (right) a p-                                                                               |    |

|     | type NCFET. Both semi-log scale and linear scale current are plotted. Dotted                                                                                     |    |

|     | and solid lines represent measurements and modeling, respectively                                                                                                | 19 |

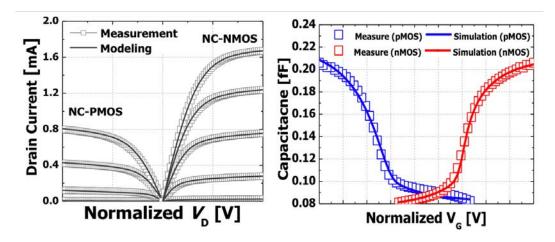

| 2.4 | Measured and modeled (left) $I_D$ - $V_D$ at various $V_{GS}$ and (right) $C$ - $V$ at $V_{DS} = 0V$                                                             |    |

|     | for both the NC-NFET and NC-PFET                                                                                                                                 | 19 |

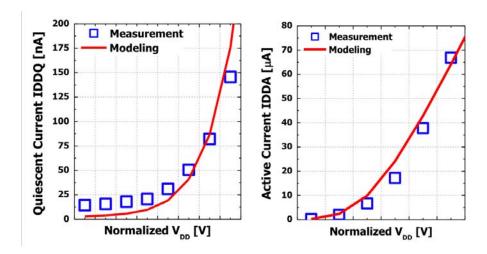

| 2.5 | Simulated and measured (a) IDDQ and (b) IDDA on the 101 stage FO3 RO. The                                                                                        |    |

|     | simulation was performed with quasistatic models calibrated to the DC measure-                                                                                   |    |

|     | ments                                                                                                                                                            | 20 |

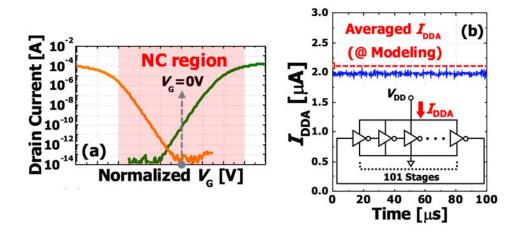

| 2.6 | (a) Operation range corresponding to a $V_{DD}$ where the PFET remains in NC                                                                                     |    |

|     | regime. (b) Simulated and measured IDDA at the $V_{DD}$ indicated in (a)                                                                                         | 21 |

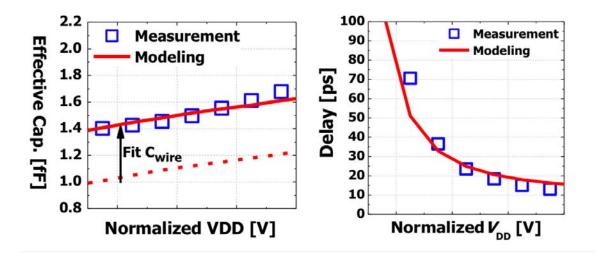

| 2.7 | The simulated and measured (left) $C_{eff}$ and (right) gate stage delay $\tau$ for the                                                                          |    |

|     | FO3 NCFET RO. (Left) The dashed line is simulated without wire load, and the                                                                                     |    |

|     | solid line is simulated with 0.4fF wire load. (Right) The delay is reproduced by                                                                                 |    |

|     | the model with 0.4fF wire load.                                                                                                                                  | 22 |

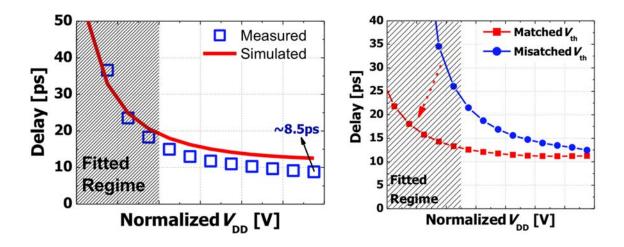

| 2.8 | (Left) Simulated and measured gate stage delay. The shaded area stands for                                                                                       |    |

|     | the $V_{DD}$ range under which the device model is calibrated to DC measurements.                                                                                |    |

|     | (Right) Simulated gate stage delay and the projection with matched $V_{th}$ . The                                                                                |    |

|     | shaded area stands for the trustworthy regime for matched- $V_{th}$ simulations                                                                                  | 22 |

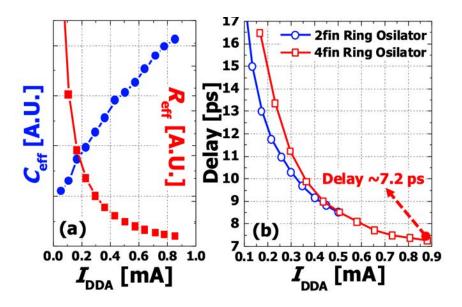

| 2.9 | (a) Measured $C_{eff}$ and $R_{eff}$ from 4-fin NCFET ring oscillator. Behavior of $C_{eff}$                                                                     |    |

|     | and $R_{eff}$ follow expected trends. (b) Delay vs. IDDA curves for 2 fin and 4 fin                                                                              |    |

|     | NC-FinFET ring oscillators. Stage delay as small as 7.2 ps was measured                                                                                          | 23 |

| n 1 |                                                                                                                                                                  |    |

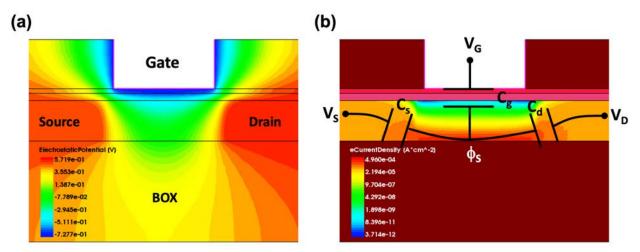

| 3.1 | (a) Electrostatic potential profile and (b) current density profile of a short-channel                                                                           |    |

|     | n-type SOI MOSFET biased in sub-threshold regime ( $V_{GS} = 0V$ and $V_{DS} = 0.05V$ ). Passages of the built in retential between the gate and the sagress and |    |

|     | 0.05V.) Because of the built-in potential between the gate and the source and                                                                                    |    |

|     | drain, the electrostatic coupling causes the potential to be lower at the channel                                                                                |    |

|     | surface than at the bottom. As a result, the leakage is dominated by the bottom path, which implies the TOB best describes SS and DIBL is located at the bottom  |    |

|     |                                                                                                                                                                  | 25 |

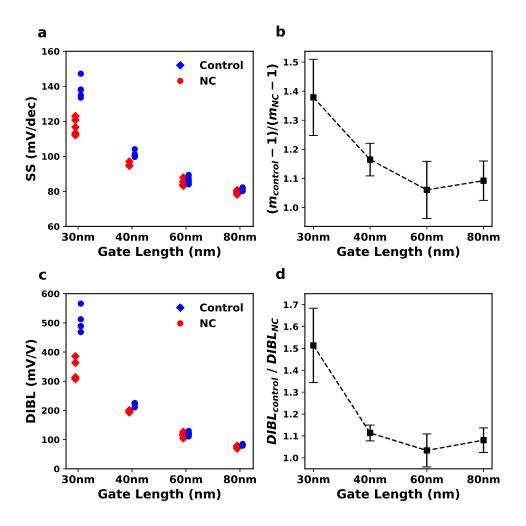

| 3.2 | of the Si layer                                                                                                                                                  | 20 |

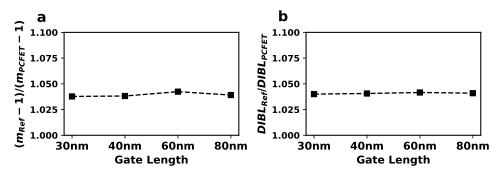

| ე.∠ | DIBL scatter plot, and (d) control-to-NC DIBL ratio with error bar, measured for                                                                                 |    |

|     | different $L_q$ devices. Each data point in (a) and (c) corresponds to one measured                                                                              |    |

|     | device, where a small horizontal shift is used to separate control and NC results                                                                                |    |

|     | for better visualization. The bars in (b) and (d) indicate the sample standard                                                                                   |    |

|     | deviation of each ratio due to device-to-device variations                                                                                                       | 27 |

|     | deviation of each ratio due to device to-device variations                                                                                                       | 41 |

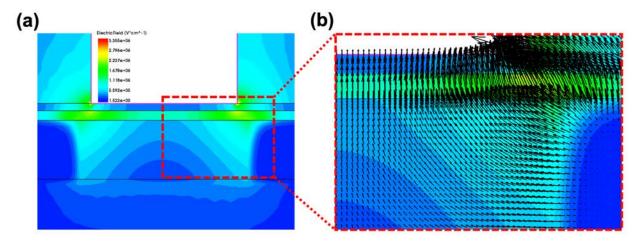

| 3.3 | Electric field profile of a short channel SOI MOSFET in sub-threshold regime.<br>The light color in the silicon channel near the source and the drain edge is due to                                                                  |                |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|     | the inner fringing field coupling, and it does not fully decay at the middle of the channel. (b) is a zoomed-in view of (a) from mid-channel region to the drain edge                                                                 |                |

|     | with arrows indicating the field direction. The electric field on the gate stack is                                                                                                                                                   |                |

|     | nearly vertical for the mid-channel region.                                                                                                                                                                                           | 28             |

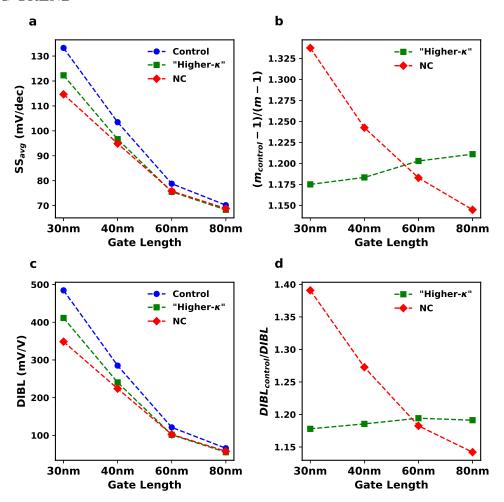

| 3.4 | Simulated (a) SS, (b) $m-1$ ratios of control devices to improved devices, (c)                                                                                                                                                        |                |

|     | DIBL, and (d) DIBL ratios of control devices to improved devices, as a function                                                                                                                                                       |                |

|     | of $L_g$ . The control devices consist of 2.31nm-EOT gate stacks. Improved devices                                                                                                                                                    |                |

|     | include "higher- $\kappa$ " conventional devices (EOT=1.73nm) and NC devices ( $\alpha = 2.4 \times 10^{11} \text{ cm}/F$ , $\beta = 0 \text{ cm}^5/(FC^2)$ , $\alpha = 3.2 \times 10^{33} \text{ cm}^9/(FC^4)$ , $\alpha = 10$ , and |                |

|     | $-2.4 \times 10^{11} cm/F$ , $\beta = 0 cm^5/(FC^2)$ , $\gamma = 3.2 \times 10^{33} cm^9/(FC^4)$ , $\epsilon_r = 19$ , and SiO <sub>2</sub> /FE interface charge density of $-0.64 \mu C/cm^2$ )                                      | 30             |

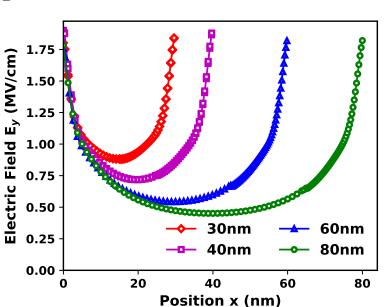

| 3.5 | Simulated out-of-plane electric field $(E_y)$ in the interfacial layer of NCFETs with                                                                                                                                                 | 90             |

| 0.0 | different $L_q$ as a function of position along the channel $(x)$ from source edge                                                                                                                                                    |                |

|     | $(x = 0)$ to drain edge $(x = L_q)$ at $V_{GS} = 200mV$ and $V_{DS} = 50mV$ (in sub-                                                                                                                                                  |                |

|     | threshold regime.)                                                                                                                                                                                                                    | 31             |

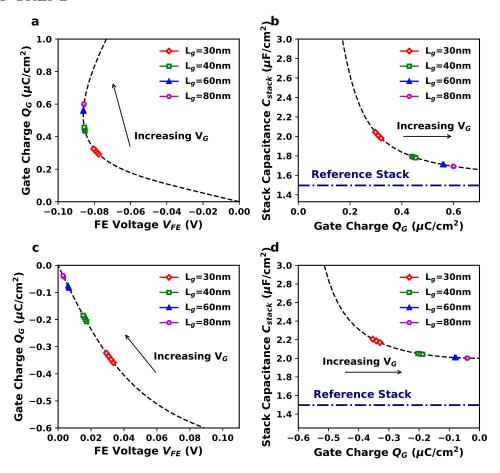

| 3.6 | Simulated (a), (c) $Q - V$ relations of the ferroelectric layer and (b), (d) $C - Q$                                                                                                                                                  |                |

|     | relations of the gate stack at the mid-channel of NCFETs with different $L_g$ . For                                                                                                                                                   |                |

|     | each $L_g$ , the gate voltage is ramped at which $I_D$ is from $10 \text{pA}/\mu\text{m}$ to $100 \text{pA}/\mu\text{m}$                                                                                                              |                |

|     | at $V_{DS}$ =50mV. For (a) and (b), the ferroelectric parameters are $\alpha = -2.4 \times 10^{-2}$                                                                                                                                   |                |

|     | $10^{11} cm/F$ , $\beta = 0 cm^5/(FC^2)$ , $\gamma = 3.2 \times 10^{33} cm^9/(FC^4)$ , and $\epsilon_r = 19$ . The devices                                                                                                            |                |

|     | in (a) and (b) are simulated with $-0.64\mu C/cm^2$ fixed charges at the SiO <sub>2</sub> /FE interface. For (c) and (d), the ferroelectric parameters are $\alpha = -1.4 \times 10^{11} cm/F$ ,                                      |                |

|     | $\beta = -1.2 \times 10^{22} cm^5/(FC^2)$ , $\gamma = 8.0 \times 10^{32} cm^9/(FC^4)$ , and $\epsilon_r = 19$ . No interface                                                                                                          |                |

|     | charges are assumed in (c) and (d)                                                                                                                                                                                                    | 32             |

| 3.7 | Simulated (a) $m-1$ ratios (b) DIBL ratios between control MOSFETs and                                                                                                                                                                | 0_             |

|     | ferroelectric FET with nonlinear positive-capacitance oxide. For the imaginary                                                                                                                                                        |                |

|     | positive-capacitance ferroelectric material, $\alpha = 4 \times 10^{11} cm/F$ , $\beta = 10^{22} cm^5/(FC^2)$ ,                                                                                                                       |                |

|     | and $\gamma = 10^{31} cm^9 / (FC^4)$                                                                                                                                                                                                  | 33             |

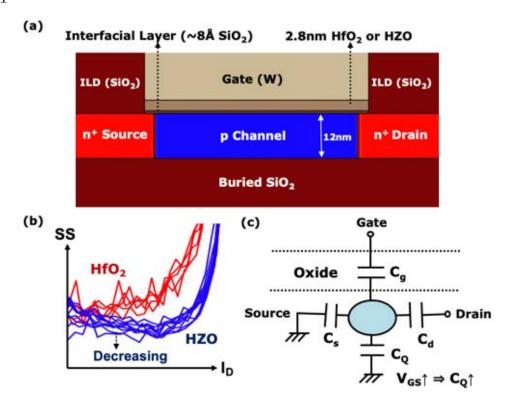

| 4.1 | (a) Schematic cross-section of the SOI n-MOSFETs. Both HfO <sub>2</sub> (Control) and                                                                                                                                                 |                |

|     | HZO (NC) devices have the same geometry. (b) SS of HfO <sub>2</sub> and HZO devices                                                                                                                                                   |                |

|     | demonstrating conventional and unconventional trend with respect to $I_D$ , respec-                                                                                                                                                   |                |

|     | tively. (c) Equivalent circuit diagram of the MOSFET in sub-threshold regime.                                                                                                                                                         | 35             |

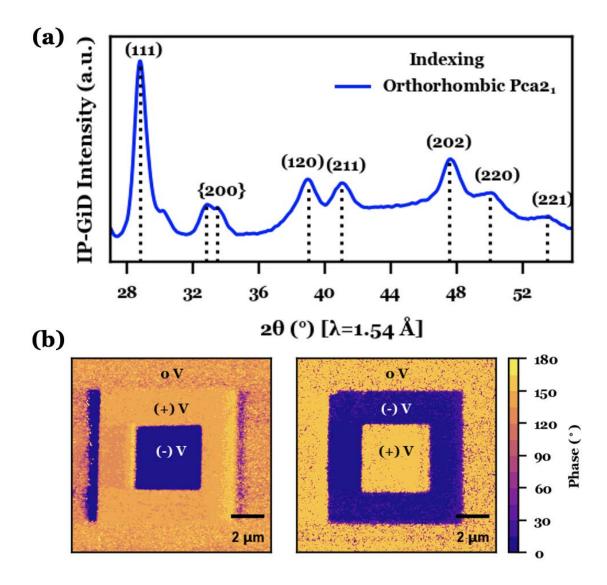

| 4.2 | Demonstration of inversion symmetry breaking and switchable electric polariza-                                                                                                                                                        |                |

|     | tion in 3 nm ZHO film. (a) Synchrotron in-plane grazing-incidence (IP-GiD)                                                                                                                                                            |                |

|     | diffraction indexed to the polar orthorhombic phase (Pca2 <sub>1</sub> ) associated with                                                                                                                                              |                |

|     | ferroelectric order in HfO <sub>2</sub> -based systems. (b) Piezoresponse force microscopy                                                                                                                                            |                |

|     | (PFM) phase-contrast images demonstrating stable, bipolar, remanent polariza-                                                                                                                                                         | 36             |

|     | tion states that can be overwritten into opposite polarization states                                                                                                                                                                 | $\mathfrak{I}$ |

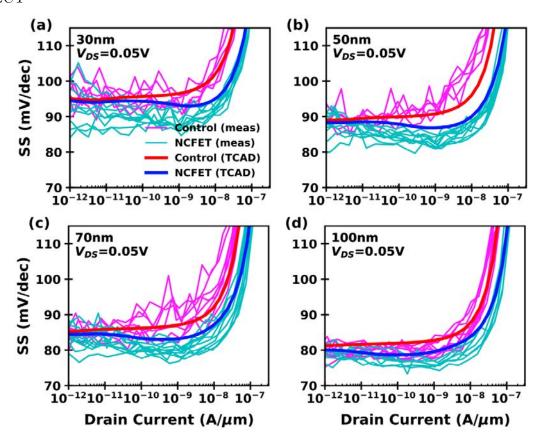

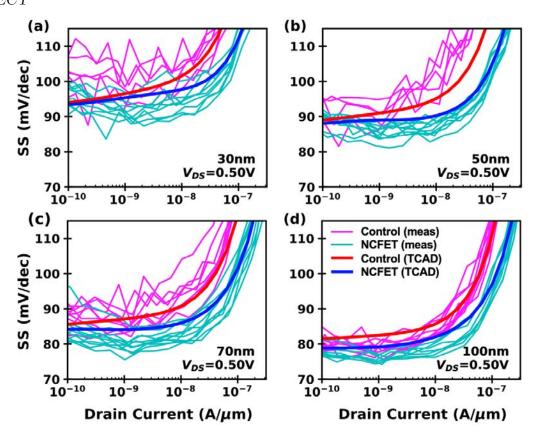

| 4.3  | Measured and TCAD-simulated SS- $I_D$ relations for Control and NC n-MOSFETs of four gate lengths at $V_{DS}$ =50mV. Applied $V_{gs}$ for measurement is -0.4V $\sim$ 1V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Multiple devices are measured for each gate length, all of which exhibit negligible hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38 |

| 4.4  | Measured and TCAD-simulated SS- $I_D$ relations for Control and NC n-MOSFETs of four gate lengths at $V_{DS}$ =500mV. Applied $V_{gs}$ for measurement is -0.4V $\sim$ 1V. Multiple devices are measured for each gate length, all of which exhibit negligible hysteresis                                                                                                                                                                                                                                                                                                                                                                                        | 39 |

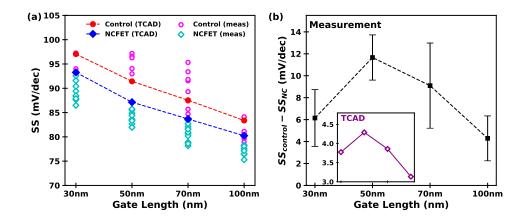

| 4.5  | (a) SS averaged over $I_D$ =0.1~1nA/ $\mu$ m at $V_{DS}$ =0.05V for measured and TCAD-simulated Control and NC MOSFET. Each marker presents one device having the corresponding gate length. (b) Experimentally estimated SS improvement for different gate lengths. Each error bar presents the estimated mean and one standard                                                                                                                                                                                                                                                                                                                                 | 00 |

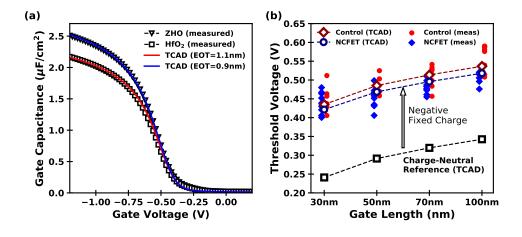

| 4.6  | deviation. (Inset) TCAD-modeled Improvements for the four gate lengths (a) Measured and TCAD-simulated C-V for p-type doped MOS capacitors with HfO <sub>2</sub> and ZHO gate stacks. No frequency dispersion is observed up to 300kHz for measurement gate bias range. (b) Constant-current ( $I_D=10$ nA/ $\mu$ m) threshold voltage ( $V_t$ ) at $V_{DS}=0.05$ V for measured and TCAD-simulated Control and NC MOSFET. Each marker presents an extraction for one device. Experimental $V_t$ are 0.18V higher than reference simulations with nearly neutral net oxide and interface trapped charge. The discrepancy is received when $0.67\mu C/cm^2$ fixed | 40 |

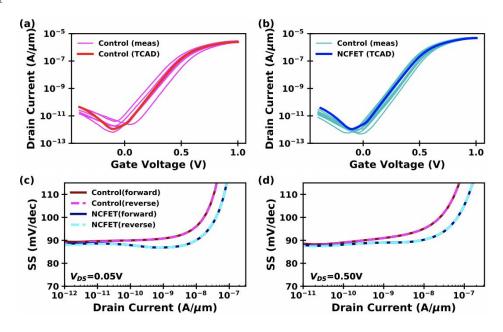

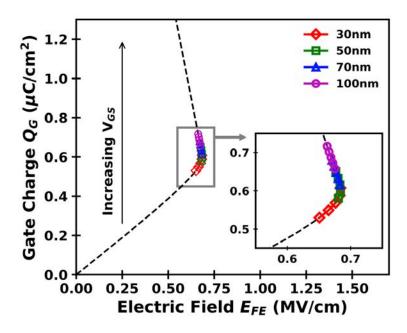

| 4.7  | interface trapped charge. The discrepancy is resolved when $-0.67\mu\text{C/cm}^2$ fixed charge is added to the model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40 |

| 4.8  | overlapping curves, implying zero hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42 |

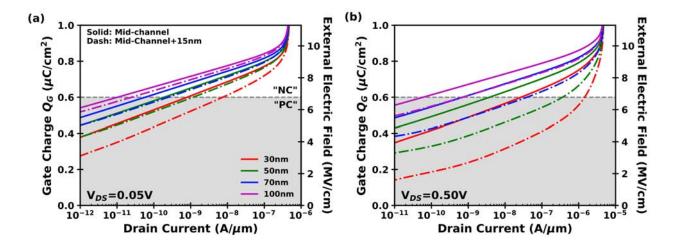

| 4.9  | length, the gate voltage is ramped at which $I_D$ is from $0.1 \text{nA}/\mu\text{m}$ to $1 \text{nA}/\mu\text{m}$ . Simulated relations between drain current and (left axis) local gate charge density / (right axis) local external electric field at (a) $V_{DS}$ =0.05V and (b) $V_{DS}$ =0.50V for NCFETs. For each gate length, the solid line is extracted at mid-channel gate stack region, and the dash line is extracted at the region 15nm laterally from mid-channel toward the drain. The white-background region corresponds to bias conditions at which the polar layer exhibits negative capacitance, while the dark                            | 43 |

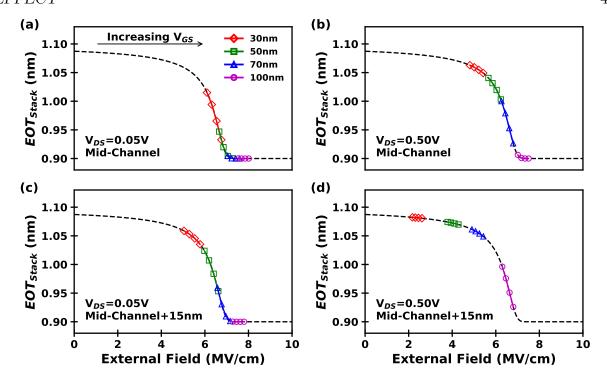

| 4.10 | background stands for positive-capacitance regime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43 |

|      | stack and applied external electric field extracted at $I_D$ =0.1 $\sim$ 1nA/ $\mu$ m. Extractions are made at different lateral positions under two drain biases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44 |

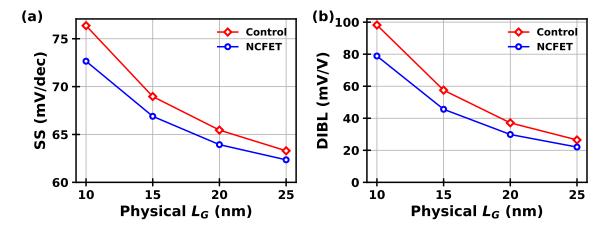

| 4.11 | Simulated (a) SS and (b) DIBL for various $L_G$ with the Control gate stack and a charge-engineered gate stack that exhibits sustained NC behavior. FinFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | structures with 7nm fin thickness are assumed according to the IRDS "5nm" node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45 |

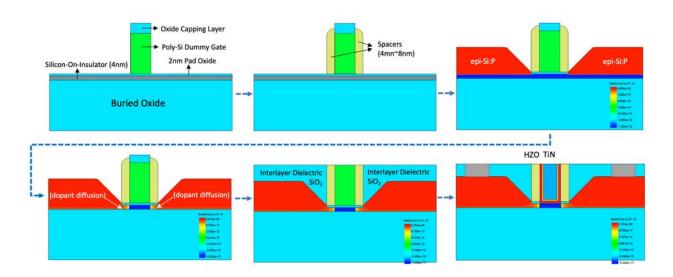

| 5.1 | Overview of the front-end process flow in this study. The shown example corresponds to the "faceted RSD" flow as described in [85], but is gate-last to accom-     |            |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     | modate the low thermal budget of the ferroelectric-metal gate stack                                                                                                | 48         |

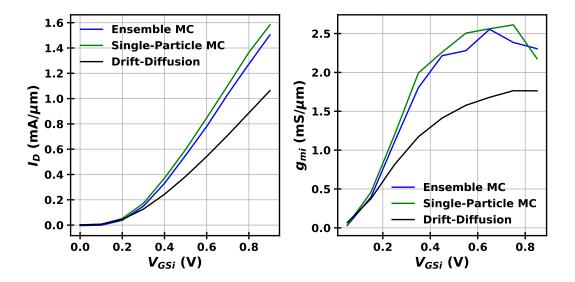

| 5.2 | Three types of devices studied in this work. (a) The typical RSD structure                                                                                         |            |

|     | with nitride spacer and nearly-vertical RSD side walls. (b) The air-gap spacer                                                                                     |            |

|     | structure where the nitride spacer is removed from (a). (c) The slanted-side-wall                                                                                  |            |

|     | RSD structre formed through specialized epi-Si:P module                                                                                                            | 50         |

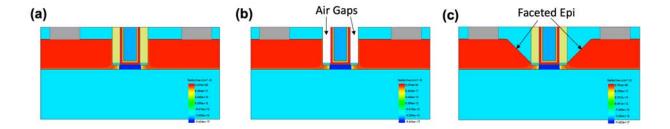

| 5.3 | (a) The equivalent circuit diagram for modeling small-signal responses of the SOI                                                                                  |            |

|     | FET device. (b) Decomposition of the SOI FET into the intrinsic channel and the                                                                                    |            |

|     | RSD subsystems. (c) Simulated structure for extracting intrinsic components $g_m$ ,                                                                                |            |

|     | $r_o$ , $C_{qsi}$ , and $C_{qdi}$ . (d) Simulated structure for parasitic components associated                                                                    |            |

|     | with the raised source $(C_{gse1}, C_{gse2}, \text{ and } r_s)$ and the drain $(C_{gde1}, C_{gde2}, \text{ and } r_d)$                                             | 51         |

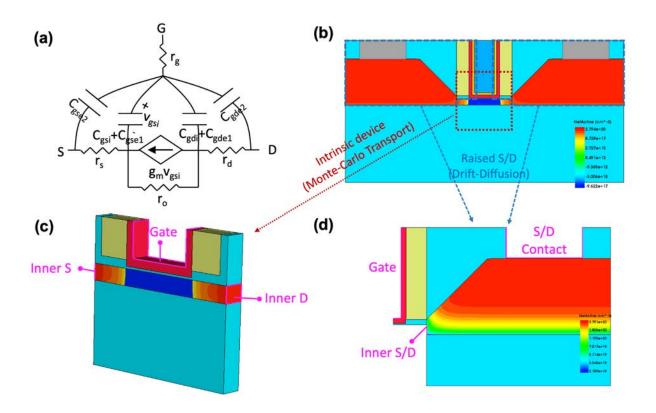

| 5.4 | Simulated (a) $I_D$ - $V_{GS}$ and (b) $g_m$ - $V_{GS}$ at $V_{DS}$ =0.7V of the same device structure                                                             |            |

|     | through different transport solvers with similar low-field mobility and optical                                                                                    |            |

|     | phonon scattering models. The drift-diffusion simulation produces lower current                                                                                    |            |

|     | than the more rigorous solvers. The single-particle MC simulation produces a                                                                                       |            |

|     | slightly higher current than the MC simulation with self-consistent electrostatic                                                                                  |            |

|     | potential                                                                                                                                                          | 53         |

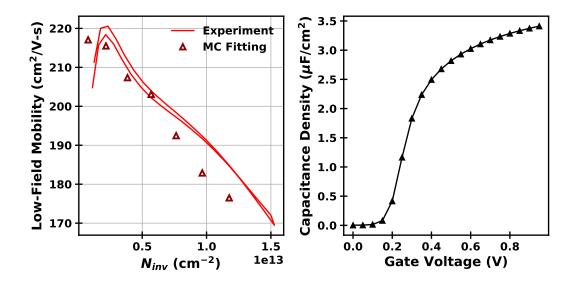

| 5.5 | (a) The measured and MC-simulated low-field electron mobility for long channel                                                                                     |            |

|     | NCFET devices. (b) The simulated long-channel capacitance density                                                                                                  | 53         |

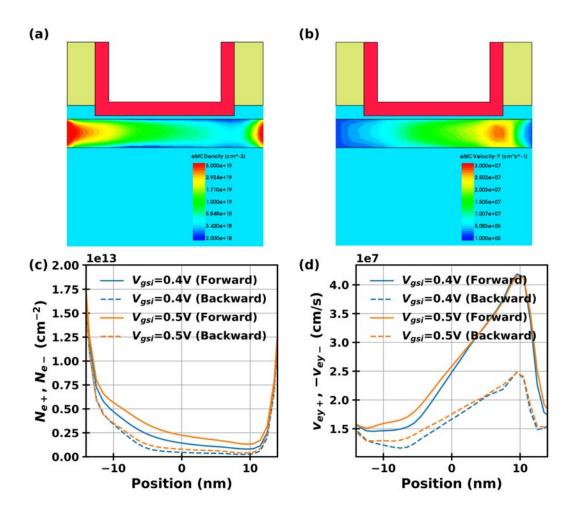

| 5.6 | MC steady-state profile of (a) conduction electron density and (b) electron ve-                                                                                    |            |

|     | locity in the transport direction for a 4nm-spacer NCFET at $V_{GSi} = 0.45V$ and                                                                                  |            |

|     | $V_{DSi} = 0.7V$ . (c) The sheet density of the right-going electrons $(N_{e+})$ and the                                                                           |            |

|     | left-going electrons $(N_{e-})$ (d) The averaged velocity in the transport direction                                                                               |            |

|     | for the right-going electrons $(v_{ey+})$ and the left-going electrons $(v_{ey-})$ . The x-axes                                                                    |            |

|     | for (c) and (d) represents the lateral position from the inner source (-14nm) to                                                                                   |            |

|     | the inner drain $(14nm)$                                                                                                                                           | 56         |

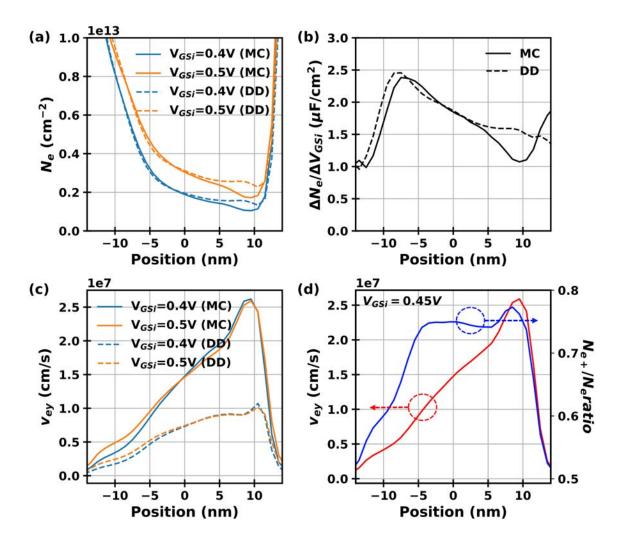

| 5.7 | (a) The sheet conduction electron density $(N_e)$ , (b) the local capacitance density                                                                              |            |

|     | characterizing the response of the $N_e$ to the change of $V_{GSi}$ , and (c) the averaged                                                                         |            |

|     | electron velocity in the transport direction $(v_{ey})$ at $V_{GSi} = 0.4V$ and $0.5V$ . Results                                                                   |            |

|     | from different transport simulators (DD and MC) are shown. (d) The $v_{ey}$ and                                                                                    |            |

|     | the ratio of the $N_{e+}/N_e$ at $V_{GSi} = 0.45V$ . The device is the same as that shown                                                                          | <b>F</b> O |

| E 0 | in Fig. 5.6, and the position follows the same definition                                                                                                          | 58         |

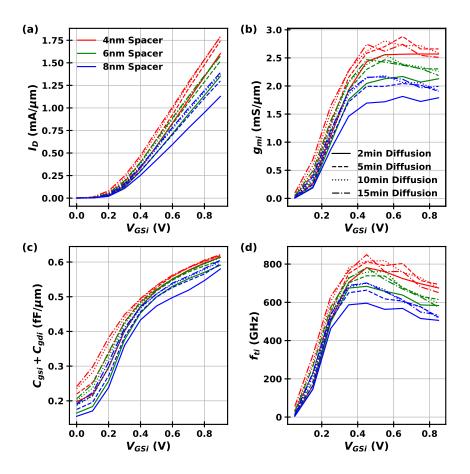

| 5.8 | Simulated (a) $I_D$ - $V_{GSi}$ , (b) $g_{mi}$ - $V_{GSi}$ , (c) $(C_{gsi} + C_{gdi})$ - $V_{GSi}$ , and (d) $f_{ti}$ - $V_{GSi}$ at                               |            |

|     | $V_{DSi}$ =0.7V for faceted RSD devices with various spacer thicknesses and dopant diffusion times. All subplots share the same logands. Small fluctuations of $a$ |            |

|     | diffusion times. All subplots share the same legends. Small fluctuations of $g_{mi}$ and $f_{ti}$ are due to the random nature of MC simulations                   | 59         |

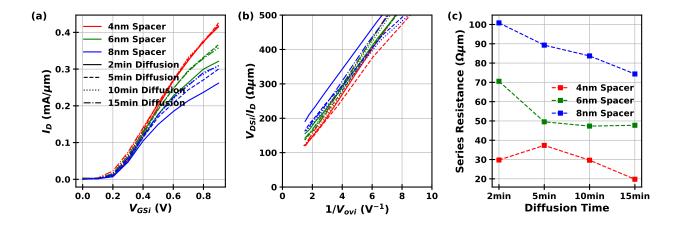

| 5.9 | Simulated (a) $I_D$ - $V_{GSi}$ , (b) $V_{DSi}/I_D$ - $1/V_{ovi}$ , and (c) the extracted series resistance                                                        | 09         |

| 5.5 | for the intrinsic device at $V_{DSi}$ = 0.05V for faceted RSD devices with various spacer                                                                          |            |

|     | thicknesses and dopant diffusion times. The legend for (a) also applies to (b).                                                                                    | 60         |

|     | inclined obtain diffusion times. The regent for (a) also applies to (b).                                                                                           | 00         |

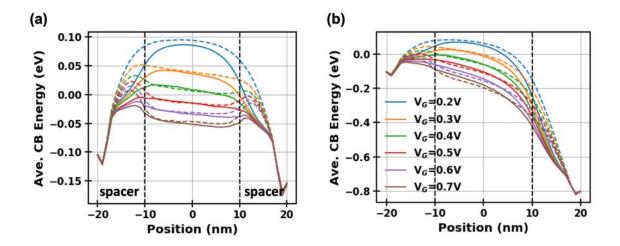

| 5.10 | The vertically-averaged conduction band energy for the SOI versus the lateral position from inner S to inner D at various $V_{GSi}$ for (a) $V_{DSi}$ =50mV and (b) |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $V_{DSi}=0.7$ V. Vertical dashed lines indicate the boundary for the gate stack and                                                                                 |     |

|      | the spacers. The simulated devices have 8nm spacers undergoing 2min (dashed                                                                                         |     |

|      | curves) or 10min (solid curves) dopant diffusion at 800°C. The 2min-diffusion                                                                                       |     |

|      | cases have the top of the potential barrier in the spacer extension region at the                                                                                   |     |

|      | source side and hence much weaker gate control of the barrier height as compared                                                                                    |     |

|      | to the 10min-diffusion cases                                                                                                                                        | 61  |

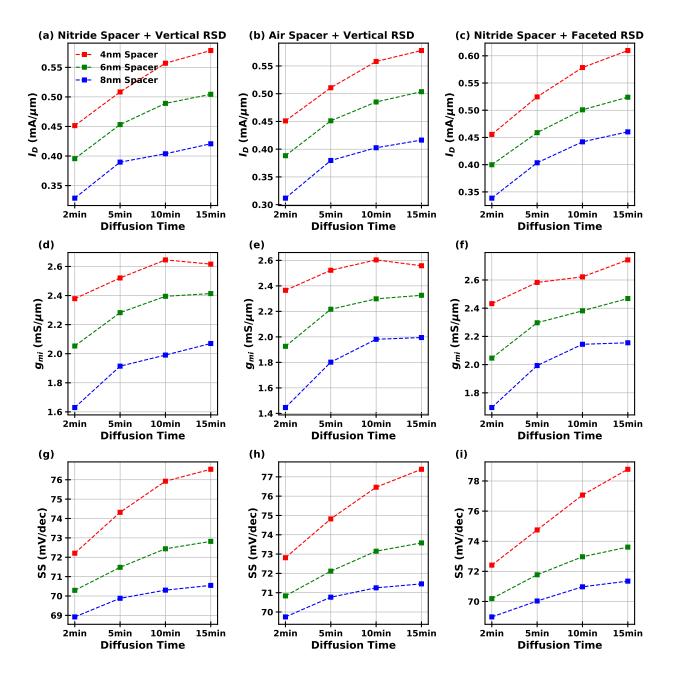

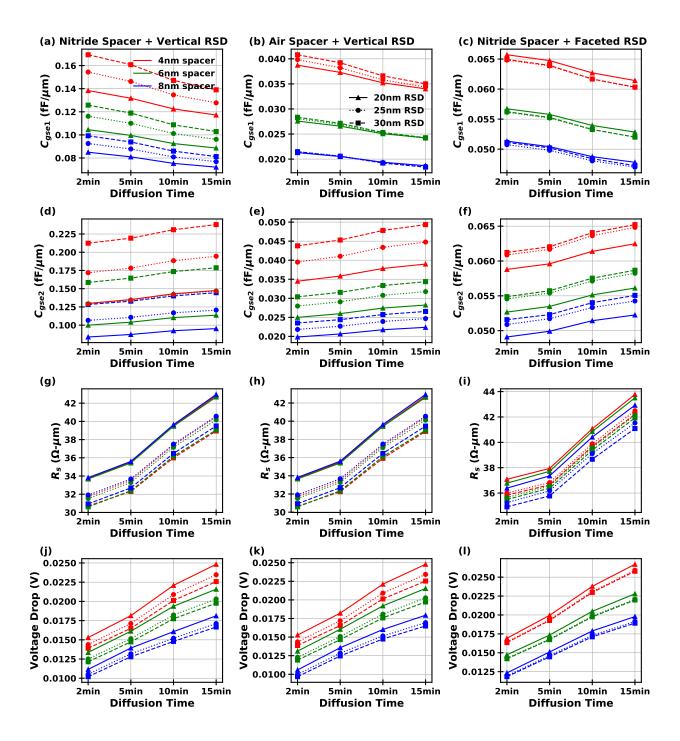

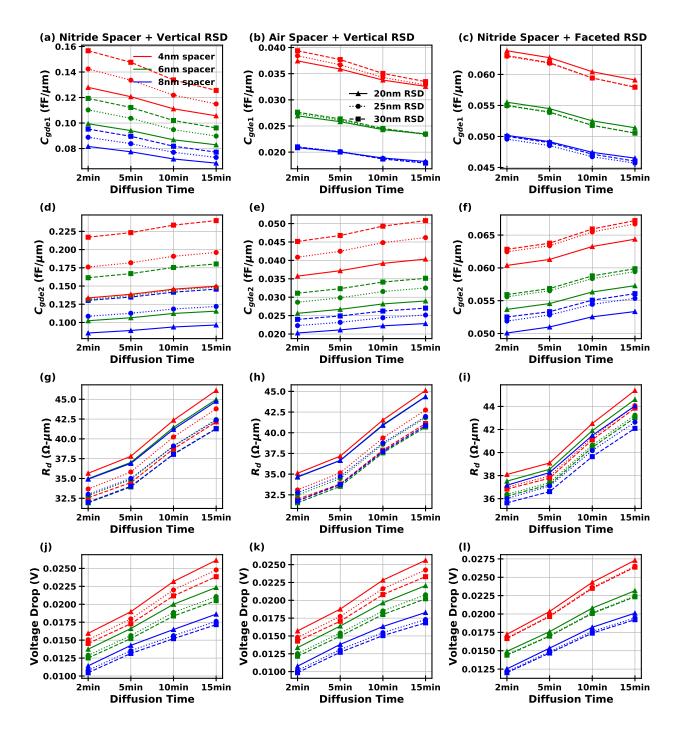

| 5 11 | Extract (a)-(c) $I_D$ at $V_{GSi}$ =0.45V and $V_{DSi}$ =0.7V, (d)-(f) $g_{mi}$ at at $V_{GSi}$ =0.45V                                                              | OI  |

| 9.11 | and $V_{DSi}$ =0.7V, and (g)-(i) SS at $V_{GSi}$ =0.49 V and $V_{DSi}$ =0.7V. The same column of                                                                    |     |

|      | subplots represents the same type of device structure as indicated in (a)-(c)                                                                                       | 62  |

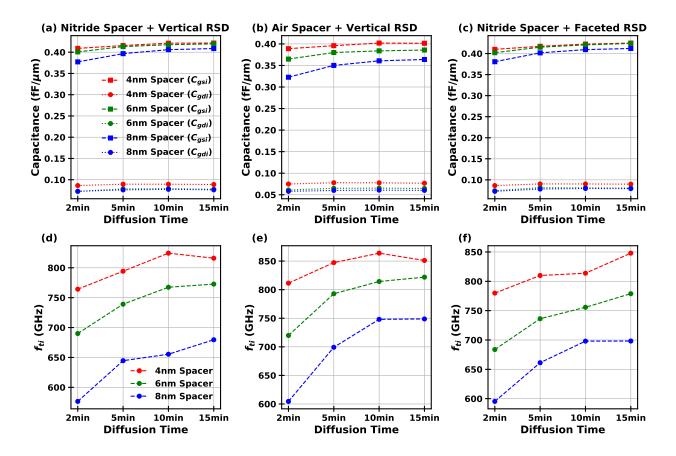

| 5 19 | Extract (a)-(c) $C_{gsi}$ and $C_{gdi}$ at $V_{GSi}$ =0.45V and $V_{DSi}$ =0.7V, (d)-(f) $f_{ti}$ at at                                                             | 02  |

| 0.12 | $V_{GSi}=0.45$ V and $V_{DSi}=0.7$ V. The same column of subplots represents the same                                                                               |     |

|      | type of device structure as indicated in (a)-(c)                                                                                                                    | 63  |

| 5 12 | Extract (a)-(c) $C_{gse1}$ , (d)-(f) $C_{gse2}$ , (g)-(i) $r_s$ , and (j)-(l) the voltage drop on the                                                               | 05  |

| 5.15 | RSD for the source side at $V_{GSi}$ =0.45V and $V_{DSi}$ =0.7V. The same column of                                                                                 |     |

|      | subplots represents the same type of device structure as indicated in (a)-(c)                                                                                       | 65  |

| 5 11 | Extract (a)-(c) $C_{gde1}$ , (d)-(f) $C_{gde2}$ , and (g)-(i) $r_d$ , and (j)-(l) the voltage drop on                                                               | 0.0 |

| 5.14 | the RSD for the drain side at $V_{GSi}$ =0.45V and $V_{DSi}$ =0.7V. The same column of                                                                              |     |

|      | subplots represents the same type of device structure as indicated in (a)-(c)                                                                                       | 66  |

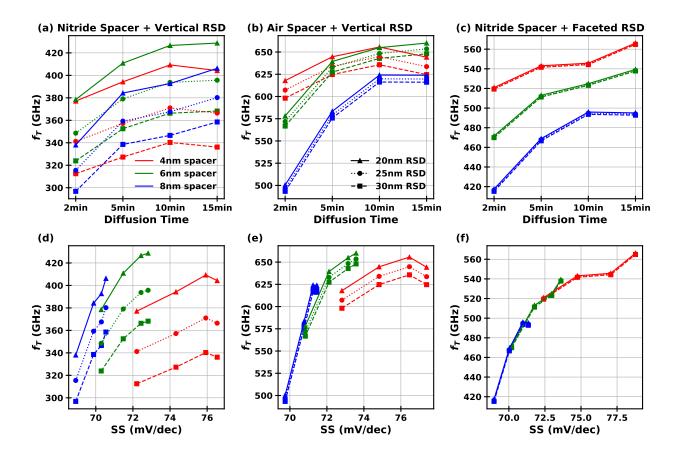

| 5 15 | Extracted $f_t$ at at $V_{GSi}$ =0.45V and $V_{DSi}$ =0.7V for various device structures and                                                                        | 00  |

| 5.15 | process parameters. Legends are shared by all the subplots. The same column of                                                                                      |     |

|      | subplots represents the same type of device structure as indicated in $(a)$ - $(c)$ .                                                                               | 67  |

|      | subplots represents the same type of device structure as indicated in $(a)$ -(c)                                                                                    | 01  |

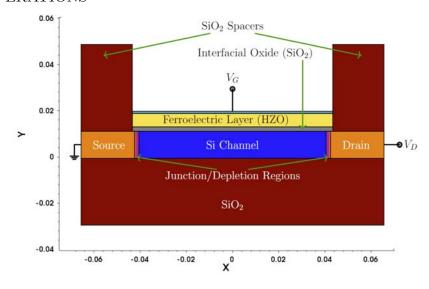

| 6.1  | 2D schematic of the TCAD-simulated SOI-FeFET device                                                                                                                 | 70  |

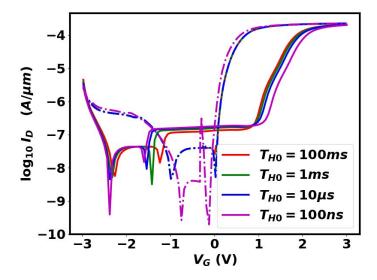

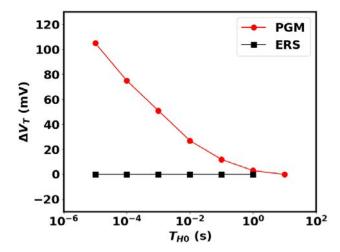

| 6.2  | $I_D$ - $V_G$ readout after different zero-bias-hold times. Solid: high- $V_T$ phase. Dashed:                                                                       |     |

|      | low- $V_T$ phase. The rapid waveform ramp time of $5 \text{ ns } V^{-1}$ ensures no polarization                                                                    |     |

|      | switching occurs during the readout. The magenta curve shows slightly differ-                                                                                       |     |

|      | ent polarization values than the other curves due to a short hold time which is                                                                                     |     |

|      | insufficient for the ferroelectric to reach its equilibrium polarization at $V_{\rm GS} = 0  V$ .                                                                   | 72  |

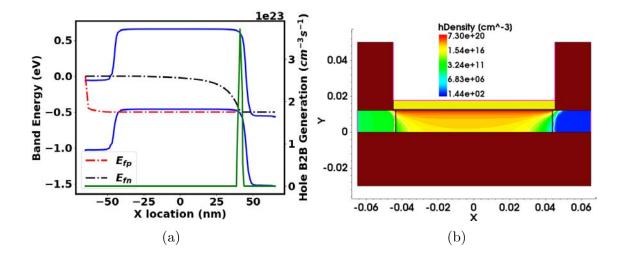

| 6.3  | (a) Band energies (blue) and hole band-to-band generation rate (green) of a                                                                                         |     |

|      | horizontal cross-section taken in the silicon channel (Y= 11 nm, 1 nm from the                                                                                      |     |

|      | interfacial oxide.) A large hole generation is observed in the channel close to drain,                                                                              |     |

|      | due to band-to-band tunneling. (b) A 2D plot showing the hole concentration of                                                                                      |     |

|      | the entire device. A large hole concentration on the order of $10^{20}\mathrm{cm}^{-3}$ is observed                                                                 |     |

|      | at the cross section where (a) is taken                                                                                                                             | 72  |

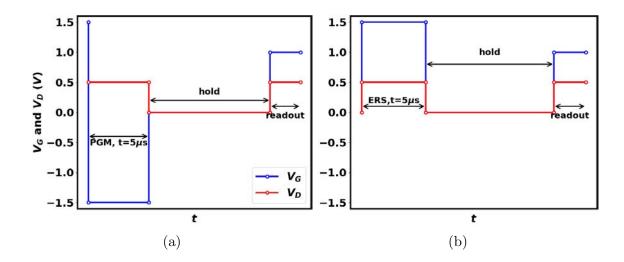

| 6.4  | Waveform schematics for writing and reading (a) high- $V_T$ (PGM) and (b) low- $V_T$                                                                                |     |

|      | (ERS) states. The hold operation is defined as the stage where $V_{\rm GS}=0{\rm V}.$ The                                                                           |     |

|      | readouts for both states are conducted at $V_{\rm GS}=1{\rm V}$ and $V_{\rm DS}=0.5{\rm V}$ . The read                                                              |     |

|      | time is on the order of ns                                                                                                                                          | 74  |

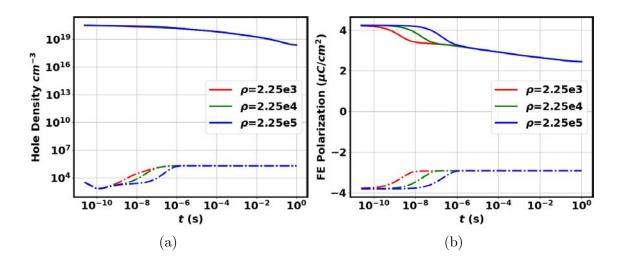

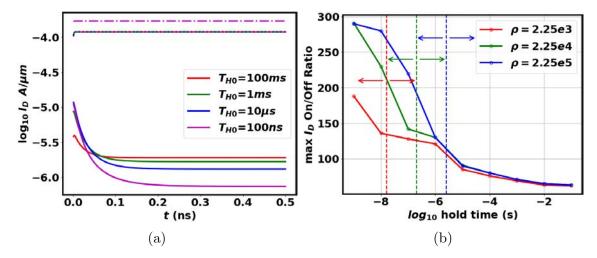

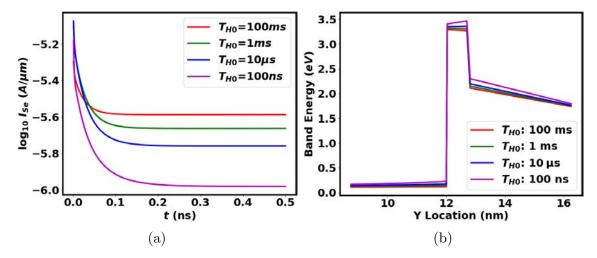

| 6.5  | Transient evolution of (a) Hole density in the Si channel and (b) Ferroelectric polarization during zero-bias hold with different $\rho$ . Solid curve: high-V <sub>T</sub> phase, dashed curve: low-V <sub>T</sub> phase. Reduced hole screening causes the polarization to                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | degrade during hold of high- $V_T$ phase, while the polarization during the low- $V_T$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _        |

| 6.6  | phase remains at a constant value during longer holds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74<br>75 |

| 6.7  | (a) Log drain current during readout (defined as the readout current) after different zero-bias-hold times, $\rho=2.25\times10^5$ . Solid: high-V <sub>T</sub> , dashed: low-V <sub>T</sub> . The low-V <sub>T</sub> readout currents for hold times greater than the polarization switching time are identical and remain flat throughout. The plot is zoomed-in to sub-ns for better visualization of the decay. (b) Maximum read margin, defined as the I <sub>D</sub> ratio of the quasi-steady-state drain current for the two states in (a), as a function of hold time. The arrows to the right show the time scale dominated by the LK equation, while the arrows to the left indicate the hole-dynamics-dominated |          |

|      | zone, particularly during the high- $V_T$ phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 76       |

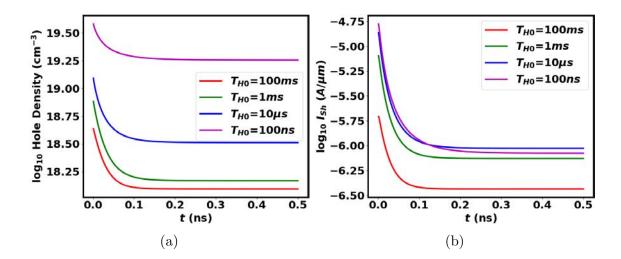

| 6.8  | (a) Log hole density vs. time during readout in the high-V <sub>T</sub> phase for different zero-bias-hold times. The hole density reaches quasi-steady state within 0.5 ns.  (b) Hole source current during readout of the high-V <sub>T</sub> phase. The hole current                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •        |

|      | decreases with increasing hold time due to lower hole concentration, hence diffusion. The quasi-steady-state hole current at $T_{H0} = 100$ ns is slightly lower than $T_{H0} = 10$ µs because of incomplete polarization switching in the ferroelectric at                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|      | short time scales.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77       |

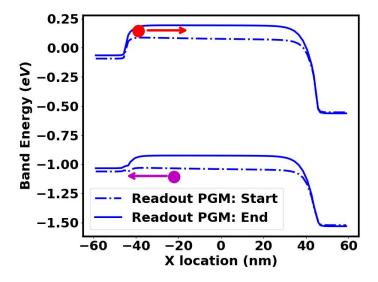

| 6.9  | Energy band diagram at the start (dashed) and end (solid) of the high- $V_T$ state readout. The increases as holes (purple) flow into the source, which increases the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 6.10 | energy barrier for the injection of source electrons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 77       |

|      | Conduction band energy of a vertical cross section showing the $\rm Si/SiO_2/FE$ stack at the end of high-V <sub>T</sub> readout. The electron quasi-Fermi levels at the source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|      | are aligned for all the cases. The reduces as the hold time increases because of reduced polarization, which leads to an increased quasi-steady-state electron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|      | source current in (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 78       |

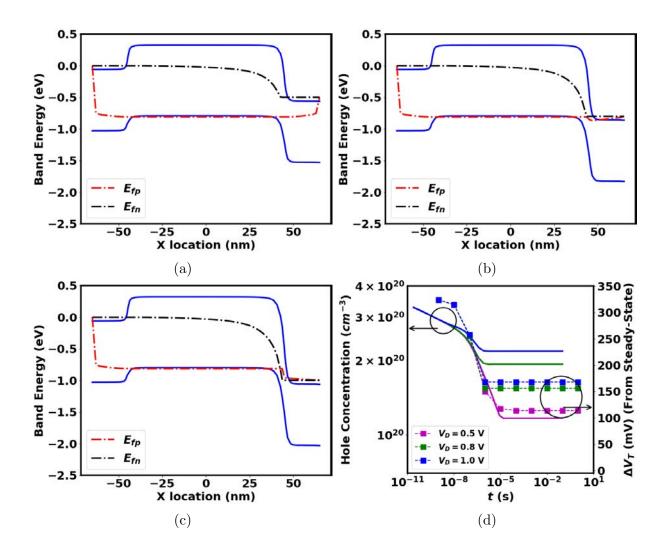

| 6.11 | Lateral band diagrams with quasi-Fermi levels taken at Y= 0.011 during the 0 $V_{GS}$ hold with applied drain bias. (a) $V_{DS} = 0.5  V$ (b) $V_{DS} = 0.8  V$ , and (c) $V_{DS} = 1.0  V$ . (d) The channel hole concentration as a function of zero-                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|      | bias hold time, for the 3 different $V_D$ values. Note that the point at which the hole concentration begins to level off varies significantly with the chosen drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|      | voltage. The high hole concentration and associated $\Delta V_t$ below 1 µs is related to incomplete polarization switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80       |

# List of Tables

| 6.1 | Selected device paramters |  | 7 |

|-----|---------------------------|--|---|

|-----|---------------------------|--|---|

#### Acknowledgments

First and foremost, I would like to thank my research advisor, Prof. Sayeef Salahuddin, for all the kind advice and firm supports over the years. I feel honored and fortunate to be a part of the group, and I really appreciate the impact-driven research culture here at Berkeley. I have grown a lot over the past few years, largely thanks to the role models that I am lucky enough to know in person and learn from. Prof. Salahuddin profoundly inspired me with his keen observations, creativity, and integrity as a researcher, which helped me develop the right attitude and methods to approach different problems. I am also grateful to Prof. Chenming Hu who is also a great source of inspiration and has shared numerous insights and encouragements with me. Both the professors are very kind and down-to-earth, which makes my life as a Ph.D. student delightful. I am immensely thankful for all the supports and the guidance, both technical and personal.

I feel deeply indebted to my undergraduate research advisor, Prof. Cheewee Liu, who opened the door of the fascinating field of semiconductor device research for me. Prof. Liu shaped my self-awareness as an engineer, trained me rigorously and patiently when I was a novice to the field, and encouraged me to pursue a Ph.D. overseas. Without the help, I wouldn't have had the luck to join UC Berkeley nor to build the foundation for the subsequent achievements. Besides, I would like to thank Prof. Junqiao Wu and Prof. Ali Javey for serving on my qualification and dissertation committee. The fruitful discussions with them greatly helped me wrap up my research projects. I also appreciate Prof. Jenn-Gwo Hwu, Prof. Samuel Pan, and many others for all the help and advice. I hope to pass on their kindnesses by staying humble and helping others in the same way as they do.

I hope to express my gratitude to all my family members which is beyond the words. My parents and grandparents raised and educated me well, making my childhood full of care and happiness. They are inseparable from my life. Another special acknowledgement goes to my fiancée, Hsin-Yi, for her continued emotional supports. Her company fills my life in the US with joy and love, constantly bringing motivations and optimisms to me.

I thank all my friends and colleagues at Berkeley, Yen-Kai, Li-Chen, Ming-Yen, Tien-Ning, Hsin-Han, Frank, Tim, Zephy, Fang-Chieh, Chen-Yu, Ping-Hung, Hsiou-Yuan, Yow-Gwo, Ava, Wenshen, Adi, Saavan, Jason, Suraj, Nirmaan, Jiuren, Hong, Korok, Justin, Daewoong, Jong-Ho, Juan, Harshit, Pragya, Avirup, Niklas, Sharon, Neelesh, Michael, Sam, Varun, Alice, Jennifer, Chung-Kuan, and many others, for the help and the good memories. I also would like to thank my mentors, Sheng-Ting and Der-Chuan, for their selfless help and guidance in the early stage of my career. I thank my relatives in the US, Judy, M.-P., Rebecca, Sylvain, and others, for their warmth and hospitality. There are many other people to whom I owe a great deal of thanks. Meeting each of you is a fortune for me, and I wish all the best for you.

# Chapter 1

# Introduction

# 1.1 Needs For Electrical Scaling of CMOS Gate Stack

The advance of Complementary-Metal-Oxide-Semiconductor (CMOS) technology has been mainly motivated by the improvement in the power, performance, and area for digital circuits. Several key benchmarks at the MOS Field Effect Transistor (MOSFET) operation level include

- the dynamic energy dissipation for a switching event  $CV_{DD}^2$ ,

- the intrinsic delay for a switching event  $CV_{DD}/I_{eff}$ , and

- the static leakage power for a stand-by device  $V_{DD}I_{off}$ .

where the C is the effective load per stage including the gate and the fringing field capacitance,  $V_{DD}$  the CMOS supply voltage,  $I_{eff}$  the effective switching current of the transistor in the ON state, and  $I_{off}$  the stand-by current when the transistor is in OFF state. A low C, a low  $V_{DD}$ , a low  $I_{off}$ , and a large  $I_{ON}$  are desired in order to simultaneously achieve low power dissipations and high speed. The last three requirements imply that a sharp transition from OFF to ON state is needed. That is, given a small change in the MOSFET gate-to-source voltage  $(V_{GS})$ , the increase of the MOSFET drain current  $(I_D)$  should be as large as possible.

For the transition rate of MOSFET in strong inversion regime, commonly characterized by the transconductance ( $g_m \equiv \partial I_D/\partial V_{GS}$ ), a high carrier velocity and a large intrinsic gate capacitance are the key boosters. For the sub-threshold regime where the carrier screening effect is negligible, the transition rate is dominated by the electrostatic control. The corresponding figure of merit is the sub-threshold swing (SS)

$$SS \equiv \frac{\partial V_{GS}}{\partial \log_{10} I_D} = \frac{\partial V_{GS}}{\partial \phi_S} \frac{\partial \phi_S}{\partial \log_{10} I_D} = \frac{\partial V_{GS}}{\partial \phi_S} \frac{kT}{q} \ln(10)$$

(1.1)

where k is the Boltzmann constant, T is the operating temperature, q is the charge of an electron, and  $\phi_S$  is the surface potential of the channel that can be determined by the

capacitive voltage divider.

$$\frac{\partial V_{GS}}{\partial \phi_S} = 1 + \frac{C_{Si}}{C_a} \tag{1.2}$$

Here the  $C_q$  is the electrostatic capacitance between gate and the top of the potential barrier (TOB) in the silicon channel, and the  $C_{Si}$  is the capacitance of the TOB that is ascribed to the silicon body. When the mobile carrier has negligible effects on the electrostatics,  $C_{Si}$ includes the coupling from the source, the drain, the substrate. Innovative device structures such as the fully-depleted silicon-on-insulator (FDSOI) MOSFETs, FinFETs, and gate-allaround (GAA) MOSFETs are effective strategies to reduce the  $C_{Si}$  and hence suppress the short channel effects [1]. However, further scaling of the gate length  $(L_q)$  inevitably increases the finite  $C_{Si}$ . Besides, available high-mobility channel materials such as germanium has a larger permittivity than silicon, which can also worsen the  $C_{Si}$ . A large  $C_q$  is still required to maintain a good gate control. Therefore, the intrinsic gate capacitance is important for achieving sharp transitions in terms of both  $g_m$  and SS. The high- $\kappa$ -metal-gate process has been historically one of the most important solutions in this regard, and it is adopted in the state-of-the-art CMOS technology. Note that, although it may seem unfavorable that the intrinsic gate capacitance increases the C that is proportional to the dynamic energy dissipation and intrinsic delay, the corresponding enhancement in  $I_{eff}$  and the allowed reduction in  $V_{DD}$  allow for improvements in the two metrics given that the parasitic capacitance constitutes a large proportion of C in modern technologies. As a result, a high capacitance of the gate stack is generally desired and has become increasingly important for MOSFET scaling.

Specifically, the International Roadmap For Devices and Systems (IRDS) [2] has projected a reduction of  $V_{DD}$  from the 0.75V as of the year of 2021 to 0.55V by 2034, while a similar ON-OFF ratio to the current technology needs to be maintained. One of the major challenges for this goal is in the gate stack. The roadmap calls for an inversion layer thickness ( $t_{inv}$ ), which is the effective SiO<sub>2</sub> thickness (EOT) for the inversion capacitance  $C_{inv}$ , of 0.90nm.

$$t_{inv} = \frac{\epsilon_{SiO_2}}{C_{inv}} = \frac{3.9\epsilon_0}{C_{inv}} \tag{1.3}$$