## Millivolt Micro-Electro-Mechanical Relay Devices & Circuits

Alice Ye

## Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-239 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-239.html

December 1, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Millivolt Micro-Electro-Mechanical Relay Devices & Circuits

by

Zhixin Alice Ye

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Vladimir Stojanović Professor Junqiao Wu

Fall 2020

Millivolt Micro-Electro-Mechanical Relay Devices & Circuits

Copyright 2020

by

Zhixin Alice Ye

#### Abstract

#### Millivolt Micro-Electro-Mechanical Relay Devices & Circuits

by

#### Zhixin Alice Ye

#### Doctor of Philosophy in Electrical Engineering and Computer Science

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

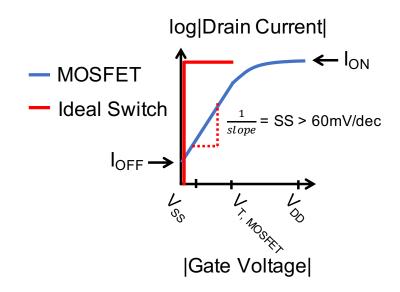

The emergence of the Internet of Things (IoT) has brought energy consumption to the forefront of challenges for future information processing devices. Digital logic integrated circuits (ICs) implemented with complementary metal-oxide-semiconductor (CMOS) transistors have a fundamental lower limit on energy consumption due to their non-zero OFF-state current ( $I_{OFF}$ ) and finite sub-threshold slope. In contrast, micro-electro-mechanical (MEM) switches (relays) can achieve zero  $I_{OFF}$  and have abrupt switching characteristics; therefore, they have attracted growing interest for ultra-low-power computing applications.

This dissertation first addresses challenges for realizing millivolt operation of relay ICs. The impact of electrode configuration on contact resistance and hysteresis voltage is investigated, and it is found that reducing the number of contact dimples from 4 to 2 improves the tradeoff between on-state resistance and minimum operating voltage. With an anti-stiction self-assembled monolayer (SAM) coating, a variety of pass-gate logic circuits using the new 2-contact-dimple relay design are demonstrated to operate with sub-50 mV voltage signals; these include AND, OR and XOR gates and a 2:1 multiplexer (MUX). Multi-functional MEM relay circuits are also demonstrated including a majority gate, 2-bit 2:1 MUX, and dual-polarity gates (XOR/XNOR).

Next, this dissertation addresses remaining practical challenges and discusses opportunities for MEM relay technology. A new method using voltage pulses to reliably break down native oxide on contact-electrode surfaces is developed. SAM coating and operation in liquid dielectric media are explored for improving on-state resistance stability for tungsten contacts in ambient conditions. Finally, MEM relays are demonstrated to function well in extreme environments across a wide temperature range.

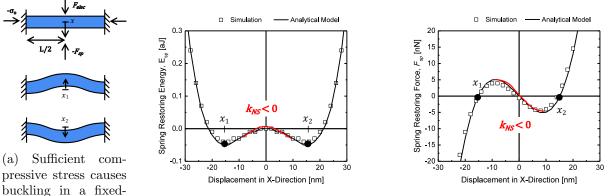

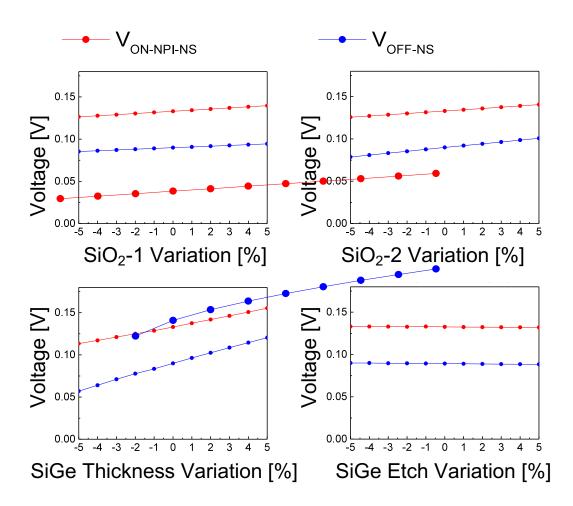

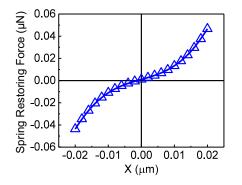

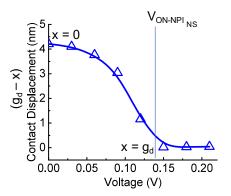

Finally, this dissertation proposes a novel relay design that incorporates a beam with negative stiffness to reduce the body bias voltage necessary for millivolt operation. This compensated relay design is investigated with the aid of computer simulations, and is found to provide for improved tradeoff between relay switching energy and turn-on delay under certain conditions. The effects of process-induced variations on relay switching voltage are studied and compared for the compensated relay design *vs.* a conventional relay design.

To my parents Qiubo and Jing and my brother Edward

# Contents

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                       | ii                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                | iv                               |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                 | ix                               |

| 1       Introduction         1.1       The CMOS Energy Efficiency Limit         1.2       Why MEM Relays?         1.3       MEM Relay Integrated Circuits         1.4       Dissertation Overview                                                                                                                                                                                                                              | 7 9                              |

| 2 Millivolt MEM Relay Integrated Circuits         2.1 Introduction         2.2 Body-biased MEM Relay Operation         2.3 MEM Relay Design and Fabrication         2.4 Multi-Function Relay Integrated Circuits         2.5 Dynamically Reconfigurable Circuit Functionality         2.6 Multi-Output Relay Circuits         2.7 Multiple-Gate MEM Relays         2.8 Non-Idealities in Relay Performance         2.9 Summary | 16<br>21<br>24<br>28<br>30<br>43 |

| <ul> <li>3 Practical Challenges and Opportunities for MEM Relay Circuits</li> <li>3.1 Relay Contact Oxide Breakdown</li> <li>3.2 Study of Relay Operation under Ambient Conditions</li> <li>3.3 Operation in Extreme Environments</li> </ul>                                                                                                                                                                                   | 53                               |

| 4       Compensated Stiffness Relay Design         4.1       Introduction         4.2       Compensated Stiffness Beam Design         4.3       Switching Energy and Voltage Analysis         4.4       Compensated-Stiffness Relay Design Optimization                                                                                                                                                                        | 64<br>70                         |

|          | <ul> <li>4.5 Impact of Process-Induced Variations</li></ul> |    |  |  |

|----------|-------------------------------------------------------------|----|--|--|

| <b>5</b> | Conclusion                                                  | 93 |  |  |

| Bi       | Bibliography                                                |    |  |  |

iii

# List of Figures

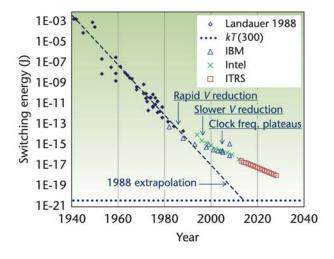

| 1.1 | Gordon Moore's observed trends in comparison to the expected reduction in                                                                                        |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | switching energy using current transistor technologies (reproduced from [1]).                                                                                    | 2  |

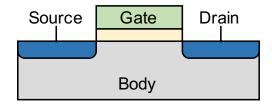

| 1.2 | Schematic cross-section of a MOSFET                                                                                                                              | 3  |

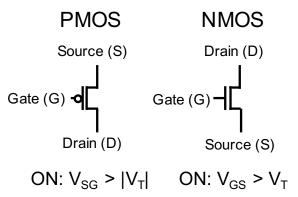

| 1.3 | CMOS circuit symbols for PMOS transistor and NMOS transistor                                                                                                     | 3  |

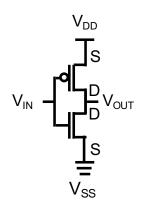

| 1.4 | CMOS implementation of an inverter circuit.                                                                                                                      | 4  |

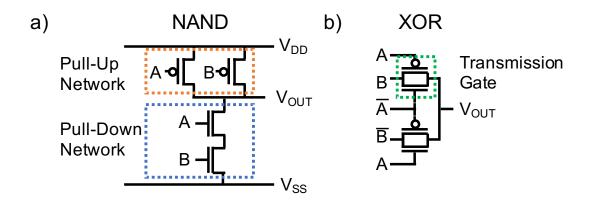

| 1.5 | a) CMOS implementation of a 2-input NAND gate, using a pull-up network of PMOS transistors and a pull-down network of NMOS transistors. b) CMOS                  |    |

|     | implementation of 2-input XOR gate, using two pass gates                                                                                                         | 5  |

| 1.6 | Illustrative transfer characteristic for a MOSFET compared to that for an ideal switch. A MOSFET is a non-ideal switch because it has non-zero off-state leakage |    |

|     | current.                                                                                                                                                         | 5  |

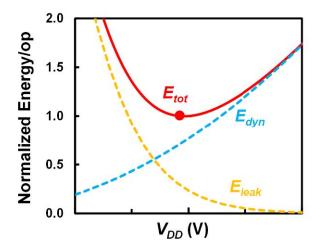

| 1.7 | Tradeoff between dynamic energy and static energy of a CMOS digital logic circuit                                                                                |    |

|     | vs. $V_{DD}$ (reproduced from [6]).                                                                                                                              | 7  |

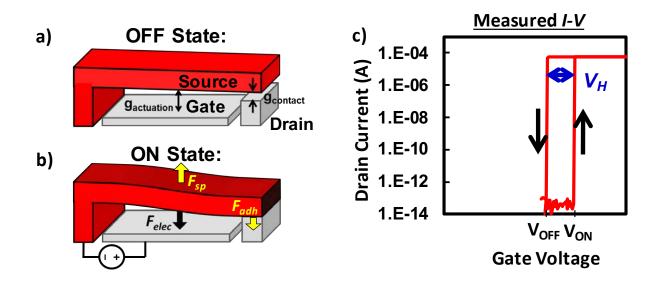

| 1.8 | Illustration of a 3-terminal MEM switch in a) OFF state, and b) ON state. c)                                                                                     |    |

|     | Illustrative semi-log $I_{DS}$ -vs $V_{GS}$ characteristics, showing abrupt switching char-                                                                      |    |

|     | acteristics (adapted from [7])                                                                                                                                   | 8  |

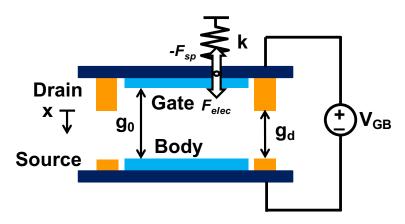

| 2.1 | Simplified model of an electrostatically actuated parallel-plate MEM relay design incorporating two pairs of source/drain conducting electrodes for a total of 6 |    |

|     | terminals. $\ldots$                                                             | 12 |

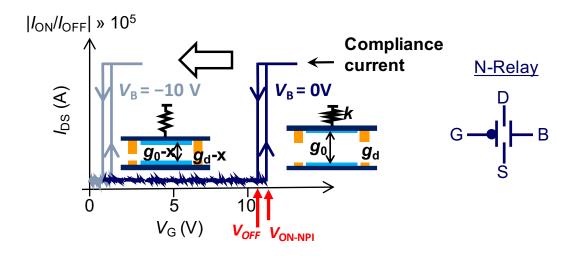

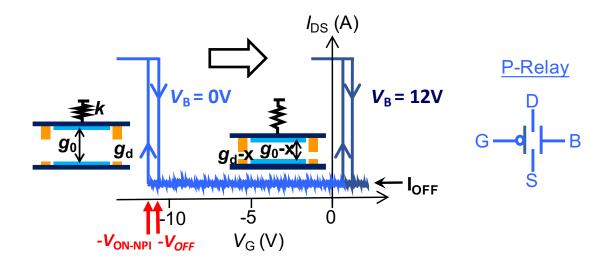

| 2.2 | (left) By applying a negative voltage to the body electrode, the gate voltage swing required to switch a N-relay is reduced. (right) N-relay circuit symbol      | 15 |

| 2.3 | (left) By applying a positive voltage to the body electrode, the gate voltage swing                                                                              |    |

|     | required to switch a P-relay is reduced. (right) P-relay circuit symbol                                                                                          | 15 |

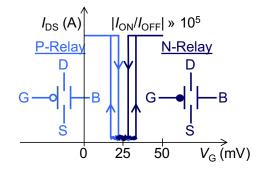

| 2.4 | Idealized body-biased N-relay and P-relay switching characteristics allowing for                                                                                 |    |

|     | millivolt integrated circuit operation $(V_{SS} = 0V \text{ and } V_{DD} = 50 \text{mV})$ .                                                                      | 16 |

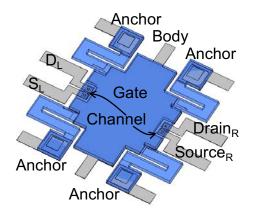

| 2.5 | Isotropic schematic of the 4C MEM relay design, with bridging contacts between                                                                                   |    |

|     | source and drain electrodes                                                                                                                                      | 17 |

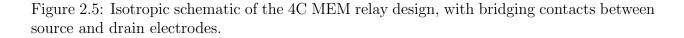

| 2.6 | Isotropic schematic of the 2C MEM relay design with direct contact between                                                                                       |    |

|     | source and drain electrodes                                                                                                                                      | 18 |

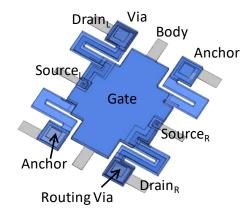

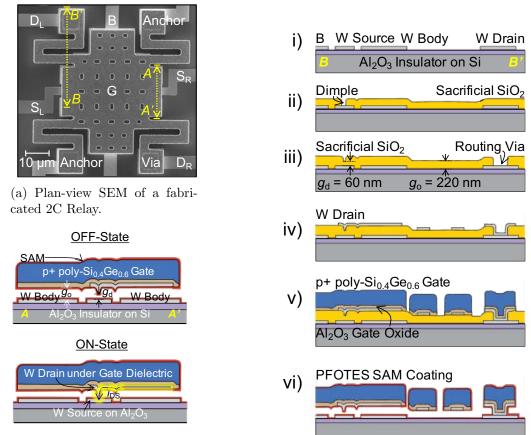

| 2.7 | (a) Plan view and (b) cross-sectional view of 2C dual-direct relay, and (c) fabri-                                                                               |    |

|     | cation process flow.                                                                                                                                             | 19 |

|     |                                                                                                                                                                  |    |

| 2.8  | Comparison of a) N-type and b) P-type 2C dual-direct relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type and d) P-type 4C dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type and d) P-type 4C dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type and d) P-type 4C dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type and d) P-type 4C dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type and d) P-type 4C dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type and d) P-type 4C dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type and d) P-type 4C dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type and d) P-type 4C dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ characteristics with c) N-type AC dual-bridge relay $I_{DS}$ vs. $V_G$ dual-brid |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | teristics, with and without self-assembled monolayer coating. Body-bias voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | $ V_B  \sim 15$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 |

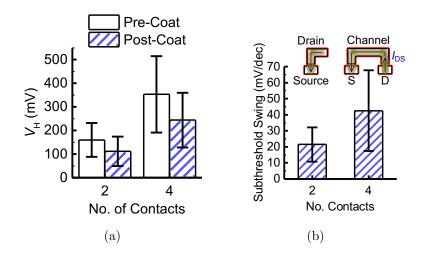

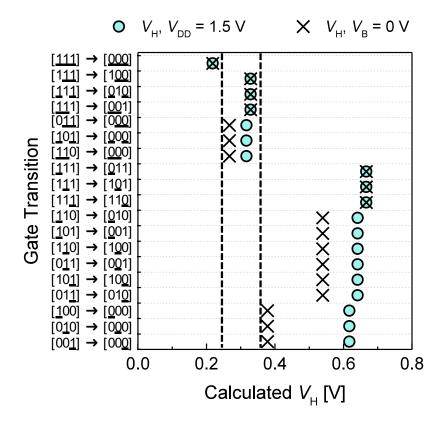

| 2.9  | Comparison of a) hysteresis voltage $(V_H)$ and b) subthreshold swing (SS) values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | for 2C Dual-Direct and 4C Dual-Bridge relays measured at 300 K and 10 $\mu$ Torr.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | $V_{DS} = 200 \text{ mV},  V_B  = \sim 15 \text{ V}.$ The error bars indicate one standard deviation of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | variation, measured across eight relays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21 |

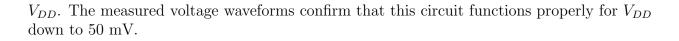

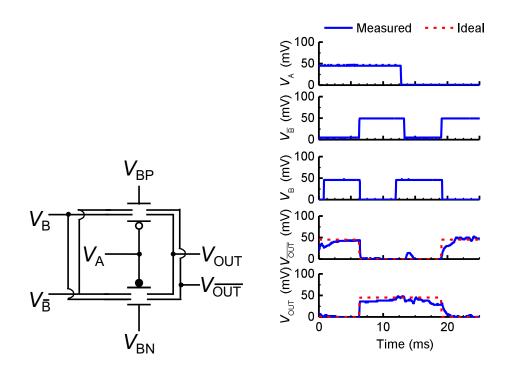

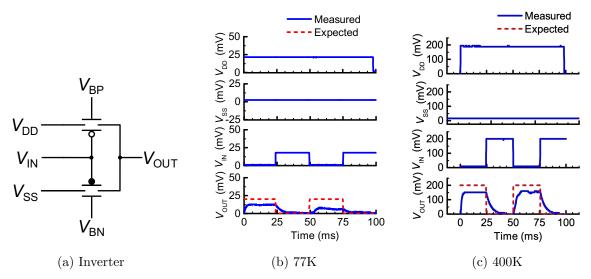

| 2.10 | PFOTES-coated relay inverter circuit operation at 300 K and 10 $\mu$ Torr. $ V_B  =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | ${\sim}15~\mathrm{V}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22 |

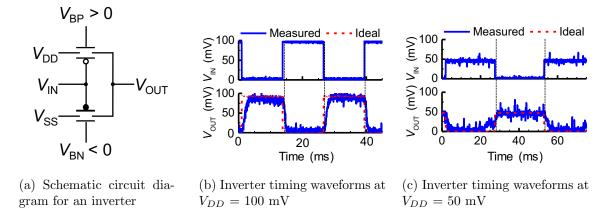

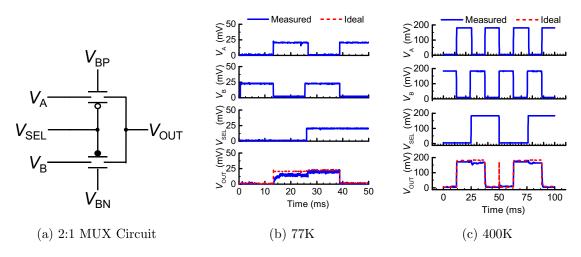

| 2.11 | 2:1 Multiplexer pass-gate logic PFOTES-coated relay circuit operation at 300 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | and 10 $\mu$ Torr. $ V_B  = \sim 15$ V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23 |

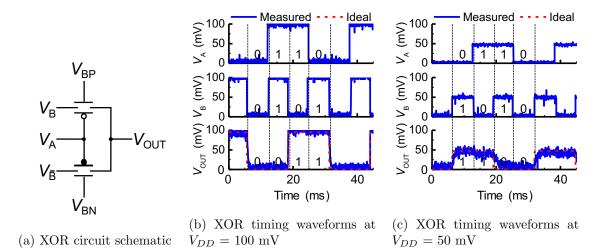

| 2.12 | XOR circuit operation at 300 K and 10 $\mu$ Torr. $ V_B  = \sim 15$ V. Relays were coated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | with PFOTES self-assembled monolayer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 |

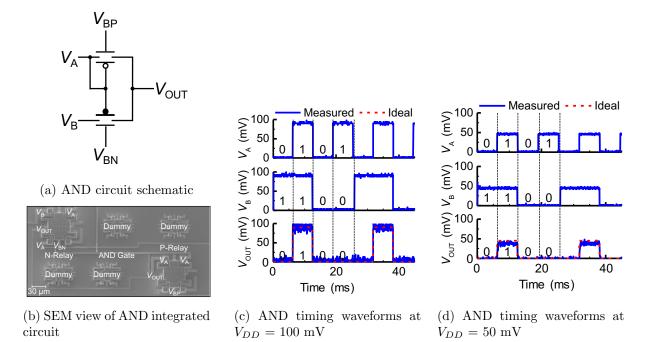

| 2.13 | AND circuit operation at 300 K and 10 $\mu$ Torr. $ V_B  = \sim 15$ V. Relays were coated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | with PFOTES self-assembled monolayer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 |

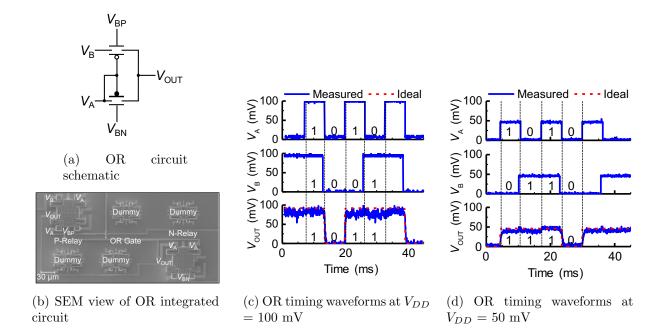

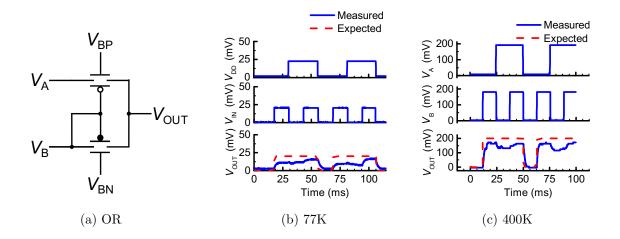

| 2.14 | OR circuit operation at 300 K and 10 $\mu$ Torr. $ V_B  = \sim 15$ V. Relays were coated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | with PFOTES self-assembled monolayer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26 |

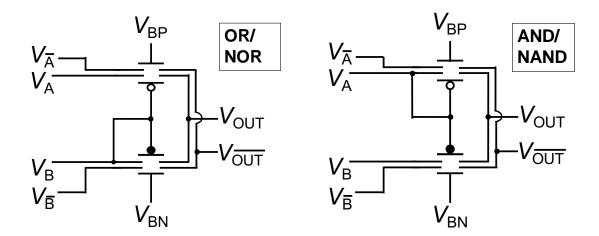

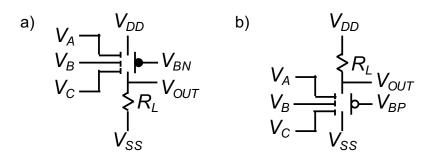

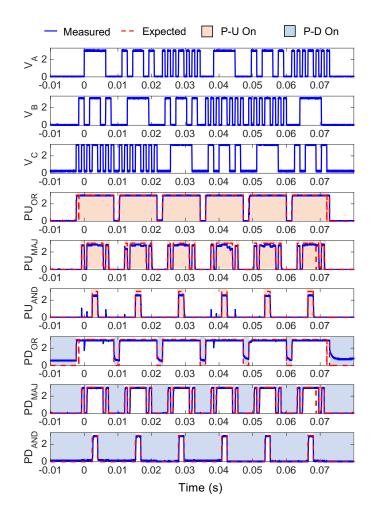

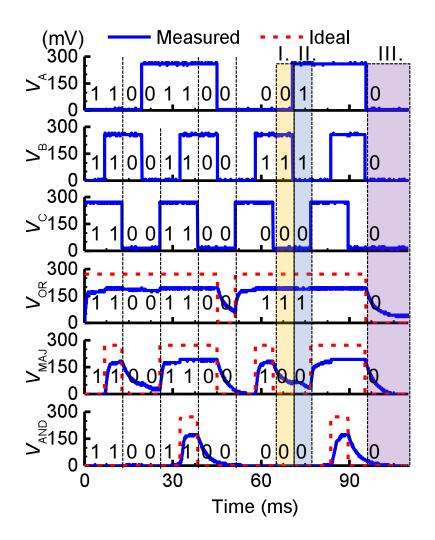

|      | Examples of differential logic gates implemented with dual-S/D MEM relays $\ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28 |

| 2.16 | Demonstration of XOR/XNOR circuit operation at 300 K and 10 $\mu$ Torr. $ V_B  =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | $\sim$ 15 V. Relays were coated with PFOTES self-assembled monolayer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29 |

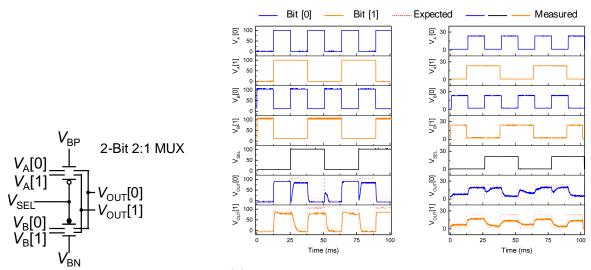

| 2.17 | 2-bit 2:1 Multiplexer circuit operation at 300 K and 10 $\mu$ Torr. $ V_B  = \sim 15$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | Relays were coated with PFOTES self-assembled monolayer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30 |

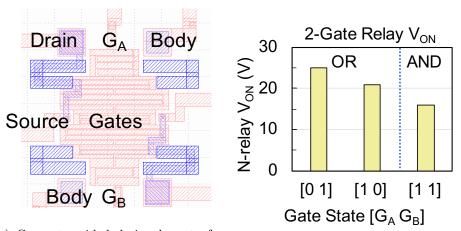

|      | Layout and measured $V_{ON}$ values for a 2-Gate relay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31 |

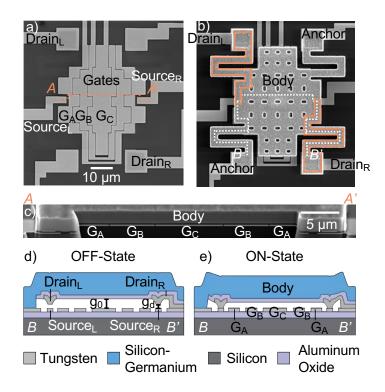

| 2.19 | SEM images of the 3-input MEM relay. (a) Plan view of the patterned electrode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | layer, and (b) plan view of the completed relay. (c) A-A' cross-section. B-B'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20 |

| 0.00 | cross-section schematics in the (d) OFF state and (e) ON-state. $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32 |

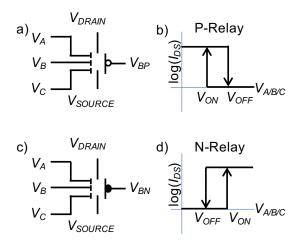

| 2.20 | Three-gate (a) P-relay circuit symbol and (b) I-V characteristics. Three-gate (c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33 |

| 0.01 | N-relay circuit symbol and (d) I-V characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | აა |

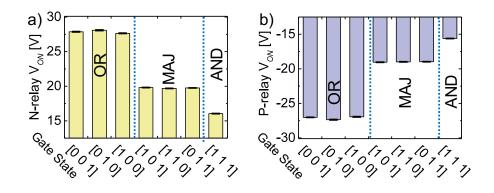

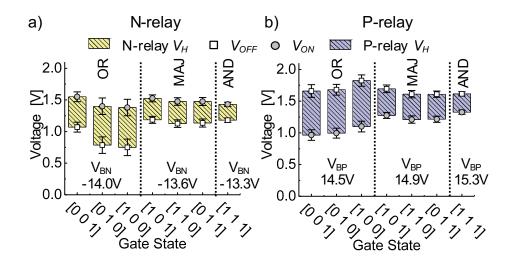

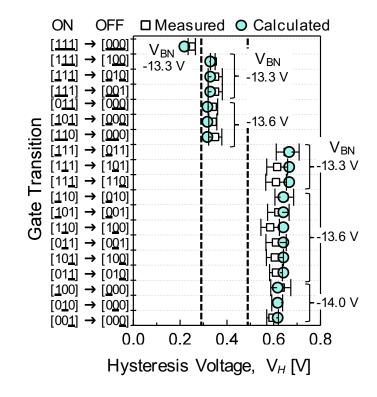

| 2.21 | Measured average $V_{ON}$ values for different combinations of switching gate voltage signals, with $V_B = 0$ V, for (a) N-relay and (b) P-relay operation. Error bars                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | indicate $+/-1$ standard deviation measured across 10 $I_{DS}-V_{A/B/C}$ DC sweeps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

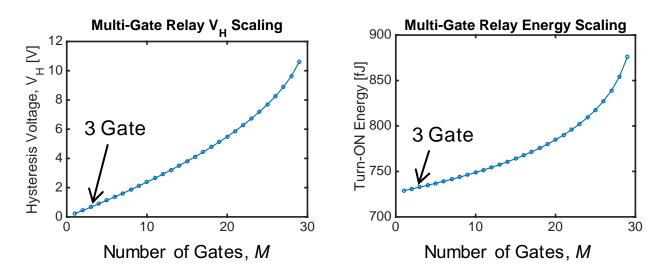

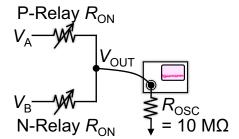

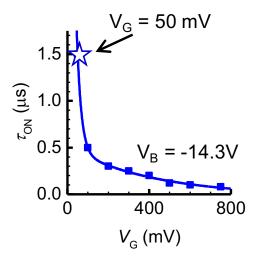

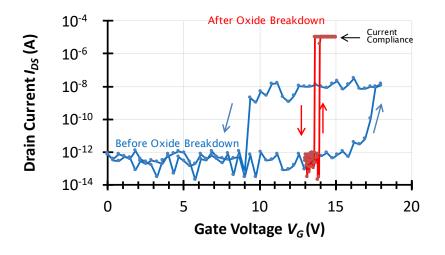

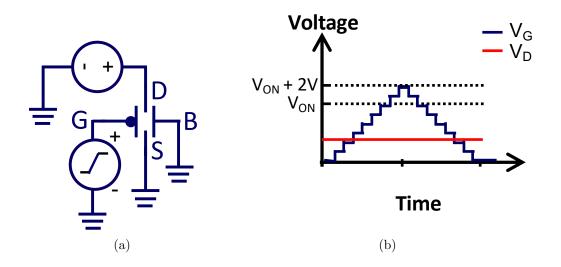

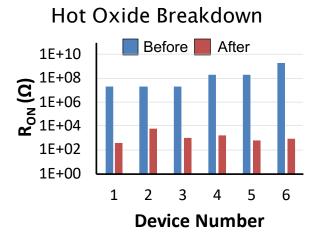

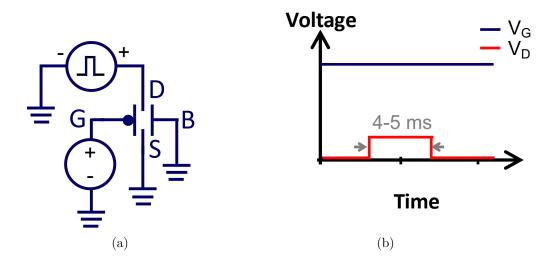

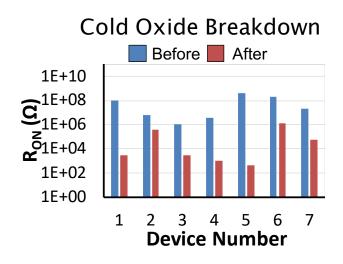

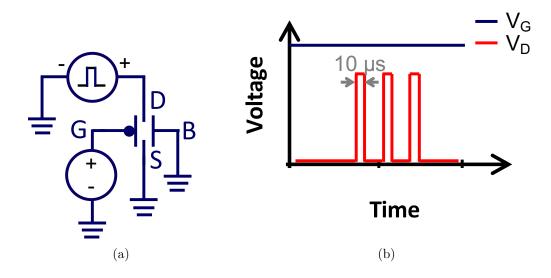

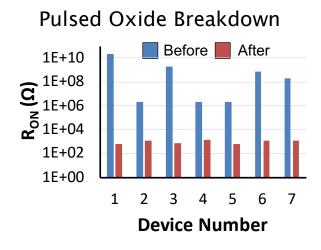

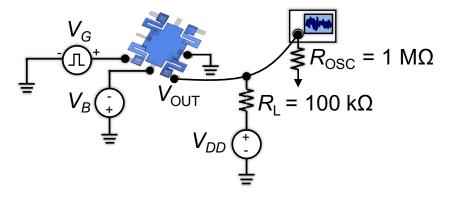

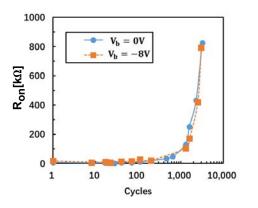

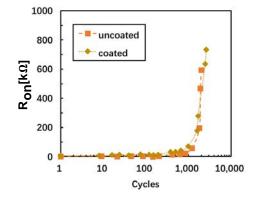

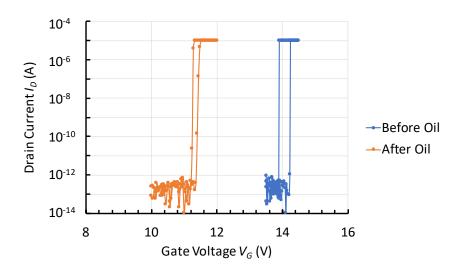

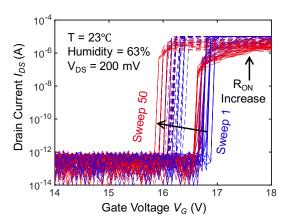

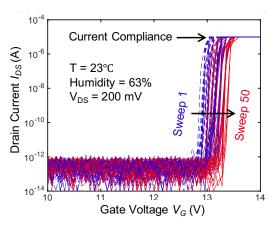

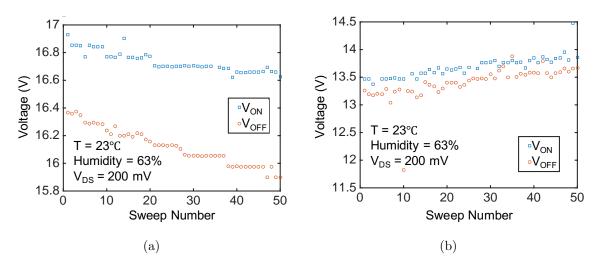

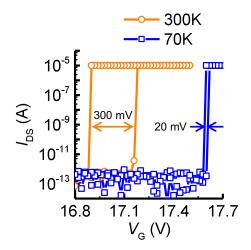

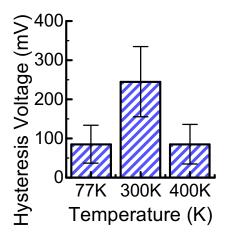

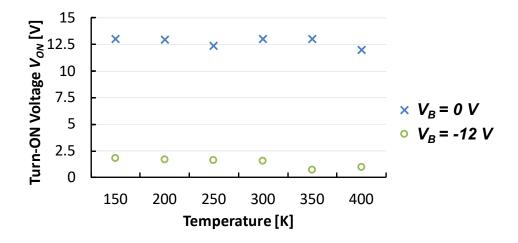

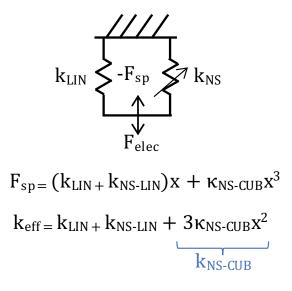

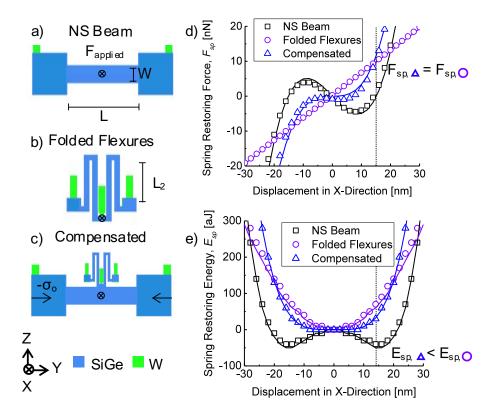

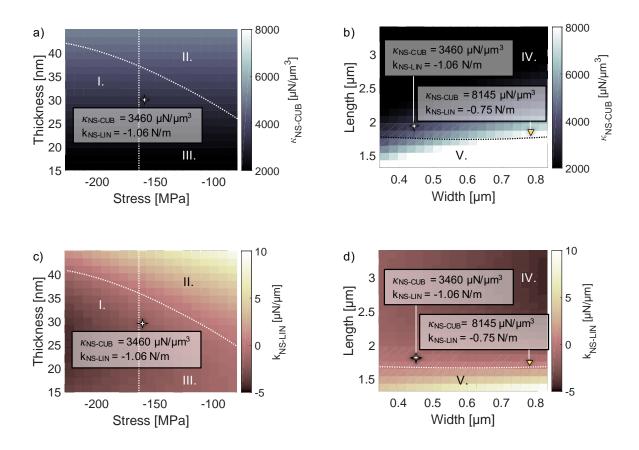

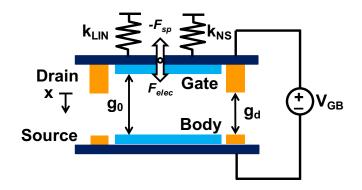

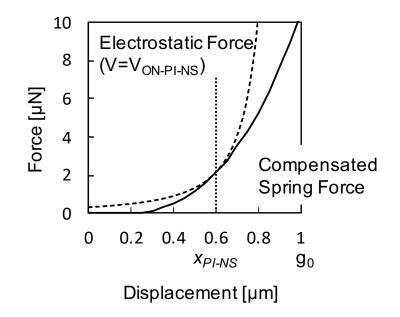

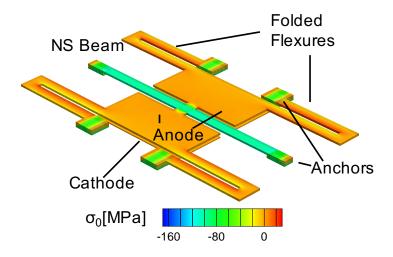

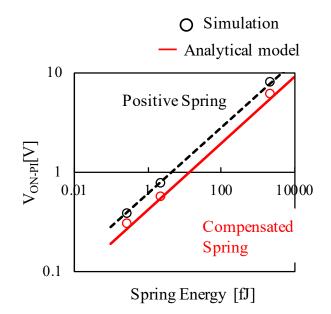

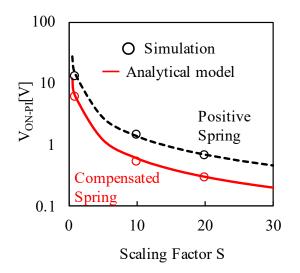

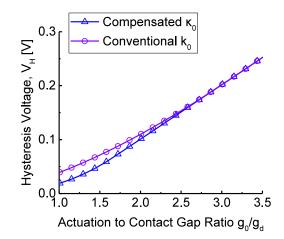

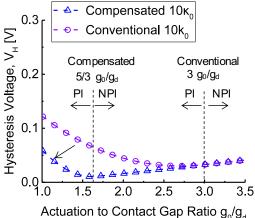

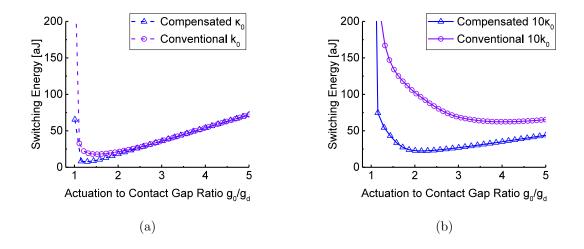

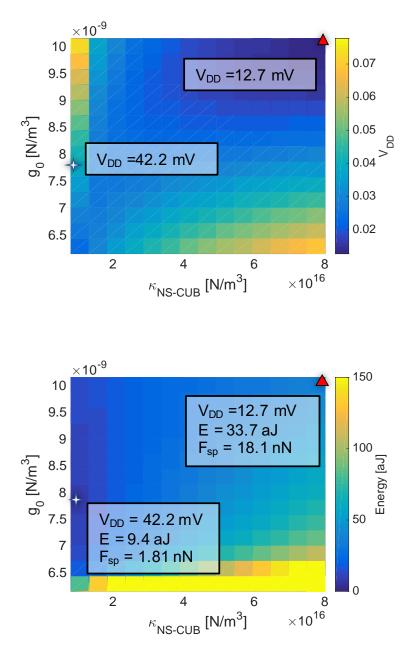

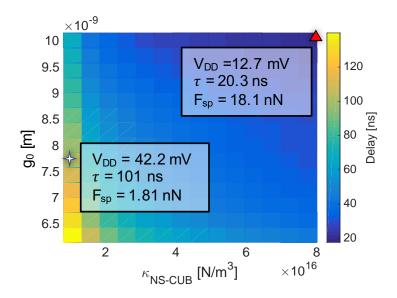

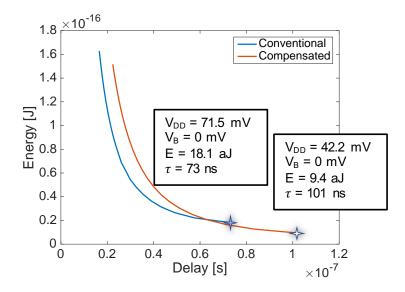

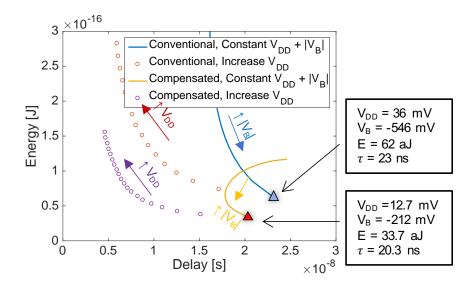

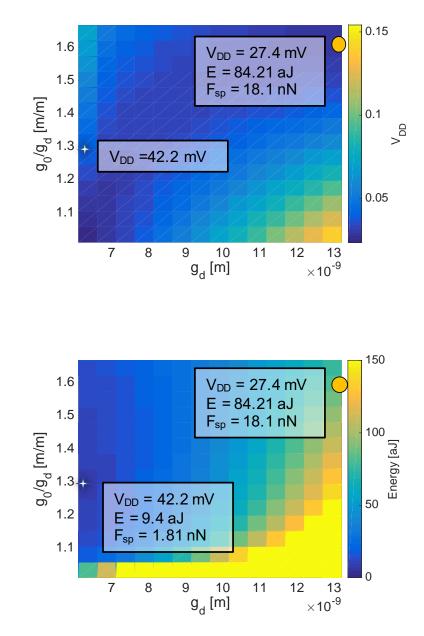

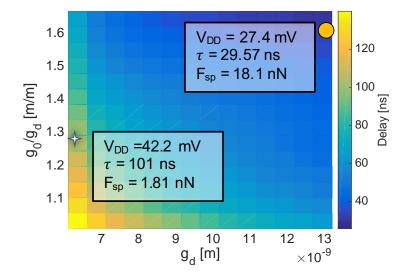

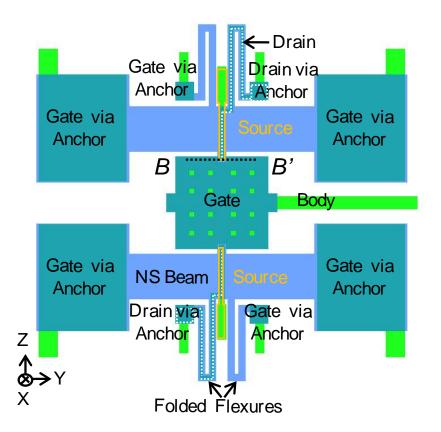

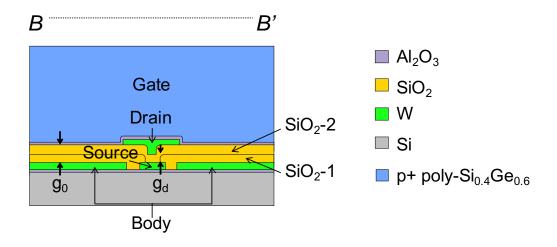

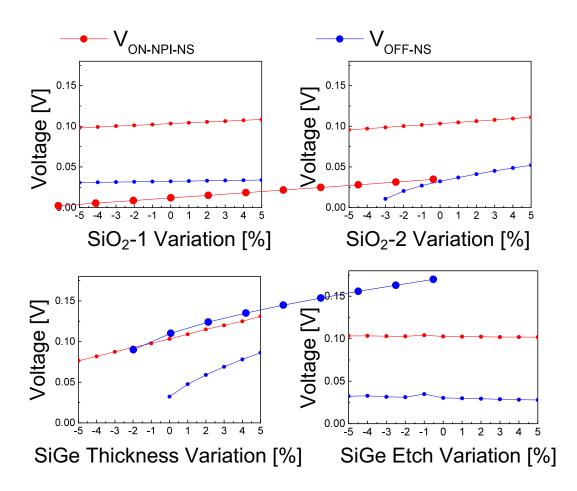

|      | for one relay. $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |