#### Interference-Resilient CMOS Receiver Front-Ends for Next Generation Radios

Sashank Krishnamurthy

#### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-231 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-231.html

December 1, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission. Interference-Resilient CMOS Receiver Front-Ends for Next Generation Radios

by

Sashank Krishnamurthy

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Borivoje Nikolić Professor Martin White

Fall 2020

Interference-Resilient CMOS Receiver Front-Ends for Next Generation Radios

Copyright 2020 by Sashank Krishnamurthy

#### Abstract

#### Interference-Resilient CMOS Receiver Front-Ends for Next Generation Radios

by

Sashank Krishnamurthy

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

In accordance with the trend of one generation of wireless mobile telecommunications technology every decade since the 1980s, the 2020s belong to 5G, the fifth generation. 5G is expected to provide a diverse range of services from enhanced mobile broadband at multigigabit per second, to supporting the massive Internet of Things revolution. While all the generations up to 4G used the frequency spectrum below 3GHz, 5G is expected to support communication on a wide range of spectrum, ranging from low-bands from 0.6-6GHz and mm-wave bands greater than 24GHz. Forecasts of hundreds of billions of connected devices by 2030 mandate the need for circuit-level techniques to mitigate the increasing interference that comes with this proliferating number of devices. To this end, we investigate techniques to make highly linear, interference resilient CMOS radio receiver front ends for three different application thrusts: sub-mW IoT applications, sub-6GHz 5G applications and mm-wave digital beamforming applications.

The need to operate radios connected to the IoT off tiny coil cell batteries has driven the recent research on sub-mW radio receivers. While existing work has focused on improving sensitivity of the receivers in a power efficient manner, there has been little focus on making them interference resilient. In the first part of this dissertation, we demonstrate a 2.4GHz radio receiver with 10x better interference resilience than the state-of-the-art sub-mW radios in the 2.4GHz ISM band, without compromising much on the sensitivity. We present a proof-of-concept integrated circuit in 28nm bulk-CMOS process and present the in-silicon results.

The ever-increasing number of bands with the advent of sub-6GHz 5G calls for high linearity receiver front-ends, with extremely high tolerance for blockers, both in close-in channels and far-out channels. Current solutions in mobile phones involve the use of multiple SAW and FBAR filters for different bands, making them extremely bulky. The re-discovery of N-path filters, with their impedance translational property, provides a path to SAW-less receivers. In the second part of the dissertation, we demonstrate enhanced N-path filter based receivers, achieving 40dB/decade, 60dB/decade and 80dB/decade RF selectivity. Techniques

to synthesize higher order driving point impedances, including the first ever known synthesis of a third order driving point impedance, are presented. Coupled with distortion cancellation techniques, record performance is achieved with respect to close-in blocker resilience. Experimental results from three separate integrated circuit prototypes in 28nm bulk CMOS confirm the benefits of our techniques.

Millimeter-wave massive MIMO arrays are expected to be an enabler of 5G. To this end, it is desirable to have digital beam-forming arrays with high spatial flexibility. This calls for highly linear RF front-ends to cope with in-band interferers. In the last part of the dissertation, we present a 10-35GHz passive mixer-first receiver for use in digital beamforming arrays. Circuit techniques are proposed to enhance the linearity of such receivers, both at baseband and the RF mixer switches. Experimental results from an integrated circuit prototype in 28nm bulk CMOS demonstrate record in-band linearity at these frequencies.

# Contents

| Contents |                                                                                                                                                                                                  | i                                                                                  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| Li       | List of Figures                                                                                                                                                                                  |                                                                                    |  |

| Li       | ist of Tables                                                                                                                                                                                    | ix                                                                                 |  |

| 1        | Introduction                                                                                                                                                                                     | 1                                                                                  |  |

| 2        | Sub-mW Interference-Resilient Receivers for IoT Applications2.1Introduction2.2Receiver Architecture2.3Feedback and Filtering2.4Noise Figure and Linearity2.5Circuit Design2.6Measurement Results | 6<br>7<br>13<br>17<br>22<br>31                                                     |  |

| 3        | 2.7 Conclusion                                                                                                                                                                                   | 35<br><b>37</b>                                                                    |  |

|          | 3.1       Introduction                                                                                                                                                                           | 37<br>39<br>42<br>55<br>61                                                         |  |

| 4        | N-Path Filters with 60dB/decade RF selectivity4.14.1Introduction4.2Impedance Synthesis4.3Circuit Design4.4Measurement4.5Conclusion                                                               | <ul> <li>63</li> <li>63</li> <li>64</li> <li>67</li> <li>68</li> <li>72</li> </ul> |  |

| 5        | N-Path Filters with Distortion Cancellation, Achieving $80 dB/decade RF$ selectivity                                                                                                             | <b>74</b>                                                                          |  |

|    | 5.1                                                                          | Introduction                                                   | 74        |

|----|------------------------------------------------------------------------------|----------------------------------------------------------------|-----------|

|    | 5.2                                                                          | Architecture                                                   | 75        |

|    | 5.3                                                                          | Distortion Cancellation                                        | 77        |

|    | 5.4                                                                          | Measurement                                                    | 80        |

|    | 5.5                                                                          | Conclusion                                                     | 82        |

| 6  | Desi                                                                         | gn of High Linearity Mixer-First Receivers for mm-wave Digital |           |

|    |                                                                              | IO Arrays                                                      | <b>85</b> |

|    | 6.1                                                                          | Introduction                                                   | 85        |

|    | 6.2                                                                          | Architecture and Circuit Design                                | 87        |

|    | 6.3                                                                          | Measurement Results                                            | 106       |

|    | 6.4                                                                          | Conclusion                                                     | 112       |

| 7  | Cone                                                                         | clusions and Future Work                                       | 115       |

|    | 7.1                                                                          | sub-mW IoT applications                                        | 115       |

|    |                                                                              | sub-6GHz 5G applications                                       | 115       |

|    | 7.3                                                                          | Mm-wave digital MIMO applications                              | 117       |

| Bi | bliog                                                                        | raphy                                                          | 118       |

| A  | A Analysis of Impedance Matching in Receivers with Translational Feedback126 |                                                                |           |

| В  | Harr                                                                         | nonic Folding of the Common-Gate LNA's Noise                   | 132       |

# List of Figures

| $1.1 \\ 1.2$ | $s_{21}$ transfer functions of some typical commercial SAW filters [1, 2] Schematic of an N-path filter based receiver illustrating impedance translation                                                                                | 2  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|              | property                                                                                                                                                                                                                                 | 3  |

| 1.3          | Digital beamforming receiver array for massive MIMO systems                                                                                                                                                                              | 4  |

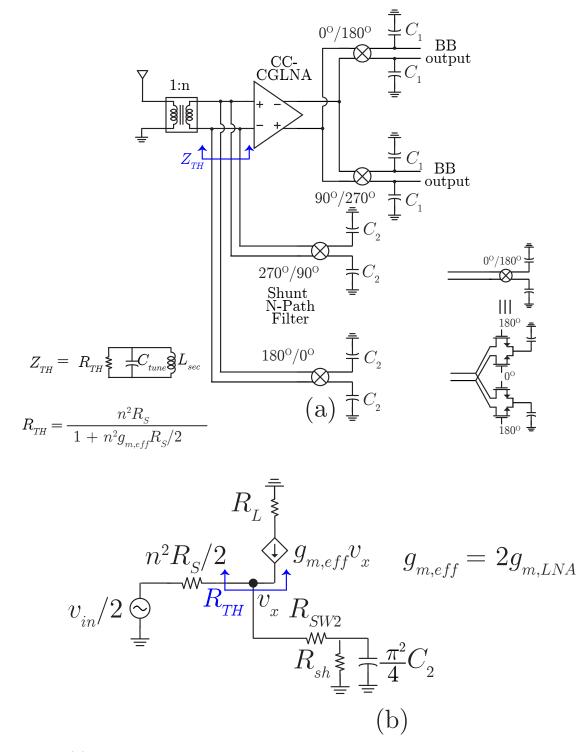

| 2.1          | (a) Simplified schematic of CC-CGLNA based receiver front-end with shunt N-<br>path filter, in conjunction with transformer-based input matching network. (b)<br>LTI equivalent half circuit to illustrate the matching at the LNA input | 9  |

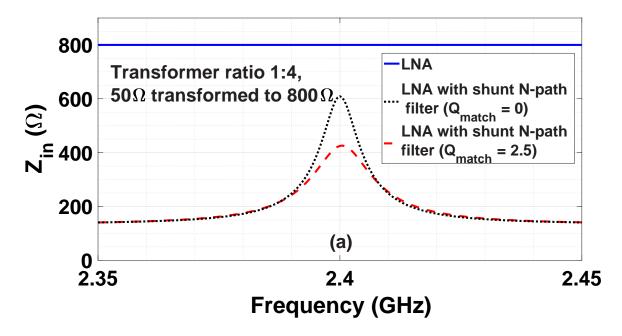

| 2.2          | Plot of input impedance v/s frequency for matching with broad-band LNA in                                                                                                                                                                | 5  |

|              | shunt with N-path filter for different $Q_{match}$ , for a fixed $R_{SW2} = 80\Omega$                                                                                                                                                    | 10 |

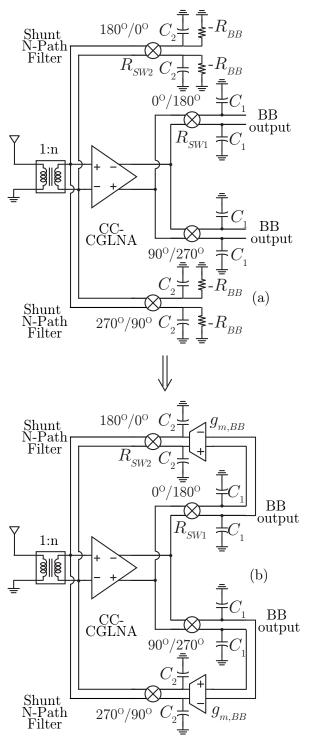

| 2.3          | Receiver front-end with translational positive feedback from baseband to RF to                                                                                                                                                           |    |

|              | boost input impedance                                                                                                                                                                                                                    | 12 |

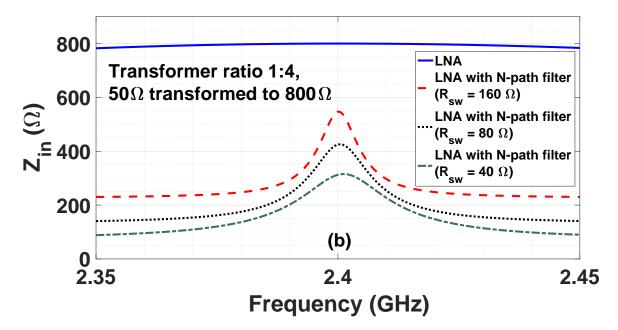

| 2.4          | Plot of input impedance v/s frequency for matching with broad-band LNA in                                                                                                                                                                |    |

| 05           | shunt with N-path filter for different $R_{SW2}$ , for a fixed $Q_{match} = 2.5$                                                                                                                                                         | 13 |

| 2.5          | LTI equivalent half-circuit of the receiver at $\omega_{LO}$ for (a) Broadband approximation<br>for input matching network (b) Narrowband approximation for input matching                                                               |    |

|              | network.                                                                                                                                                                                                                                 | 14 |

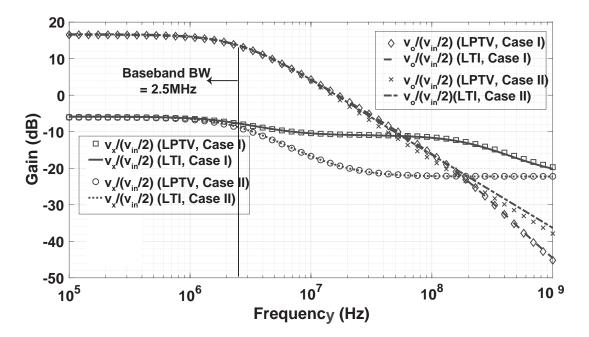

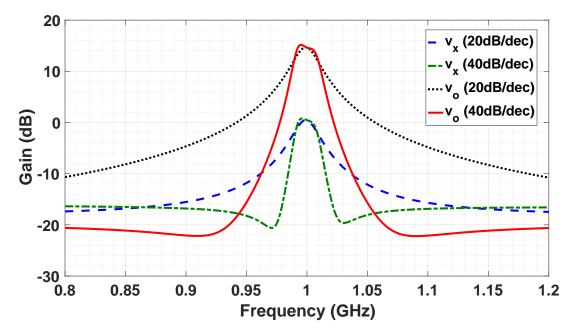

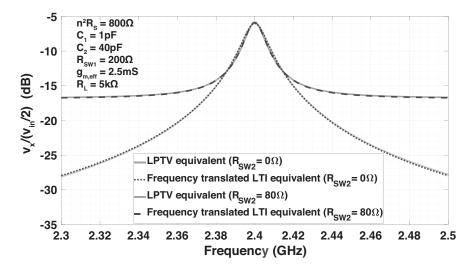

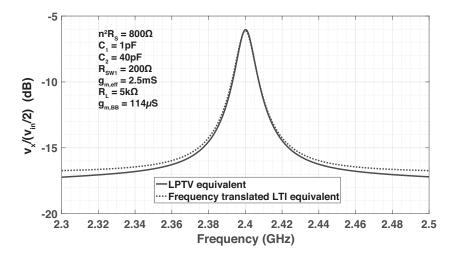

| 2.6          | Transfer functions to node $v_x$ and output node $v_o$ (see the half-circuit equivalent of Fig. 2.5) for different choice of capacitors $C_1$ , $C_2$ , the capacitors in the feed-                                                      | 14 |

|              | forward and the feedback N-path filters, respectively. Transfer functions from<br>a PAC analysis of the LPTV circuit, as well as frequency translated transfer                                                                           |    |

|              | functions based on the equation (2.4) are provided. Excellent agreement is seen                                                                                                                                                          |    |

|              | between the LPTV simulation and the results from the LTI model                                                                                                                                                                           | 16 |

| 2.7          | Noise factor due to the transistor in the common-gate LNA (other noise sources                                                                                                                                                           |    |

|              | are not considered). The degradation due to the shunt N-path filter is observed.                                                                                                                                                         | 18 |

| 2.8          | A mixer-first receiver front-end with a transformer input matching network, and                                                                                                                                                          |    |

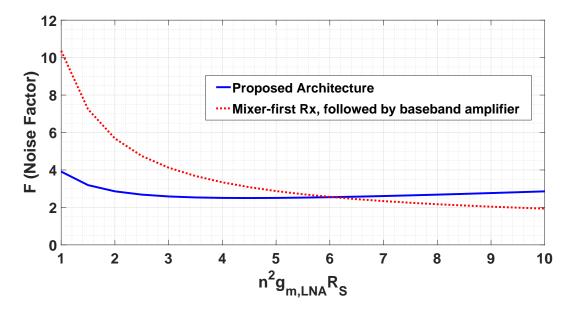

| 0.0          | a baseband low-noise amplifier.                                                                                                                                                                                                          | 19 |

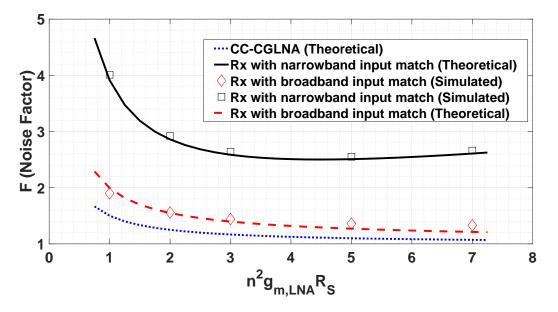

| 2.9          | Noise factor due to the transistor in the amplifier alone (other noise sources are<br>not considered). Our proposed receiver architecture (see Fig. 2.3) is compared                                                                     |    |

|              | against the mixer-first architecture of Fig. 2.8. The comparison is done such that                                                                                                                                                       |    |

|              | the overall amplifier power consumption is the same in both cases. In both cases,                                                                                                                                                        |    |

|              | the input matching network is assumed to be narrowband, with $R_{SW2}/(n^2R_S) = 0.1$ .                                                                                                                                                  | 20 |

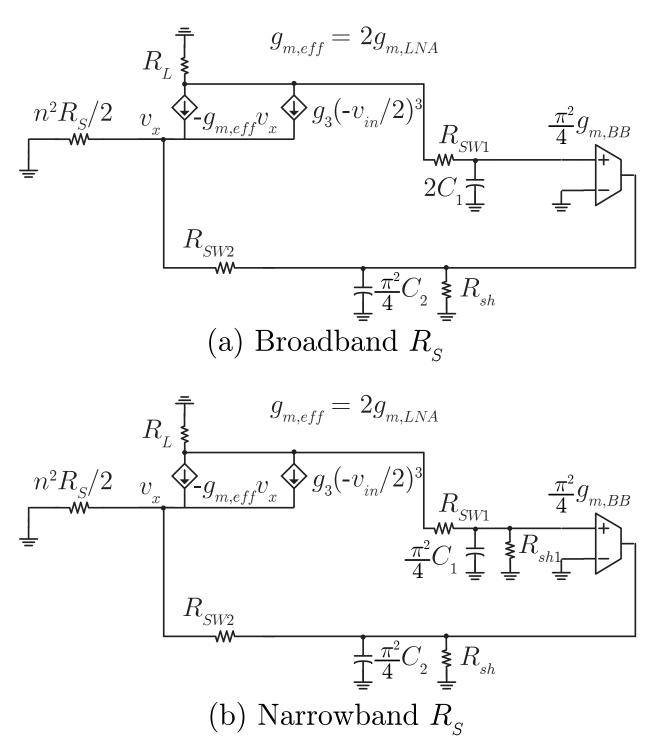

| 2.10         | Equivalent circuit to compute third order non-linearity.                                                                                                                                                                                 | 23 |

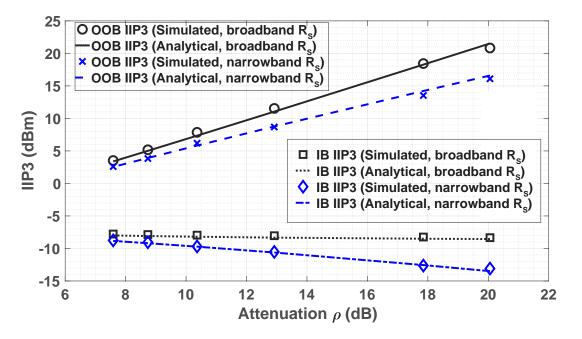

| 2.11     | Simulated plot of in-band and far-out out-of-band IIP3 for different values of                 |     |

|----------|------------------------------------------------------------------------------------------------|-----|

|          | $R_{SW2}$ . IIP3 is plotted against the far-out OOB attenuation $\rho$ (in dB), as computed    | 0.4 |

| 0.10     | in equation (2.5). The plot is for a transformer with electrical turns ratio $n$ of 3.3.       | 24  |

| 2.12     | 1                                                                                              | ٥٢  |

| 0.10     | switch resistance $R_{SW2} = 53\Omega$ , transformer electrical turns ratio <i>n</i> of 3.3    | 25  |

| 2.13     |                                                                                                | 25  |

|          | Layout of the transformer                                                                      | 26  |

|          | Simulated inductance and Q of the primary and secondary of the transformer .                   | 26  |

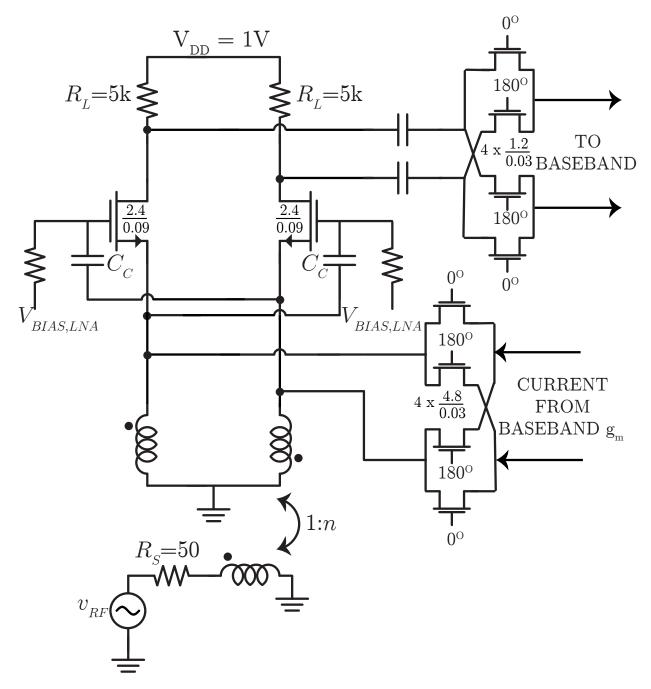

|          | CCC-CG-LNA and passive mixers, I-path shown                                                    | 28  |

| 2.17     |                                                                                                | 30  |

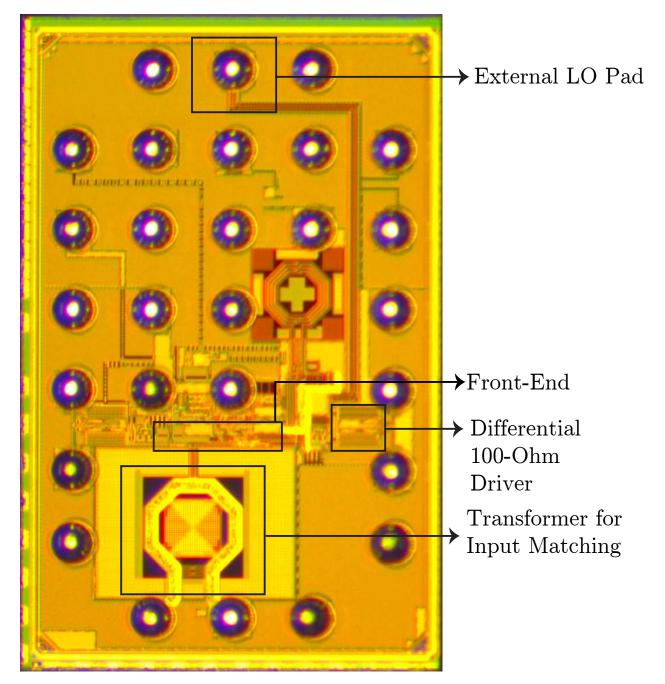

|          | Chip Micrograph                                                                                | 31  |

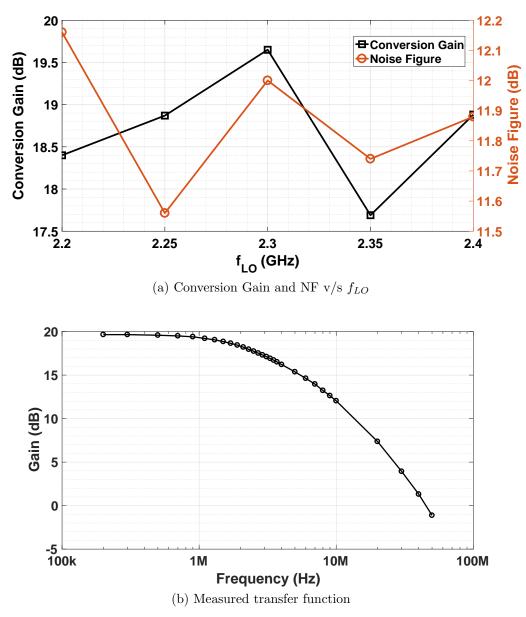

|          | Measured Gain, Noise Figure and Transfer function                                              | 32  |

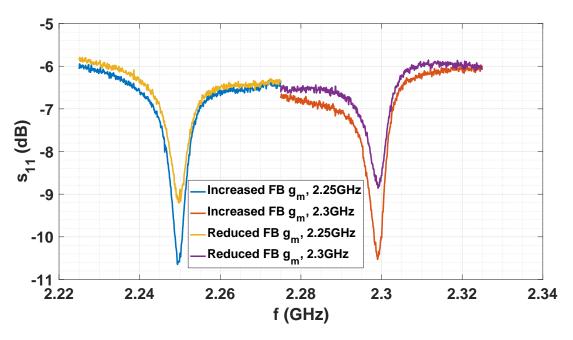

|          | Effect of positive FB on matching from $s_{11}$                                                | 33  |

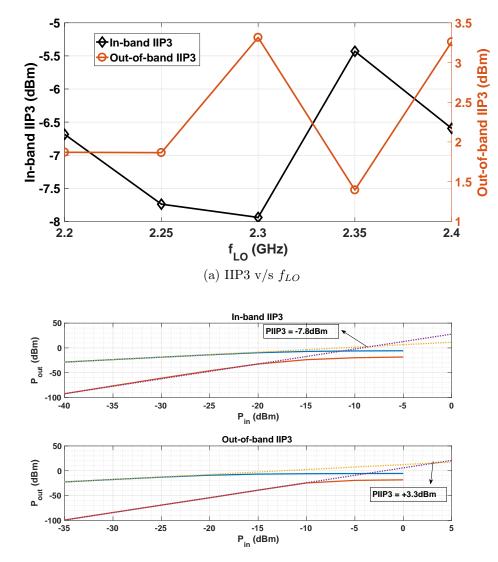

|          | Measured IIP3 v/s $f_{LO}$ and measured IM3 v/s input power $P_{in}$                           | 34  |

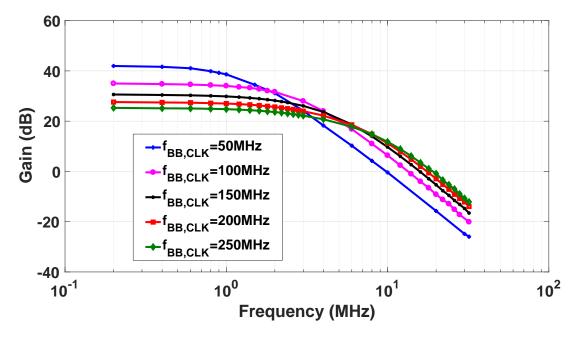

| 2.22     | Measured transfer function of baseband switched capacitor filter for different                 | ~~  |

|          | values of $f_{CLK}$                                                                            | 35  |

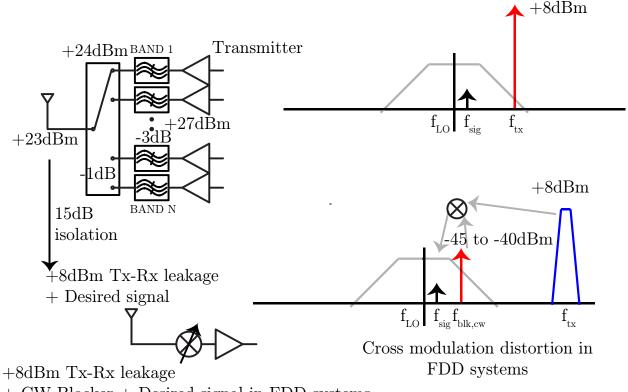

| 3.1      | System diagram showing need for stringent linearity due to transmitter leakage                 |     |

| 0.1      | to receiver.                                                                                   | 38  |

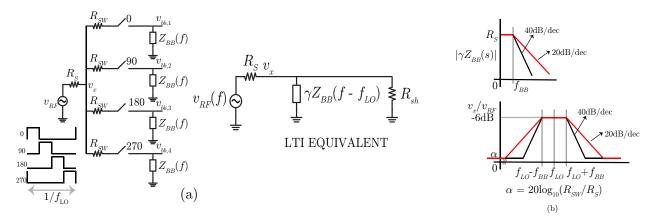

| 3.2      | (a) LTI equivalent of N-path filters at $f_{LO}$ (b) Impedance translation in N-path           | 00  |

| 0.2      | filters. $\ldots$                                                                              | 39  |

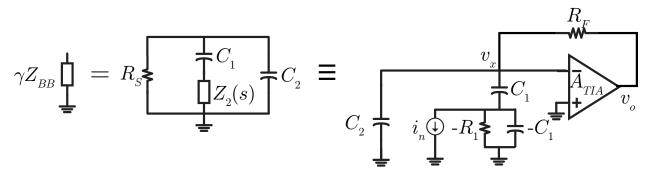

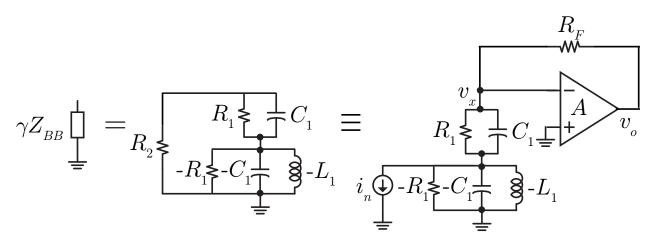

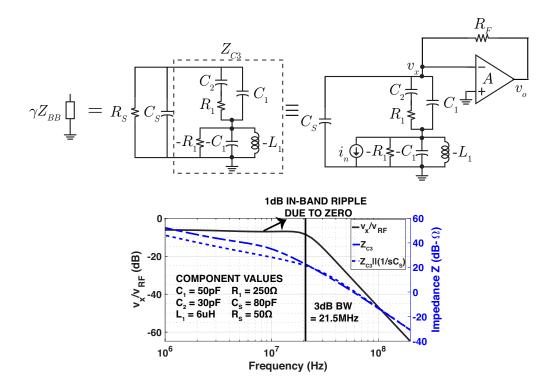

| 3.3      | Impedance with 40dB/dec. roll-off.                                                             | 41  |

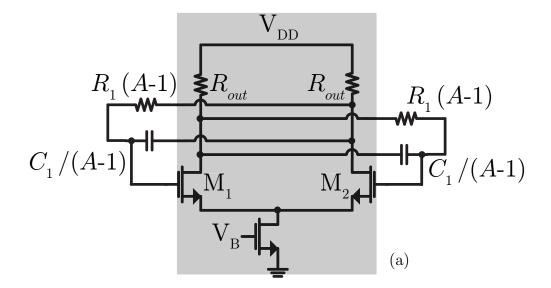

| 3.4      | (a) Cross-coupling resistance and capacitance across a differential pair to realize            | 11  |

| 0.1      | negative shunt <i>RC</i> . (b) Small-signal equivalent                                         | 43  |

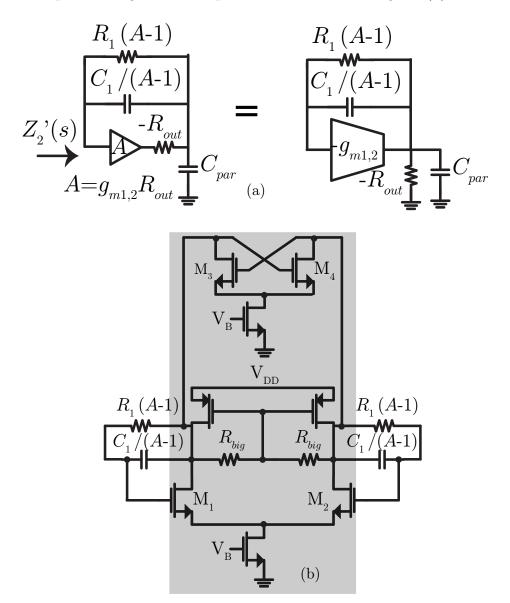

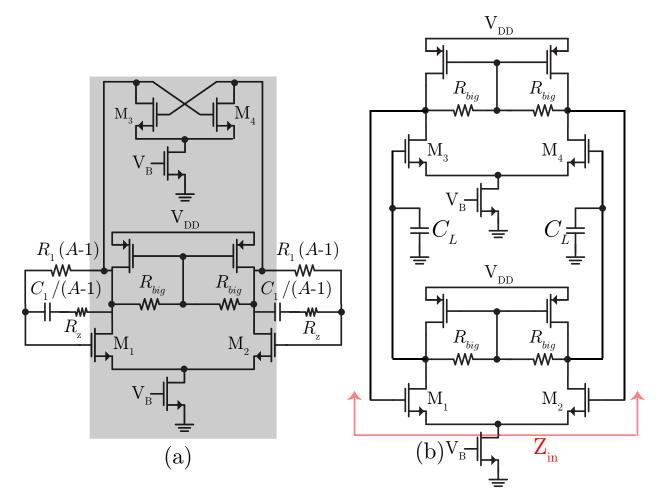

| 3.5      | (a) Small-signal equivalent of desired implementation. (b) Transistor level schematic          | 10  |

| 0.0      | of negative $RC$ implementation                                                                | 44  |

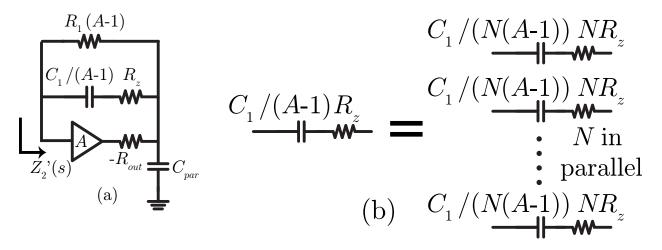

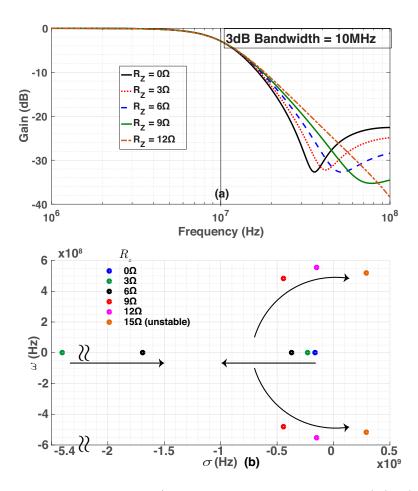

| 3.6      | (a) Series resistance $R_z$ to push the location of zeros further out. (b) Actual              |     |

| 0.0      | implementation.                                                                                | 45  |

| 3.7      | (a) Low-pass function $v_x/v_{RF}$ for different values of $R_z(\Omega)$ . (b) Root locus of   | 10  |

| 0.1      | non-dominant poles as $R_z(\Omega)$ varies                                                     | 47  |

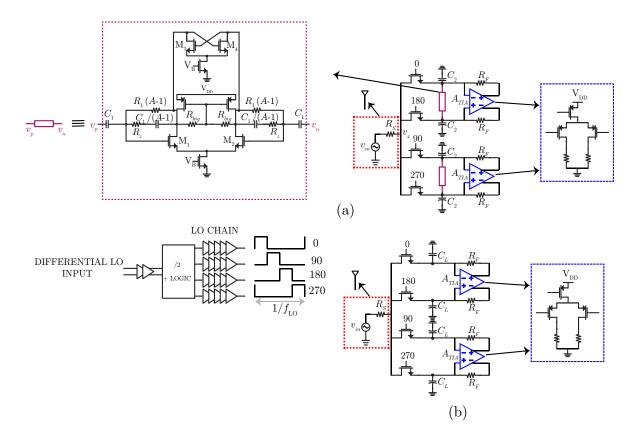

| 3.8      | (a) Block diagram summarizing the entire receiver front-end with "second-order"                |     |

| 0.0      | N-path filter, and the LO chain. (b) Receiver front-end with conventional N-path               |     |

|          | filter                                                                                         | 48  |

| 3.9      | Small-signal PAC transfer function to node $v_x$ (see Fig. 3.8(a)) and PXF transfer            | 10  |

| 0.0      | function to the output for conventional N-path filter and enhanced N-path filter.              | 49  |

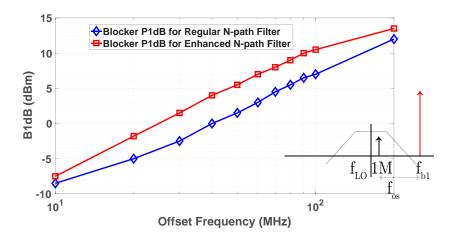

| 3.10     |                                                                                                | 10  |

| 0.10     | N-path filter and enhanced N-path filter                                                       | 50  |

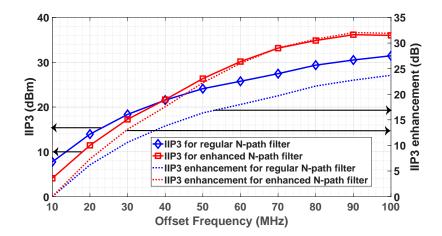

| 3.11     | Simulated out-of-band IIP3 as a function of tone offset frequency $f_{OS}$ for conven-         | 00  |

| J.11     | tional N-path filter and enhanced N-path filter                                                | 50  |

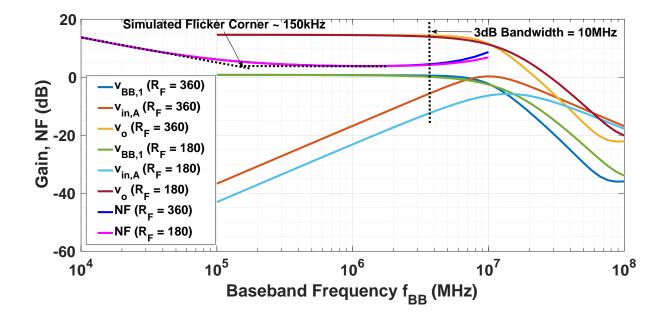

| 3.12     | Translated transfer function from input at RF to baseband node $v_{BB,1}$ , input              | 50  |

| <u>.</u> | of the Z-synthesizing amplifier $v_{in,A}$ , the output node $v_o$ and the noise figure.       |     |

|          | $R_F = 360\Omega$ corresponds to $Q = 1/\sqrt{2}$ , $R_F = 180\Omega$ corresponds to $Q = 1/2$ | 51  |

|          | -r $-r$ $-r$ $-r$ $-r$ $-r$ $-r$ $-r$                                                          | ~ - |

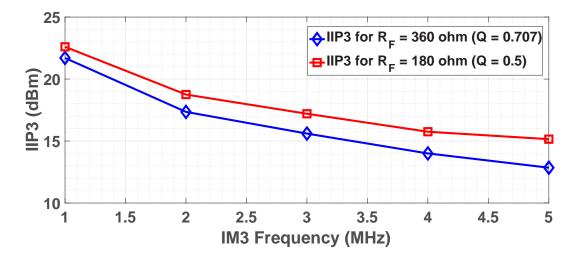

| 3.13  | Simulated out-of-band IIP3 at a tone offset of 50MHz as a function of the IM3 product frequency (MHz). The 2 plots are for the cases of a filter with $Q = 1/2$ |             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|       | and $Q = 1/\sqrt{2}$ .                                                                                                                                          | 52          |

| 3.14  | Z synthesized with lower power using a pre-amplifier                                                                                                            | 53          |

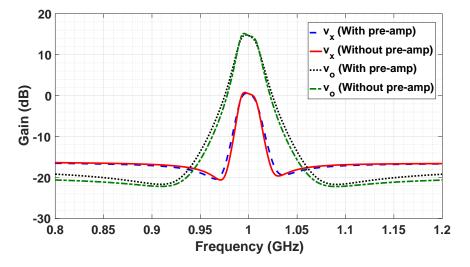

|       | Small-signal PAC transfer function to node $v_x$ and PXF transfer function to the                                                                               | 00          |

| 0.10  | output for enhanced N-path filter with and without pre-amplifier. $\ldots$                                                                                      | 54          |

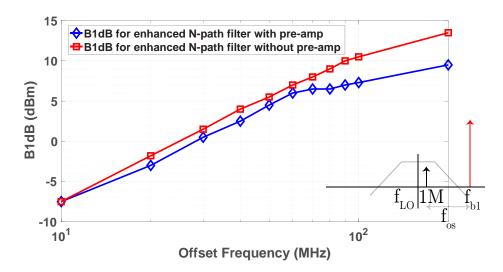

| 3.16  |                                                                                                                                                                 | 01          |

| 0.10  | and without pre-amp.                                                                                                                                            | 54          |

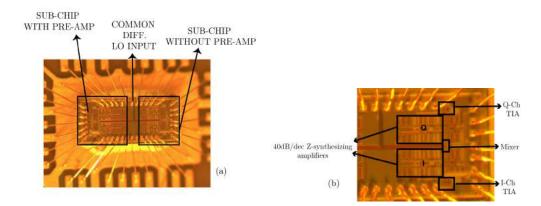

| 3.17  | (a) Die micro-graph of 2 sub-chip implementations, one with a pre-amplifier, one without. (b) Zoomed in version of die micro-graph of sub-chip without the      |             |

|       | pre-amplifier.                                                                                                                                                  | 56          |

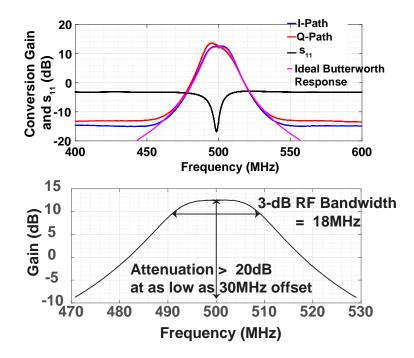

| 3.18  | Plots of measured $s_{11}$ , gain and zoomed-in gain without the pre-amp ( $f_{LO} =$                                                                           |             |

|       | 500MHz).                                                                                                                                                        | 56          |

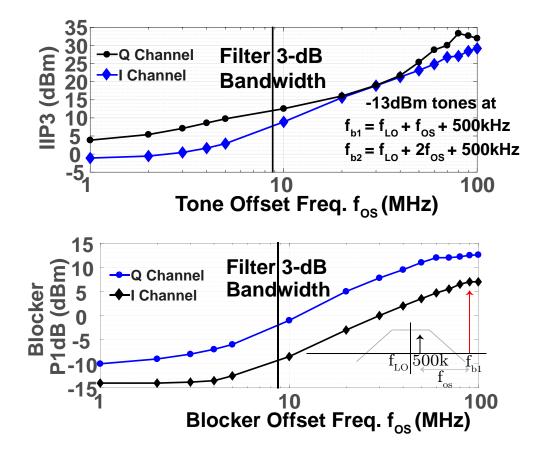

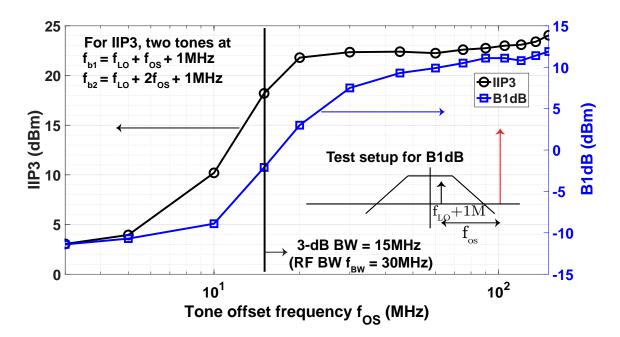

| 3.19  | Plots of IIP3 and Blocker P-1dB v/s offset frequency, without the pre-amp, as                                                                                   |             |

|       | measured from both I and Q channels ( $f_{LO} = 500 \text{MHz}$ )                                                                                               | 57          |

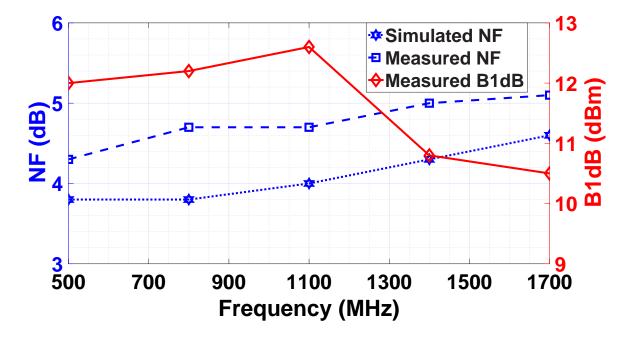

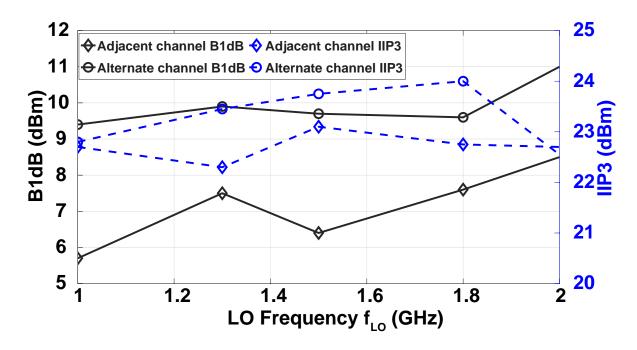

| 3.20  | Plot of simulated noise figure, measured noise figure and B1dB (at 60MHz offset)                                                                                |             |

|       | v/s LO frequency, without the pre-amp.                                                                                                                          | 58          |

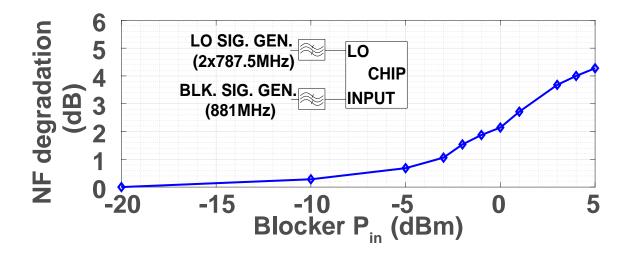

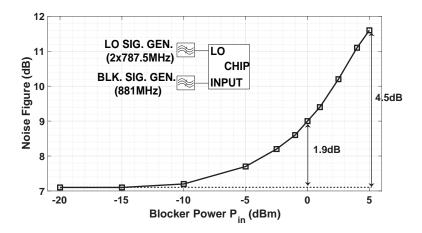

| 3.21  | Plot of blocker NF degradation v/s blocker $P_{in}$ , without the pre-amp ( $f_{LO} =$                                                                          | -           |

|       | 787.5MHz, $f_{blk} = 881$ MHz)                                                                                                                                  | 59          |

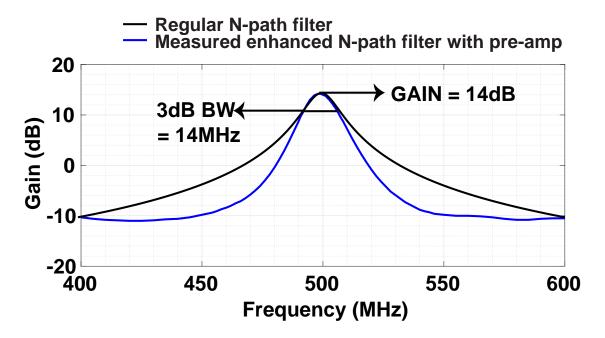

|       | Plot of measured gain for implementation with the pre-amplifier                                                                                                 | 59          |

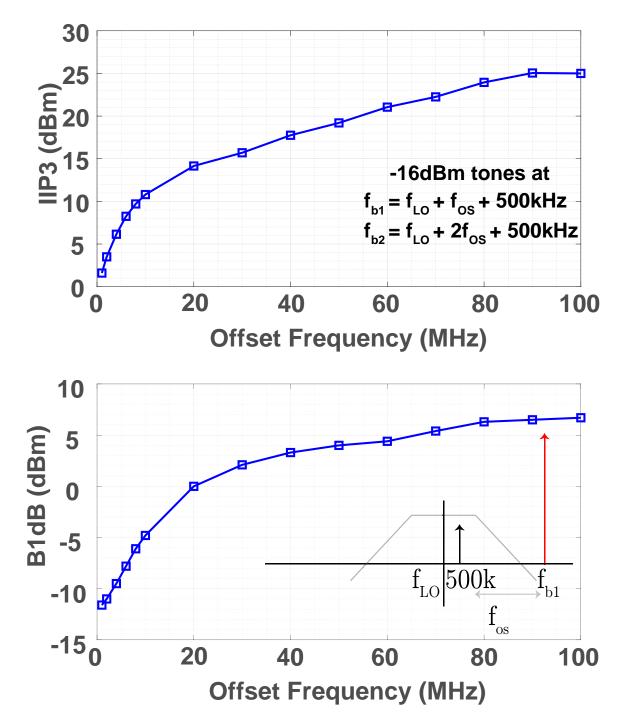

| 3.23  | Plots of IIP3 and Blocker P-1dB v/s offset frequency for implementation with                                                                                    |             |

|       | pre-amplifier ( $f_{LO} = 500 \text{MHz}$ ).                                                                                                                    | 60          |

| 4.1   | LTI equivalent of N-path filters at $f_{LO}$ , illustrating impedance translation in N-                                                                         |             |

|       | path filters.                                                                                                                                                   | 64          |

| 4.2   | Third order driving impedance.                                                                                                                                  | 65          |

| 4.3   | Driving point impedance with four poles and one zero. Also, representative sim-                                                                                 |             |

|       | ulation plots for the "third" order capacitive impedances and transfer function                                                                                 |             |

|       | from $v_{RF}$ to $v_x$ (see Fig. 4.1) are shown for the component values indicated in                                                                           |             |

|       | the figure.                                                                                                                                                     | 66          |

| 4.4   | (a) Amplifier to realize negative RC. (b) "Negative gyrator" to realize negative                                                                                | <b>a -</b>  |

|       | inductance                                                                                                                                                      | 67          |

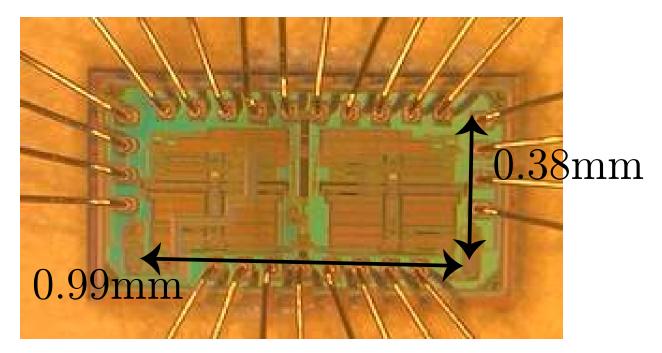

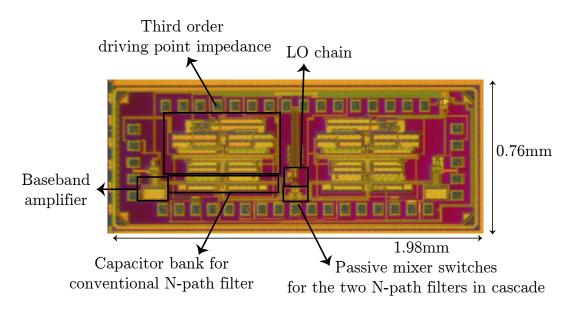

| 4.5   | Die micrograph.                                                                                                                                                 | 68          |

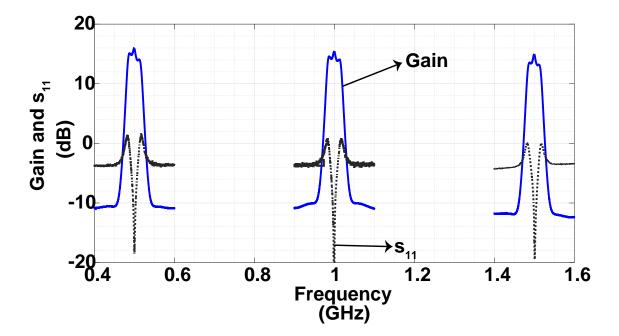

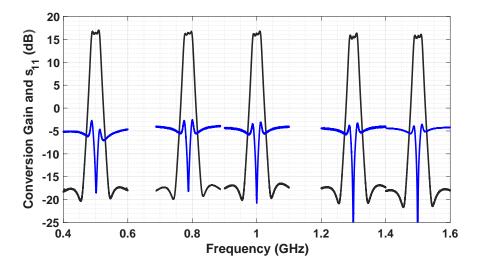

| 4.6   | Measured $s_{11}$ , gain for three different LO frequencies                                                                                                     | 69          |

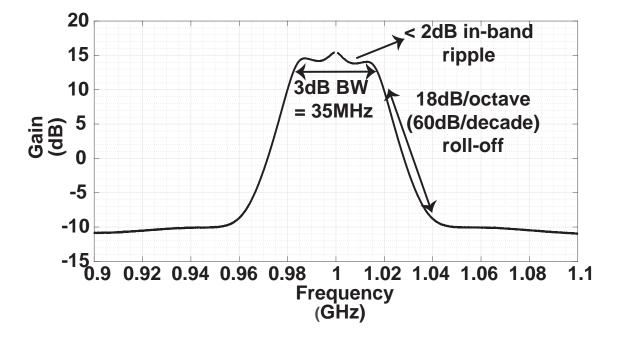

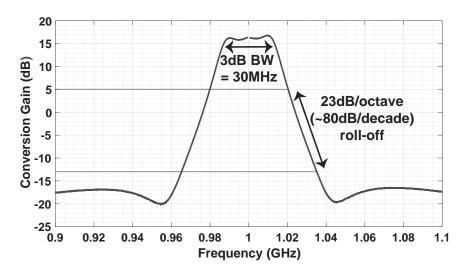

| 4.7   | Zoomed-in gain for $f_{LO} = 1$ GHz.                                                                                                                            | 69          |

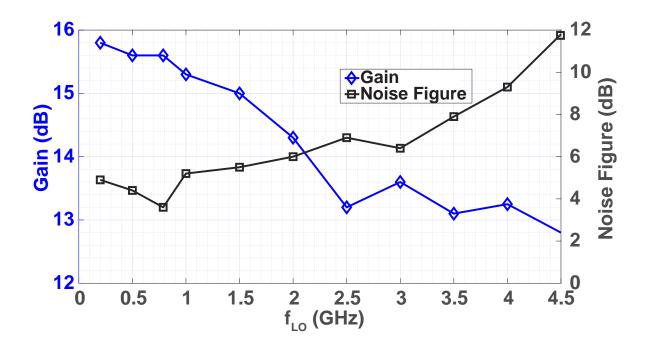

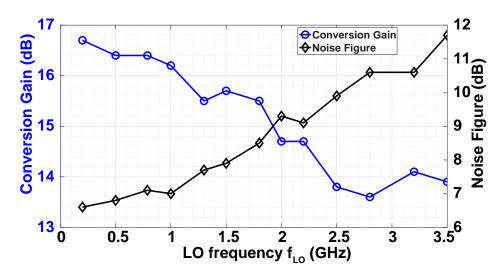

| 4.8   | Measured gain, NF versus $f_{LO}$ .                                                                                                                             | 70          |

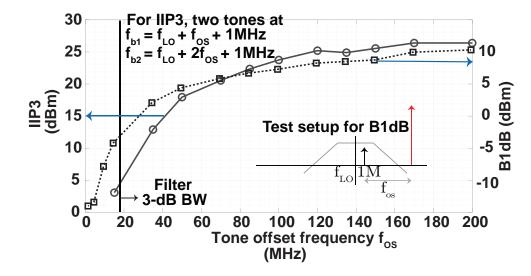

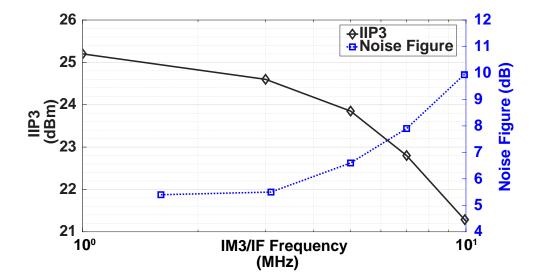

| 4.9   | Measured IIP3 and B1dB v/s offset frequency for $f_{LO} = 1$ GHz.                                                                                               | 71          |

| 4.10  | Measured out-of-band IIP3 at a tone offset of 120MHz as a function of the IM3                                                                                   | <b>17</b> 1 |

| 1 1 1 | product frequency, and measured NF as a function of IF frequency for $f_{LO} = 1$ GHz.                                                                          | 71          |

| 4.11  | Measured in-band blocker noise figure for $f_{LO} = 787.5$ MHz                                                                                                  | 72          |

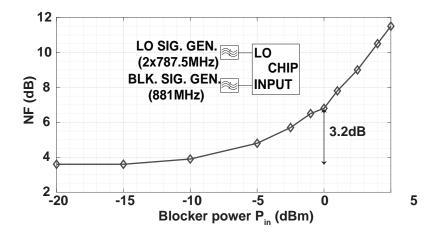

| 5.1   | Passive cascade of N-path filters similar to [3, 4].                                                                                                            | 75          |

v

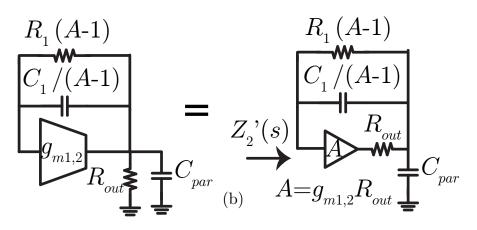

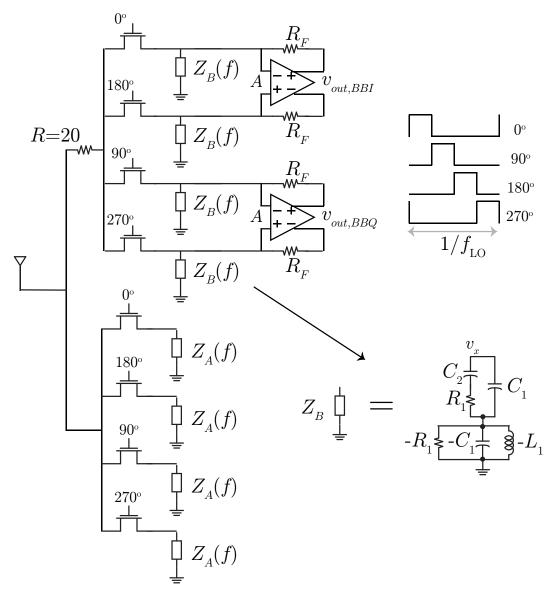

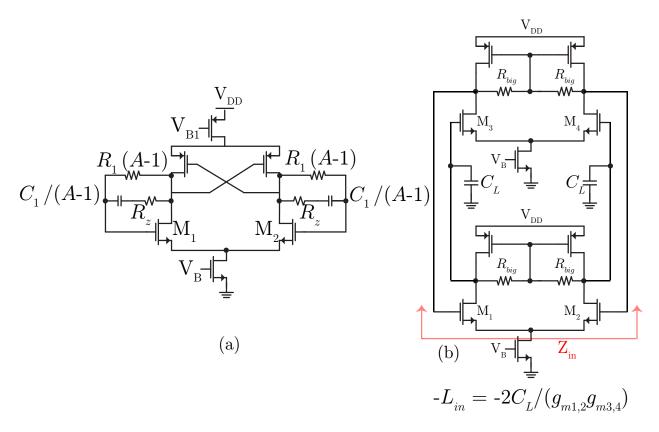

| 5.2  | (a) Amplifier to realize negative RC. (b) "Negative gyrator" to realize negative inductance                                                                                                                                                                                                                                                                                                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

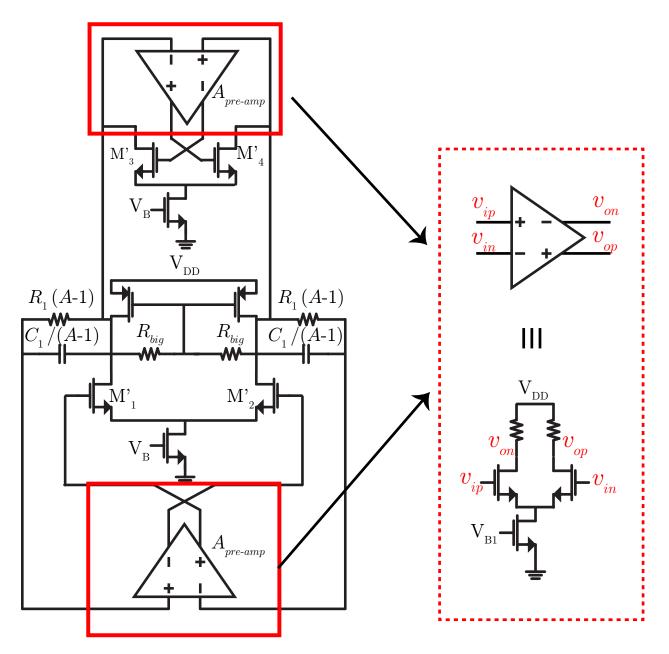

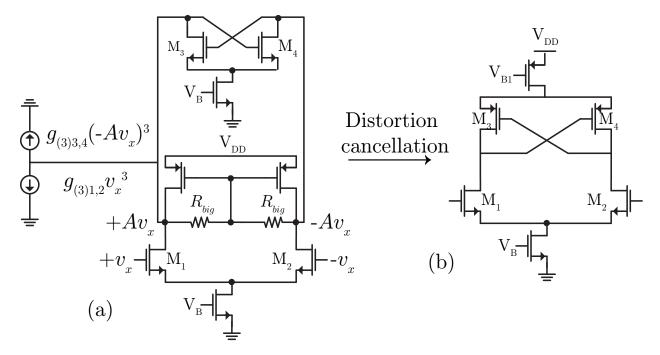

| 5.3  | (a) Amplifier to realize negative RC in [5, 6]. (b) Proposed Amplifier used to realize negative RC, with distortion cancellation                                                                                                                                                                                                                                                                                                        |

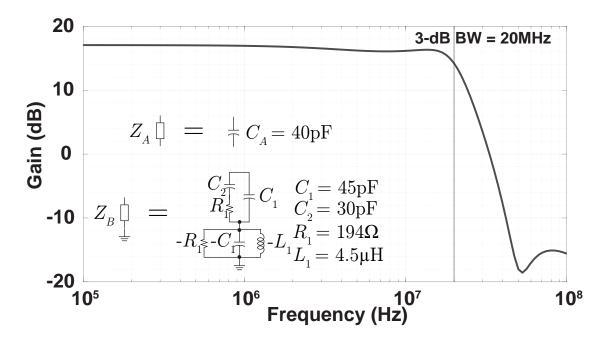

| 5.4  | Representative simulation plots for the transfer function from the RF input to<br>the baseband output (see Fig. 5.1) are shown for the component values indicated<br>in the figure. For the amplifier used to synthesize the negative RC impedance,<br>the value of $g_{m1,2} = 164$ mS and $g_{m3,4} = 104$ mS. The value of $A = 1.58$                                                                                                |

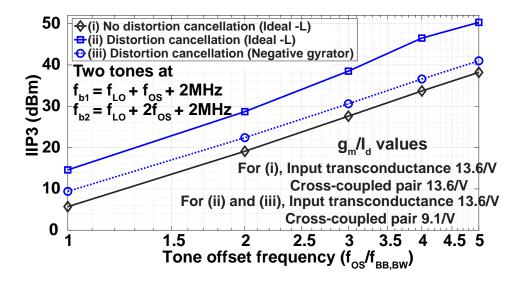

| 5.5  | Plot showing simulated IIP3 as a function of tone offset frequency (represented<br>as a fraction of the baseband bandwidth), for the following cases: (i) Without<br>distortion cancellation and ideal negative inductance, (ii) With distortion can-<br>cellation in the negative RC amplifier and ideal negative inductance, (iii) With<br>distortion cancellation in the negative RC amplifier, but not in the "negative"<br>gyrator |

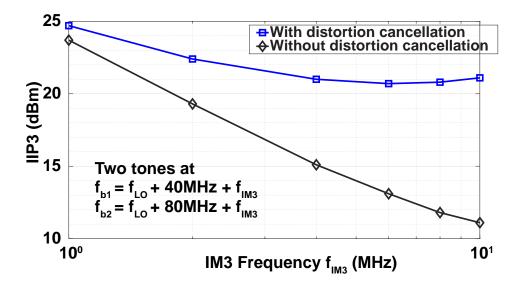

| 5.6  | Plot showing simulated IIP3 as a function of in-band IM3 frequency (for a fixed tone-offset frequency of 40MHz), with and without distortion cancellation for the negative RC amplifier. In both cases, the simulation is with the actual "negative gyrator" circuit.                                                                                                                                                                   |

| 5.7  | Die micrograph. The chip occupies an area of $1.5 \text{mm}^2$                                                                                                                                                                                                                                                                                                                                                                          |

| 5.8  | Measured $s_{11}$ , gain for three different LO frequencies                                                                                                                                                                                                                                                                                                                                                                             |

| 5.9  | Zoomed-in gain for $f_{LO} = 1$ GHz. 81                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.10 | Measured gain, NF versus $f_{LO}$                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | Measured IIP3 and B1dB versus offset frequency for $f_{LO} = 1$ GHz                                                                                                                                                                                                                                                                                                                                                                     |

|      | Measured adjacent and alternate channel B1dB and IIP3 versus $f_{LO}$ 83                                                                                                                                                                                                                                                                                                                                                                |

|      | Measured in-band blocker noise figure for $f_{LO} = 787.5$ MHz                                                                                                                                                                                                                                                                                                                                                                          |

| 6.1  | Conventional N-path filter and its LTI equivalent.                                                                                                                                                                                                                                                                                                                                                                                      |

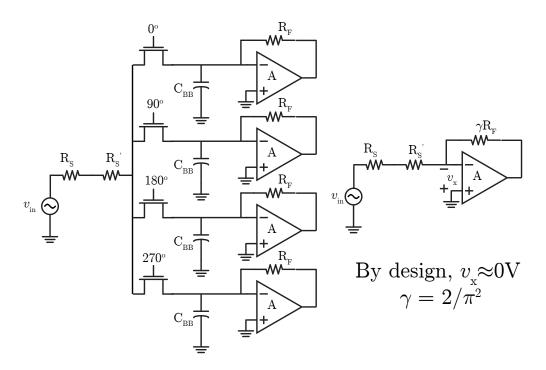

| 6.2  | N-path filter exploiting feedback linearization and its LTI equivalent 89                                                                                                                                                                                                                                                                                                                                                               |

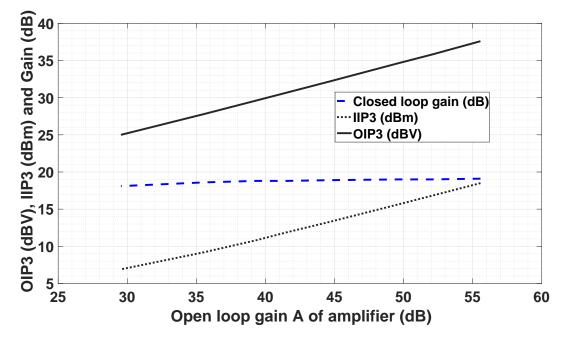

| 6.3  | Simulated in-band IIP3, differential OIP3 and closed loop differential gain of                                                                                                                                                                                                                                                                                                                                                          |

|      | proposed architecture versus amplifier open loop gain $A$                                                                                                                                                                                                                                                                                                                                                                               |

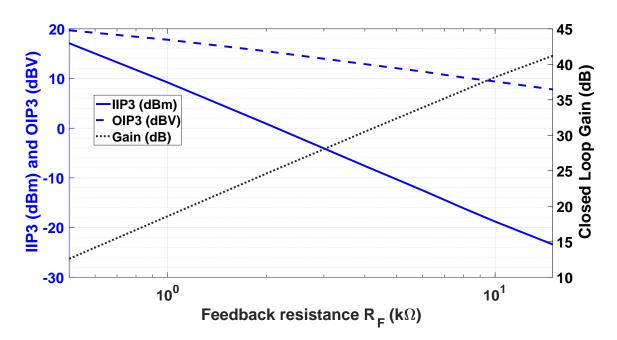

| 6.4  | Simulated in-band IIP3, differential OIP3 and closed loop differential gain of proposed architecture versus $R_F$ , for amplifier open loop gain A equal to 60 92                                                                                                                                                                                                                                                                       |

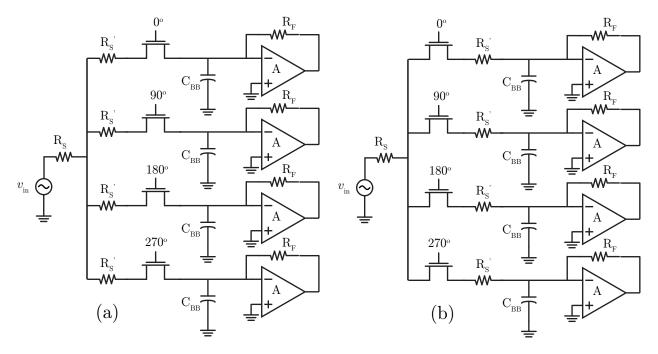

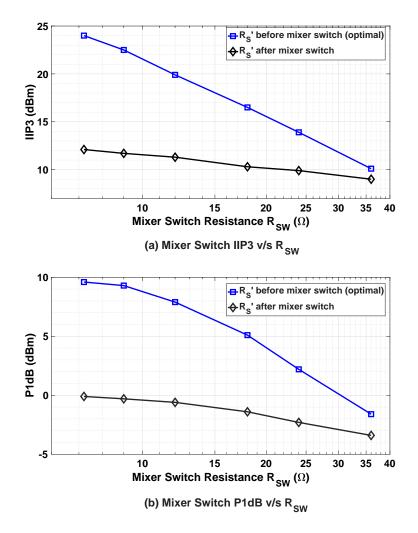

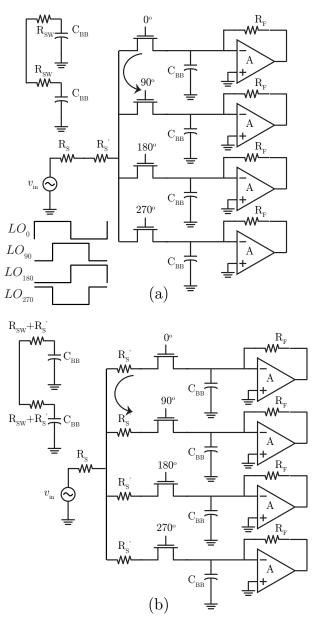

| 6.5  | Two variants of proposed N-path filter architecture with series resistor $R'_S$ (a) before the mixer switches (b) after the mixer switches                                                                                                                                                                                                                                                                                              |

| 6.6  | Simulated IIP3 and P1dB ( $f_{LO} = 20$ GHz) of mixer switches for the two circuits<br>shown in Figs. 6.5(a) and (b). The series resistor is placed before and after the<br>mixer switch, in the two cases. The baseband is assumed to be perfectly linear<br>for this simulation                                                                                                                                                       |

vi

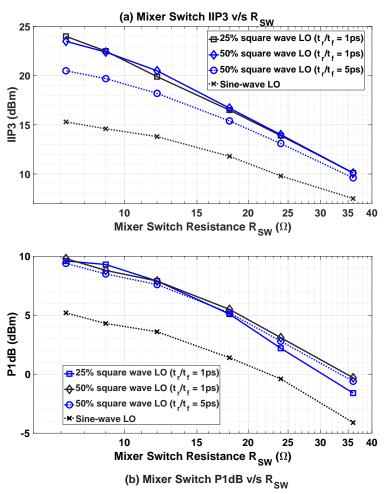

| 6.7  | Simulated IIP3 and P1dB ( $f_{LO} = 20$ GHz) of mixer switches for the circuit                                                                                                                                             |            |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | shown in Fig. 6.5(a), for different LO drives. The different cases are 25% non-                                                                                                                                            |            |

|      | overlapping LO, 50% overlapping LO and pseudo non-overlapping sine wave drive.                                                                                                                                             |            |

|      | The LO swings from 0 to $V_{DD} = 1.2$ V in each case. The baseband is assumed to                                                                                                                                          |            |

|      | be perfectly linear for this simulation                                                                                                                                                                                    | 96         |

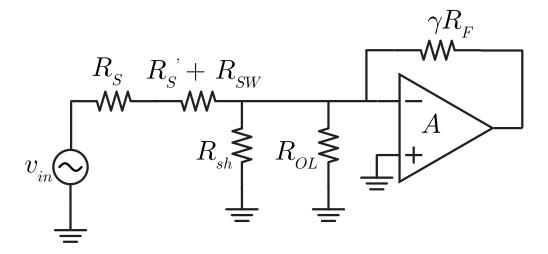

| 6.8  | LTI equivalent circuit of the circuits in Figs. 6.1 and 6.10, showing shunt re-                                                                                                                                            |            |

|      | radiation resistance $R_{sh}$ and overlap resistance $R_{OL}$ . The values of $R_{OL}$ are                                                                                                                                 |            |

|      | different for each of the circuits, depending on the nature of the LO driving the                                                                                                                                          |            |

|      | mixers                                                                                                                                                                                                                     | 98         |

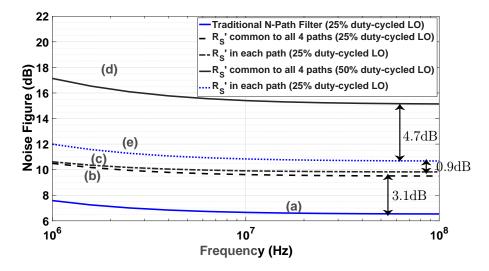

| 6.9  | Simulated noise figure $(f_{LO} = 20 \text{GHz})$ for the following cases (a) The circuit in                                                                                                                               |            |

|      | Fig. 6.1 driven by non-overlapping 25% duty-cycled LO. (b) The circuit in Fig.                                                                                                                                             |            |

|      | 6.10(a) driven by non-overlapping 25% duty-cycled LO. (c) The circuit in Fig.                                                                                                                                              |            |

|      | 6.10(b) driven by non-overlapping 25% duty-cycled LO. (d) The circuit in Fig.                                                                                                                                              |            |

|      | 6.10(a) driven by overlapping 50% duty-cycled LO. (e) The circuit in Fig. 6.10(b)                                                                                                                                          |            |

|      | driven by overlapping 50% duty-cycled LO.                                                                                                                                                                                  | 99         |

| 6.10 | (a) Charge sharing problem due to LO overlap when driven by a 50% duty-cycled                                                                                                                                              |            |

|      | LO. (b) Mitigating charge-sharing.                                                                                                                                                                                         | 100        |

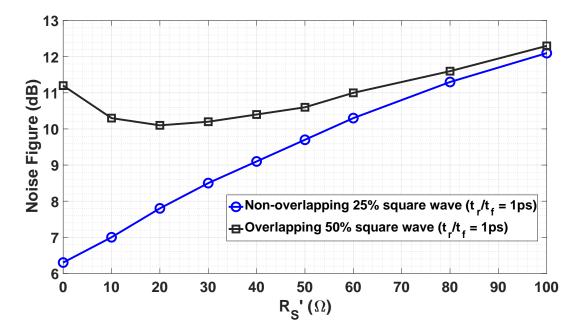

| 6.11 | Simulated noise figure ( $f_{LO} = 20$ GHz) of the circuit in Fig. 6.10(b) versus series                                                                                                                                   |            |

|      | termination resistance $R'_{S}$ for different cases of LO drive. For these simulations,                                                                                                                                    |            |

|      | the switch ON resistance (equal to $12\Omega$ ) is constant and corresponds to the actual                                                                                                                                  |            |

|      | switch used in the circuit.                                                                                                                                                                                                | 101        |

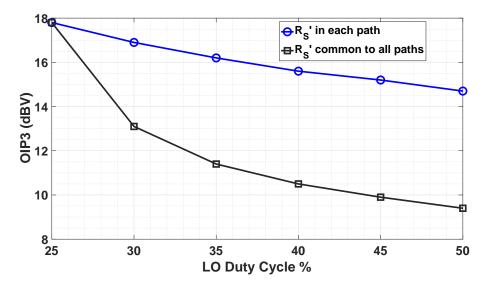

| 6.12 | Degradation of baseband non-linearity due to LO overlap for the circuits in Figs.                                                                                                                                          |            |

|      | 6.10(a) and (b). The model used for the baseband amplifiers is the same as                                                                                                                                                 |            |

|      | the one used for the simulation plot in Fig. 6.4, and is derived from the actual                                                                                                                                           |            |

|      | transistor implementation of the amplifier used in this work. The OIP3 is shown                                                                                                                                            |            |

|      | for $R_F = 1 \mathrm{k}\Omega$ . In each case, an ideal mixer of switch ON resistance equal to $5\Omega$                                                                                                                   | 100        |

| C 19 | is placed in each of the four paths.                                                                                                                                                                                       | 102        |

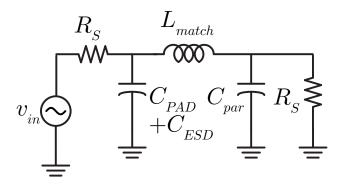

| 0.13 | Schematic of the input matching network. The matching network includes pad                                                                                                                                                 |            |

|      | and ESD capacitance and an additional inductor L-match added to reduce front-                                                                                                                                              | 109        |

| C 14 | end loss, by forming a $\pi$ -section T-line                                                                                                                                                                               | 103        |

|      | Input matching network losses. $\dots \dots \dots$                                                                         | 103        |

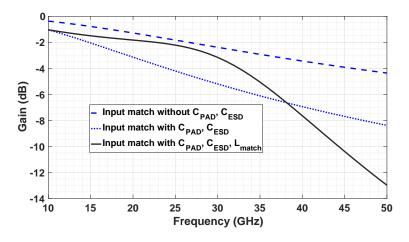

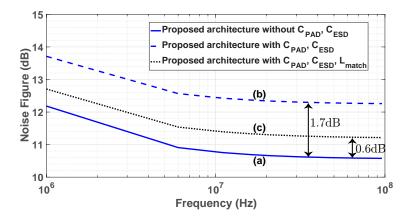

| 0.15 | Simulated noise figure at $f_{LO} = 20$ GHz (a) with only $C_{par}$ (b) with $C_{par}$ , $C_{PAD}$ ,                                                                                                                       | 104        |

| 6 16 | $C_{ESD}$ (c) with entire input matching network including $L_{match}$ .                                                                                                                                                   | 104        |

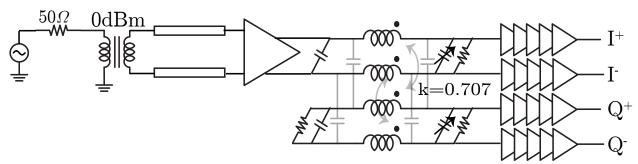

|      | Schematic of LO chain.                                                                                                                                                                                                     | 105        |

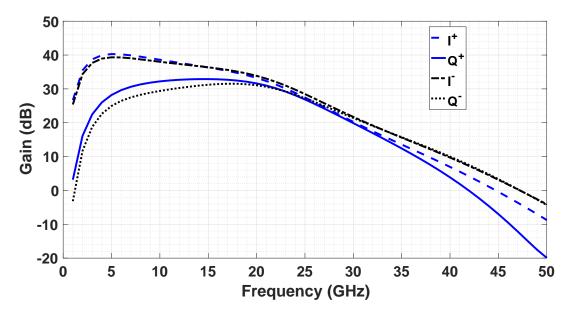

| 0.17 | Small signal gain of the LO chain from LO input to the four gates of the $I/Q$                                                                                                                                             | 105        |

| 6 10 | mixer switches.                                                                                                                                                                                                            | 105        |

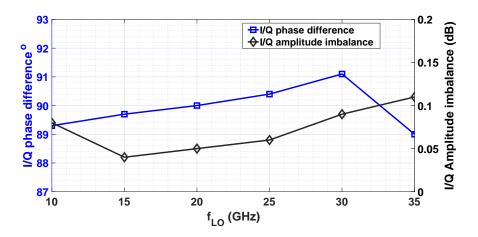

|      | Simulated I/Q amplitude and phase imbalance for differential baseband outputs.<br>Die micrograph of 28nm bulk CMOS prototype of receiver front-end.                                                                        | 106<br>106 |

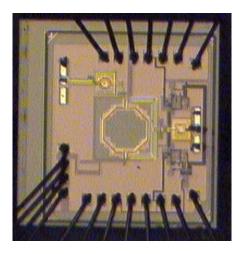

|      | Measured conversion gain and input match for $R_F = 1k\Omega$ versus frequency for                                                                                                                                         | 100        |

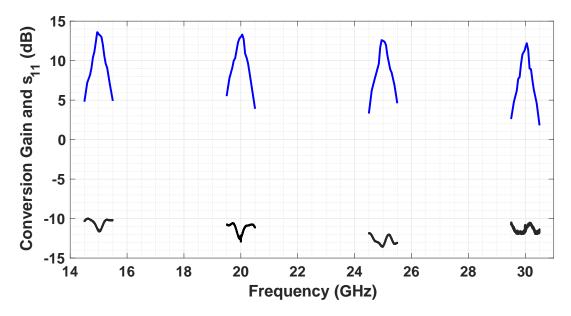

| 0.20 |                                                                                                                                                                                                                            | 107        |

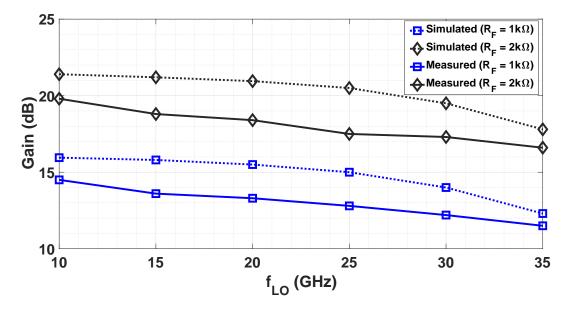

| 6 91 | four different $f_{LO}$<br>Measured and simulated gain versus $f_{LO}$ for $R_F = 1k\Omega$ and $R_F = 2k\Omega$                                                                                                           | 107        |

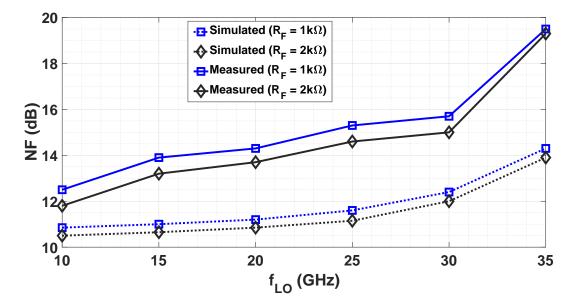

|      | Measured and simulated gain versus $f_{LO}$ for $R_F = 1 \text{k}\Omega$ and $R_F = 2 \text{k}\Omega$ .<br>Measured and simulated noise figure versus $f_{LO}$ for $R_F = 1 \text{k}\Omega$ and $R_F = 2 \text{k}\Omega$ . | 108        |

| 0.22 | Measured and simulated holse figure versus $J_{LO}$ for $h_F = 1KM$ and $h_F = 2KM$ .                                                                                                                                      | 100        |

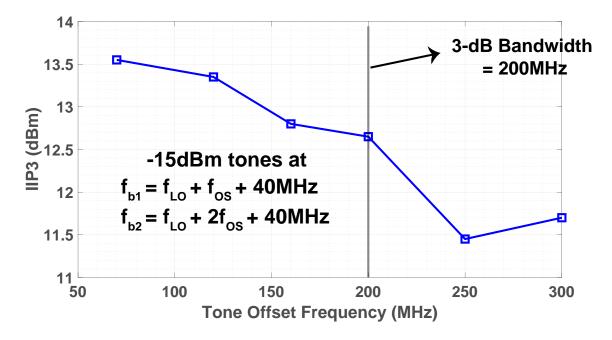

| 6.23 Measured IIP3 as a function of tone offset for $f_{LO} = 20$ GHz for $R_F = 1$ k $\Omega$ 1       | 109 |

|--------------------------------------------------------------------------------------------------------|-----|

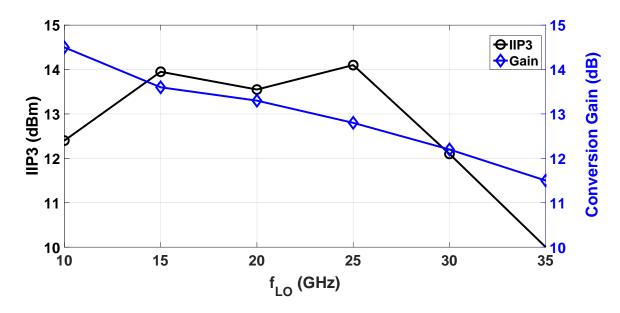

| 6.24 Measured conversion gain and in-band IIP3 versus $f_{LO}$ for $R_F = 1k\Omega$                    | 110 |

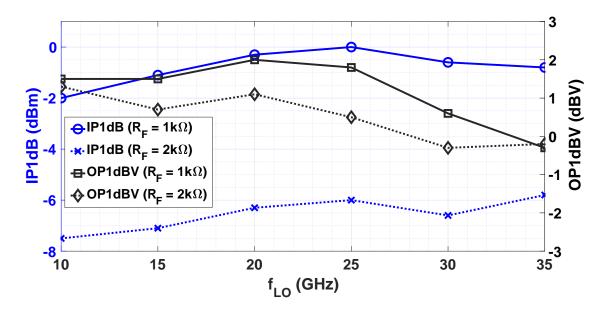

| 6.25 Measured IP1dB and OP1dBV versus $f_{LO}$ for $R_F = 1k\Omega$ and $R_F = 2k\Omega$ 1             | 10  |

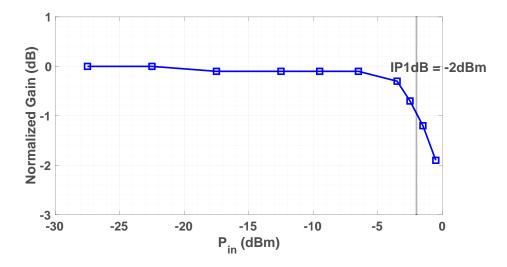

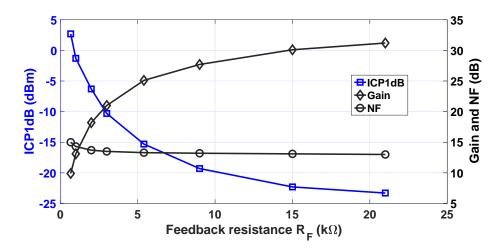

| 6.26 Normalized measured gain versus input power $P_{in}$ for $R_F = 1k\Omega$ at $f_{LO} = 10$ GHz. 1 | 111 |

| 6.27 Trade-off between P1dB, Gain and NF versus feedback resistance $R_F$ . (Measured) 1               | 11  |

| A.1 Equivalent half-circuit of the schematic in Fig. 2.3(b), and the representation of                 |     |

| the circuit during phase $m$ of the LO. The CC-CGLNA is replaced by its input                          |     |

| impedance $1/g_{m,eff}$ and a high input-Z transconductance $g_{m,eff}$ with load $R_L$ . 1            | 127 |

| A.2 LTI equivalent representation of the circuit in Fig. A.1 for $R_{SW2} = 0\Omega$ and               |     |

| broadband input match                                                                                  | 130 |

| A.3 SpectreRF PAC simulation of the LPTV half-circuit of Fig. A.1(a) and the                           |     |

| frequency translated transfer function of the derived LTI equivalent shown in                          |     |

| Fig. 2.5(a), for a broadband source impedance $R_s$ . Simulation results are shown                     |     |

| for two different values of $R_{SW}$                                                                   | 130 |

| A.4 SpectreRF PAC simulation of the LPTV half-circuit of Fig. A.1(a) and the                           |     |

| frequency translated transfer function of the derived LTI equivalent shown in                          |     |

| Fig. 2.5(b), for a narrowband source impedance $R_S$                                                   | 131 |

# List of Tables

| 2.1 | Comparison With State-Of-Art sub-milliwatt 2.4GHz Receiver Front-Ends                     | 35 |

|-----|-------------------------------------------------------------------------------------------|----|

|     | Comparison of implementations with and without Pre-amplifier                              |    |

| 4.1 | Comparison with State-of-Art                                                              | 73 |

| 5.1 | Comparison with State-of-the-Art N-Path Filter-Based Receivers with Higher Order Roll-Off | 84 |

|     | Comparison with mixer-first receivers greater than 10GHz                                  |    |

#### Acknowledgments

It would have been impossible to navigate through the testing waters of a five-year long PhD without the support and guidance, both technical and non-technical, of several people. I take this opportunity to thank all my pillars of support during this arduous but enjoyable journey. First and foremost, I thank my advisor Prof. Ali Niknejad. I am grateful for all the opportunities he gave me to explore my creativity. I do not think any other advisor would have allowed me such a high degree of freedom in research. I thank him for all his technical feedback which has definitely made me a better IC designer. I cannot thank him enough for all his timely feedback before various conference deadlines, despite my paper drafts reaching him less than twelve hours before the deadline. I am grateful for his instantaneous responses and feedback during my long arduous hours of measuring my chips with days to go for the deadline. I thank him for doing more than what is expected of a PhD advisor, and being a father figure to me. He supported me through some really tough early years, always providing encouragement, without once exerting pressure for results. He kept my spirits and confidence high through a tough first two and a half years, and this helped me become more prolific in the second half of my PhD. His best advice was asking me to focus on doing good research without worrying about metrics like impact of publications. He is a living embodiment of a Karmayogi. In Chapter 2 Verse 47 of the Bhagavad Gita, Lord Krishna tells Arjuna "You only have a right to perform your duty, but you are not entitled to the fruits of your actions". While it is easy to preach this to others, Prof. Ali has also led by example. I will be eternally grateful to Prof. Ali.

I would not have been attracted to the field of IC design during my undergraduate days, if not for Prof. Shanthi Pavan and Prof. Nagendra Krishnapura of IIT Madras. Today, while it is the trend d'jour to be attracted to greener pastures, it was impossible not to be smitten with the way famed duo of Prof. Shanthi and Prof. Nagi made circuits come alive on the blackboard. Prof. Shanthi was also my advisor for my undergraduate thesis. Apart from the solid technical grounding I gained, Prof. Shanthi also instilled in me a sense of professionalism in the way I present my results to others. Every year when we meet at ISSCC, he takes a deep interest in my research and spends a significant time discussing my work. I have been lucky to be advised by the world's leading expert in data converters during my undergraduate studies and the world's leading expert in RF and mm-wave circuits during my PhD. Also, I wish to thank Prof. Borivoje Nikolic, Prof. Martin White and Prof. Elad Alon for taking the time to serve on my qualifying exam committee and dissertation committee, and provide feedback.

I wish to thank my mother Srividhya and father Krishnamurthy for their unwavering support through all the tough times not only over the last five years, but for the last twenty seven years since I was born. No amount of words can express the gratitude one feels for parents. I also wish to thank my grandmother Saraswathi who raised me and took care of me when my parents were away for work during the day. I owe everything to my family.

It is well-known that during a PhD, you learn as much from your labmates as from your advisor. I had the good fortune of being able to learn from some very solid IC designer

colleagues. First and foremost, I wish to thank Andrew Townley, who took me under his mentorship for the first year and a half of my PhD, and taught me the ropes of doing good circuit layout. Despite his busy schedule as a senior PhD student, he always had time for me. I wish to thank Lorenzo Iotti, with whom I have had several fruitful collaborations in N-path filter work. I am grateful for all the auxiliary circuit IP which he graciously shared with me, knocking a good few months off my PhD. I also wish to thank Nima Baniasadi, for all his help on anything to do with electromagnetic simulations and teaching me how to use a probe station. I wish to thank Kosta Trotskovsky for taking an active interest in my development as a PhD student during my early years and Filip Maksimovic for a fruitful collaboration on the low-power work. I wish to thank Ali Ameri, who was my partner for all the course projects during the first year in addition to being a good friend and my ping-pong partner. Finally, I wish to thank other seniors in our lab, Greg LaCaille, Lucas Calderin and Nai-Chung Kuo.

I wish to thank the BWRC director, Ajith Amerasekera, for great management support. I will fondly remember our long conversations about cricket. I wish to thank Brian Richards for smooth handling of affairs with TSMC, and Candy Corpus and Shirley Salanio for all the administrative support.

I wish to thank the various funding sources during my PhD, including DARPA, NSF and Intel. Specifically, I wish to thank Christopher Hull of Intel Labs for useful feedback during the regular sponsor meetings. I wish to thank Chintan Thakkar for providing me an opportunity to intern at Intel Labs. I was fortunate to work with and learn from him, Cooper Levy and Saeid Daneshgar. Also, I was fortunate to become good friends with Cooper and Chintan, who also graciously offered me rides back home after work. I wish to thank my very good friend Jahnavi Sharma, who went out of her way to help me throughout the duration of my internship. Jahnavi continues to be a great friend, helping me and offering sage advice.

I also wish to thank other friends from Berkeley and BWRC, including Nandish Mehta, who took an active interest in my career, Panagiotis Zarkos, Matthew Anderson and Rohit Braganza. I wish to thank my roommate and friend Vijay Govindarajan for taking over all household chores whenever I had deadlines.

I wish to thank my all-weather friend from undergrad, Manikandan Srinivasan. The endless phone calls with him helped me keep my sanity during the last five years. I also fondly remember the various trips I took across the United States with him, Sundar Rajan and Jayanth Ramesh, all of whom are good friends from undergrad. I also wish to thank Nirmal Lekshminarayanan and Akshay Krishna, who apart from being great friends, introduced me to the wonderful world of word games. I also wish to thank Narasimhan Balakrishnan and Shashank Subramanian, my good friends from undergrad.

I am also grateful to Arjun Subrahmanyan and Srihari Veeraraaghavan, my very good friends from high-school, who used to have me over at their place in the South Bay regularly. The anticipation of these visits kept me going and I will definitely miss them. I also wish to thank Prajwal Padmanabh, my friend from high-school, who graciously showed me around Europe on my visit to Germany for a conference. I will have fond memories of our shared happiness at watching Rafael Nadal go on to become the greatest ever tennis player.

# Chapter 1 Introduction

In accordance with the trend of one generation of wireless mobile telecommunications technology per decade since the 1980s [7], the 2020s belong to 5G, the fifth generation. 5G is expected to provide a diverse range of services from enhanced mobile broadband at multigigabit per second, to supporting the massive Internet of Things revolution. While all the generations up to 4G used the frequency spectrum below 3GHz, 5G is expected to support communication on a wide range of spectrum, ranging from low-bands from 0.6-6GHz and mm-wave bands greater than 24GHz. Forecasts of hundreds of billions of connected devices by 2030 [8] mandate the need for circuit-level techniques to mitigate the increasing interference that comes with this proliferating number of devices.

At the network level, this problem is solved by re-transmitting packets which are not transmitted successfully in the presence of an interferer [9]. However, re-transmissions increase latency and therefore, it is desirable to build RF front-ends which are interference resilient. Additionally, with the growing number of bands with the advent of 5G, mobile devices need to support all the new bands [7] in addition to existing 3G, 4G and Wi-Fi bands. Also, different parts of the world have different bands, making multi-band support even more challenging.

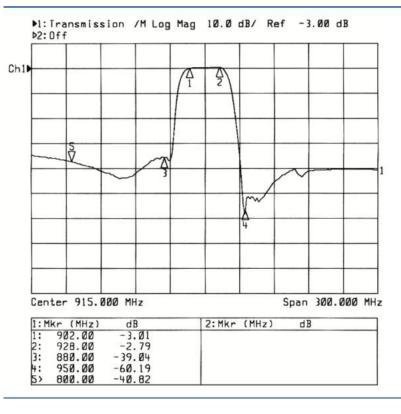

Current solutions involve the use of multiple surface acoustic wave (SAW) and thin-film bulk acoustic resonator (FBAR) filters. Both of these work on the principle of transduction of acoustic waves, where piezoelectric materials are used for the transduction from electrical to mechanical energy [10]. While SAW filters typically support only frequencies up to around 1.5GHz [10], FBAR filters can be used for frequencies up to 10GHz. However, since these filters are not tunable, multi-band support would require a large increase in the number of such filters on the mobile device. Apart from the cost and the area footprint, these filters are also quite lossy and can exhibit up to 3dB insertion loss [1]. However, they do provide extremely sharp front-end filtering as evidenced by the transfer functions of some commercial SAW filters, shown in Fig. 1.1.

Figure 1.1:  $s_{21}$  transfer functions of some typical commercial SAW filters [1, 2].

The N-path filter was first demonstrated as early as the 1950s [11, 12]. It was re-discovered a decade back [13, 14], and is the ideal candidate for the SAW-less receiver. In essence, the N-Path filter consists of N paths of switched-RC kernels. As analyzed extensively in [15–18],

#### CHAPTER 1. INTRODUCTION

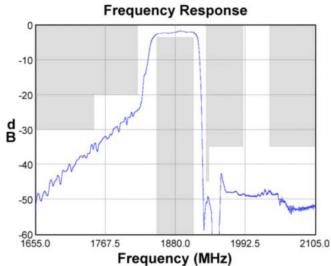

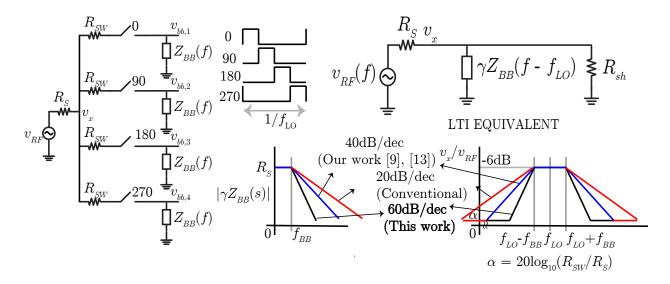

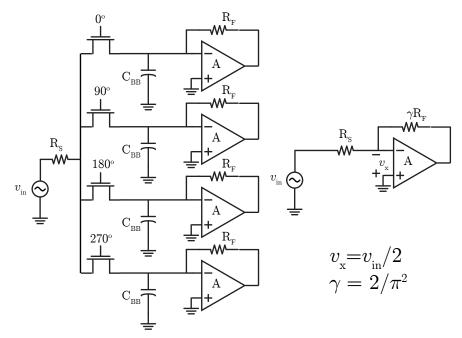

this switched-RC circuit behaves as a passive mixer, when switched at a frequency  $\omega_S$  much higher than 1/RC, the time constant of the switched-RC kernel. The N-path filter has the interesting property of impedance translation, as illustrated in [19]. A conventional N-path filter (see Fig. 1.2), like the one described in [19] translates a shunt RC impedance from baseband to RF, enabling the realization of programmable band-pass filters, whose center frequency is exactly equal to the LO frequency  $f_{LO}$  at which the mixer switches are driven. However, while promising, these can achieve only 20dB/decade RF selectivity and are no match to the superior filtering provided by SAW filters.

Figure 1.2: Schematic of an N-path filter based receiver illustrating impedance translation property.

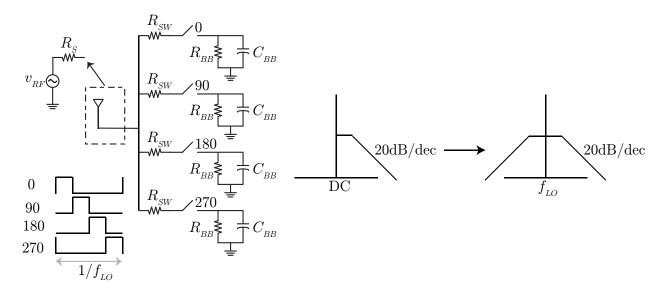

An important "promise" of 5G is to offer enhanced user experience with 100x end user data rates and lower latency, by exploiting the spatial dimension of communication using multiple antennas at the transmitter and receiver [20, 21]. To serve multiple users (K) simultaneously, massive MIMO (Multiple-Input Multiple-Output) systems have base-stations with large number of antennas M, with  $M \gg K$  [22]. MIMO systems with a small number of concurrent beams [23–25] have used RF phase shifters for spatial filtering, in an attempt to save LO and baseband power. However, for massive MIMO arrays which serve a larger number of users, higher degree of spatial flexibility is desired. The  $K \times M$  number of phase shifters required in multi-user MIMO systems makes the implementation of vector interpolator based active RF phase shifters [23, 24] prohibitively power hungry. Use of passive transmission line based phase shifters [25] results in loss and a large area penalty.

Figure 1.3: Digital beamforming receiver array for massive MIMO systems.

To this end, it is desirable to have massive digital beam-forming arrays for systems with high spatial flexibility. As spatial filtering of out-of-beam, in-band interferers is performed at the baseband, the RF front-end needs to be highly linear to handle these interferers (see Fig. 1.3), posing yet another circuit design challenge.

This dissertation attempts to provide some solutions to several of the problems described thus far by building N-path filter based interference resilient RF receiver front-ends. The five different receiver front-end ICs (integrated circuits) demonstrated in this dissertation target three separate application thrusts: one front-end for sub-mW IoT applications, three front-ends targeting sub-6GHz 5G applications and one targeting mm-wave digital beam-forming applications.

The first part of this dissertation deals with interference resilient CMOS receiver frontends for low power internet-of-things (IoT) applications. In Chapter 2, a sub-mW 2.4GHz receiver front-end is presented. The front-end consists of a capacitively cross-coupled common gate LNA, with translational positive feedback from baseband to RF through a 4-phase switching mixer, providing RF filtering and matching, in conjunction with an input transformer. A detailed analysis of the architecture is presented, highlighting the design trade-offs between noise, out-of-band filtering and power. A prototype integrated circuit, fabricated in 28nm CMOS, demonstrates a record out-of-band IIP3 of +3.3dBm for sub-mW 2.4GHz receiver front-ends. The content in Chapter 2 is an extended version of the content presented in [26].

The second part of this dissertation, covering chapters 3 through 5, presents enhanced Npath filter-based receivers. These consist of N-path filters loaded by driving point impedances with a steeper roll-off than the 20dB/decade presented by a shunt RC impedance, which is the load for a conventional N-path filter. These provide a pathway to the SAW-less receiver for sub-6GHz 5G applications. In Chapter 3, a "second order" passive mixer-first receiver is proposed to improve channel selectivity, linearity and noise figure in the presence of out-ofband blockers, by presenting an impedance which rolls off at 40dB/decade as the load to an N-path filter. The synthesis of this impedance is described in a step-by-step manner starting from the required impedance transfer function to its actual circuit realization. Various tradeoffs and limitations of the architecture are described in detail, and layout related techniques are also provided. Two integrated circuit prototypes were fabricated in 28nm bulk CMOS as proof of concept for this circuit, including a low-power version. The receiver, capable of broadband operation from 0.2-2GHz, achieves an out-of-band IIP3 of +33dBm and a blocker P1dB of +12dBm. Chapter 3 contains the material found in [5].

Chapter 4 presents a "third-order" passive mixer-first receiver to improve channel selectivity and resilience to close-in blockers, by building an N-path filter which drives an impedance with 60dB/decade roll-off. A step-by-step derivation is provided for the synthesis of the first ever driving point impedance with 60dB/decade roll-off. An integrated circuit prototype was fabricated in 28nm bulk CMOS as proof-of-concept, and characterized. The receiver front-end, capable of broadband operation from 0.2-4.5GHz, demonstrates thirdorder filtering of close-in blockers and achieves an out-of-band IIP3 of +21dBm and B1dB of greater than 6dBm for blockers at the alternate channel. Chapter 4 contains the material found in [6]

Chapter 5 extends the work on the third order N-path filter of Chapter 4, by demonstrating an enhanced N-path filter-based receiver with 80dB/decade RF selectivity and distortion cancellation to improve channel selectivity and resilience to adjacent channel blockers. An integrated circuit prototype is fabricated in 28nm CMOS as proof-of-concept, and characterized. The front-end, capable of operation from 0.2-3.5GHz, shows a close-in roll-off of 80dB/decade. It achieves a record adjacent channel B1dB of +8dBm, alternate channel B1dB of +10dBm and adjacent channel IIP3 of +23dBm.

The last part of this dissertation focuses on building high linearity receiver front-ends for mm-wave digital MIMO applications. In Chapter 6, a 10–35GHz passive mixer-first receiver is proposed for use in digital beam-forming arrays. Techniques are proposed to enhance the linearity of such receivers, both at baseband and the RF mixer switches. Techniques to mitigate charge sharing due to LO overlap are also proposed. Detailed simulation results are provided to illustrate the benefits of these techniques. An integrated circuit prototype is fabricated in 28nm bulk CMOS and fully characterized. The receiver has built-in programmability to trade-off gain for linearity. The receiver achieves a peak in-band IIP3 of +14.1dBm, a peak gain of 14.5dB and a noise figure of 12.5dB, in its nominal setting. Chapter 6 is an extended version of the material presented in [27]

In Chapter 7, we conclude by presenting the key academic contributions of this dissertation and also providing several avenues for future research to build on the work done in this dissertation.

#### Chapter 2

## Sub-mW Interference-Resilient Receivers for IoT Applications

#### 2.1 Introduction

With the advent of the Internet-of-Things (IoT) revolution, the number of connected devices is expected to surge up to 500 billion by 2030 [8]. This rapid increase calls for the use of radios with extended battery lives, leading to research in radios with sub-mW power consumption. Additionally, the large number of devices also leads to mutual interference between them. Therefore, there is a need for sub-mW interference tolerant radio receivers.

There is an abundance of work in enhancing interference resilience of receiver front-ends, based on N-path filters [13, 28–30]. However, these are targeted at SAW-less LTE and sub-6GHz 5G applications, and hence consume tens to hundreds of milliwatts of power.

The state-of-the-art sub-mW receiver front-ends [31–35], for the 2.4GHz and 915MHz ISM bands, all have LNA based front-ends, and use techniques to achieve improved noise figure (and sensitivity) at low power. While [32, 33] consume power as low as  $64\mu$ W and  $282\mu$ W and show modest noise figures of < 9dB, their IIP3 is as low as -21 to -28dBm. [34] demonstrated a receiver with moderately better IIP3 (-15.8dBm) and much higher gain (55dB) at a power consumption of  $600\mu$ W. However, the NF was worse at 15.1dB. [31, 35] demonstrated the possibility of noise cancellation at low power, demonstrating noise figures of 6.55dB and 2.8dB respectively at powers as low as  $230\mu$ W and  $475\mu$ W respectively. While [31, 35] did demonstrate improved linearity with an IIP3 of -10dBm, all of [31–35] had broadband input matching. The only RF filtering, if any, was provided by the finite bandwidth of the input matching network. Therefore, up to such frequencies where the matching network starts to cause input attenuation, the out-of-band IIP3 of [31–35] are as low as -28 to -10dBm (approximately the same as their in-band IIP3).

RF filtering is a characteristic of any passive mixer due to the translation of the first order low-pass impedance from baseband to RF [19]. However, the amount of RF filtering is determined by the size of the switches used in the passive mixer, and hence the LO power.

The far-out attenuation cannot be lower than  $R_{SW}/(R_{SW} + R_S)$  [36], where  $R_{SW}$  is the ON resistance of the mixer switch and  $R_S$  is the source impedance. [37] used a transformer to step-up the source impedance from 50 $\Omega$ , enabling the use of smaller switches in the passive mixer which followed. This work exhibited an IIP3 of +2.6dBm, and benefited from the RF filtering that comes with the use of passive mixers before any active circuit. However, this was designed for 5GHz WLAN applications and had a power consumption as high as 11.6mW. More recently, [38] demonstrated a 0.6mW (at 1GHz) mixer-first receiver frontend, with as high as +25dBm OOB IIP3. The high IIP3 was a result of the mixer-first architecture used. However, the gain of this front-end is limited by the gain of the off-chip input matching network and 6dB passive gain from the capacitive read-out. Additionally, the power of this front-end is expected to scale proportional to  $f_{LO}$ , to more than a milliwatt at the desired 2.4GHz ISM band.

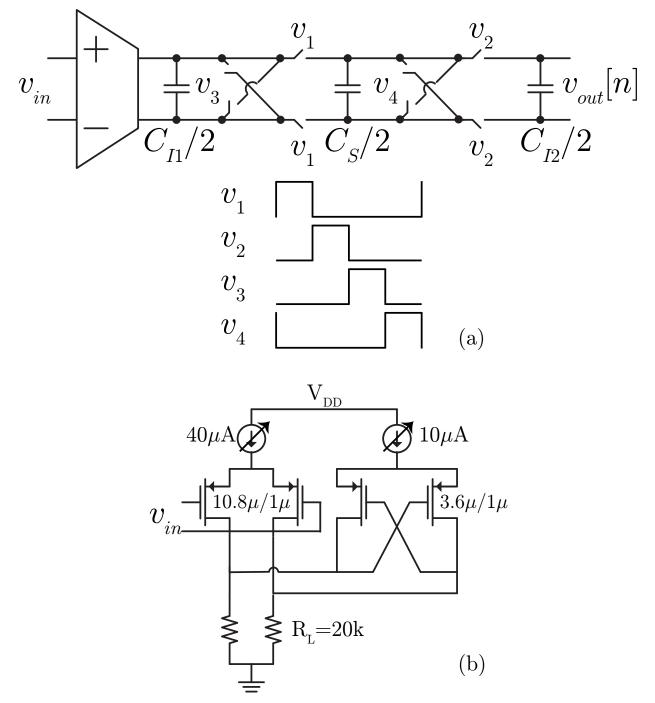

In [26], we proposed an architecture for a direct-conversion receiver at 2.4GHz which achieves moderate NF, gain, in-band linearity and most importantly improved out-of-band linearity due to RF filtering, while keeping the power consumption of the entire front-end under a milliwatt. Compared to [26], this chapter delves into greater depth on analyzing the translational-feedback-based architecture and design trade-offs with respect to noise, linearity and RF filtering. With the aim of building a complete receiver front-end, it also includes the design and measurement results of a baseband amplifier with programmable gain and bandwidth.

This chapter is organized as follows. Section 2.2 describes the front-end architecture. It starts off with a commonly used low-power LNA, and builds up to our proposed architecture. Section 2.3 presents the results of the LTI equivalent circuit for the receiver, and describes the design of the N-path filters in the circuit to achieve the desired transfer function. Section 2.4 provides a detailed analysis of the noise from various sources and compares it against more traditional architectures. It also provides an analysis of both in-band and out-of-band non-linearity, from a design perspective. Section 2.5 provides design details of the transformer, LNA and the baseband filter. Section 2.6 provides measurement results of the front-end and the baseband filter. Section 2.7 compares this work against the state-of-the-art and provides some key takeaways of the work.

#### 2.2 Receiver Architecture

To keep the power consumption of the receiver under a milliwatt, it is desirable to have a front-end matching network with gain. Additional to providing gain, the matching network transforms the antenna resistance from 50 $\Omega$  to a higher value, relaxing the power budget on the subsequent blocks. Similar to [31, 35, 37] and many other works in literature, a transformer-based matching network is used in the front-end. Differential outputs, passive gain and ESD protection are some of the advantages of using transformer-based matching networks. To meet the sub-mW targets, is also desirable to use techniques to lower the power consumption of the LNA. To this end,  $g_m$  boosting in a common-gate LNA is a commonly

used technique. A simple power-efficient method of doing this is to use passive inverting amplification by using capacitively cross-coupling in a differential CGLNA (see Fig. 2.16 for schematic), as demonstrated in [39]. A passive mixer at the output of the LNA completes the receiver front-end.

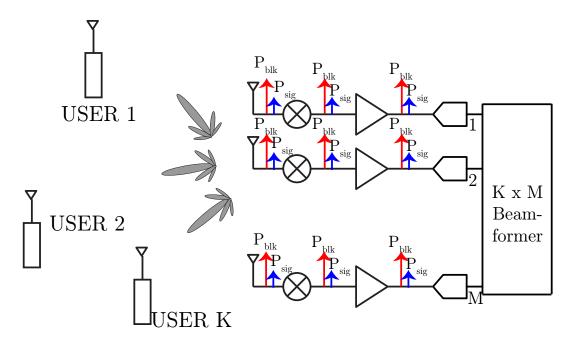

While the transformer-based input matching is not broadband, the bandwidth (100s of MHz) is still much higher than the channel bandwidth (1-10 MHz) required for the modest data rates in IoT applications. Consequently, such a receiver front-end has little or no frequency selectivity. In order to be instantaneously narrowband and frequency selective at the RF input, but still support operation over the entire range of bandwidth of the input matching network, an N-path filter may be added in shunt with the CC-CGLNA at the input, as shown in Fig. 2.1(a). The N-path filter, first seen in [11, 12] and re-discovered in [13, 14], has an important property of impedance translation from baseband to RF. Consequently, it can be used to realize high-Q tunable RF band-pass filters (with center frequency equal to  $\omega_{LO}$ , the frequency at which the mixer is switched).

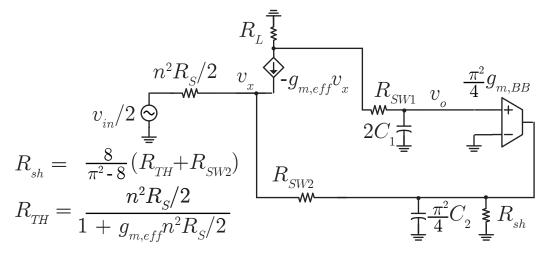

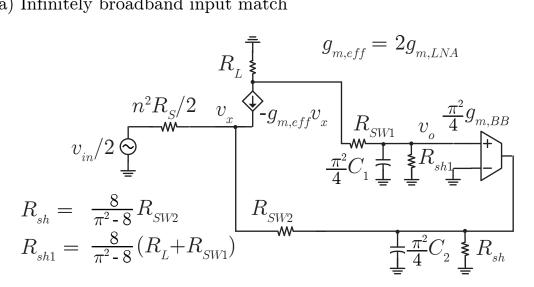

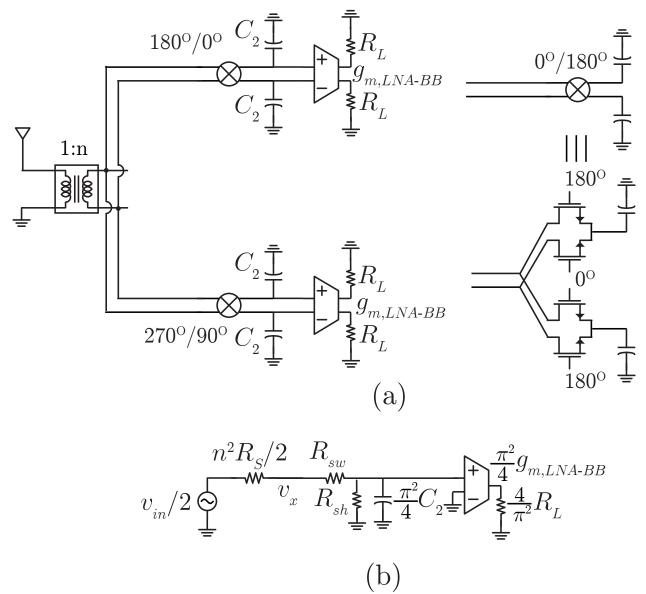

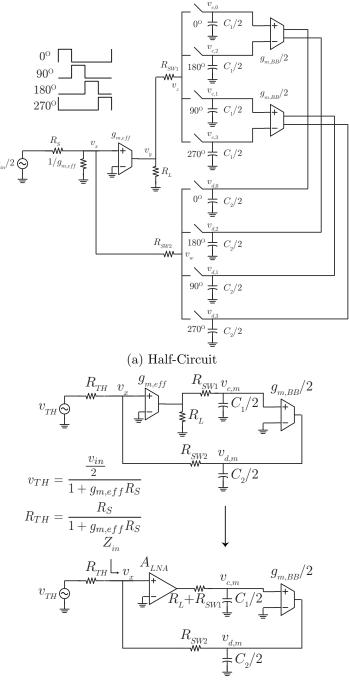

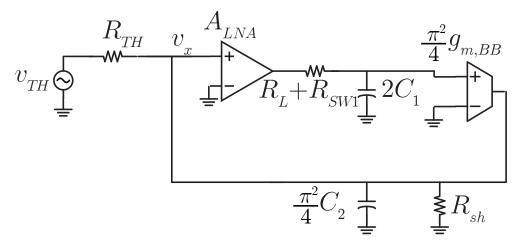

The receiver front-end shown in Fig. 2.1(a) is a linear periodic time varying (LPTV) system, with a linear time invariant (LTI) half-circuit equivalent representation at frequencies around  $\omega_{LO}$  (See Fig. 2.1(b)). Note that this LTI equivalent representation also includes the common gate LNA. As seen in [19], harmonic re-upconversion losses in the N-path filter are represented in the LTI equivalent circuit with a shunt resistance  $R_{sh}$ . The re-radiation resistance  $R_{sh}$  is a function of the impedance seen by the shunt N-path filter  $Z_{TH}$  (see Fig. 2.1).  $Z_{TH}$  may be modeled as a shunt LCR network with  $Q_{match} = R_{TH}/(\omega_0 L_{sec})$ , where the equivalent resistance  $R_{TH}$  is given by

$$R_{TH} = \frac{n^2 R_S}{1 + \frac{n^2 g_{m,eff} R_S}{2}}$$

(2.1)

where  $R_S$  is the source impedance of the antenna, n is the electrical turns ratio of the transformer,  $L_{sec}$  is the secondary inductance of the transformer and  $g_{m,eff}$  is the effective transconductance of the capacitively cross-coupled CG LNA, and is given by  $g_{m,eff} = 2g_{m,LNA}$ . Note that in traditional N-path filters such as the one in [19, 37],  $R_{TH}$  is given by  $n^2 R_S$ . That is, the impedance seen by the N-path filter is exactly equal to the transformed source impedance. However, in the circuit in Fig. 2.1, an additional dependence on  $g_{m,eff}$  is seen due to the use of a common-gate LNA, as seen in equation (2.1). For the extremal cases of infinitely broadband ( $Q_{match} = 0$ ) and infinitesimally narrowband ( $Q_{match} = \infty$ ),  $R_{sh}$  for the circuit in Fig. 2.1 [19] is given by,

$$R_{sh} = \begin{cases} \frac{8}{\pi^2 - 8} \left( \frac{\frac{n^2 R_S}{2}}{1 + \frac{n^2 g_{m,eff} R_S}{2}} + R_{SW2} \right) & \text{Broadband} \\ \frac{8}{\pi^2 - 8} R_{SW2} & \text{Narrowband} \end{cases}$$

(2.2)

where  $R_{SW2}$  is the ON resistance of the mixer switches in the shunt N-path filter.

Figure 2.1: (a) Simplified schematic of CC-CGLNA based receiver front-end with shunt N-path filter, in conjunction with transformer-based input matching network. (b) LTI equivalent half circuit to illustrate the matching at the LNA input.

For input match at  $\omega_{LO}$  with the circuit in Fig. 2.1, the condition for matching can be derived as

$$\frac{\frac{n^2 R_S}{2}}{R_{SW2} + R_{sh}} = 1 - n^2 g_{m,eff} \frac{R_S}{2}$$

(2.3)

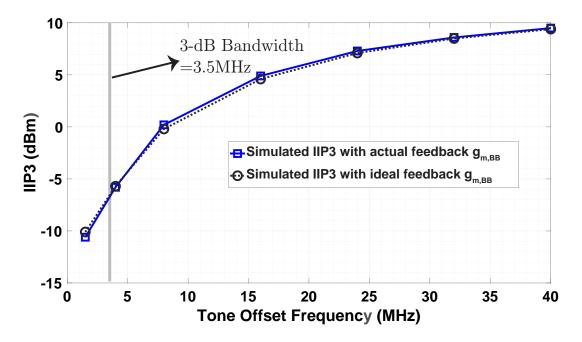

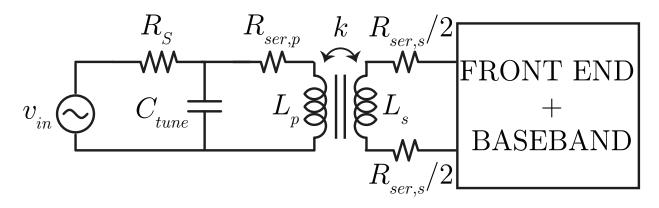

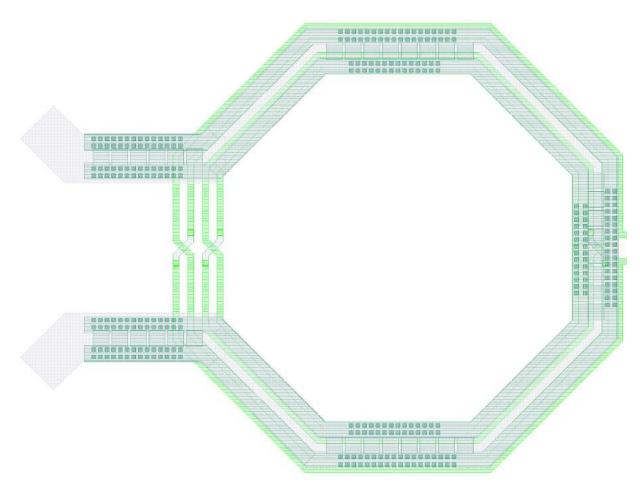

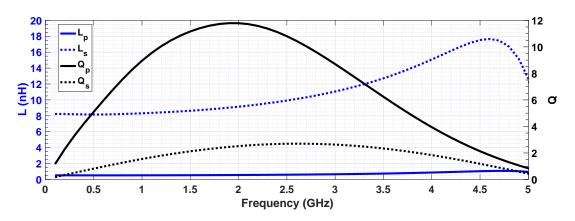

Clearly, it is impossible to match for  $n^2 g_{m,eff} R_S/2 > 1$ . This is the well-known  $g_m$  versus matching trade-off in a common gate LNA [39]. In a conventional common-gate LNA, the value of  $g_m$  required for matching is  $1/R_S$  and this yields a noise factor of  $1 + \gamma/\alpha^1$ . When effects of re-radiation losses in the shunt N-path filter are considered, the input impedance of the circuit drops. Therefore, an even lower value of  $g_m$  is needed to match, exacerbating the noise versus matching trade-off of the LNA.