# Low Thermal Budget Process Engineering for Flexible Electronics, Sensors, and Nanoscale Patterning

Thomas Rembert Tsu-Jae King Liu

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-225 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-225.html

December 1, 2021

Copyright © 2021, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Low Thermal Budget Process Engineering for Flexible Electronics, Sensors, and Nanoscale Patterning

by

Thomas Ryland Rembert

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Ming C. Wu Professor Junqiao Wu

December 2019

# $\begin{array}{c} \text{Low Thermal Budget Process Engineering for Flexible Electronics, Sensors, and Nanoscale} \\ \text{Patterning} \end{array}$

$\begin{array}{c} {\rm Copyright~2019} \\ {\rm by} \\ {\rm Thomas~Ryland~Rembert} \end{array}$

#### Abstract

Low Thermal Budget Process Engineering for Flexible Electronics, Sensors, and Nanoscale Patterning

by

#### Thomas Ryland Rembert

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

Within every process of electronic device fabrication and subsequent device use, there exists an inherent temperature limitation. This limitation can be part of a particular processing step or a target specification of device operation. To determine the temperature restrictions required by a device and its fabrication, the material system and target application of the resultant device must be assessed, as the thermal budget will vary based on both of these factors. If the temperature limit imposed on a device and its process becomes low enough, measures must be taken to ensure a reduction in thermal load is met without sacrificing the integrity of the constituent materials or the final device behavior. More specifically, these measures result in the development of low temperature materials deposition techniques, devices with reduced power consumption, or low temperature in-line processing techniques. In this dissertation, I will present solutions to circumvent temperature limitations in three areas: transparent flexible electronics, small-scale gas sensors for the Internet of Things (IoT), and back-end-of-line (BEOL) processing steps of state-of-the-art integrated circuits (ICs).

First, in Chapter 2, a novel method of metal oxide material deposition for flexible thin film transistors (TFTs) will be discussed. Materials characterization indicates this material is of high quality suitable for flexible electronics, demonstrated via fabrication of fully transparent all-oxide flexible TFTs. Second, in Chapter 3, a chip-integratable pollutant gas sensor based on silicon transistors is discussed. Transistor-based gas sensing leverages IC manufacturing and enables low temperature operation, allowing for lower power consumption carbon monoxide sensors for air quality monitoring and personal pollution tracking. Lastly, Chapter 4 will present a novel low cost fully-BEOL-compatible nanoscale patterning method based on tilted ion implantation and conventional deep ultraviolet (DUV) lithography. Utilizing silicon-containing spin-on films, patterns on the order of 20 nm are achieved, providing an alternative lithographic method for state-of-the-art transistor fabrication with nanoscale features.

To those who support me, believe in me, care for me, and love me, even when I can't do it myself

This page intentionally left blank.

# Contents

| Co         | onten           | ts                                      | iii |

|------------|-----------------|-----------------------------------------|-----|

| $_{ m Li}$ | st of           | Figures                                 | vi  |

| Li         | st of           | Tables                                  | ix  |

| 1          | $\mathbf{Intr}$ | oduction                                | 1   |

|            | 1.1             | Flexible Electronics                    | 1   |

|            |                 | 1.1.1 Background & Motivation           | 1   |

|            |                 | 1.1.2 Semiconducting Metal Oxides       | 2   |

|            |                 | 1.1.3 Temperature Limitations           | 3   |

|            | 1.2             | IoT Sensors                             | 5   |

|            |                 | 1.2.1 Background & Motivation           | 5   |

|            |                 | 1.2.2 Pollutant Gases                   | 5   |

|            |                 | 1.2.3 Temperature Limitations           | 6   |

|            | 1.3             | Integrated Circuit Fabrication          | 6   |

|            |                 | 1.3.1 Background & Motivation           | 6   |

|            |                 | 1.3.2 Patterning Technologies           | 7   |

|            |                 |                                         | 10  |

|            | 1.4             | •                                       | 10  |

| 2          | All-            | Oxide Transparent, Flexible Electronics | 1   |

|            | 2.1             | <del>-</del> ,                          | 11  |

|            | 2.2             | Filtered Cathodic Arc Deposition        | 13  |

|            | 2.3             | <del>-</del>                            | 14  |

|            | 2.4             | ZnO Materials Characterization          | 15  |

|            |                 | 2.4.1 Structural Characterization       | 15  |

|            |                 | 2.4.2 Electrical Characterization       | 16  |

|            |                 | 2.4.3 Optical Characterization          | 17  |

|            | 2.5             | <del>-</del>                            | 19  |

|            |                 | 2.5.1 Alkali-Free Glass Substrate       | 19  |

|            |                 |                                         | 20  |

|   |      | 2.5.3 Performance of Bent TFT                                 | 22 |

|---|------|---------------------------------------------------------------|----|

|   | 2.6  | Demonstration of NMOS Inverter                                | 23 |

|   | 2.7  | Conclusion                                                    | 25 |

|   |      | 2.7.1 Summary                                                 | 25 |

|   |      | 2.7.2 Future Work                                             | 25 |

| 3 | Q:1: | con Transistor-Based Gas Sensors                              | 26 |

| 3 | 3.1  |                                                               |    |

|   |      | Existing Carbon Monoxide Sensing Technology                   | 26 |

|   | 3.2  | Chemical-Sensitive FET                                        | 28 |

|   |      | 3.2.1 Device Fabrication                                      | 28 |

|   |      | 3.2.2 Device Operation                                        | 28 |

|   | 0.0  | 3.2.3 Personal Pollution Tracking                             | 29 |

|   | 3.3  | CS-FET Carbon Monoxide Sensor                                 | 31 |

|   |      | 3.3.1 Materials Optimization for Peak Sensor Response         | 31 |

|   |      | 3.3.2 CO Sensor Response                                      | 37 |

|   |      | 3.3.3 Sensor Selectivity                                      | 39 |

|   |      | 3.3.4 Proposed Sensing Mechanism                              | 42 |

|   | 3.4  | Summary                                                       | 46 |

|   |      | 3.4.1 Conclusion                                              | 46 |

|   |      | 3.4.2 Future Work                                             | 46 |

| 4 | Tilt | ed Ion Implantation for Nanoscale Patterning                  | 47 |

|   | 4.1  | Introduction                                                  | 47 |

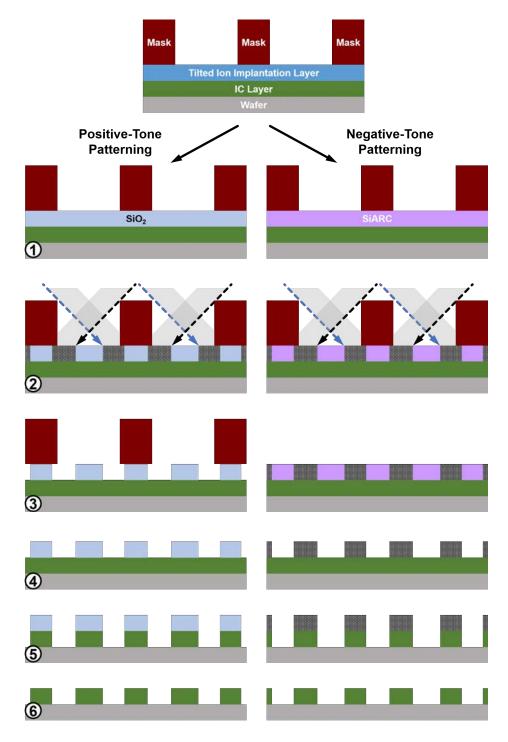

|   | 4.2  | Positive-Tone vs. Negative-Tone TII Patterning Process        | 48 |

|   | 4.3  | Implantation-Induced Change in SiARC Wet Etch Rate            | 48 |

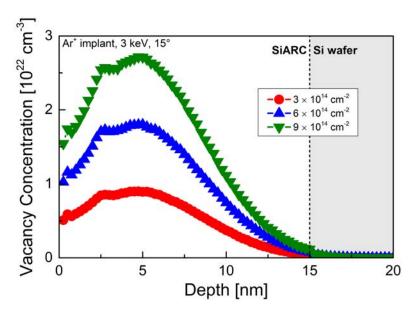

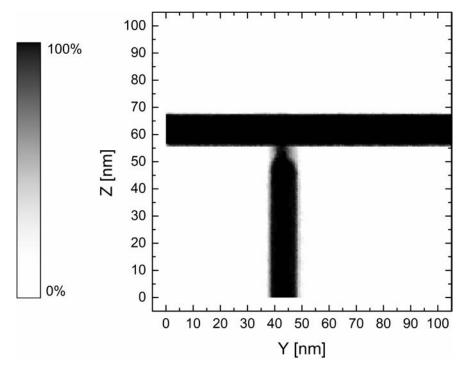

|   |      | 4.3.1 SRIM Simulations of SiARC Implantation                  | 48 |

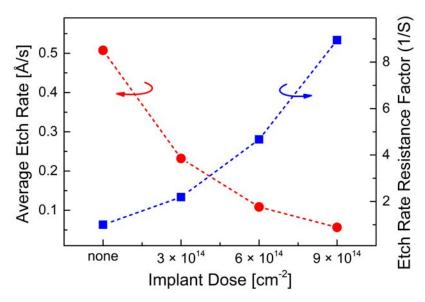

|   |      | 4.3.2 Wet Etching of Implanted SiARC Films                    | 48 |

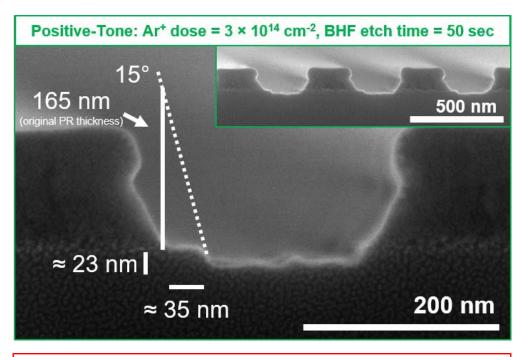

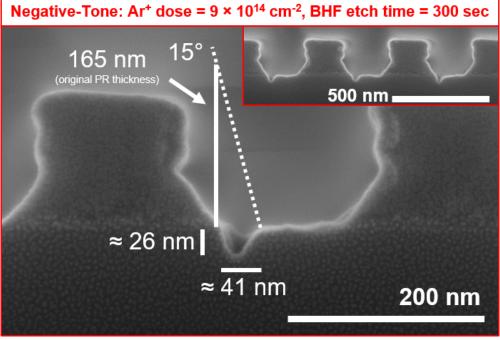

|   | 4.4  | Sub-lithographic Nanoscale Patterning using SiARC TII Process | 51 |

|   |      | 4.4.1 Process Flow of TII Line Patterning with SiARC          | 51 |

|   |      | 4.4.2 Demonstration of Trench Patterning with TII             | 51 |

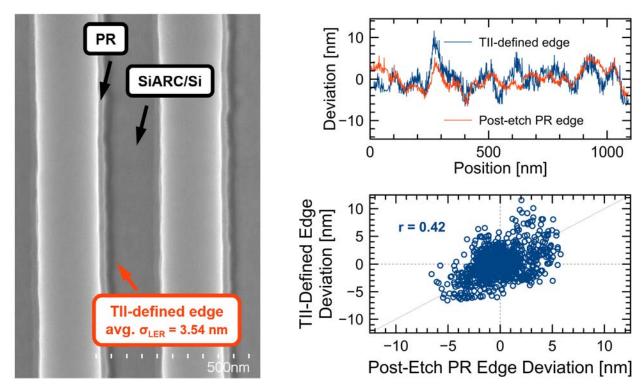

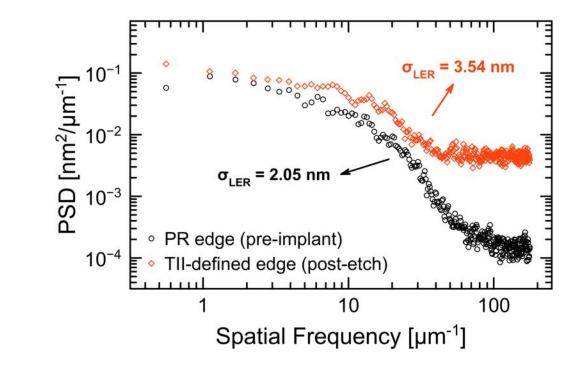

|   |      | 4.4.3 Plan-View LER and Edge Deviation                        | 52 |

|   |      | 4.4.4 Near-20 nm Feature Patterning via SiARC TII             | 54 |

|   |      | 4.4.5 Dual-Tone Patterning Using SiARC TII Process            | 54 |

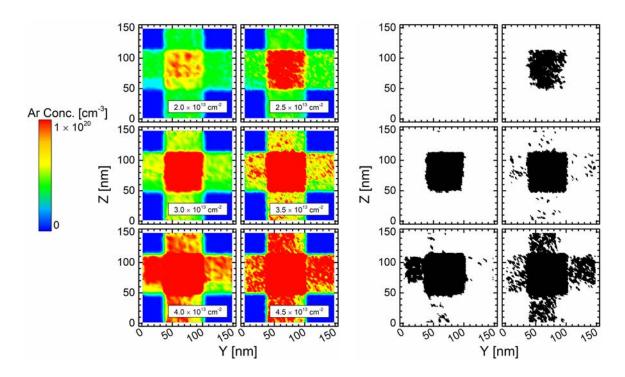

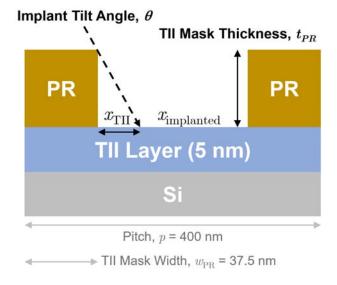

|   | 4.5  | Monte Carlo Simulations of TII Patterning                     | 58 |

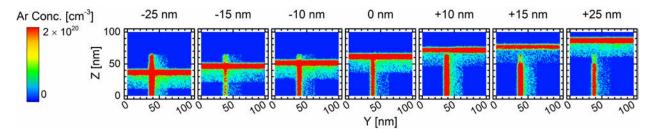

|   |      | 4.5.1 Two-Dimensional Patterning Concept                      | 58 |

|   |      | 4.5.2 Repeatability of TII-Based Patterning                   | 62 |

|   |      | 4.5.3 Effect of Mask-to-Mask Misalignment on Latent Image     | 62 |

|   |      | 4.5.4 Feasibility of Boolean Patterning                       | 63 |

|   |      | 4.5.5 LER Design Considerations                               | 63 |

|   | 4.6  | Conclusion                                                    | 66 |

|   |      | 4.6.1 Summary                                                 | 66 |

|   |      | 4.6.2 Future Work                                             | 66 |

| 5  | Con   | clusion     | 68 |

|----|-------|-------------|----|

|    | 5.1   | Summary     | 68 |

|    | 5.2   | Future Work | 69 |

| Bi | bliog | graphy      | 70 |

# List of Figures

| 1.1  | Flexible electronics market by application                                                                                   | 2   |

|------|------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2  | Comparison of TFT material system ratings for various material and processing properties                                     | ę   |

| 1.3  | Glass transition temperatures of common flexible electronics substrate materials.                                            | 4   |

| 1.4  | IoT connected device growth for different device types                                                                       | Ę   |

| 1.5  | Transistor count of manufactured processors as a function of time                                                            | 7   |

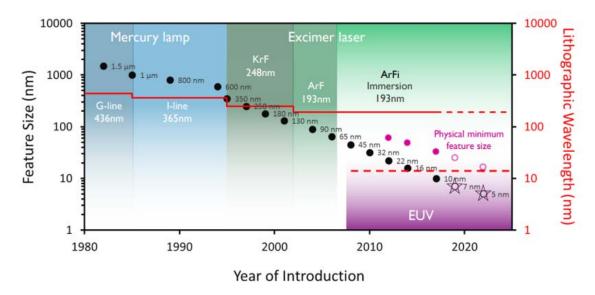

| 1.6  | Trend in optical lithography wavelength as a function of patterned feature size                                              | Ć   |

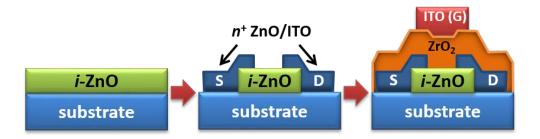

| 2.1  | Process schematics of ZnO TFT fabrication                                                                                    | 12  |

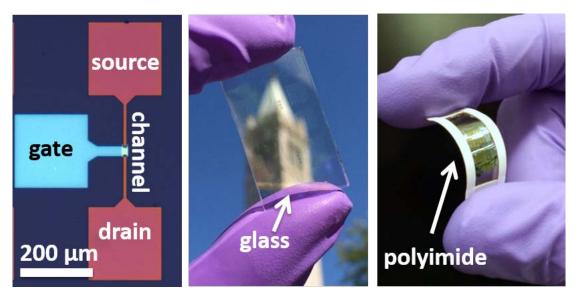

| 2.2  | Images of finished ZnO TFTs on silicon, glass, and freestanding polyimide foil                                               | 12  |

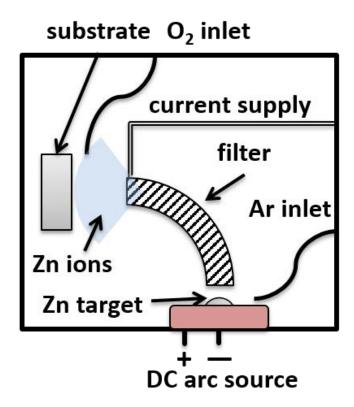

| 2.3  | Schematic of cathodic arc deposition chamber                                                                                 | 13  |

| 2.4  | Photograph of filtered cathodic arc deposition process of ZnO thin films                                                     | 14  |

| 2.5  | XRD spectra for ZnO films deposited at different $O_2$ flow rates                                                            | 15  |

| 2.6  | Surface roughness measurements of ZnO films deposited by filtered cathodic arc.                                              | 16  |

| 2.7  | Electron concentration $(n)$ , Hall mobility $(\mu)$ , and resistivity $(\rho)$ of ZnO films as                              |     |

|      | a function of $O_2$ flow rate                                                                                                | 17  |

| 2.8  | Dependence of the optical absorption of ZnO films with deposition $O_2$ flow rate.                                           | 18  |

| 2.9  | $I_{\mathrm{DS}}\text{-}V_{\mathrm{GS}}$ and $I_{\mathrm{DS}}\text{-}V_{\mathrm{DS}}$ curves for device on alkali-free glass | 19  |

| 2.10 | $I_{\mathrm{DS}}\text{-}V_{\mathrm{GS}}$ and $I_{\mathrm{DS}}\text{-}V_{\mathrm{DS}}$ curves for device on polyimide         | 22  |

| 2.11 |                                                                                                                              | 0.0 |

| 0.10 | bent                                                                                                                         | 23  |

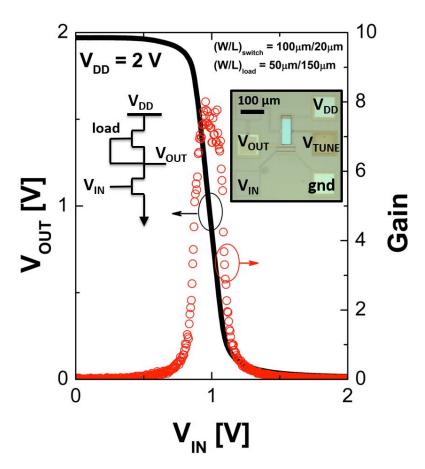

| 2.12 | Voltage transfer curve and DC gain of an all-oxide NMOS inverter on polyimide.                                               | 24  |

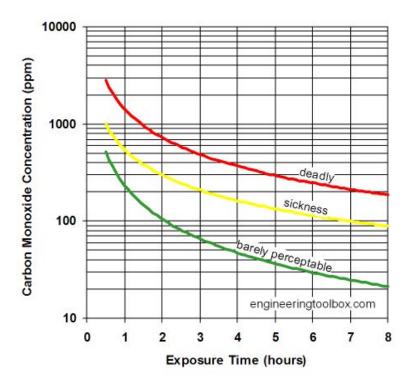

| 3.1  | Health effects of CO exposure as a function of exposure time and CO concentra-                                               |     |

|      | tion [60]                                                                                                                    | 27  |

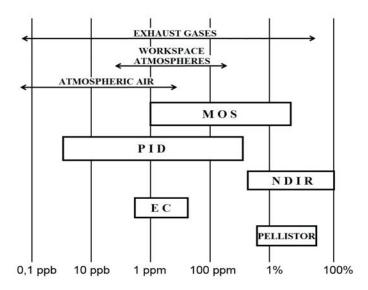

| 3.2  | Gas sensor types as a function of detection range and corresponding atmospheric and workplace concentrations [61]            | 27  |

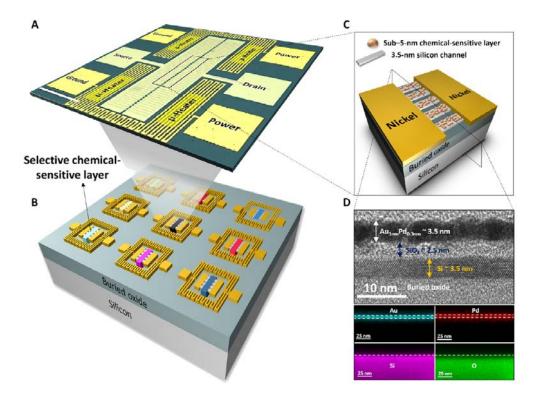

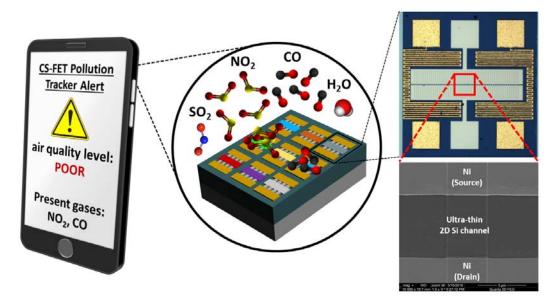

| 3.3  | Schematics and images of CS-FET chip and individual device [62]                                                              | 29  |

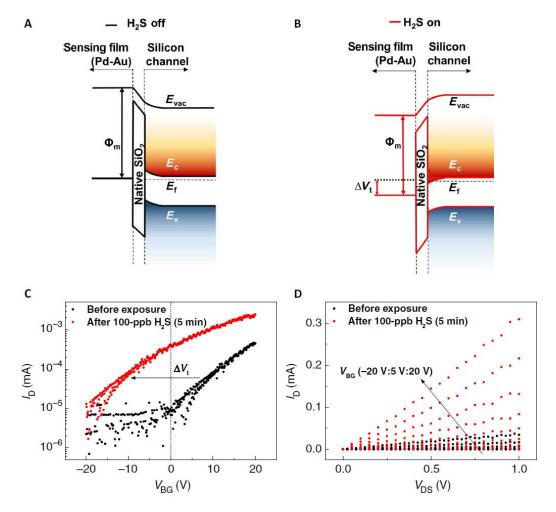

| 3.4  | Sensing mechanism of example CS-FET $H_2S$ sensor [62]                                                                       | 30  |

| 3.5  | Conceptual schematic of a CS-FET array integrated into a mobile phone for                                                    |     |

|      | personal pollution tracking                                                                                                  | 31  |

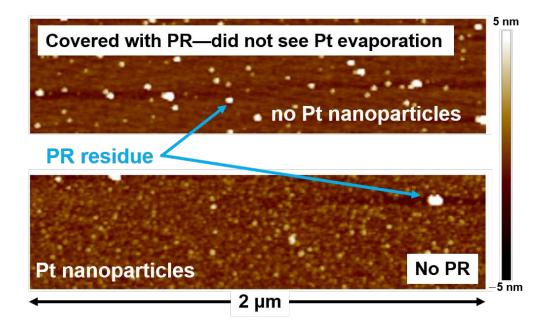

| 3.6  | AFM images of Pt nanoparticles deposited by electron beam evaporation                                                        | 32  |

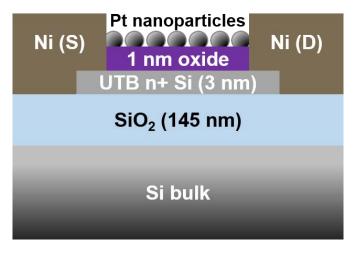

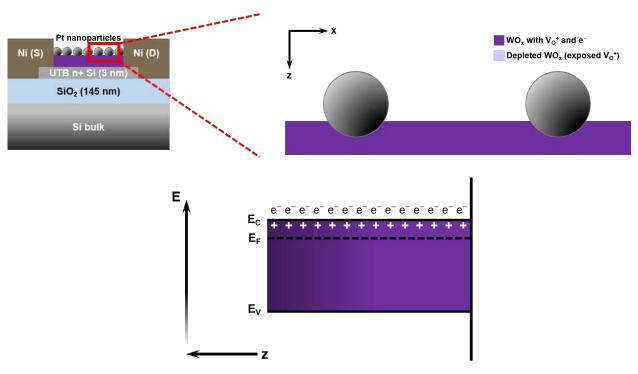

| 3.7  | Cross-sectional schematic of the CO sensor CS-FET structure                                                                  | 33  |

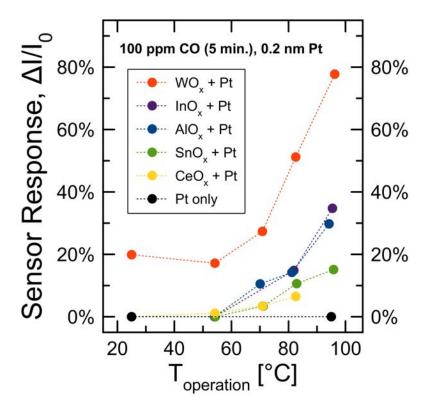

| 3.8   | CO sensor response as a function of operation temperature for different combinations of 1 nm thermally evaporated metal oxides and Pt nanoparticles 3               |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

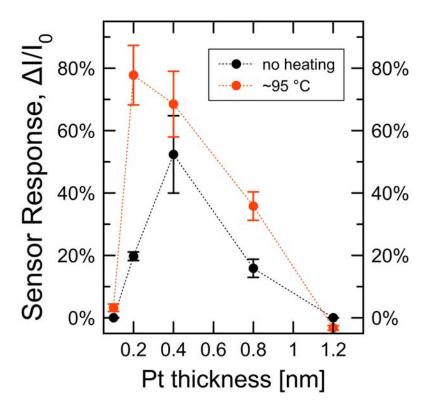

| 3.9   | Room temperature and heated CO sensor response as a function of electron beam                                                                                       |

|       | evaporated Pt thickness on a 1 nm $WO_x$ layer                                                                                                                      |

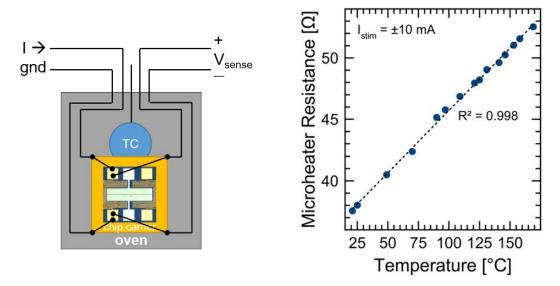

| 3.10  | Schematic of microheater resistance measurement and resulting resistance vs. temperature measurements and linear fit                                                |

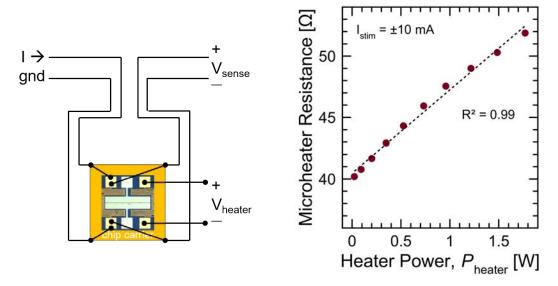

| 3.11  | Schematic of microheater resistance measurement and resulting resistance vs. heater power measurements and linear fit                                               |

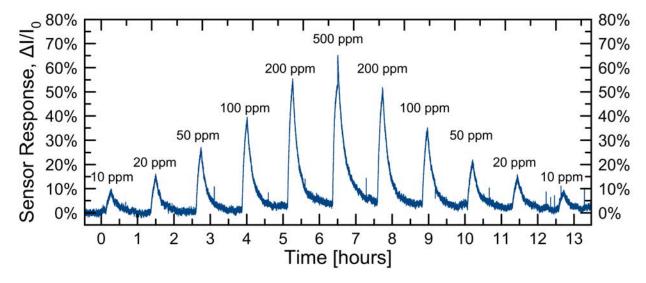

| 2 1 9 | Full range dynamic CO sensor response from 10 ppm to 500 ppm                                                                                                        |

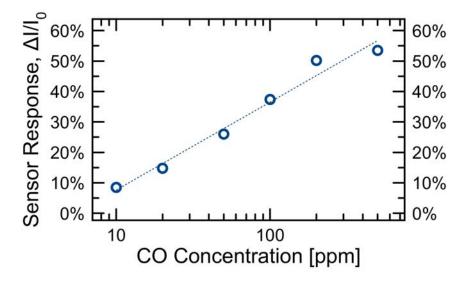

|       | Peak sensor response as a function of CO concentration extracted from Fig. 3.12.                                                                                    |

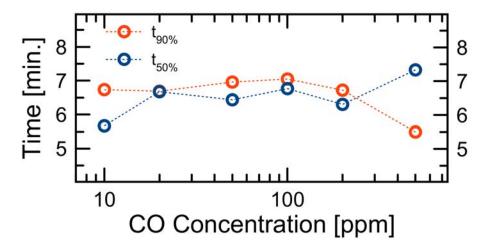

|       | Response time, $t_{90\%}$ , and recovery time, $t_{50\%}$ , of the CO CS-FET as a function of                                                                       |

|       | exposed CO concentration (10 min)                                                                                                                                   |

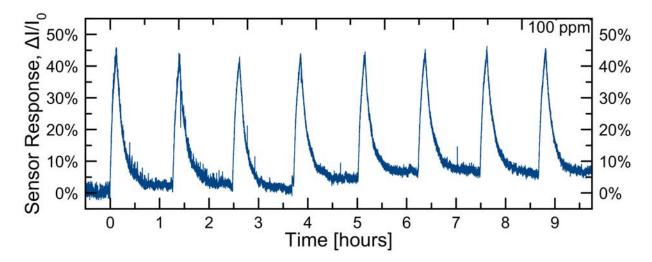

| 3.15  | Dynamic response of the sensing repeatability of the CO CS-FET 4                                                                                                    |

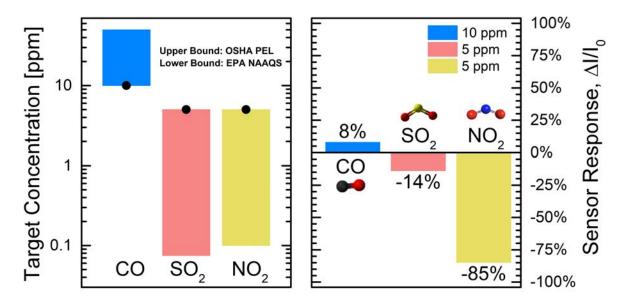

|       | Target NAAQS gases for selectivity tests and their corresponding CO sensor response                                                                                 |

| 3 17  | Dynamic sensor response to CO in varied relative humidity levels of and the                                                                                         |

| 0.17  | corresponding peak sensor response for each condition                                                                                                               |

| 2 12  | Enlarged cross-sectional schematic of the $WO_x + Pt$ sensing layer and corre-                                                                                      |

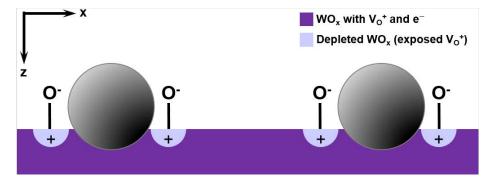

| J.10  | sponding energy band diagram of the $WO_x$ layer                                                                                                                    |

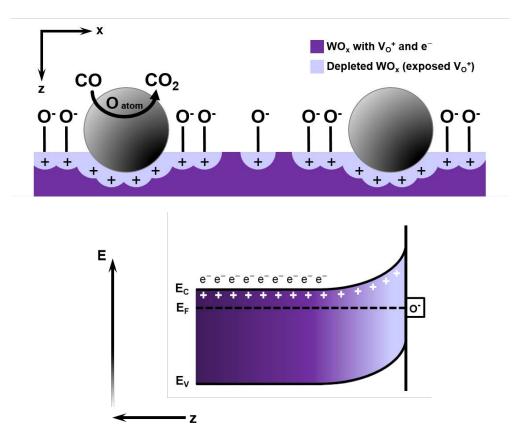

| 3.19  | Cross-sectional schematic representation of the adsorption of oxygen atoms onto                                                                                     |

|       | the surface of $WO_x$                                                                                                                                               |

| 3.20  | Cross-sectional schematic representation of the CO-induced increase of negatively-charged oxygen adsorption on the surface of $WO_x$ and an accompanying energy     |

|       | band diagram of the $WO_x$ depicting surface depletion                                                                                                              |

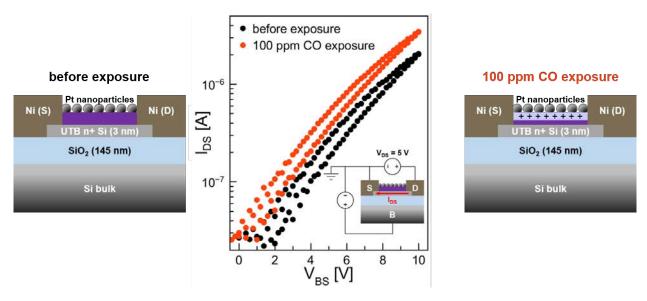

| 3.21  | Cross-sectional schematics of the $WO_x$ + Pt CS-FET before CO exposure and after 100 ppm CO exposure, creating depletion charges. Experimental $I_{DS}$ - $V_{BS}$ |

|       | curves before and after CO exposure indicate a shift in the $I_{\mathrm{DS}}\text{-}V_{\mathrm{BS}}$ curve due to                                                   |

|       | the presence of positive charges                                                                                                                                    |

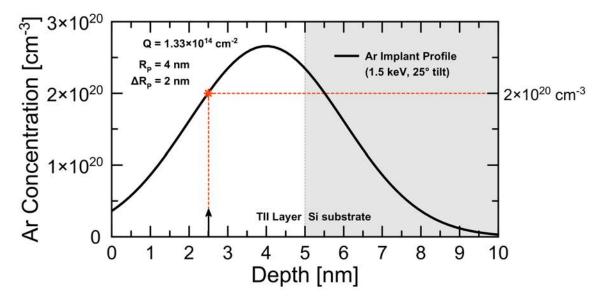

| 4.1   | Process flow for positive-tone and negative-tone TII patterning                                                                                                     |

| 4.2   | SRIM simulations of vacancy concentration depth profile for a 15 nm SiARC film                                                                                      |

|       | on a Si substrate after a 3 keV, 15° tilt Ar <sup>+</sup> implant for three different implant                                                                       |

|       | dose values                                                                                                                                                         |

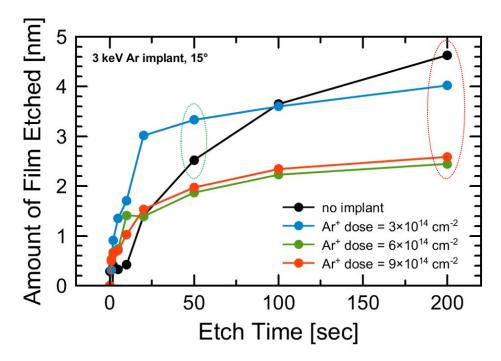

| 4.3   | Characterization of TII-induced SiARC wet etch rate changes, in 200:1 BHF                                                                                           |

|       | solution, for various Ar <sup>+</sup> implant doses                                                                                                                 |

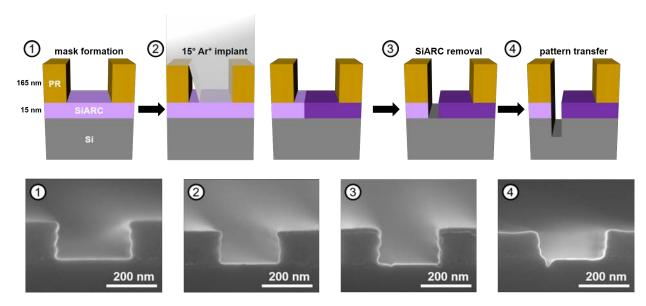

| 4.4   | Cross-sectional process flow schematics and corresponding SEMs of SiARC-based TII line patterning                                                                   |

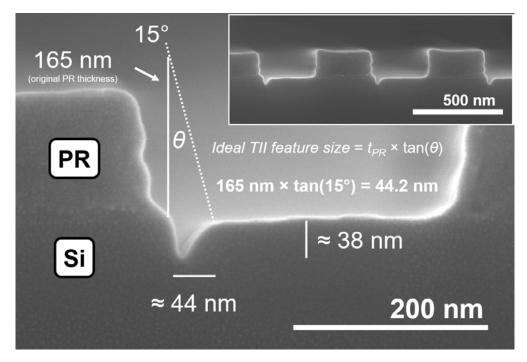

| 4.5   | Cross-sectional SEM of the final TII-defined ~44 nm feature                                                                                                         |

| 4.6   | Plan-view SEM image of TII-defined feature along a PR mask line pattern and                                                                                         |

| 4.0   | the corresponding edge deviation and correlation plots                                                                                                              |

| 4.7   | Power spectral density (PSD) comparison between DUV-patterned PR mask                                                                                               |

| 4.1   | edges and TII-defined edge                                                                                                                                          |

|       |                                                                                                                                                                     |

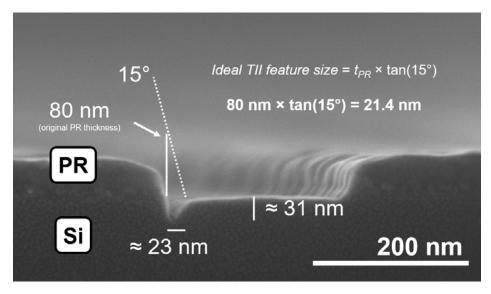

| 4.8  | Cross-sectional SEM of TII patterning process using an 80 nm-thick PR mask,       |    |

|------|-----------------------------------------------------------------------------------|----|

|      | reducing $x_{\text{TII}}$                                                         | 55 |

| 4.9  | Characterization of dual-tone TII-induced SiARC wet etch rate changes, in 200:1   |    |

|      | BHF solution, for various Ar <sup>+</sup> implant doses                           | 56 |

| 4.10 | Cross-sectional SEMs of positive- and negative-tone TII patterning with a single  |    |

|      | SiARC material                                                                    | 57 |

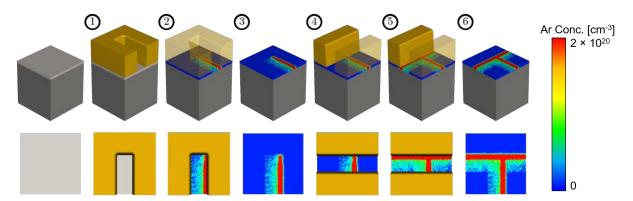

| 4.11 | Monte Carlo simulated isometric- and plan-view images illustrating how a 2D       |    |

|      | composite latent image can be formed in the TII layer by a sequence of two        |    |

|      | masked $1.5 \mathrm{keV} \mathrm{Ar^+}$ implants                                  | 58 |

| 4.12 | Ar concentration in TII layer after implantation and the resultant pattern of the |    |

|      | TII layer after etching                                                           | 59 |

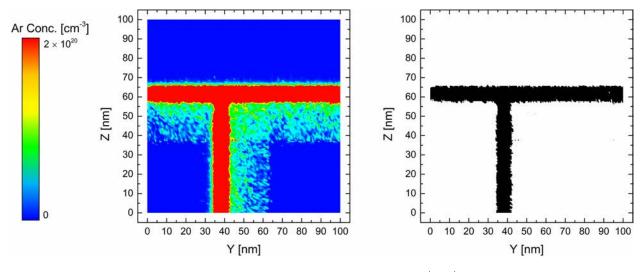

| 4.13 | SRIM vacancy concentration distribution as function of depth into a Si TII layer  |    |

|      | for a 1.5 keV Ar implantation at an angle of 25° and corresponding extreme value  |    |

|      | distribution function fit curve                                                   | 60 |

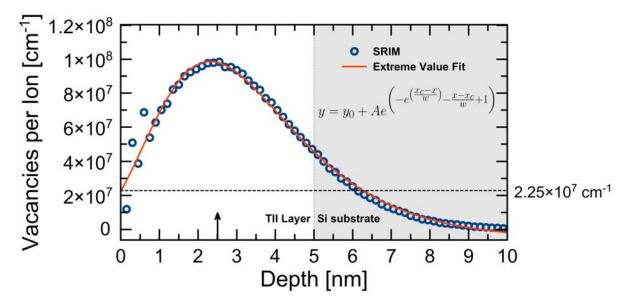

| 4.14 | Gaussian Ar implantation concentration profile as a function of depth into a TII  |    |

|      | layer for a 1.5 keV Ar implant at a tilt angle of 25°                             | 61 |

|      | Repeatability of 2D TII patterning assessed by latent image averaging             | 62 |

|      | Effect of mask-to-mask misalignment on latent image                               | 63 |

|      | Boolean 2D patterning using overlapping implantations                             | 64 |

|      | Cross-section schematic of simulated structure for TII-defined LER studies        | 64 |

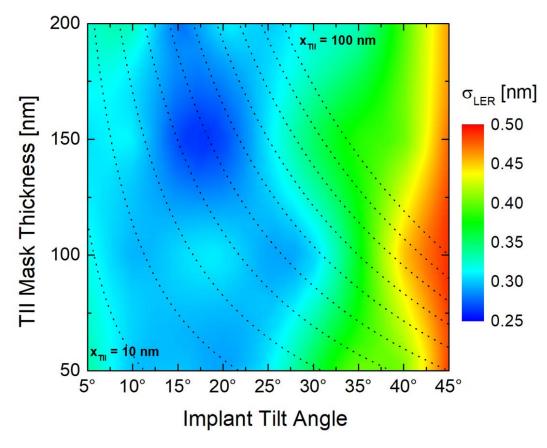

| 4.19 | Monte Carlo simulations of TII-defined LER as a function of mask thickness and    |    |

|      | implant tilt angle                                                                | 65 |

# List of Tables

| 1.1 | IDLH, PEL, and air quality gas concentrations for EPA-defined pollutant gases.                     | 6  |

|-----|----------------------------------------------------------------------------------------------------|----|

| 1.2 | IRDS projections for device half-pitch, physical gate length $(L_{\rm G})$ , and metal line        |    |

|     | half-pitch                                                                                         | 8  |

| 1.3 | $Comparison \ of \ patterning \ technologies' \ target \ feature/device \ and \ key \ challenges.$ | 9  |

| 2.1 | Comparison of this work to ZnO and IGZO TFTs previously reported in literature.                    | 21 |

### Acknowledgments

Academically, I want to thank my thesis advisor and dissertation chair, Prof. Tsu-Jae King Liu, for letting me join her group at the beginning of my sixth year, supporting me financially, providing project/writing input, and helping me graduate. I also want to thank Prof. André Anders for being a collaborator at LBNL and a pleasure to work with and talk to. I appreciate the work I have shared with many colleagues over my multi-group carousel of a Ph.D., and I hope I was able to return the favor. Many thanks to the DOE Office of Science for the fellowship for my first few years of grad school and to the amazing staff that ran the program that made me feel part of an academic family. Lastly, I am grateful for the countless positive student interactions I have had through my 100+ hours of GSI-ing and the unique teaching experiences I have had during my time here.

In particular, I want to thank Shirley Salanio, our department's Director of Graduate Matters, for literally everything. She was by far the most supportive person in our department's staff in every way possible, constantly providing encouragement, positivity, care, logistics info, personal emails, smiley faces, and an appreciation for who I am as a person. Thanks for being my biggest fan in EECS and for being with me every step of the way. I honestly would not have gotten through this program without you and cannot thank you enough.

And for everyone else in my life I have the pleasure of knowing outside of the lab (including some of those I also knew in the lab), I am incredibly thankful for the ideas, creativity, help, friendship, laughs, tears, memories, love, and support y'all have provided. Each of you, whether grad school friends, college friends, high school friends, best friends, or family, has been there for me in your own way that helped me get to where I am and be who I am today.

# Chapter 1

# Introduction

Within every process of electronic device fabrication and subsequent device use, there exists an inherent temperature limitation. This limitation can be part of a particular processing step or a target specification of device operation. To determine the temperature restrictions required by a device and its fabrication, the material system and target application of the resultant device must be assessed, as the thermal budget will vary based on both of these factors. If the temperature limit imposed on a device and its process becomes low enough, measures must be taken to ensure a reduction in thermal load is met without sacrificing the integrity of the constituent materials or the final device behavior. More specifically, these measures result in the development of low temperature materials deposition techniques, devices with reduced power consumption, or low temperature in-line processing techniques. In this dissertation, I will present solutions to circumvent temperature limitations in three areas: transparent flexible electronics, small-scale gas sensors for the Internet of Things (IoT), and back-end-of-line (BEOL) processing steps of state-of-the-art integrated circuits (ICs).

# 1.1 Flexible Electronics

# 1.1.1 Background & Motivation

The development of low-cost, widespread consumer electronics, combined with the introduction of wearable health monitoring systems, has created a need for devices based on materials other than traditional crystalline Si used in high-performance microprocessors. Common examples of this need are seen in modern television and mobile phone display systems as well as smart watches with integrated health sensors, utilizing materials systems such as amorphous Si (a-Si), low temperature polysilicon (LTPS), organic semiconductors, and semiconducting metal oxides. Most of these technologies are implemented using the thin-film transistor (TFT) as their driving technology due to its larger processing window, relaxed material quality constraints, and reduced cost compared to traditional transistors [1]. For example, the initial commercial uses of TFTs for pixel control in displays were based on an a-Si material

platform, but the need for improvement of particular device characteristics such as the offcurrent  $(I_{\text{OFF}})$  and the ratio of the on-current to the off-current  $(I_{\text{ON}}/I_{\text{OFF}})$ , on/off ratio) as well as material properties such as electron mobility (indicative of TFT switching speed, or display refresh rate) caused many industry vendors to turn to a TFT platform based on the quaternary metal oxide material indium-gallium-zinc oxide (IGZO) material system [1–3]. This switch is an example of the materials-focused research to create application-specific transistors for new electronics.

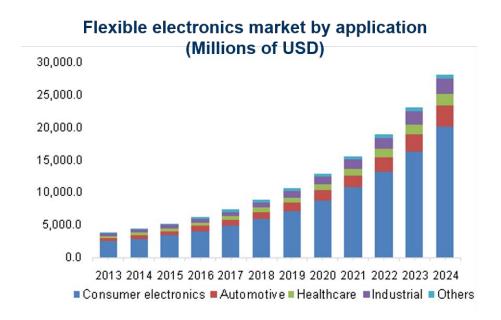

As these electronics become more integrated into our existing infrastructure, the market share for flexible electronics is projected to continually increase (Fig. 1.1). Given the diversity

Figure 1.1: Flexible electronics market by application [4].

of applications of flexible electronics, different areas may require the use of certain materials systems or have specific processing limitations. For example, flexible electronics on thin glass substrates have a less stringent thermal budget than plastics, allowing for different material deposition methods and processing conditions, and transparent electronics require using materials with minimal optical absorbance. Semiconducting metal oxides, such as IGZO, offer both high material quality at various deposition temperatures and optical transparency in the visible wavelengths, making them a strong candidate for future flexible electronics applications.

# 1.1.2 Semiconducting Metal Oxides

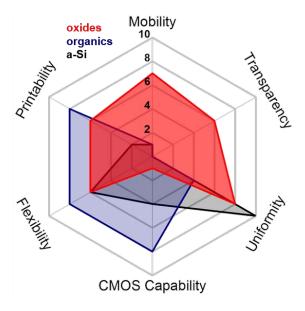

Each of the previously referenced material systems for TFTs (a-Si, LTPS, organics, metal oxides) possesses a subset of desirable material qualities, such as mechanical flexibility and

electron mobility, and processing requirements, such as low temperature deposition and large-scale thickness uniformity, but no system offers a universal solution to TFTs or flexible electronics. Fig. 1.2 provides a qualitative comparison of some of these materials. This

Figure 1.2: Comparison of TFT material system ratings for various material and processing properties, adapted from [3].

leads to materials selection based on the desired application. Given this work's target of high quality TFT performance for flexible transparent electronic applications, oxides are the chosen TFT channel material.

Most semiconducting metal oxides exhibit n-type behavior, making the capability of true complementary metal-oxide-semiconductor (CMOS) devices difficult, as they require both an n-type and p-type transistor. While the development of p-type oxides for TFT applications is an ongoing research direction, this issue is not addressed in this work, which instead focuses on the development of a novel n-type oxide deposition process for future integration into existing TFT systems such as displays, transparent electronics, and flexible electronics. While IGZO is the industry-favorite metal oxide TFT material, previous work on ZnO-based TFTs helped pioneer the field of oxide TFTs [1]. Additionally, given the deposition process used in this work, our process was inherently limited to a single oxide species rather than forming oxide compounds with more than one metal type.

# 1.1.3 Temperature Limitations

#### **TFT Channel Material**

Regardless of the chosen TFT channel material, deposition onto plastic substrates requires lower processing temperatures, leading to a degradation in material quality as compared to

a higher temperature process for the same material (i.e., loss of crystal structure with decreased deposition temperature leading to reduced electrical transport properties) [5]. While this is known to be circumvented by implementing post-deposition thermal treatment of thin films, such as an ambient air anneal step, many of these treatment processes can exceed the thermal budget restrictions of the substrate material [6–10]. This necessitates materials deposition processes that minimally reduce material quality when scaled to plastic-compatible temperatures and do not require post-deposition thermal treatment steps.

#### Flexible Substrate

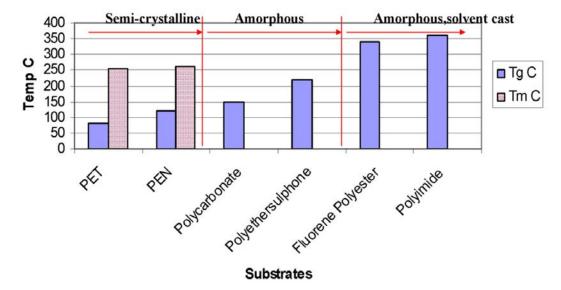

Specifically in terms of flexible electronics, the substrate material used is mechanically deformable, which is usually achieved by means of a thin plastic material. This limits the material and processing steps further by requiring the desired TFT material to be both mechanically robust and deposited at plastic-compatible temperatures. Given mechanical bending can be improved by thinning the substrate, which also helps reduce strain on subsequent layers, the temperature stability of the plastic material arises as the limiting factor of fabrication process steps [11]. Many different plastics can and have been used as flexible substrate materials, with the most common plastics used being polyethylene terephthalate (PET), polyethylene naphthalate (PEN), and polyimide (PI) (Fig. 1.3). Each plastic has its

Figure 1.3: Glass transition temperatures  $(T_g)$  of common substrate materials used in flexible electronics.  $T_m$  indicates the melting point for lower-thermal-budget materials [11].

own advantages and may be a more suitable choice depending on the application or processing requirements. For example, PET is known for having high optical clarity but may suffer from surface roughness issues due to its semi-crystalline character, whereas solvent cast PI has very low surface roughness but is not fully transparent in the visible light spectrum. In

this work, spin-cast PI is used for the plastic substrate material to benchmark our novel semiconducting oxide material deposition process due to its low surface roughness.

### 1.2 IoT Sensors

### 1.2.1 Background & Motivation

With the rise of IoT, the number of connected devices is projected to continually increase, with almost the majority of device increase coming from IoT devices (Fig. 1.4). This will lead to a growing network of sensors and control systems that will require integration into existing infrastructures and consumer electronics. IoT sensors are based on a mesh of devices that

Figure 1.4: IoT connected device growth for different device types [12].

exist separate from a main user interface, transmitting sensing data to a central location for monitoring. One of the specific IoT sensors under continued development is the gas sensor. While current gas monitoring systems exist, they do not have a form factor sufficient for mobile use or require high power supplies that limit the sensor to a nearby fixed power source. Therefore, the future of IoT gas sensors requires minimal power consumption and small form factor in order to successfully integrate with mobile electronics.

#### 1.2.2 Pollutant Gases

Among the plethora of gases to detect, one subset of interest is that of pollutant gases. These gases can affect both the natural environment in which they are being produced as well as have adverse health effects on the people who are exposed to too much pollution. The Environmental Protection Agency (EPA) has established the National Ambient Air Quality Standards (NAAQS) to identify the major pollutant gases and their respective concentration values that are not to be exceeded if air quality is to be maintained [13]. Table 1.1 indicates these values along with the National Institute for Occupational Safety and Health (NIOSH)

and Center for Disease Control (CDC) defined workplace permitted exposure limit (PEL) and immediately dangerous to life and health (IDLH) gas concentration values of the NAAQS pollutant gases: carbon monoxide (CO), sulfur dioxide (SO<sub>2</sub>), nitrogen dioxide (NO<sub>2</sub>), and ozone (O<sub>3</sub>).

Table 1.1: IDLH, PEL, and air quality gas concentrations for EPA-defined pollutant gases [13, 14].

| Pollutants and<br>Exposure Levels | СО                                                                | $\mathrm{SO}_2$                    | $\mathrm{NO}_2$                  | $O_3$                             |

|-----------------------------------|-------------------------------------------------------------------|------------------------------------|----------------------------------|-----------------------------------|

| IDLH                              | $1200\mathrm{ppm}$                                                | $100\mathrm{ppm}$                  | $20\mathrm{ppm}$                 | 5 ppm                             |

| PEL                               | $50\mathrm{ppm}$                                                  | $5\mathrm{ppm}$                    | $5\mathrm{ppm}$                  | $0.1\mathrm{ppm}$                 |

| NAAQS                             | $35 \mathrm{ppm} (1 \mathrm{h}) \\ 9 \mathrm{ppm} (8 \mathrm{h})$ | $0.075\mathrm{ppm}\ (1\mathrm{h})$ | $0.1\mathrm{ppm}\ (1\mathrm{h})$ | $0.07\mathrm{ppm}\ (8\mathrm{h})$ |

### 1.2.3 Temperature Limitations

The target sensing gas, along with the sensing mechanism of the device itself, dictates the inherent power and/or temperature limitations for successful operation. In the case of an IoT sensor, these would need to be minimized, as high power consumption would require the sensor power supply to either be large or replaced often. Gas sensors based on a chemical reaction (i.e., gas oxidation or reduction) are typically enhanced with heating, as additional heat enhances the reaction rate, leading to faster sensing. However, heating needs to be minimized in order to conserve power. Many in-home sensors may require heating of sensing elements up to 300 °C which is not practical for standalone sensors or for sensors integrated into mobile electronics. Therefore, IoT pollutant gas sensors need to implement a sensor architecture that has an inherently high sensitivity, as reducing the operation temperature will make accurate detection of low gas concentrations more difficult.

# 1.3 Integrated Circuit Fabrication

# 1.3.1 Background & Motivation

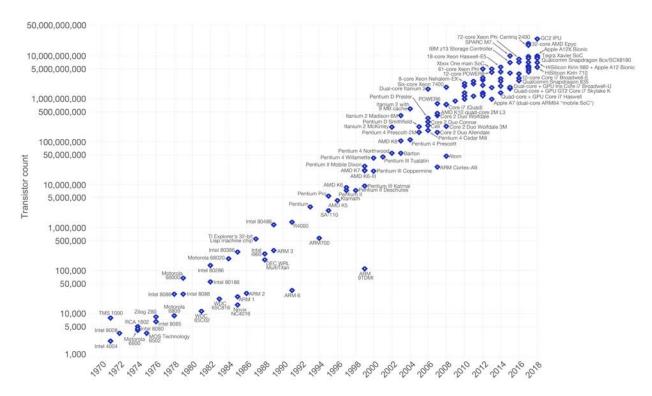

#### Moore's Law

The trend of Moore's Law states the number of transistors on a chip doubles every two years, fueling the continued scaling of transistors for increased device density as well as lower cost per function (Fig. 1.5) [15]. The evolution of transistors over the past few decades has seen devices reach nanometer-scale dimensions, orders of magnitude smaller than their predecessors. Scaling to such feature sizes uncovers many nonidealities in transistor behavior, such

Figure 1.5: Transistor count of manufactured processors as a function of time [16].

as those seen in device performance degradation via short channel effects [17]. To circumvent this, designers have implemented novel fabrication schemes and device architectures such that these detrimental effects can be mitigated while maintaining the overall goal of increased transistor density and increased on-current [17, 18].

In addition to physical transistor dimensions, subsequent layers during fabrication, such as metal line layers, also have scaling requirements of their own. The International Roadmap for Devices and Systems (IRDS) predicts that by as early as four years from now, we will reach dimensions for which manufacturable solutions are not known (Table 1.2) [19]. While portions of the device architecture, such as transistor half-pitch, are projected to be scaled using novel transistor layouts (i.e., transitioning from fins to lateral channel gate-all-around, LGAA, to vertical channel gate-all-around, VGAA), many feature sizes of chip fabrication do not have in-place solutions. This fast-approaching need for patterning technologies with minimum feature sizes beyond current capabilities presents an immediate need for alternative lithographic approaches.

# 1.3.2 Patterning Technologies

While the continued scaling and novel device structures have enabled scaling of Si transistors to nanometer-scale dimensions, these processes and feature sizes are inherently limited by the patterning technologies used during fabrication. Therefore, as device dimensions con-

Table 1.2: IRDS projections for device half-pitch, physical gate length  $(L_{\rm G})$ , and metal line half-pitch. DRAM, HP, and MPU stand for dynamic random access memory, high performance, and microprocessor unit, respectively. Yellow cells indicate parameters for which manufacturable solutions are known but high volume manufacturing has not been developed. Red cells indicate parameters for which manufacturable solutions are not known.

| Year of Production                 | 2017 | 2019 | 2021 | 2024   | 2027 | 2030 | 2033 |

|------------------------------------|------|------|------|--------|------|------|------|

| DRAM min. ½ pitch [nm]             | 18   | 17.5 | 17   | 14     | 11   | 8.4  | 7.7  |

| HP Logic physical $L_{\rm G}$ [nm] | 20   | 18   | 16   | 14     | 12   | 12   | 12   |

| MPU metal $1/2$ pitch [nm]         | 18   | 14   | 12   | 10.5   | 7    | 7    | 7    |

| Transistor ½ pitch [nm]            | 16   | 14   | 12   | 10.5   | 9    | 7    | 7    |

| , r[]                              | (fi  | n)   |      | (LGAA) |      | (VG  | AA)  |

tinue to shrink, so do the minimum resolutions of the utilized patterning mechanisms. The most commonly used lithography technology used in industry has been optical photolithography based on mercury lamps ultraviolet (UV) and excimer laser deep ultraviolet (DUV) light sources [20]. Over the past handful of decades, smaller feature sizes in patterned device layers have been achieved via the use of light sources with decreasing wavelengths as well as immersion-based systems to decrease the numerical aperture of the exposure tool (Fig. 1.6) [21].

In addition to optical patterning, multiple patterning or pitch-halving techniques such as self-aligned double and quadruple patterning (SADP and SAQP, respectively) used in conjunction with photolithography have been adopted by industry for further dimension scaling past the lithographic limit [22, 23]. At the same time, much progress has been made in the area of using light with wavelengths approximately an order of magnitude lower than previous exposure wavelengths, referred to as extreme ultraviolet (EUV) lithography, with single-exposure patterns on the order of 14 nm having been demonstrated [22]. The adoption of EUV lithography for high volume manufacturing is in place for existing foundries in the coming years [24].

Despite the industrial adoption of techniques such as multiple patterning and EUV lithography, each technique is not without its own challenges. Additionally, competing technologies, such as nanoimprint lithography and directed self-assembly, offer their own advantages and drawbacks for nanometer-scale patterning (Table 1.3). Common challenges among these technologies include cycle time, cost, line-edge roughness (LER), and defectivity. Thus, a future patterning technology that can achieve high-fidelity nanometer-scale patterns at low cost and processing time is requisite for further transistor scaling.

Figure 1.6: Trend in optical lithography wavelength as a function of patterned feature size [20].

Table 1.3: Comparison of patterning technologies' target feature/device and key challenges [19].

| Patterning Technology            | Target Feature                                                                               | Key Challenges                                                                      |

|----------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Multiple Patterning $> 4 \times$ | vias, contact, cut<br>patterns                                                               | edge placement errors,<br>overlay, long cycle time,<br>cost                         |

| EUV                              | 22/24 nm half<br>pitch contact<br>holes, cuts; BEOL<br>metals (18 nm)                        | tool uptime, defectivity,<br>resist speed combined with<br>LER and stochastics      |

| Nanoimprint                      | $20\mathrm{nm}\ \mathrm{line/space},\ 20/30\ \mathrm{nm}\ \mathrm{half}$ pitch contact holes | defectivity, overlay, master template writing/inspection, template replication      |

| Directed Self-Assembly           | $rac{	ext{contact holes/cut}}{	ext{levels, nanowire}}$                                      | pattern placement,<br>defectivity and defect<br>inspection, design, 3D<br>metrology |

# 1.3.3 Temperature Limitations

#### **BEOL Process Steps**

A uniquely difficult feature to process is that of the back-end-of-line (BEOL) metal line half-pitch, as it will soon require sub-10 nm line widths and requires that all processing steps do not exceed ~400 °C to avoid unwanted effects on underlying device layers (i.e., resistance increase of metal vias) [25]. With a BEOL-limited process temperature hundreds of degrees lower than processing steps used in the initial device layer fabrication steps, combined with the stringent requirement of low cost high-fidelity nanometer-scale patterning, an alternative low temperature fabrication process is needed.

### 1.4 Dissertation Structure

First, in Chapter 2, a novel method of metal oxide material deposition for flexible thin film transistors (TFTs) will be discussed. Materials characterization indicates this material is of high quality suitable for flexible electronics, demonstrated via fabrication of fully transparent all-oxide flexible TFTs. Second, in Chapter 3, a chip-integratable pollutant gas sensor based on silicon transistors is discussed. Transistor-based gas sensing leverages IC manufacturing and enables low temperature operation, allowing for lower power consumption carbon monoxide sensors for air quality monitoring and personal pollution tracking. Lastly, Chapter 4 will present a novel low cost fully-BEOL-compatible nanoscale patterning method based on tilted ion implantation and conventional deep ultraviolet (DUV) lithography. Utilizing silicon-containing spin-on films, patterns on the order of 20 nm are achieved, providing an alternative lithographic method for state-of-the-art transistor fabrication with nanoscale features.

# Chapter 2

# All-Oxide Transparent, Flexible Electronics

# 2.1 Materials for Oxide-Based Flexible TFTs

As previously discussed, metal oxides have the material quality and process capability to be utilized in high quality TFTs for consumer electronics and wearable applications. Transparent and flexible electronics represent two emerging fields that have much traction for future technological applications [26–28]. Traditional thin-film transistors fabricated from polysilicon and amorphous silicon and later from organic semiconductors and carbon nanotubes enabled the realization of large-scale flexible circuits for display and sensor applications [29– 36. More recently, the family of semiconducting post-transition metal oxides (ZnO, In<sub>2</sub>O<sub>3</sub>, InZnO, InGaZnO, etc.) offers an additional platform with wide energy band gaps for optical transparency over the full visible range, room temperature deposition (both solution-based and physical vapor deposition techniques) for plastic substrate compatibility, and electronic properties suitable for TFTs for transparent, flexible, and bio-related applications [6, 37–41]. However, many existing fabrication techniques for these oxide TFTs, while they are being deposited at room temperature, require higher temperature annealing steps to prime the oxide (i.e., improve crystallinity, improve stoichiometry, or calcination of solutions) for TFT use or to improve the device performance to an acceptable level [6–10]. Unfortunately, the use of higher temperatures for processing and device improvement can severely limit substrate compatibility and present challenges for integration with other components. In order to retain a wide range of substrate choices without sacrificing device performance, a low temperature fabrication scheme is needed. In this work, we demonstrate fully transparent all-oxide based ZnO TFTs with low operational voltages fabricated using a room temperature deposition method with no post-processing annealing and a maximum device processing temperature of 110 °C.

The schematic process flow for the fabrication of top-gated ZnO TFTs is shown in Fig. 2.1. ZnO TFTs are fabricated on three different substrates: i) a reference silicon wafer substrate

Figure 2.1: Process schematics of ZnO TFT fabrication.

with a 50 nm thick thermal oxide, ii) transparent alkali-free borosilicate glass, iii) flexible polyimide foil (Fig. 2.2). Substrates are cleaned with acetone and isopropyl alcohol and blown dry with nitrogen. Substrates are then loaded into a cathodic arc vacuum deposition chamber and pumped down to  $\sim 5 \times 10^{-6}$  Torr for ZnO deposition. The filtered cathodic arc deposition for zinc oxide has originally been developed for the deposition of transparent conducing oxide films [42]. It has been shown that this deposition technology is similar to pulsed laser deposition (PLD) as it produces a flux of energetic ions. The typical Zn ion energy is  $36 \, \text{eV}$  [43] which leads to local heating right at the film growth region without imposing a large heat load to the substrate. Additionally, in contrast to magnetron sputtering, negative oxygen ions are not accelerated to very high energies of several 100 eV because the arc operates at low arc voltage (the potential difference between anode and cathode is less than 40 V).

Figure 2.2: Optical microscope image of finished device on silicon (left), photograph of finished device array on glass slide (center), and photograph of finished devices on freestanding polyimide foil bent between fingers (right).

# 2.2 Filtered Cathodic Arc Deposition

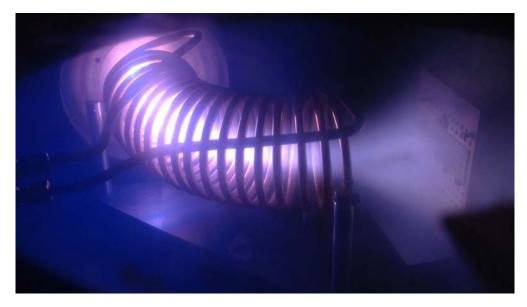

Cathodic arc deposition (Fig. 2.3) uses a relatively low DC voltage to trigger and sustain a metal arc plasma, where the discharge current of about 50 A is concentrated in non-stationary cathode spots [44]. In contrast to the former work on AZO [42], here we use a pure (undoped) zinc (99.99%) cathode. It is surrounded by an annular grounded anode body. A permanent ring magnet is placed at the bottom part of the cathode cone: its purpose is to steer the moving arc spots around the cathode, enabling efficient material use and spreading of the heat load on the cathode. The zinc plasma generated at cathode spots streams away from the cathode into the curved macroparticle filter coil. The purpose of the coil is to guide the plasma to the substrate, which is not in line-of-sight with the cathode. In doing so, the plasma particles (electrons and ions) are separated from the microscopic but relatively massive zinc droplets, also known as "macroparticles." The coil is made of hollow, watercooled copper tubing. It operates at a constant current of 400 A, producing a magnetic field of the order of 100 mT (more details on plasma guiding and macroparticle removal can be found in Ref. [44]). Zn ions react with oxygen dosed into the deposition chamber via a mass flow controller to form a ZnO film on the near-room-temperature substrate surface. Fig. 2.4 shows a photograph of a ZnO deposition process via filtered cathodic arc.

Figure 2.3: Schematic of cathodic arc deposition chamber. The permanent magnet is denoted in red.

Figure 2.4: Photograph of filtered cathodic arc deposition process of ZnO thin films.

# 2.3 All-Oxide TFT Fabrication Process

For the start of the fabrication process, 30 nm of ZnO is deposited as the active TFT channel material onto the substrates placed 12.5 cm away from the exit of the plasma macroparticle filter coil in a 5 mTorr O<sub>2</sub>/Ar ambient (O<sub>2</sub> 60 sccm, Ar 20 sccm unless otherwise stated). Photolithography is used to define patterns for the source and drain electrodes via liftoff. Source and drain pads consist of 40 nm-thick degenerately doped ZnO deposited at lower O<sub>2</sub> partial pressure than the TFT channel ZnO (5 mTorr, O<sub>2</sub> 20 sccm, Ar 20 sccm, room temperature), followed by 30 nm of indium tin oxide (ITO) sputtered in a 7 mTorr Ar ambient also at room temperature. A second photolithography step is performed to define the ZnO channel region of the transistors by etching in hydrochloric acid (HCl 1% for 1s). In this process, the top ITO film on the source and drain serves as an etch stop barrier for the underlying ZnO, as the etch rate for ITO in HCl is much lower than that of ZnO [45]. A 20 nm-thick ZrO<sub>2</sub> top gate oxide is deposited by atomic layer deposition (ALD) at a maximum temperature of 110 °C, and subsequently patterned by photolithography. The same ITO sputtering and lift-off process is then used to define the top gate contact. Fig. 2.2 shows optical images of the devices completed on silicon, alkali-free glass, and free-standing polyimide foil, respectively.

# 2.4 ZnO Materials Characterization

### 2.4.1 Structural Characterization

#### X-ray Diffraction

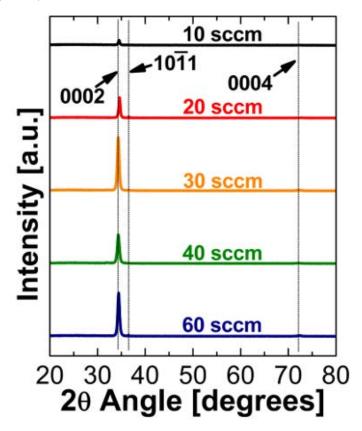

We first explore the material properties of ZnO thin films deposited by cathodic arc. X-ray diffraction spectra (XRD) of the ZnO films for various O<sub>2</sub> flow rates are shown in Fig. 2.5. All

Figure 2.5: XRD spectra for ZnO films deposited at different O<sub>2</sub> flow rates.

films exhibit a polycrystalline hexagonal wurtzite structure and  $\{0002\}$  texture in agreement with literature [46]. The c-axis lattice constant extracted from the 0002 peak at 34.8° is 5.2 Å in good agreement with values for sputtered ZnO films [47]. No peaks corresponding to metallic Zn inclusions are detected. Estimating the grain size from the 0002 peak positions,  $2\theta$ , and full-width half-maximum widths,  $\beta$ , using the Scherrer equation

$$D(2\theta) = \frac{K\lambda}{\beta\cos 2\theta} \tag{2.1}$$

assuming a crystallite shape factor K = 0.9 and substituting  $\lambda = 0.154$  nm for the wavelength of Cu K $\alpha$  radiation, yields grain sizes between  $\sim 17-23$  nm [48].

#### **Atomic Force Microscopy**

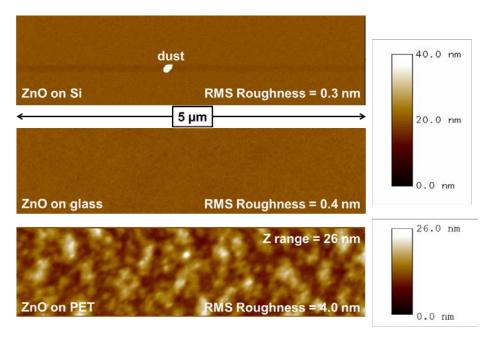

Additionally, the surface roughness of the ZnO films was characterized via atomic force microscopy (AFM). Film roughness was assessed for ZnO films deposited on glass, Si, and ~250 µm-thick free-standing polyethylene terephthalate (PET) substrates (Fig. 2.6). The resulting measurements indicate the ZnO film is quite smooth, with the roughness of each film closely matching the roughness of its underlying substrate.

Figure 2.6: Surface roughness measurements of ZnO films deposited by filtered cathodic arc on Si (top), glass (middle), and PET (bottom).

#### 2.4.2 Electrical Characterization

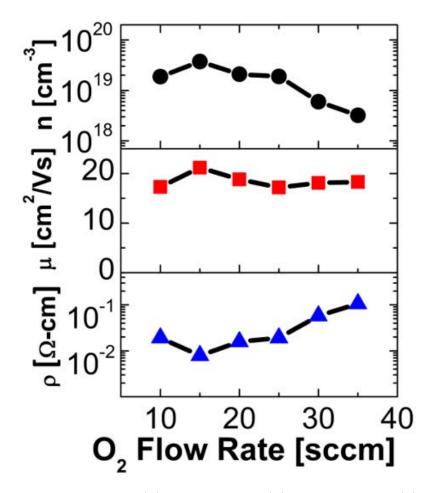

For transistor application, it is important to precisely control the conductivity of the ZnO channel to enable gate control. The carrier concentration in the ZnO film can be tuned by adjusting the O<sub>2</sub> flow rate during deposition as the carrier concentration of intrinsic ZnO films directly correlates with the number of oxygen vacancies [46, 49]. We chose to keep the Ar flow rate and the total deposition pressure constant (20 sccm and 5 mTorr, respectively) and vary the O<sub>2</sub> flow rate from 10 sccm to 35 sccm to modulate the electron concentration in the ZnO. As the O<sub>2</sub> flow rate is increased from 15 sccm to 35 sccm, the electron concentration drops from the mid-10<sup>19</sup> cm<sup>-3</sup> range to the low 10<sup>18</sup> cm<sup>-3</sup> range (Fig. 2.7), while the Hall mobility (second panel in Fig. 2.7) essentially remains constant between 17.3–21.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, with the highest recorded mobility of 21.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> being deposited at an O<sub>2</sub> flow rate of 15 sccm. For the higher O<sub>2</sub> flow rates above 35 sccm, the resistivity of the films (third panel

Figure 2.7: Electron concentration (n), Hall mobility  $(\mu)$ , and resistivity  $(\rho)$  of ZnO films as a function of  $O_2$  flow rate.

in Fig. 2.7) increases too rapidly, rendering Hall measurements unreliable on our setup. However, the ZnO mobilities reported here appear to be some of the highest Hall mobilities for room-temperature-deposited thin film oxides for TFTs reported in literature, showing that cathodic arc deposition is reliable for producing high quality ZnO films [6, 38–40, 50, 51].

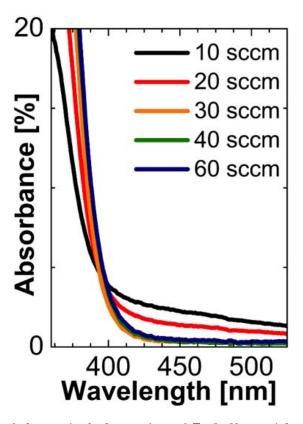

# 2.4.3 Optical Characterization

The ZnO films were optically characterized with transmission and reflection measurements in the visible and UV light wavelength range. Fig. 2.8 shows the optical absorption of the ZnO films as a function of wavelength for various  $O_2$  flow rates. As the  $O_2$  flow rate increases from 10 sccm to 30 sccm, the sub-bandgap absorption at wavelengths longer than 400 nm decreases significantly. This is caused by metallic Zn clusters becoming embedded in the film. Too low of an  $O_2$  flow rate prevents present Zn particles from reacting with

Figure 2.8: Dependence of the optical absorption of ZnO films with deposition O<sub>2</sub> flow rate.

the ambient oxygen, causing Zn particles to remain and provide trap states that reduce the absorption. Increasing the  $O_2$  flow rate reduces the number of unreacted Zn particles, thusly reducing the number of trap states and decreasing the absorption. The absorbance of 30 nm ZnO films in this spectral range drops below 2%. In parallel, the absorption edge at wavelengths shorter than 400 nm shifts to longer wavelengths for increasing  $O_2$  flow rates due to the decreasing electron concentration. This effect is attributed to the reduction of the Burstein-Moss shift, which decreases the optical bandgap as the Fermi level lowers with decreasing electron concentration. These findings are consistent with our Hall measurement results. Absorbance data for  $60 \, \text{sccm} \, O_2$  which is the  $O_2$  flow rate used for the ZnO TFT channel, is practically identical to the data for  $40 \, \text{sccm}$  although film resistivity further increases.

# 2.5 ZnO-Based All-Oxide TFT Performance

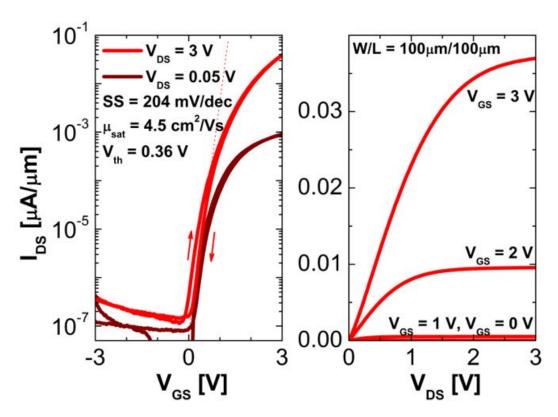

#### 2.5.1 Alkali-Free Glass Substrate

Fig. 2.9 shows the drain to source (DS) and gate to source (GS)  $I_{\rm DS}$ - $V_{\rm GS}$  transfer curves of a TFT device on alkali-free glass with channel width and length of 100 µm, operated at  $V_{\rm GS}=\pm 3\,{\rm V}$  and  $V_{\rm DS}=3\,{\rm V}$ , resulting in an on/off current ratio of  $\sim 10^5$ . The subthreshold slope (SS) is calculated from a linear fit (dotted line) to be SS = 204 mV dec<sup>-1</sup>. The threshold voltage of  $V_{\rm t}=0.36\,{\rm V}$  was extracted from a linear fit of  $I_{\rm DS}^{-1/2}$  vs.  $V_{\rm GS}$ . The saturation mobility was determined to be  $\mu_{\rm sat}=4.5\,{\rm cm}^2\,{\rm V}^{-1}\,{\rm s}^{-1}$ , calculated using the peak value of the slope of the  $I_{\rm DS}^{-1/2}$  vs.  $V_{\rm GS}$  plot under  $V_{\rm DS}=3\,{\rm V}$  saturation operation and a capacitance-voltage (CV) extracted gate oxide capacitance of  $C_{\rm ox}=597\,{\rm nF}\,{\rm cm}^{-2}$ . Fig. 2.9 shows the  $I_{\rm DS}$ - $V_{\rm DS}$  characteristic of the device, exhibiting typical square-law behavior and reaching an on-current of almost 40 nA µm<sup>-1</sup>. These values compare well with the best reported oxide

Figure 2.9:  $I_{\rm DS}$ - $V_{\rm GS}$  (left) and  $I_{\rm DS}$ - $V_{\rm DS}$  (right) curves for  $W/L=100\,\mu{\rm m}/100\,\mu{\rm m}$  device on alkali-free glass. The arrows on the transfer curves indicate the direction of the double sweep measurement.

low temperature TFTs in literature with SS typically in the range of one hundred to a few hundreds of mV dec<sup>-1</sup> and  $V_t$  less than 1 V [51–57]. It should be noted that alkali-free glass is chosen due to impurities in other glasses, such as microscopy slides. We found that charged

ions in the glass were causing a threshold voltage shift of our devices, so alkali-free glass was used to avoid this issue. Additionally, the off-current of our devices is comparable to those reported in literature, showing that the room-temperature process is able to produce devices with just as low of an off-current as compared to those with higher temperature processes. In terms of the saturation mobility, our lower values as compared to literature can be associated with interface states between the  $ZrO_2$  gate oxide and ZrO channel overlap capacitances between the gate and source/drain, which would cause some of the applied gate field to contribute to state filling and source/drain charges rather than channel inversion, as well as contact resistance effects. These effects can be combated by annealing or plasma treatments for the oxide interfaces and improved alignment during fabrication to reduce the overlap capacitances. Again, seeing that we are avoiding any higher temperature or post-annealing to improve the gate-channel interface, future work should look into plasma treatment to enhance the  $ZrO_2$ -ZrO interface.

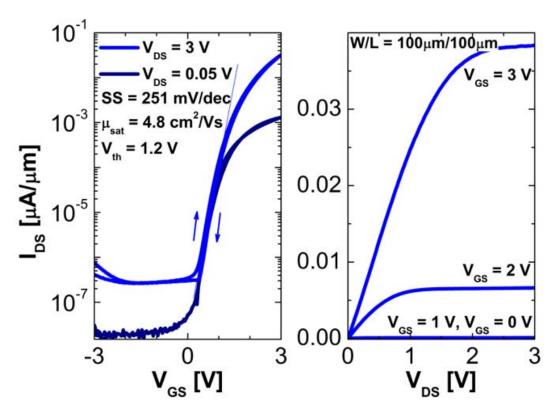

### 2.5.2 Polyimide Substrate

The TFT fabrication process was then ported to flexible polyimide foils. Polyimide resin was spun on a temporary silicon handling wafer and cured at 300°C for an hour before device fabrication. Fig. 2.10 shows the  $I_{DS}$ - $V_{GS}$  transfer curve of the ZnO TFT on polyimide with channel width and length of 100 µm operated at  $V_{\rm GS}=\pm3\,{\rm V}$ , exhibiting an on/off current ratio of almost 10<sup>5</sup>, with extracted subthreshold slope, threshold voltage, and saturation mobility of SS = 251 mV dec<sup>-1</sup>,  $V_{\rm t} = 1.2$  V, and  $\mu_{\rm sat} = 4.8$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively. Fig. 2.10 shows the  $I_{\rm DS}$ - $V_{\rm DS}$  curves indicating expected square-law behavior with an on-current of almost 40 nA μm<sup>-1</sup>, thus reaching identical performance characteristics to the device on glass and with those reported in literature. For each of the  $I_{DS}$ - $V_{GS}$  curves on the two substrates, the increase in off-current at low  $V_{\rm GS}$  operation can be attributed to gate leakage resulting from both the thin 20 nm gate oxide and the source/drain to gate overlap. The steepness of the subthreshold slope can also be restricted by trap states in the channel-oxide interface, energy band tail states of the ZnO, and contact resistance effects from the ITO contacts to the ZnO channel. The on/off ratio is 10<sup>5</sup> at 3 V operation, whereas other studies report ratios as high as  $10^8$  [52, 53]. Since the focus of this project is on low voltage operation for digital circuits, we are unable to directly compare the low voltage operation performance of some of the referenced TFTs with higher on/off ratios at higher operation voltages. This is because the referenced devices are operated at voltages of  $V_{\rm GS}$  and  $V_{\rm DS} \geq 10 \, \rm V$ , while ours are run at a  $V_{\rm GS}$  and  $V_{\rm DS}=3\,{\rm V}$ . Overall, the devices made on glass and polyimide show consistent, transferable and reproducible behavior, suggesting the cathodic arc deposition method to be a universally applicable technique for creating fully-transparent ZnO TFTs on a variety of substrates. Table 2.1 summarizes our results for the ZnO TFT on polyimide and compares this device to other high-performance oxide TFTs reported in literature.

was reported, with the accompanying  $V_{\rm DS}$  voltage being the highest of the reported  $V_{\rm op}$  value. It should be noted that Table 2.1: Comparison of this work (denoted with \*) to previously reported ZnO and IGZO TFTs.  $V_{\rm op}$  and W/L denote the operation voltage and channel size of the published device, respectively. Max T refers to the maximum temperature used during device processing, excluding substrate preparations.  $V_{\rm op}$  refers to the gate voltage range in which the device transparency is defined as all components of the transistor, including the gate, source/drain contacts, and the substrate altogether be transparent.

| Material                                       | ZnO*     | ZnO [10]  | ZnO [55]                     | ZnO [56]   | ZnO [57]    | IGZO [52]  | IGZO [53] | IGZO [54]  |

|------------------------------------------------|----------|-----------|------------------------------|------------|-------------|------------|-----------|------------|

| Dep. Method                                    | CAD      | PLD       | sol-gel                      | sputtering | solution    | sputtering | sol-gel   | sputtering |

| $\mathrm{On}/\mathrm{off}$ ratio               | $10^{5}$ | $>10^{4}$ | $10^{4}$                     | $> 10^4$   | $> 10^4$    | $<10^{7}$  | $10^{8}$  | $< 10^{8}$ |

| $V_{ m op} \ [{ m V}]$                         | #3       | -1-4      | 0-3                          | ±1.5       | -1-3        | ±20        | ±10       | #3         |

| SS [mV/dec]                                    | 251      | 250       | $\approx 300 \text{ (est.)}$ | 180        | 250         | 200        | 95.8      | 09         |

| $V_{ m t} \left[ { m V}  ight]$                | 1.2      | 2         | 0.7                          | 0.1        | 0.1         | 23         | 2.7       | 0.5        |

| $\mu_{\rm sat} \ [{\rm cm^2  V^{-1}  s^{-1}}]$ | 3.1      | 0.024     | 3.4                          | 0.45       | 22.1        | 11         | <10.5     | 10         |

| M/L                                            | 100/100  | 2000/50   | 1500/100                     | 500/50     | N/A         | 400/100    | 100/10    | 1000/5     |

| $\operatorname{Max} T [^{\circ}C]$             | 110      | 200       | 280                          | 200        | 150         | RT         | 150       | 325        |

| Transparent?                                   | Yes      | Yes       | No                           | No         | No          | Yes        | No        | No         |

| Flexible?                                      | Yes      | No        | Yes                          | Yes        | $N_{\rm O}$ | No         | Yes       | No         |

Figure 2.10:  $I_{\rm DS}$ - $V_{\rm GS}$  (left) and  $I_{\rm DS}$ - $V_{\rm DS}$  (right) curves for  $W/L=100\,\mu{\rm m}/100\,\mu{\rm m}$  device on polyimide. The arrows on the transfer curves indicate the direction of the double sweep measurement.

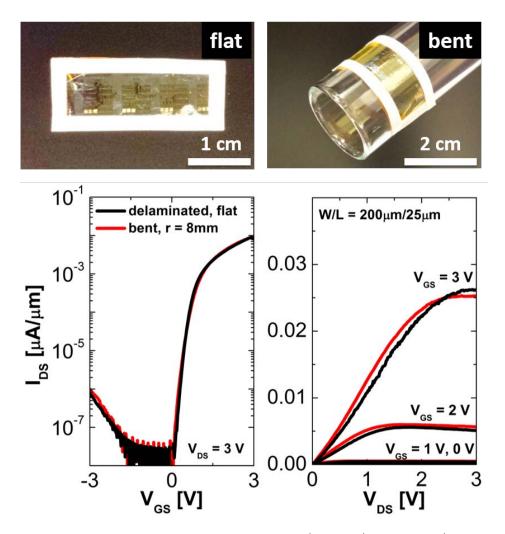

#### 2.5.3 Performance of Bent TFT

With the focus of these TFTs being on applications in flexible electronics, bending studies are performed to get an idea of the mechanical robustness and its effect on the electrical performance of the device. To remove the polyimide from the handle wafer, the polyimide was cut around the edges and then submerged into DI water for twenty minutes. Putting the sample in water promotes self-delamination of the polymer from the substrate. This process prevents the polyimide from needing to be manually peeled off, which induces strain on the polymer, potentially cracking the fabricated devices. Once the polyimide has delaminated, the polyimide foil is laid flat, and the devices are measured to quantify possible effects from internal strain relaxation during delamination. Bending tests are then performed by wrapping the polyimide around a test tube with  $r=8\,\mathrm{mm}$  and measuring the device performance while bent. Fig. 2.11 shows the  $I_{\mathrm{DS}}$ - $V_{\mathrm{DS}}$  and  $I_{\mathrm{DS}}$ - $V_{\mathrm{DS}}$  curves for the  $W/L=200\,\mathrm{\mu m}/25\,\mathrm{\mu m}$  device after peeling off the handle wafer before bending and while bent. This device geometry is chosen for its higher output current values. The on-current of the device drops almost one order of magnitude during delamination, which may be attributed to defects created in the device during strain relaxation of the polyimide film upon delamination. However, while

Figure 2.11: Photographs of the substrate while flat (top left) and bent (top right) around a test tube with  $r = 8 \,\mathrm{mm}$ .  $I_{\mathrm{DS}}\text{-}V_{\mathrm{GS}}$  (bottom left) and  $I_{\mathrm{DS}}\text{-}V_{\mathrm{DS}}$  (bottom right) curves for  $W/L = 200 \,\mathrm{\mu m}/25 \,\mathrm{\mu m}$  device on freestanding polyimide (black) and bent at  $r = 8 \,\mathrm{mm}$  (red).

bent at  $r = 8 \,\mathrm{mm}$ , there is minimal change in device performance, proving that our ZnO TFT process is not only universally applicable to various substrates but also mechanically robust for flexible electronics.

# 2.6 Demonstration of NMOS Inverter

Furthermore, to demonstrate the applicability of this process to integrated logic systems, we have fabricated an inverter gate. Due to these devices being solely NMOS, the inverter was constructed with a depletion-mode transistor load rather than a PMOS device or resistor. Henceforth, the transistor in which the input  $(V_{\text{IN}})$  is passed is referred to as the "switching"

transistor," whereas the depletion-mode transistor, whose gate terminal is connected to the inverter output node  $(V_{\rm OUT})$ , is referred to as the "load transistor." The switching voltage of the inverter only depends on the  $V_{\rm t}$  of the switching transistor since the load transistor is acting as the resistive load, so the supply voltage to the inverter  $(V_{\rm DD})$  was chosen to maximize the inverter noise margin. At an input voltage of  $V_{\rm IN}=0\,\rm V$ , the switching transistor is off and has a much greater resistance than the load transistor. Thus,  $V_{\rm OUT}$  tends toward  $V_{\rm DD}$ , logic 1. Upon the onset of inversion, the switching transistor changes from the off-state to the on-state. As the switching transistor turns on, the resistance of the switching transistor becomes comparable to and then much less than that of the load transistor, causing  $V_{\rm OUT}$  to be pulled to ground, logic 0. Fig. 2.12 shows the transfer characteristics of the inverter at  $V_{\rm DD}=2\,\rm V$  as well as an optical image and circuit schematic of the device. The contact pads have been labeled for convenience. It should be noted that the purpose of the  $V_{\rm TUNE}$

Figure 2.12: Voltage transfer curve  $(V_{\rm OUT}$  vs.  $V_{\rm IN})$  and DC gain  $(|\partial V_{\rm OUT}/\partial V_{\rm IN}|)$  of the all-oxide NMOS inverter on polyimide under an operation voltage  $V_{\rm DD}=2\,\rm V$ . The switching transistor has a  $W/L=100\,\mu\rm m/20\,\mu\rm m$ , and the depletion-mode load transistor has a  $W/L=50\,\mu\rm m/150\,\mu\rm m$ . Inset is a schematic representing the device layout as well as the corresponding optical image of the device with labeled contacts.

pad is to adjust the  $V_{\rm t}$  of the load transistor so that it serves as a resistive load device. Also plotted is the DC gain of the inverter, defined as  $|\partial V_{\rm OUT}/\partial V_{\rm IN}|$ , which is shown to reach  $\approx 8$ . Additionally, the noise margins of the inverter were extracted from the transfer curve by taking the maximum low input voltage  $(V_{\rm LI})$  and the minimum high input voltage  $(V_{\rm HI})$ , corresponding to the input voltages at unity gain, and the corresponding output values of those inputs,  $V_{\rm HO}$  and  $V_{\rm LO}$ , respectively. The high and low input noise margins are then defined as  $NM_{\rm H} = V_{\rm HO} - V_{\rm HI}$  and  $NM_{\rm L} = V_{\rm LO} - V_{\rm LI}$ , respectively. The noise margin values were calculated as  $NM_{\rm H} = 0.36\,V_{\rm DD}$  and  $NM_{\rm L} = 0.33\,V_{\rm DD}$ .

# 2.7 Conclusion

## 2.7.1 Summary

In conclusion, a filtered cathodic arc deposition technique is demonstrated for room temperature deposition of intrinsic ZnO with electrical and optical quality suitable for transparent transistor applications. Additionally, this method of ZnO deposition has been shown to be usable in the fabrication of all-oxide fully transparent transistors on alkalki-free glass and polyimide with comparable or better electrical performance to alternative TFT platforms and existing oxide TFTs. Bending studies were performed to show the mechanical robustness of the device structure to confirm its potential use on flexible substrates. Additionally, further processing shows the material from cathodic arc deposition can be used for digital logic by creating a working inverter gate entirely out of oxides. Overall, this work demonstrates a low temperature fabrication process for ZnO TFTs enabling use in both fully transparent and flexible electronic applications.

#### 2.7.2 Future Work

In future work, such a process could be ported to other flexible plastics with much lower thermal budget than polyimide, such as PET or PEN. Device performance improvements can be achieved by creating better channel-oxide interfaces and decrease series resistance issues, which will help with the gate control of the device and boost device mobility and on/off ratio. Additionally, lower temperature gate oxides via ALD or solution processing will be explored to lower the processing temperature to its lowest limit of 90 °C, as determined by photolithography. Previous research by colleagues should be noted for the development of an e-skin platform based on carbon nanotubes [35, 58, 59], which requires uniform TFTs for pixel backplane addressing as well as large-scale digital circuits for on-chip pixel addressing and simple data manipulation. Continued development of this ZnO device platform will enable use in future e-skin applications as an emerging flexible, large-area systems for backplanes and circuits on various flexible substrates.

# Chapter 3

# Silicon Transistor-Based Gas Sensors

# 3.1 Existing Carbon Monoxide Sensing Technology

CO is a prevalent pollutant gas that, in higher concentrations, is known to have immediate lethal effects. The danger of CO exposure is related to both the present CO concentration and exposure time. For example, according to Fig. 3.1, exposure to a CO concentration of 200 ppm for one hour is barely perceptible, whereas exposure to the same concentration over the course of eight hours can be lethal [60]. The variation in both gas concentration and exposure time shapes the sensor design space needed to appropriately detect or monitor CO gas.

For pollutant levels of CO, the minimum detection limit is close to ~10 ppm, representing the maximum eight hour exposure limit for sensitive people groups (i.e., people with respiratory issues or those of old age) as determined by NAAQS [13]. Traditionally, metal oxide semiconductor (MOS) sensors suffer from high detection limit or require high temperature operation (≥200 °C) to detect low gas concentration values, making them good candidates for in-home detection of dangerous levels of CO but not for remote/mobile applications for consumer electronics requiring low power operation [61]. Electrochemical (EC) sensors are known for their high sensitivity and low power operation, enabling their integration into existing home monitoring electronics, but the physical form factor requiring a chamber with electrolyte solution does not allow for IC chip-level integration for mobile applications. Optical-based methods of detection such as photoionization detectors (PID) and non-dispersive infrared (NDIR) sensors have their respective gas concentration operation regimes but similarly suffer from scalability. Fig. 3.2 indicates general concentration ranges of various sensor types along with approximate gas concentration ranges for atmospheric air, work space environments, and exhaust gases.

With a target of on-chip integration for our gas sensor technology, the main issues of scalability, temperature operation, detection dynamics (including lowest detection limit and response/recovery time) need to be addressed. To accomplish this, we focus on the integration of MOS sensor capability into existing fabrication processes. More specifically,

Figure 3.1: Health effects of CO exposure as a function of exposure time and CO concentration [60].

Figure 3.2: Gas sensor types as a function of detection range and corresponding atmospheric and workplace concentrations [61].

the application of metal oxides to existing transistor fabrication processes allows for direct integration of gas sensors into a chip-level package for mobile sensing.

## 3.2 Chemical-Sensitive FET

The development of a Si transistor-based gas sensor, referred to as a chemical-sensitive field effect transistor (CS-FET), replaces the gate oxide and metal gate elements of a transistor with a material that is chemically sensitive to a target gas, creating a traditional MOSFET that experiences current modulation via a chemically-induced process rather than a pure electrostatic potential [62]. Integrating the known low power operation and exponential current change of transistors along with the capability of metal oxide-based CO sensing provides a unique sensor design architecture allowing for high sensitivity detection at lower temperatures than existing MOS-based sensors.

#### 3.2.1 Device Fabrication