# Design, Development and Applications of Portable Field Emission Devices

Nishita Deka Vivek Subramanian Kristofer Pister

Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-224 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-224.html

December 1, 2021

Copyright © 2021, by the author(s).

All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

by

#### Nishita Deka

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Vivek Subramanian, Chair Professor Kristofer Pister Professor Alex Zettl

Fall 2019

## Design, Development and Applications of Portable Field Emission Devices

Copyright 2019 by Nishita Deka

#### Abstract

Design, Development and Applications of Portable Field Emission Devices

by

#### Nishita Deka

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Vivek Subramanian, Chair

Vacuum tubes were integral to the rise of electronics in the 20<sup>th</sup> century, enabling the development of many core technologies, such as radar, television, radio and audio communications and early computers. However, the invention of the solid-state transistor, and subsequent integrated circuit technology, meant that electronics could be smaller, cheaper, faster and more reliable than vacuum tubes. Because of this, vacuum tubes were ultimately superseded by solid-state devices and thus began the trend of rapid miniaturization of electronics. Interestingly, although solid-state devices supplanted vacuum tubes in most domains, the trend towards miniaturization also enabled the emergence of vacuum microelectronics – a field that uses modern solid-state microfabrication techniques to develop micrometer-scale vacuum-based devices, or field emission devices. The emergence of this field was motivated by the desire to leverage some of the unique performance advantages offered by vacuum-based devices. Indeed, vacuum as an electron conduction medium offers some unique technical advantages over solid-state transport, such as ballistic electron transport, the ability to operate at high frequencies and robustness in harsh conditions, such as extreme temperatures, extreme pressures and high radiation environments. However, in order to leverage these features and enable widespread and practical use of field emission devices in electronics, on-chip ambient operation device architectures directly integrated on Si must be designed.

Here, the design and application of portable field emission devices that can operate in ambient conditions will be presented and discussed. This includes the first demonstration of vacuum-sealed fully integrated diode and triode field emission arrays that are developed in a scalable, BEOL-compatible process directly on Si. The device architectures demonstrate effective vacuum-sealing and gate-modulated field emission, with the ability to block voltages of up to 200 V. High operating voltages and low currents make these devices useful in high voltage drive circuits for MEMS actuators. Then, a novel device architecture for a portable electron source is presented. A fabrication process is developed to integrate graphene as an extraction electrode for field emission arrays on Si. Operation of this device is the first demonstration

of a fully integrated field emission array utilizing graphene as both an extraction electrode and electron-transparent vacuum seal, enabling in-air extraction of electrons. The type of on-chip portable electron source developed here presents a unique method for using field emission-based electron sources in non-ideal conditions, unlocking applications ranging from ion thrusters for microrobotics to environmental microscopy.

To those who struggle with anxiety, and to those who support them

# Contents

| $\mathbf{C}$  | onter | nts                                                                | ii   |

|---------------|-------|--------------------------------------------------------------------|------|

| $\mathbf{Li}$ | st of | Figures                                                            | iv   |

| Li            | st of | Tables                                                             | viii |

| 1             | Intr  | roduction                                                          | 1    |

|               | 1.1   | Historical overview of vacuum microelectronics                     | 1    |

|               | 1.2   | Field emission fundamentals                                        | 3    |

|               |       | 1.2.1 Electron emission                                            | 3    |

|               |       | 1.2.2 Fowler-Nordheim tunneling theory                             | 4    |

|               |       | 1.2.3 Modifications to the Fowler-Nordheim equation                | 7    |

|               | 1.3   | Applications of vacuum microelectronics                            | 7    |

|               |       | 1.3.1 High voltage devices for MEMS actuators                      | 8    |

|               |       | 1.3.2 Portable electron sources                                    | 9    |

|               | 1.4   | Methodology of study                                               | 10   |

|               | 1.5   | Organization                                                       | 11   |

| 2             | Dio   | de Field Emission Arrays: Design, Fabrication and Characterization | 12   |

|               | 2.1   | Background information                                             | 12   |

|               | 2.2   | Device fabrication                                                 | 14   |

|               |       | 2.2.1 Process flow                                                 | 14   |

|               |       | 2.2.2 Process characterization                                     | 16   |

|               |       | 2.2.3 Key features of final geometry                               | 18   |

|               | 2.3   | Results and discussion                                             | 20   |

|               |       | 2.3.1 Experimental setup                                           | 20   |

|               |       | 2.3.2 On-state performance and trends                              | 20   |

|               |       | 2.3.3 Current drivability and limitations                          | 24   |

|               |       | 2.3.4 Off-state performance and trends                             | 26   |

|               |       | 2.3.5 Design guidelines                                            | 26   |

|               | 2.4   |                                                                    | 30   |

| 3  | Tric                       | ode Field Emission Arrays: Design, Fabrication and Characterization 3: |  |  |  |

|----|----------------------------|------------------------------------------------------------------------|--|--|--|

|    | 3.1                        | Introduction                                                           |  |  |  |

|    | 3.2                        | Background information                                                 |  |  |  |

|    | 3.3                        | Device fabrication                                                     |  |  |  |

|    |                            | 3.3.1 Process flow                                                     |  |  |  |

|    |                            | 3.3.2 Process characterization                                         |  |  |  |

|    |                            | 3.3.3 Key features of final geometry                                   |  |  |  |

|    | 3.4                        | Results and discussion                                                 |  |  |  |

|    |                            | 3.4.1 Experimental setup                                               |  |  |  |

|    |                            | 3.4.2 Output characteristics                                           |  |  |  |

|    |                            | 3.4.3 Transfer characteristics                                         |  |  |  |

|    |                            | 3.4.4 Low temperature measurements                                     |  |  |  |

|    |                            | 3.4.5 Design guidelines                                                |  |  |  |

|    | 3.5                        | Conclusions                                                            |  |  |  |

| 4  | Dor                        | table Electron Sources: Design, Fabrication and Characterization 49    |  |  |  |

| 4  | 4.1                        | Design considerations                                                  |  |  |  |

|    | 1.1                        | 4.1.1 Role of field emission devices                                   |  |  |  |

|    |                            | 4.1.2 Role of graphene                                                 |  |  |  |

|    | 4.2                        | Device fabrication                                                     |  |  |  |

|    | 1.2                        | 4.2.1 Cathode preparation                                              |  |  |  |

|    |                            | 4.2.2 Graphene preparation                                             |  |  |  |

|    |                            | 4.2.3 Transfer process                                                 |  |  |  |

|    |                            | 4.2.4 Process characterization                                         |  |  |  |

|    | 4.3 Results and discussion |                                                                        |  |  |  |

|    | 1.0                        | Results and discussion                                                 |  |  |  |

|    |                            | 4.3.2 Atmospheric sealing                                              |  |  |  |

|    |                            | 4.3.3 Electron transparency                                            |  |  |  |

|    |                            | 4.3.4 In-air extraction of electrons                                   |  |  |  |

|    |                            | 4.3.5 Design guidelines                                                |  |  |  |

|    |                            | 4.3.6 Comparison to metal-sealed field emission arrays                 |  |  |  |

|    | 4.4                        | Conclusions                                                            |  |  |  |

| 5  | Cor                        | nclusions 99                                                           |  |  |  |

| 9  | 5.1                        |                                                                        |  |  |  |

|    | $5.1 \\ 5.2$               | Summary                                                                |  |  |  |

|    | 5.2                        |                                                                        |  |  |  |

|    |                            | 5.2.1 Applied research       9         5.2.2 Basic research       9    |  |  |  |

|    |                            | 5.2.2 Dasic research                                                   |  |  |  |

| Bi | bliog                      | graphy 98                                                              |  |  |  |

# List of Figures

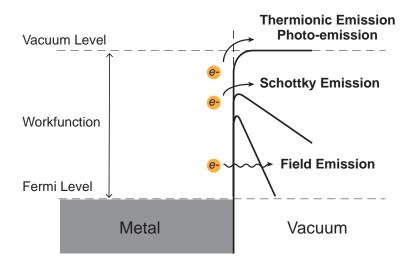

| 1.1  | Various types of electron emission, adapted from [11]                                                                                                                                                                                                                                                                                                                                                            | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

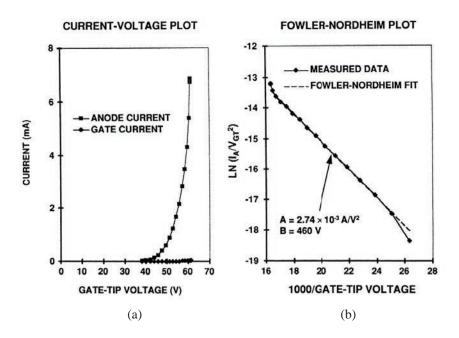

| 1.2  | Representative (a) current-voltage and (b) FN plot for a microfabricated field emitter array [16]                                                                                                                                                                                                                                                                                                                | 6  |

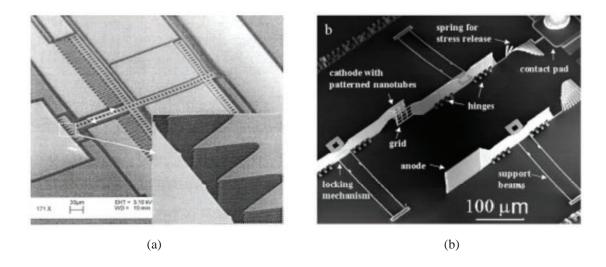

| 1.3  | Examples of field emission devices built using MEMS design and fabrication principles. (a) Microelectromechanical field emission device (MEMFED) composed of lateral field emission tips with a cathode-anode separation that can be mechanically tuned using a comb-drive actuator [17]. (b) Carbon nanotube-based microtriode developed using silicon micromachining and assembled via polysilicon hinges [18] | 8  |

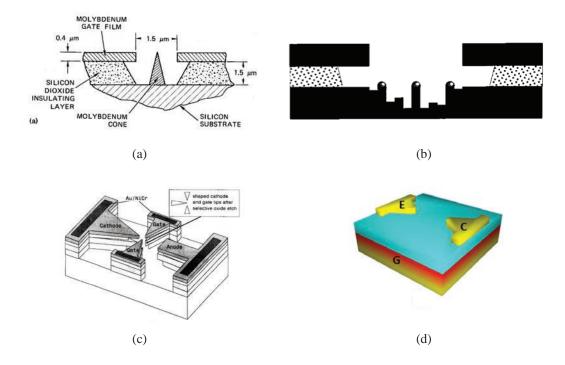

| 2.1  | Examples of vertical and lateral field emission devices. Vertical designs include (a) metal tips, such as the Spindt-tip cathode and (b) nanostructures, such as AuPd nanopillars. Lateral designs typically consist of (c) Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub> /poly-Si stack (d) SOI patterning                                                                                                   | 13 |

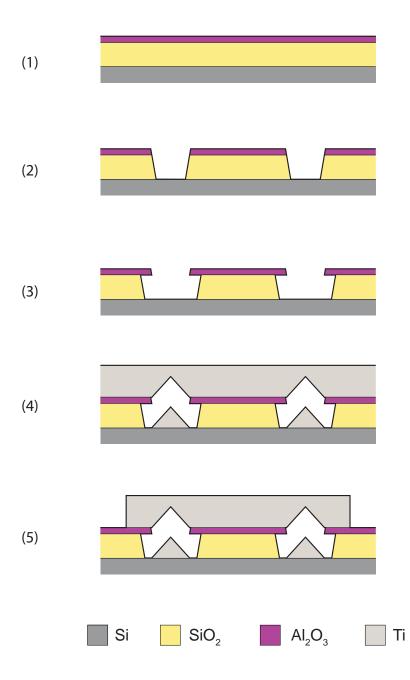

| 2.2  | Schematic illustration of the fabrication process for the diode arrays                                                                                                                                                                                                                                                                                                                                           | 15 |

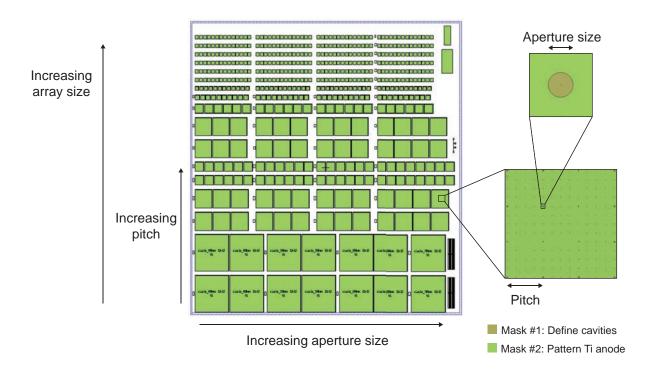

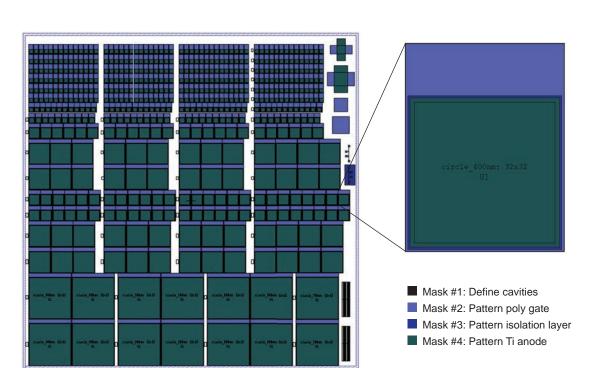

| 2.3  | Mask layout for diode lithography steps                                                                                                                                                                                                                                                                                                                                                                          | 17 |

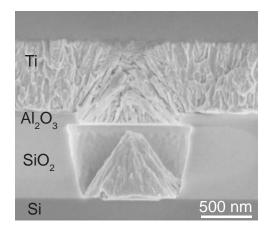

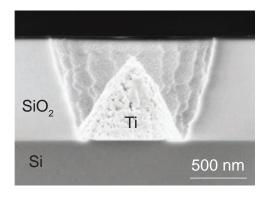

| 2.4  | Cross-sectional SEM of a single emitter tip in a diode configuration                                                                                                                                                                                                                                                                                                                                             | 17 |

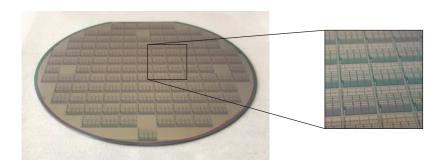

| 2.5  | Top-down view of a 6" wafer after the full process sequence is completed; magni-                                                                                                                                                                                                                                                                                                                                 |    |

|      | fied views shows multiple, electrically isolated device arrays within each die                                                                                                                                                                                                                                                                                                                                   | 18 |

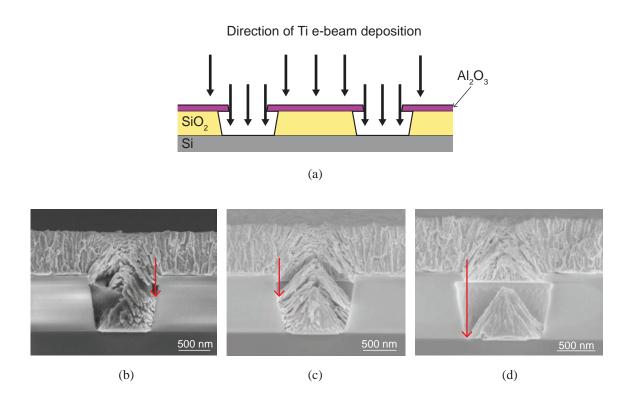

| 2.6  | (a) Schematic illustration of Ti deposition direction with respect to substrate. Cross-sectional SEM of cavity and emitter after HF vapor etch of (b) 170 sec (c) 240 sec and (d) 480 sec. The direction of Ti deposition is indicated by the red arrows; it can be seen that the Ti deposits on the cavity sidewalls when the top                                                                               |    |

|      | of the cavity does not have an alumina overhang                                                                                                                                                                                                                                                                                                                                                                  | 19 |

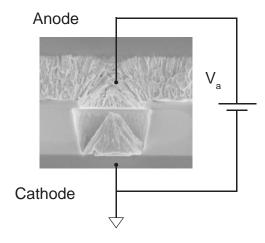

| 2.7  | Test setup for diode configuration.                                                                                                                                                                                                                                                                                                                                                                              | 20 |

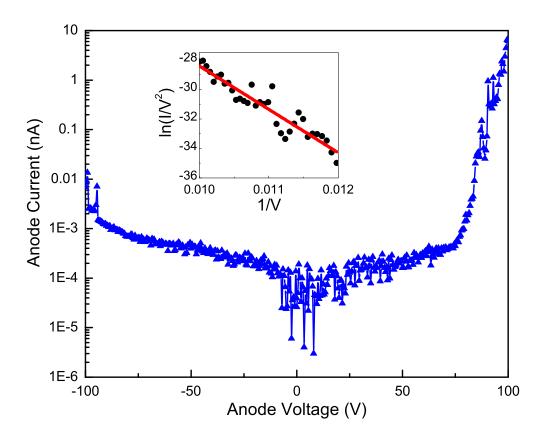

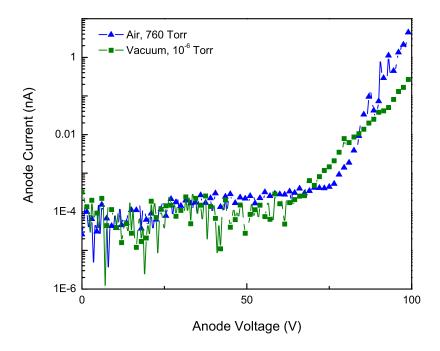

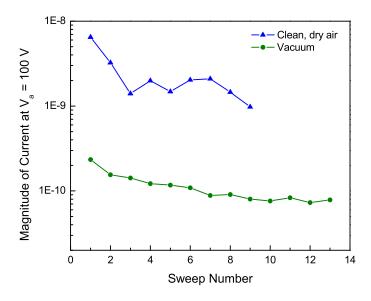

| 2.8  | Measured I-V characteristics for a 32x32 diode array at room temperature in                                                                                                                                                                                                                                                                                                                                      |    |

|      | clean, dry air                                                                                                                                                                                                                                                                                                                                                                                                   | 21 |

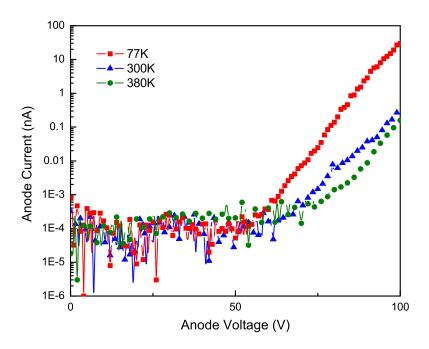

| 2.9  | Measured I-V characteristics for a $32x32$ diode array under $10^{-6}$ Torr vacuum at                                                                                                                                                                                                                                                                                                                            |    |

|      | room temperature (300 K), low temperature (77 K) and high temperature (380 K).                                                                                                                                                                                                                                                                                                                                   | 22 |

| 2.10 | Measured I-V characteristics for a 32x32 diode array in air and 10 <sup>-6</sup> Torr vacuum.                                                                                                                                                                                                                                                                                                                    | 23 |

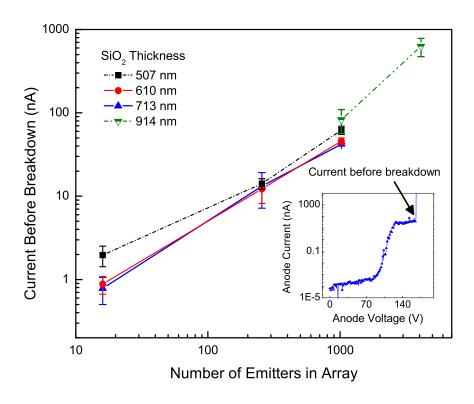

| 2.11 | ,                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | ranging from 16 to 4,096 emitters for varying SiO <sub>2</sub> thicknesses                                                                                                                                                                                                                                                                                                                                       | 25 |

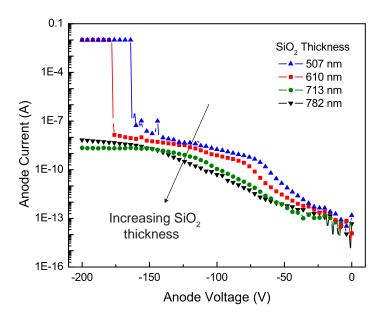

|            | Reverse I-V characteristics for 32x32 diode arrays for varying SiO <sub>2</sub> thicknesses, showing off-state leakage current and reverse breakdown voltage Off-state leakage current, measured at -100V anode bias, for array sizes ranging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

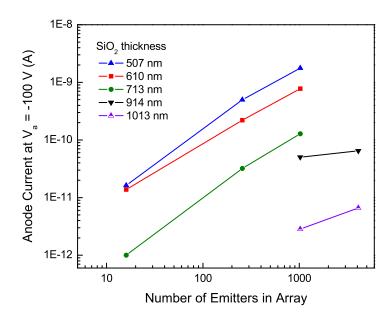

| 2.14       | from 16 to 4,096 emitters for varying $SiO_2$ thicknesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28       |

| 2.15       | in clean, dry air and at 10 <sup>-6</sup> Torr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 29       |

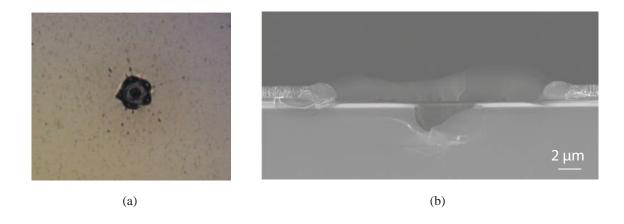

|            | versible breakdown event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30       |

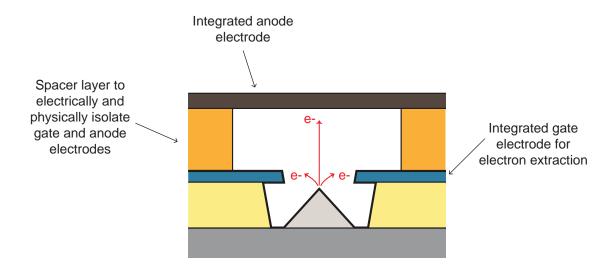

| 3.1        | Schematic illustration of target device geometry for a fully integrated triode field emission array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33       |

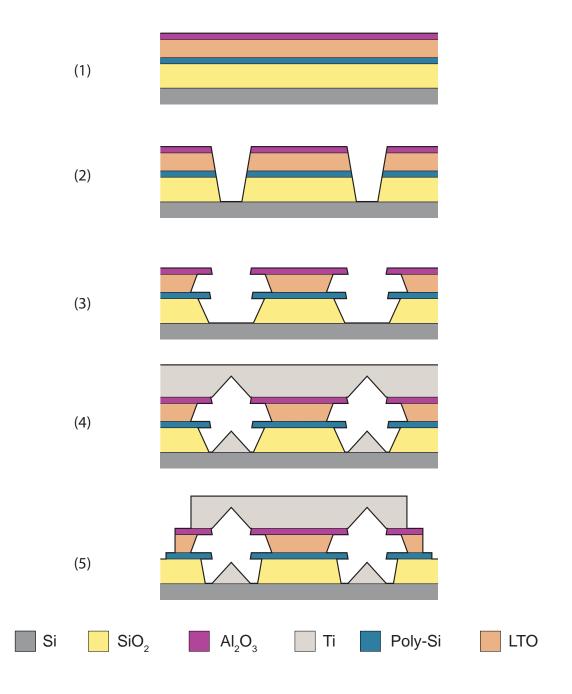

| 3.2        | Schematic illustration of the fabrication process for the triode arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34       |

| 3.3        | Mask layout for triode lithography steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36       |

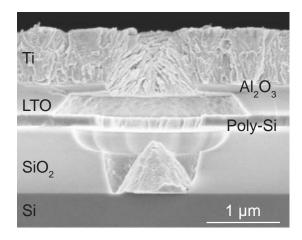

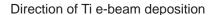

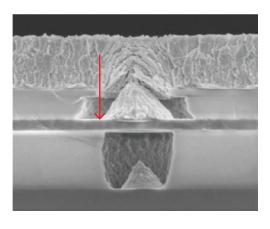

| 3.4<br>3.5 | Cross-sectional SEM of a single emitter tip in a triode configuration (a) Schematic illustration of Ti deposition direction with respect to substrate. (b) Cross-sectional SEM of triode with insufficient poly-silicon lateral etch, resulting in the poly-silicon layer extending further inward than the alumina layer. The direction of Ti deposition for this geometry is indicated by the red arrow, showing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36       |

|            | that Ti is deposited on the poly-silicon layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37       |

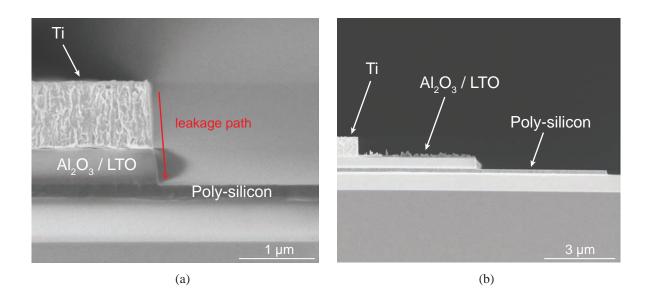

| 3.6        | Cross-sectional SEM of edge of device array showing (a) insufficient and (b) sufficient electrical isolation between the Ti anode and poly-silicon gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39       |

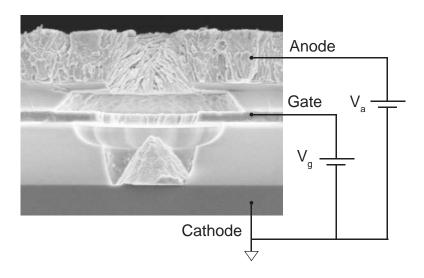

| 3.7        | Test configuration for triode arrays, with grounded cathode and positive biases applied to gate and anode electrodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39       |

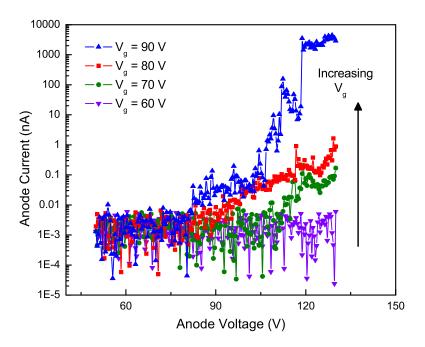

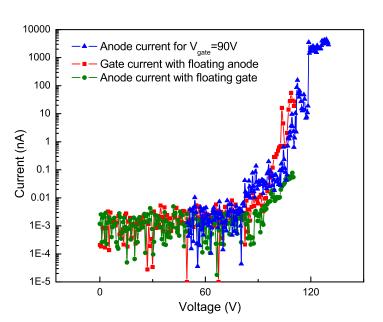

| 3.8        | Output characteristics for a $32x32$ triode array, with corresponding ratio of anode current $(I_a)$ to gate current $(I_g)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40       |

| 3.9        | Measurements showing triode performance with and without bias applied to the gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41       |

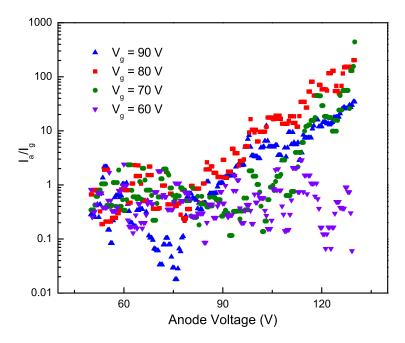

| 3.10       | Output characteristics for a 32x32 triode array, with corresponding ratio of anode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 3.11       | current (I <sub>a</sub> ) to gate current (I <sub>g</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42       |

| 3.12       | fraction of electrons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43<br>45 |

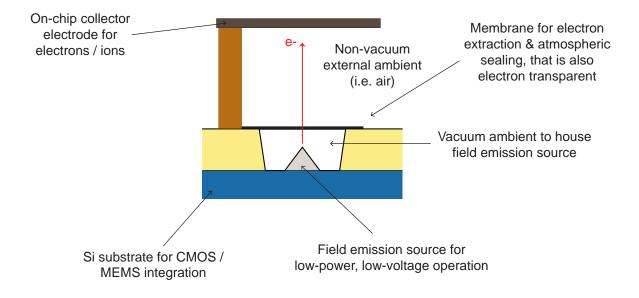

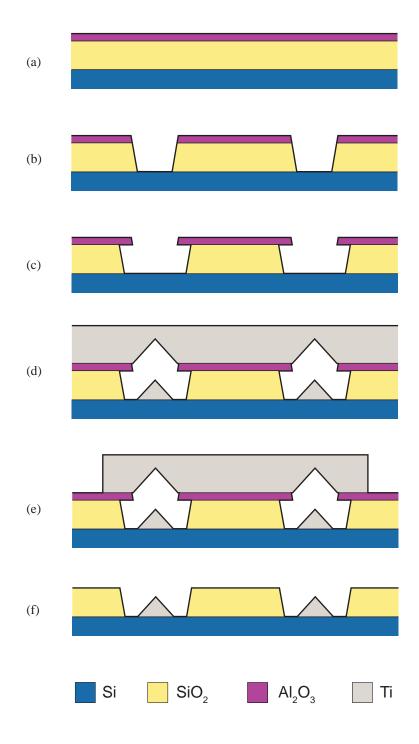

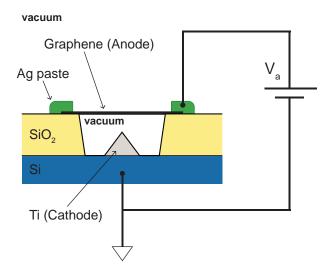

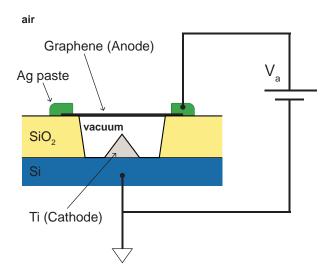

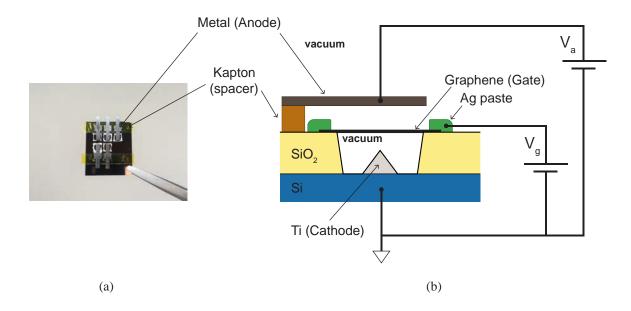

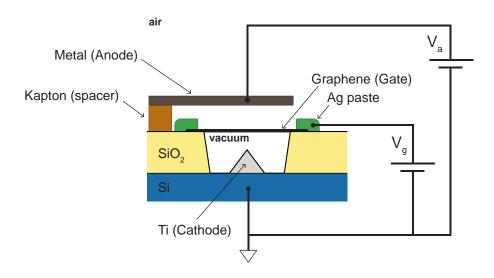

| 4.1<br>4.2 | Schematic illustration of the target device architecture, with key features annotated. Schematic illustration of the fabrication process for preparing the cathode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50<br>53 |

| -          | The second secon |          |

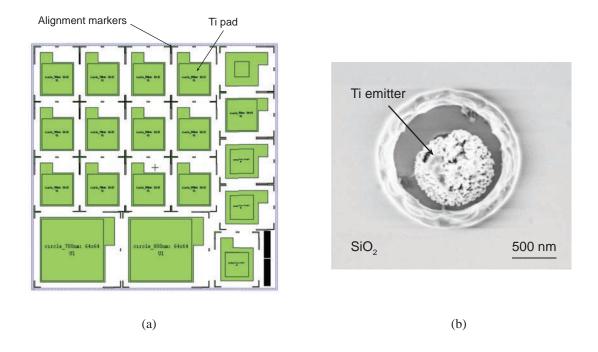

| 4.3   | (a) Layout of mask in first iteration of lithography for cathode fabrication process, with top-down SEM of emitter shown in (b) indicating visible damage to the emitter.        | 54  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

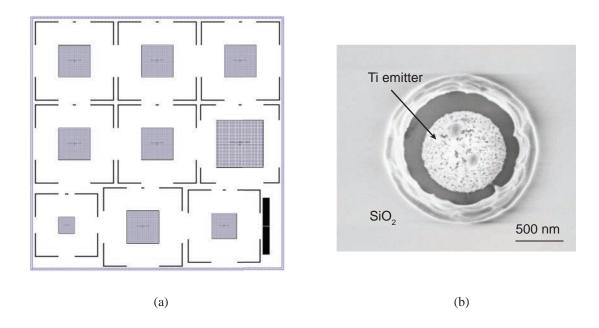

| 4.4   | (a) Layout of mask in second iteration of lithography for cathode fabrication                                                                                                    | _   |

|       | process, with top-down SEM of emitter shown in (b) indicating no damage to the                                                                                                   |     |

|       | emitter                                                                                                                                                                          | 55  |

| 4.5   | Cross-sectional SEM of emitter in silicon dioxide cavity                                                                                                                         | 56  |

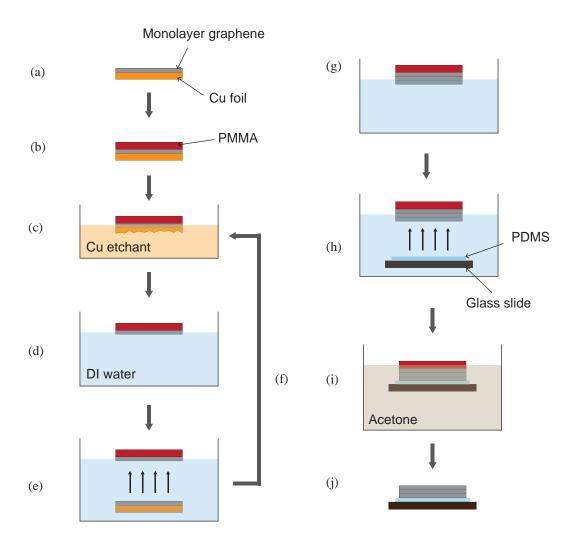

| 4.6   | Schematic illustration of process sequence for preparation of tri-layer graphene                                                                                                 |     |

|       | on PDMS, supported by a glass slide                                                                                                                                              | 58  |

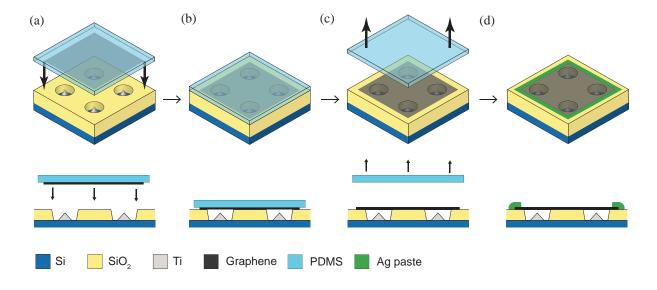

| 4.7   | Schematic illustration of process for transferring graphene to the cathode chip                                                                                                  | 59  |

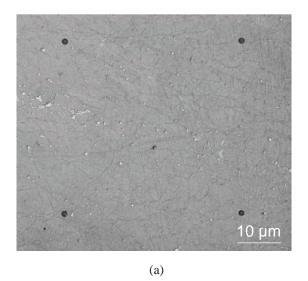

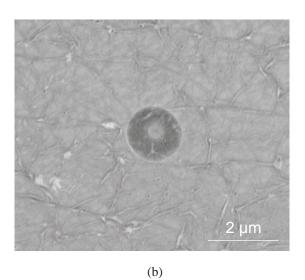

| 4.8   | (a) SEM of emitter array sealed by graphene, with magnified view shown in (b).                                                                                                   | 60  |

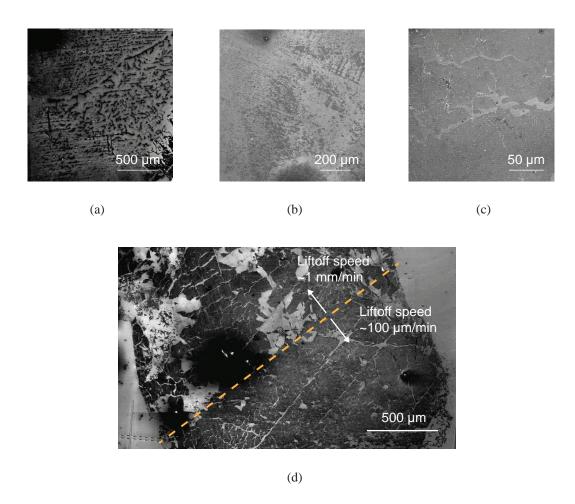

| 4.9   | SEM of chip after graphene transfer with (a) monolayer, (b) bi-layer and (c) tri-                                                                                                |     |

|       | layer graphene, indicating differences in uniformity and coverage. (d) SEM of                                                                                                    |     |

|       | chip after graphene transfer starting with a tri-layer graphene stack under two                                                                                                  |     |

|       | different liftoff speeds                                                                                                                                                         | 61  |

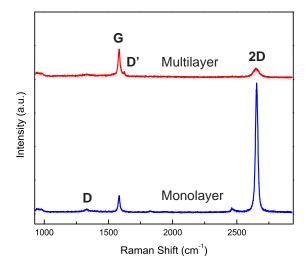

|       | Raman spectra of graphene after transfer onto cathode chip                                                                                                                       | 62  |

|       | Test setup for diode configuration, under ideal vacuum conditions                                                                                                                | 64  |

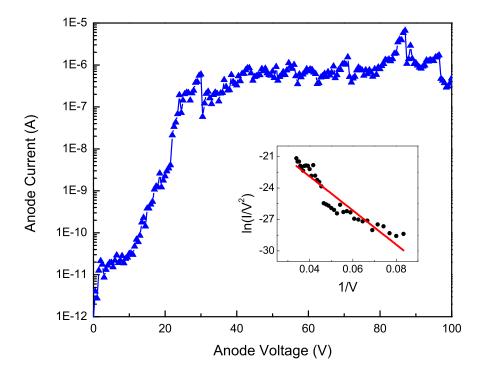

| 4.12  | Measured I-V characteristics for a $32x32$ diode array with $822$ nm thick $SiO_2$                                                                                               |     |

|       | under 10 <sup>-6</sup> Torr vacuum                                                                                                                                               | 65  |

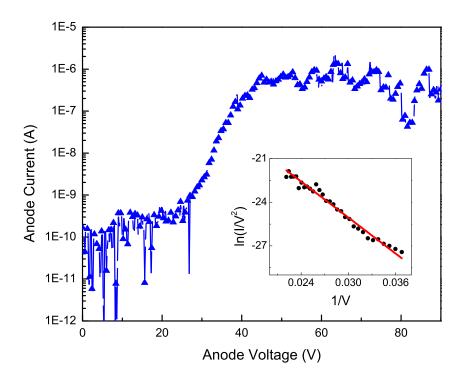

| 4.13  | Measured I-V characteristics for a 32x32 diode array with 1041 nm thick SiO <sub>2</sub>                                                                                         |     |

| 4 4 4 | under 10 <sup>-6</sup> Torr vacuum.                                                                                                                                              | 66  |

| 4.14  | Test setup for diode configuration, tested in clean, dry air after vacuum pump-                                                                                                  | o r |

| 115   |                                                                                                                                                                                  | 67  |

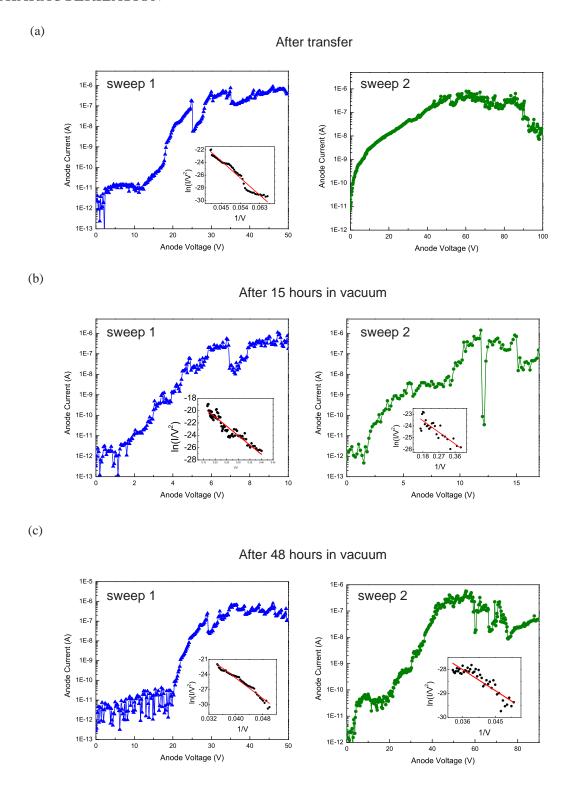

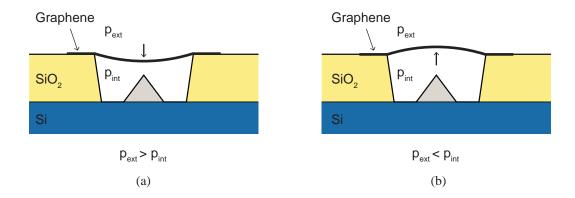

| 4.15  | Representative I-V characteristics for 32x32 diode arrays tested in clean, dry air                                                                                               | es  |

| 4.16  | after being held at 10 <sup>-6</sup> Torr vacuum for (a) 0 hours, (b) 15 hours and (c) 48 hours. Schematic illustration of graphene membrane deflection under different pressure | UC  |

| 4.10  | conditions. In scenario (a), the pressure external to the cavity is greater than the                                                                                             |     |

|       | internal cavity pressure, resulting in a downward deflection of the membrane. In                                                                                                 |     |

|       | scenario (b), the pressure external to the cavity is lower than the internal cavity                                                                                              |     |

|       | pressure, resulting in an upward deflection of the membrane                                                                                                                      | 70  |

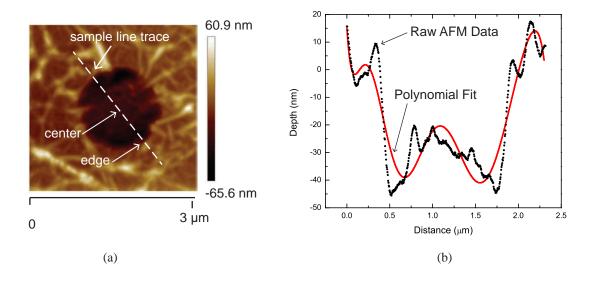

| 4.17  | (a) Tapping-mode AFM image of a graphene membrane suspended over a single                                                                                                        |     |

|       | cavity. (b) Plot of a single line trace of the AFM data, along with a best fit                                                                                                   |     |

|       | polynomial curve for analysis                                                                                                                                                    | 70  |

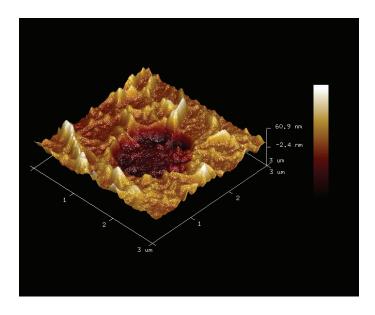

| 4.18  | 3D image of AFM scan indicating variation in depth across surface of sample                                                                                                      | 71  |

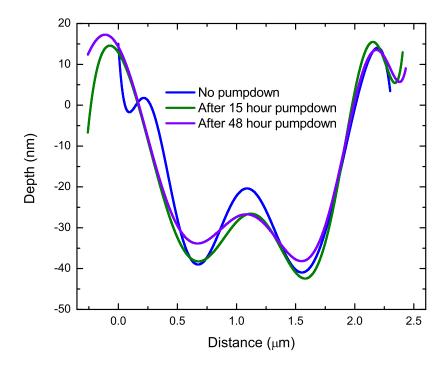

| 4.19  | Representative plot of graphene membrane deflection measured in air after device                                                                                                 |     |

|       | pumpdown for 0 hours, 15 hours and 48 hours. As the pumpdown time increases,                                                                                                     |     |

|       | the internal cavity pressure decreases                                                                                                                                           | 72  |

| 4.20  | (a) Single device chip after preparation for triode testing. (b) Test setup for                                                                                                  |     |

|       | triode configuration, under ideal vacuum conditions                                                                                                                              | 74  |

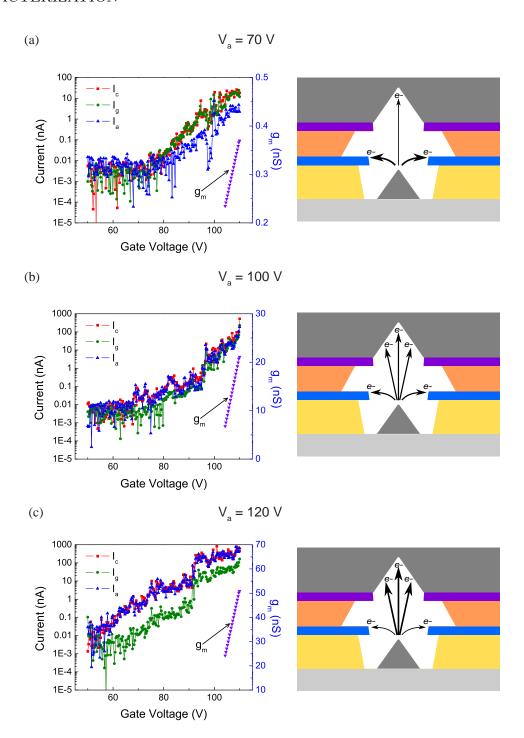

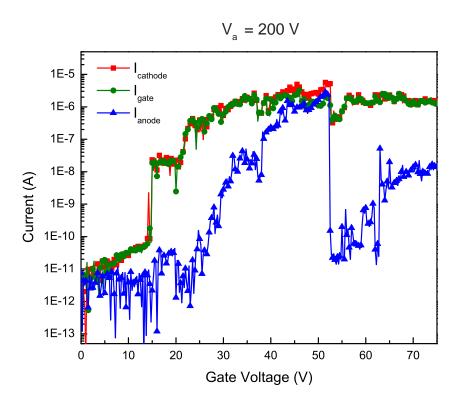

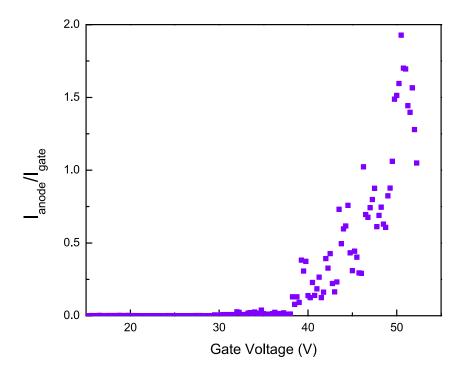

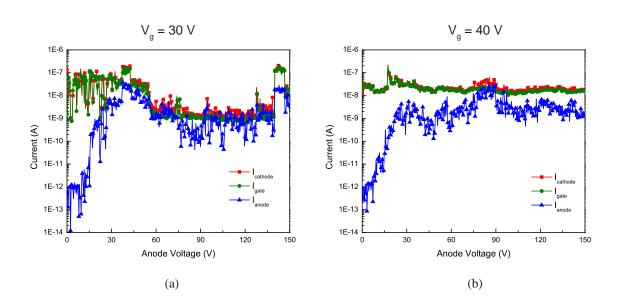

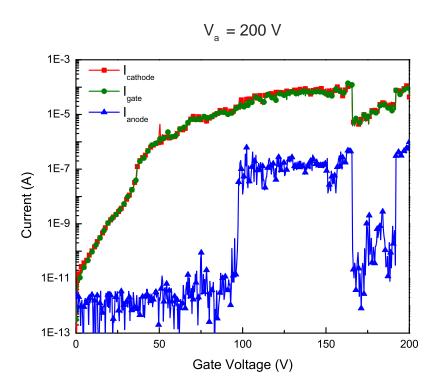

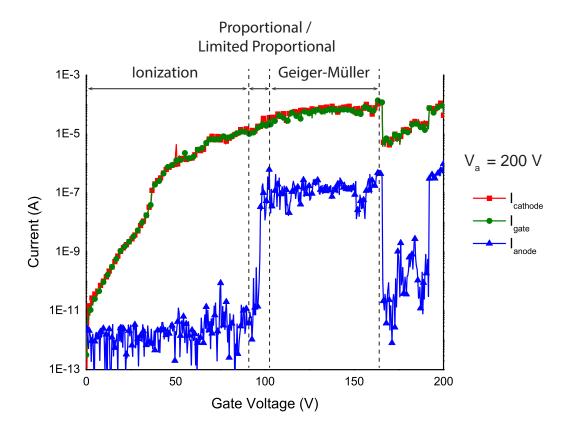

|       | Transfer characteristics for a triode array, with an anode voltage of 200 V                                                                                                      | 75  |

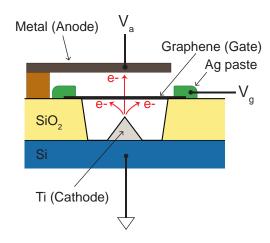

|       | Schematic illustration of electron trajectory during operation of triode devices                                                                                                 | 76  |

| 4.23  | Ratio of anode current $(I_a)$ to gate current $(I_g)$ plotted as a function of gate voltage.                                                                                    | 77  |

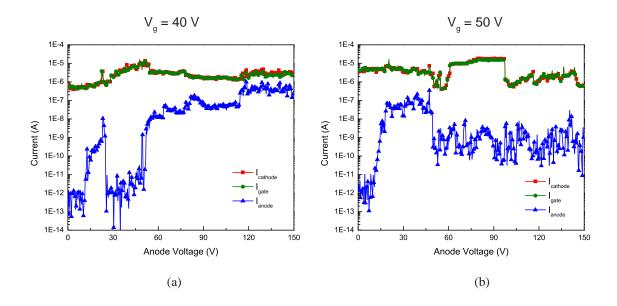

| 4.24 | Output characteristics for a triode array with 822 nm thick $SiO_2$ for $V_g$ equal to (a) 40 V and (b) 50 V                                                                                                                                                                                                                                                                                                                                             | 79 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.25 | Output characteristics for a triode array with 1042 nm thick ${ m SiO_2}$ for ${ m V_g}$ equal                                                                                                                                                                                                                                                                                                                                                           |    |

|      | to (a) 30 V and (b) 40 V                                                                                                                                                                                                                                                                                                                                                                                                                                 | 79 |

| 4.26 | (a) I-V characteristics for triode arrays, under ideal vacuum conditions, showing additional component of current from the cathode that is not seen at the gate or anode electrodes. This illustrates that some fraction of electrons are not intercepted by the gate, but also do not reach the anode. (b) I-V characteristics for diode arrays, under ideal vacuum conditions, with additional component of                                            |    |

|      | current from the cathode that is not seen at the anode electrode                                                                                                                                                                                                                                                                                                                                                                                         | 80 |

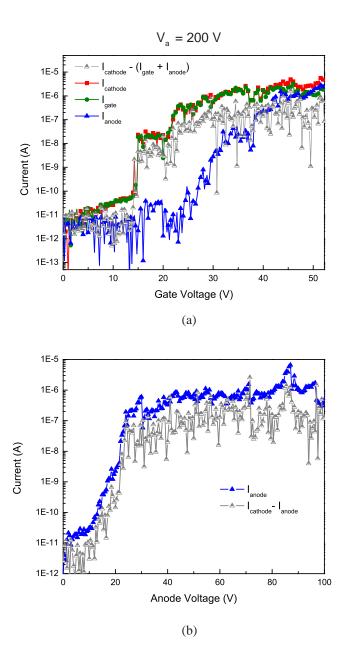

| 4.27 | Test setup for triode configuration for devices tested in air after vacuum pumpdown.                                                                                                                                                                                                                                                                                                                                                                     | 82 |

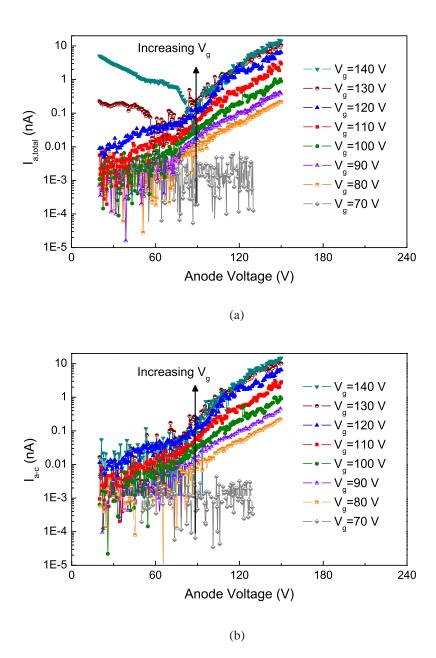

|      | Transfer characteristics for triode array measured in air after vacuum pumpdown,                                                                                                                                                                                                                                                                                                                                                                         |    |

|      | illustrating in-air extraction of electrons                                                                                                                                                                                                                                                                                                                                                                                                              | 83 |

| 4.29 | Transfer characteristics for triode measurement in air, with gas ionization regions                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | annotated                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84 |

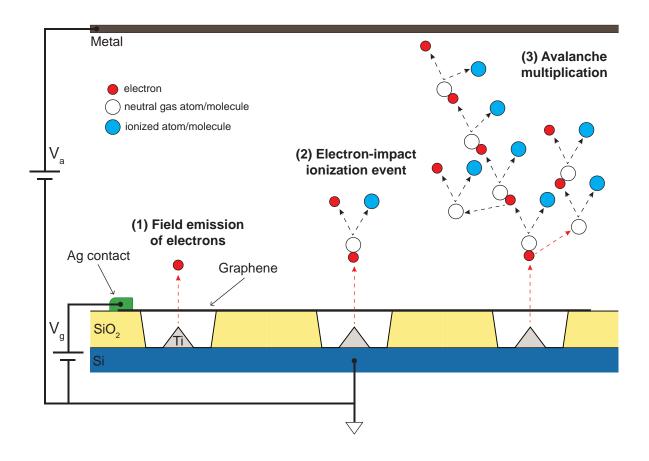

| 4.30 | Illustration of processes occurring in the triode air measurement. First, field emission of electrons occurs, shown in (1), followed by ionization events caused by electron impact, as shown in (2). As the gate voltage increases, additional electrons are emitted and both primary and secondary electrons continue to cause ionization events, creating an avalanche multiplication of electrons that enables electrical conduction through the air | 85 |

| 4.31 | key differences annotated. The metal-sealed diode is shown in (a) and the graphene-sealed diode is shown in (b). The key differences between these two device architectures are the anode shape and material as well as the inter-electrode                                                                                                                                                                                                              | 07 |

| 4.32 | distance between the anode and cathode                                                                                                                                                                                                                                                                                                                                                                                                                   | 87 |

| 4.02 | key differences annotated. The metal-sealed triode is shown in (a) and the                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | graphene-sealed triode is shown in (b)                                                                                                                                                                                                                                                                                                                                                                                                                   | 89 |

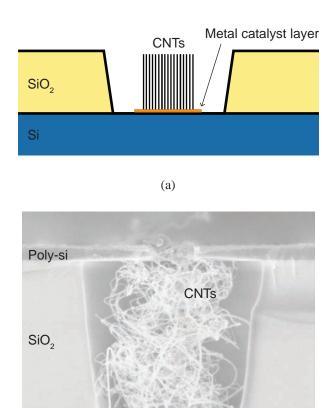

| 5.1  | (a) Schematic illustration of CNTs integrated in $SiO_2$ cavities. (b) Cross-sectional SEM of CNT forest grown in $SiO_2$ cavity with integrated poly-silicon gate, using a 5 nm Fe catalyst layer.                                                                                                                                                                                                                                                      | 95 |

|      | a o mm re cavaryou rayer                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55 |

# List of Tables

| 1.1 | Comparison of Solid-state Devices and Vacuum Microelectronics [1]–[6] | 2  |

|-----|-----------------------------------------------------------------------|----|

|     | Voltage to Reach Threshold Current (V)                                |    |

| 2.2 | Punchthrough Voltage (V)                                              | 26 |

| 2.3 | Diode Arrays: Applications and Future Work Recommendations            | 31 |

| 3.1 | Summary of Transfer Characteristics                                   | 44 |

| 3.2 | Triode Arrays: Applications and Future Work Recommendations           | 48 |

| 4.1 | AFM Data for Graphene Membranes After Varying Pumpdown Times          | 71 |

| 4.2 | Metal vs. Graphene in Diode Configuration                             | 88 |

| 4.3 | Metal vs. Graphene in Triode Configuration                            | 89 |

| 4.4 | Portable Electron Source Applications and Future Work Recommendations | 92 |

#### Acknowledgments

This dissertation would not have been complete without the support of many individuals, both in my professional and personal life. Before I even understood what research was, Professor Andrea Armani took the time to mentor me as a rising sophomore in college. In hindsight, the three years I spent with her prepared me extremely well for graduate school and laid the foundation for the rest of my career. The opportunity to explore the novel ideas and concepts in this work was provided to me by my Ph.D. advisor, Professor Vivek Subramanian, who allowed me to study completely uncharted territory in his group. Under his tutelage, I gained a deep sense of confidence in both my academic and personal pursuits. I know now that if I want to get something done, I will get it done – a powerful lesson that I will always carry with me, particularly in times of doubt. I have also been fortunate enough to have had another great mentor in my co-advisor, Professor Kris Pister, who inspired me to explore my work in a playful manner. His guidance helped refine the ideas that resulted in some of the most interesting portions of this work, that I hope move him one step closer to his dreams. I also would not have made it through this journey without support from my friends. In particular, Carlos Biaou made all the late nights on campus enjoyable and became the little brother I never had; and Juan Pablo Llinás never failed to keep me entertained at any time of the day. I am also deeply indebted to all of my amazing friends outside of graduate school – no words are sufficient for expressing my gratitude. Our travels, adventures, and excursions meant more to me than I probably express and kept me sane during difficult times. Special thanks to Calvin Robert Lee, for making me believe I've never had anything to doubt in myself and for knowing me well enough to help me write my dedication. Finally, to my brother, Rishi, and my parents, Ruli and Bimal, for their truly unwavering support.

# Chapter 1

## Introduction

The miniaturization of electronics is a clear technological trend that has enabled the widespread use of electronics in all areas of society. Accelerated by the invention of the solidstate transistor, miniaturization has taken electronics from the early days of vacuum tubes to the integrated circuits that are ubiquitous today, in applications such as smartphones, televisions and computers. While integrated circuit technology has superseded vacuum tubes in many domains, the trend towards miniaturization also led to the emergence of vacuum microelectronics –a field that utilizes solid-state microfabrication techniques to develop devices based on electron transport in vacuum. The ability to use vacuum microelectronic devices alongside solid-state technology has the potential to not only address the limitations faced by solid-state technology, but also enable new applications in electronics. Thus, the focus of this work is to develop on-chip ambient operation micrometer-scale vacuum-based devices directly on Si, with the goal of enabling their widespread and practical use in electronics. In this chapter, the evolution of vacuum-based technology is discussed, including a section on the fundamental physics of electron emission to outline the principles upon which vacuum microelectronic devices operate. Emerging applications are reviewed and discussed in the context of other key technological platforms, such as microelectromechanical systems (MEMS). With these applications in mind, the fundamental motivation and key objectives of this work are introduced, and the chosen methodology of study is presented. This chapter concludes with an outline of the thesis organization.

#### 1.1 Historical overview of vacuum microelectronics