High-Performance Architectures for Vehicle Propulsion: An Unconventional Approach to Design, Fabrication and Analysis using Scalable Flying Capacitor Multilevel Converter Modules

Nathan Pallo

### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-189 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-189.html

August 13, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Acknowledgement

Much of this work was both motivated and funded by the Advanced Air Transport Technology (AATT) Project at the National Aeronautics and Space Administration (NASA) through cooperative agreement NNX14AL79A. Additional support has been provided by the Vehicle Technologies Office in the United States Department of Energy through the Electric Drive Technologies Consortium (EDTC) under Award Number DEEE0008712. High-Performance Architectures for Vehicle Propulsion: An Unconventional Approach to Design, Fabrication and Analysis using Scalable Flying Capacitor Multilevel Converter Modules

by

Nathan Pallo

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Robert Pilawa-Podgurski, Chair Professor Seth Sanders Professor Duncan Callaway Professor Alejandro Dominguez-Garcia

Summer 2021

High-Performance Architectures for Vehicle Propulsion: An Unconventional Approach to Design, Fabrication and Analysis using Scalable Flying Capacitor Multilevel Converter Modules

> Copyright 2021 by Nathan Pallo

#### Abstract

### High-Performance Architectures for Vehicle Propulsion: An Unconventional Approach to Design, Fabrication and Analysis using Scalable Flying Capacitor Multilevel Converter Modules

by

#### Nathan Pallo

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

#### University of California, Berkeley

#### Professor Robert Pilawa-Podgurski, Chair

The consequences of climate change grow more pronounced each year as carbon emissions continue unabated. Decarbonizing all aspects of the transportation sector is a major requirement for a sustainable pathway to mitigate these consequences. However, this requires overcoming substantial engineering challenges, not the least of which are the power density and efficiency requirements of the inverter system in future electric drivetrains. This work examines a high-performance and scalable approach for modeling, designing, fabricating and testing an architecture that meets aggressive industry targets through innovative techniques and the use of an unconventional topology. Several prominent and promising topologies are reviewed, and an unconventional approach using the flying-capacitor multilevel topology is introduced to drive the order-of-magnitude improvements required by the industry targets. A 10-level, 1 kV, dual-interleaved converter module serves as the platform for an in-depth study of the electrical and thermal design and performance attained using this approach, where a peak power of 18.9 kW and a peak efficiency of 98.95% is experimentally demonstrated. Scalability and reliability of the proposed architecture is discussed and tested using individual modules as well as an array paralleling nine of these  $38.4 \,\mathrm{kW/kg}$ ,  $24.4 \,\mathrm{kW/L}$ modules. Finally, potential extensions to the work in future studies are reviewed.

To my husband, Xin. He will likely never read this document, nor particularly care about any of the implications of this work. However, he was instrumental in the support, nourishment and encouragement required to complete the efforts within.

Also, to my family and friends. My family has been an anchor in all of the years of my adulthood, while my found family has provided additional enrichment and encouragement beyond the borders of my hometown.

# Contents

| Co       | onter | nts                                         | ii        |

|----------|-------|---------------------------------------------|-----------|

| Li       | st of | Figures                                     | iv        |

| Li       | st of | Tables                                      | x         |

| 1        | Veh   | icle Drivetrain Electrification             | 1         |

|          | 1.1   | Constraints and Performance Criteria        | 3         |

|          | 1.2   | Survey of Topologies                        | 6         |

|          | 1.3   | An Unconventional Approach                  | 9         |

| <b>2</b> | Inve  | erter Module Electrical Design              | 13        |

|          | 2.1   | Structure for Computational Analysis        | 18        |

|          | 2.2   | Loss Modeling                               | 19        |

|          | 2.3   | Startup Dynamics                            | 32        |

|          | 2.4   | Mitigation of Commutation Loop Inductance   | 33        |

|          | 2.5   | Experimental Results                        | 37        |

|          | 2.6   | Chapter Remarks                             | 45        |

| 3        | The   | ermal Management and Mechanical Integration | <b>47</b> |

|          | 3.1   | Cooling Technologies and Media              | 47        |

|          | 3.2   | Modular Heat Sink Design                    | 48        |

|          | 3.3   | Analysis using Computational Fluid Dynamics | 52        |

|          | 3.4   | Experimental Results                        | 56        |

|          | 3.5   | Chapter Remarks                             | 63        |

| <b>4</b> | Inve  | erter Array Design and Operation            | 65        |

|          | 4.1   | Hierarchical Control                        | 66        |

|          | 4.2   | Multi-Module Harmonic Content Analysis      | 70        |

|          | 4.3   | Current Sharing & Parameter Sensitivity     | 73        |

|          | 4.4   | Experimental Results                        | 78        |

|          | 4.5   | Chapter Remarks                             | 84        |

| 5  | <b>Syst</b> 5.1 5.2 | Sem Reliability<br>Short-Circuit Fault Mitigation | <b>85</b><br>88<br>104 |

|----|---------------------|---------------------------------------------------|------------------------|

|    | 5.3                 | Parallel Module Redundancy                        | 107                    |

|    | 5.4                 | Chapter Remarks                                   | 118                    |

| 6  | Futu                | are Work & Conclusion                             | 121                    |

|    | 6.1                 | Extended Component Characterization               | 121                    |

|    | 6.2                 | Advanced Gate-Drive Techniques                    | 121                    |

|    | 6.3                 | Validation of Sense and Measurement Schemes       | 123                    |

|    | 6.4                 | Online Health-Monitoring                          | 124                    |

|    | 6.5                 | Folded & Three-Dimensional Module Packaging       | 125                    |

|    | 6.6                 | Improved Cooling and Integration                  | 127                    |

|    | 6.7                 | Coupled Inductors for Interleaved Modules         | 127                    |

|    | 6.8                 | Modeling of Converter Dynamics                    | 128                    |

|    | 6.9                 | Conclusion                                        | 129                    |

| Bi | bliog               | raphy                                             | 130                    |

iii

# List of Figures

| 1.1            | Depictions of more electric aircraft propulsion leveraging boundary layer inges-<br>tion, as adapted from concepts and figures in [12] and [13]. For illustrative pur-<br>poses, contributions to drag from the wings of the aircraft are assumed to be less<br>than that of the fuselage and are ignored.                                                                                                                                                   | 2        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

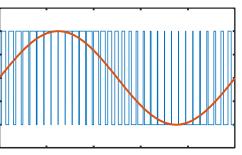

| 1.2            | The common, 2-level bridge topology, with corresponding single-phase output waveform.                                                                                                                                                                                                                                                                                                                                                                        | 6        |

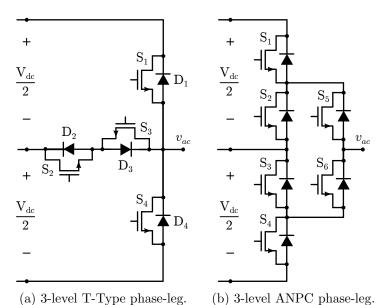

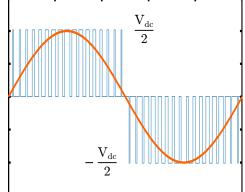

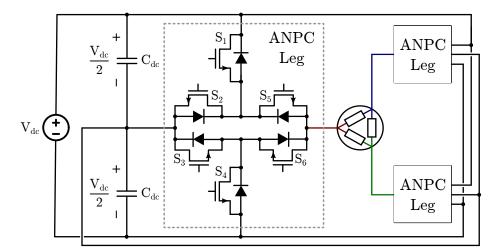

| 1.3            | The 3-level topologies highlighted in this chapter, with corresponding output $f$                                                                                                                                                                                                                                                                                                                                                                            |          |

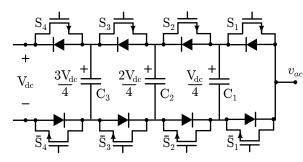

| 1.4            | waveform                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7<br>10  |

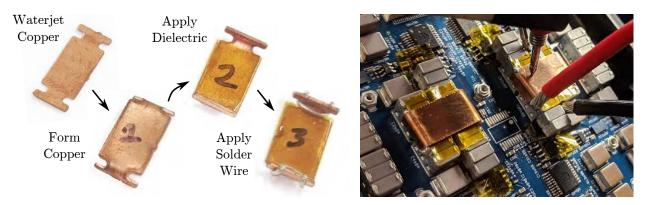

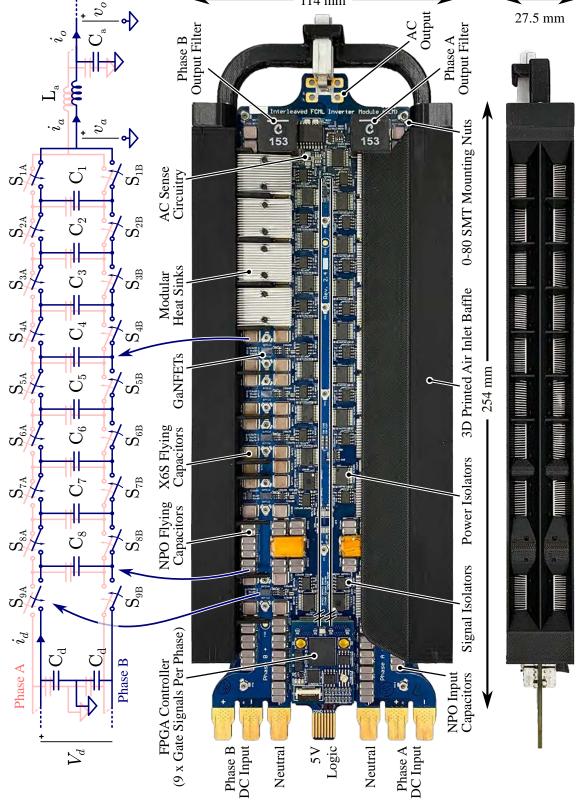

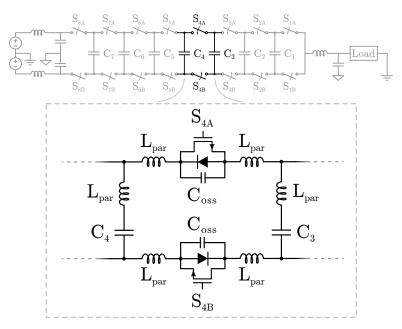

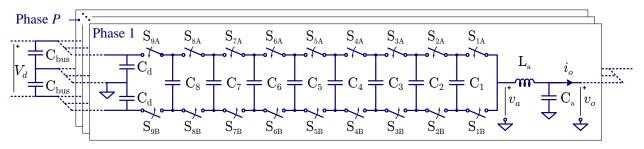

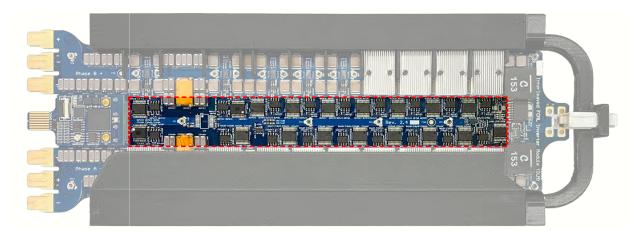

| 2.1<br>2.2     | Fabrication, installation and high voltage testing of a custom busbar for $C_8$ The schematic of the 10-level, dual-interleaved FCML inverter module of this work, accompanied by the top and side views of a hardware prototype. The converter is shown partially assembled to illustrate the mechanical assembly and thermal management, with the exception that screws used for heat sink mounting are were replaced with an improved design in Chapter 3 | 15<br>17 |

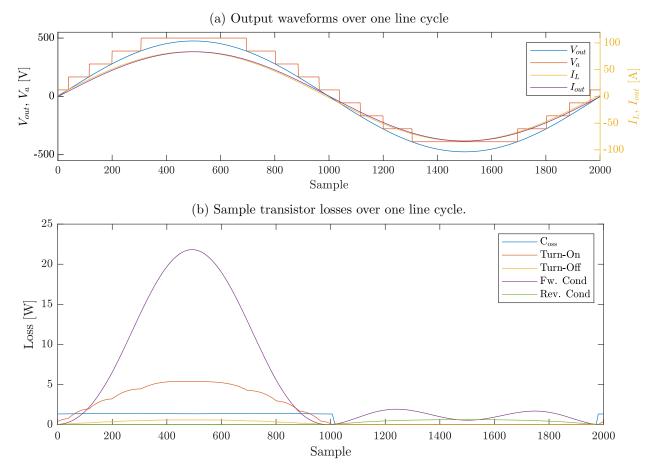

| 2.3            | Sampled converter waveforms used to simulate and model FCML losses                                                                                                                                                                                                                                                                                                                                                                                           | 20       |

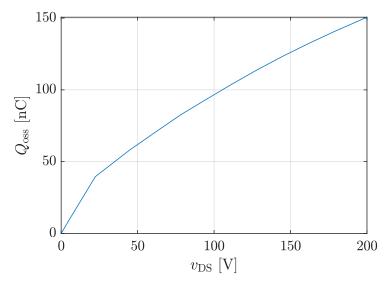

| 2.4            | Typical nonlinear $Q_{oss}$ characteristics for an EPC2034C gallium nitride transistor.                                                                                                                                                                                                                                                                                                                                                                      | 23       |

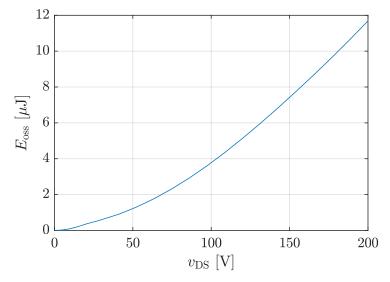

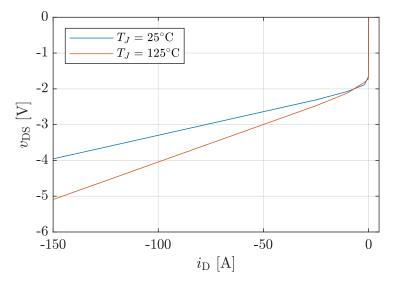

| $2.5 \\ 2.6$   | Typical nonlinear $E_{\text{oss}}$ characteristics for an EPC2034C gallium nitride transistor.<br>Typical reverse conduction characteristics for an EPC2034C gallium nitride tran-                                                                                                                                                                                                                                                                           | 24       |

|                | sistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25       |

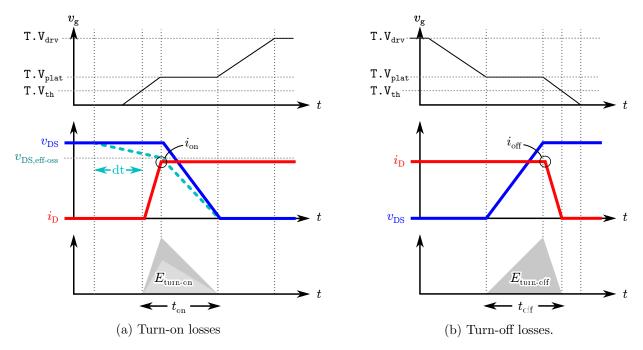

| 2.7            | Turn-on and turn-off waveforms.                                                                                                                                                                                                                                                                                                                                                                                                                              | 26       |

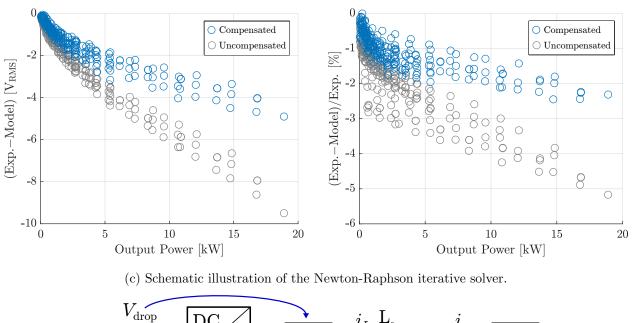

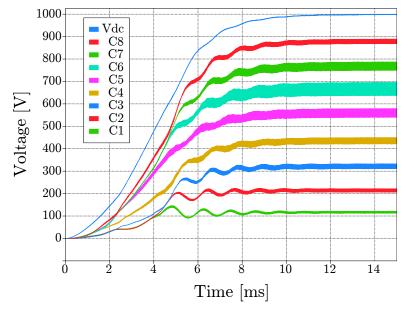

| 2.8            | Comparison of loss models without (gray series) and with (blue series) an iterative solver that compensates for converter losses in the output power and efficiency                                                                                                                                                                                                                                                                                          |          |

|                | calculations.                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30       |

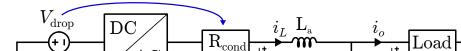

| 2.9            | Modeling accuracy validated across various operating points                                                                                                                                                                                                                                                                                                                                                                                                  | 31       |

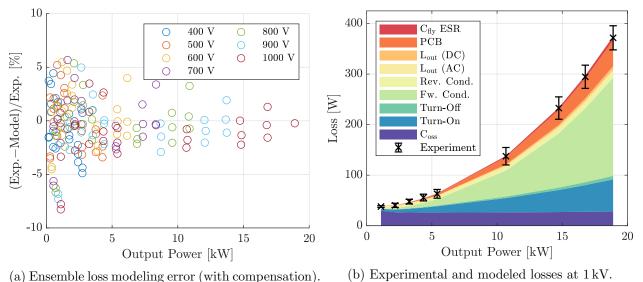

| $2.10 \\ 2.11$ | Startup simulation in PLECS                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32       |

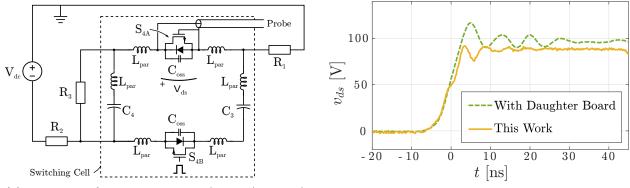

|                | 9-level FCML inverter, shown here for a 9-level converter                                                                                                                                                                                                                                                                                                                                                                                                    | 33       |

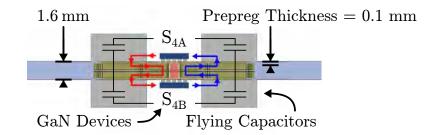

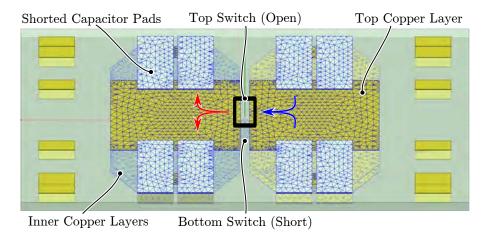

| 2.12 | Cross section showing commutation loop between a given pair of complementary switches. Internal layers and vias create an electrically-thin vertical layout on a |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | single PCB; the cross-sectional area inside the PCB (shaded red), and thus the                                                                                   |    |

|      | corresponding loop inductance, can be greatly reduced with this approach                                                                                         | 34 |

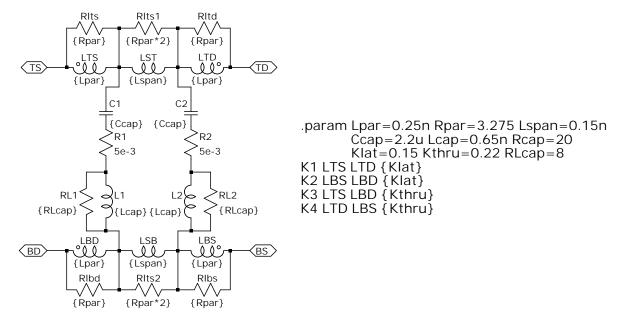

| 2.13 | 3D model of a switching cell with buried vias, as imported and meshed in Q3D.                                                                                    | 35 |

|      | Spice model of commutation loop implemented as a component in LTSpice using                                                                                      |    |

|      | parameters extracted from Q3D finite-element analysis.                                                                                                           | 36 |

| 2.15 | Experimental characterization of drain-source voltage overshoot during commu-                                                                                    |    |

|      | tation as a means of comparing loop parasitics between designs                                                                                                   | 37 |

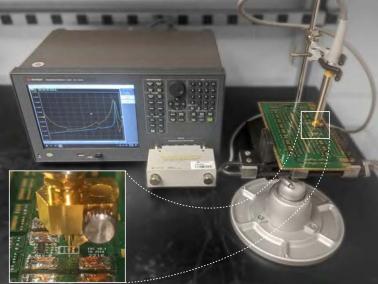

| 2.16 |                                                                                                                                                                  |    |

|      | After calibration is carried out to the adapter tip endpoint (inset), the loop                                                                                   |    |

|      | impedance between the drain to source pads can be measured with high accuracy.                                                                                   | 38 |

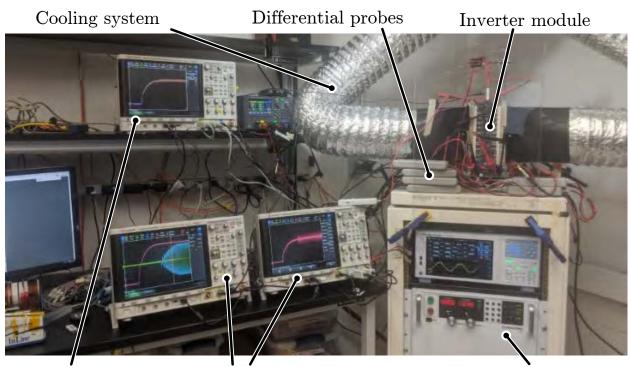

| 2.17 |                                                                                                                                                                  |    |

|      | ule. Waveforms were captured on three synchronized Keysight MSO-X 4024A                                                                                          |    |

|      | oscilloscopes with several models of high voltage differential probes of 25 MHz                                                                                  |    |

|      | bandwidth or greater.                                                                                                                                            | 39 |

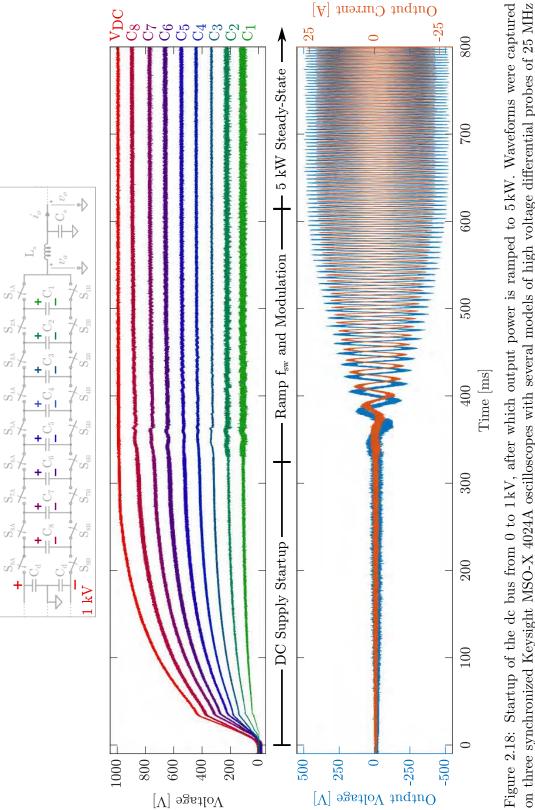

| 2.18 | Startup of the dc bus from 0 to 1 kV, after which output power is ramped to                                                                                      |    |

|      | 5 kW. Waveforms were captured on three synchronized Keysight MSO-X 4024A                                                                                         |    |

|      | oscilloscopes with several models of high voltage differential probes of 25 MHz                                                                                  |    |

|      | bandwidth or greater. High-frequency content present on a given waveform can be                                                                                  |    |

|      | attributed to the specific probe used, or the higher fidelity of ac content capture                                                                              |    |

|      | for the signals with lower dc voltage                                                                                                                            | 40 |

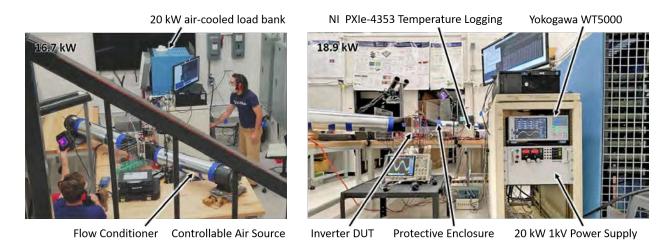

| 2.19 | Experimental setup for high power module tests.                                                                                                                  | 41 |

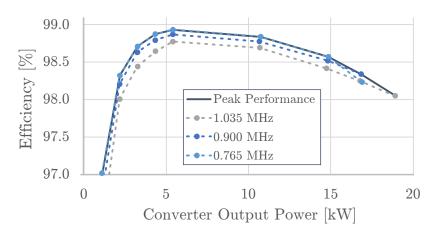

| 2.20 | 10-level converter performance at $1 \mathrm{kV}$ dc bus with varied switching frequency.                                                                        | 42 |

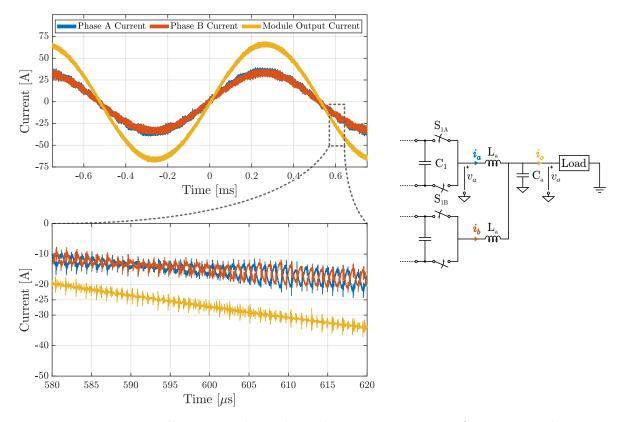

| 2.21 | Experimentally-measured interleaved output current waveforms at 16.7 kW out-                                                                                     |    |

|      | put power. Waveforms are captured digitally on an oscilloscope and plot to                                                                                       |    |

|      | enhance details.                                                                                                                                                 | 43 |

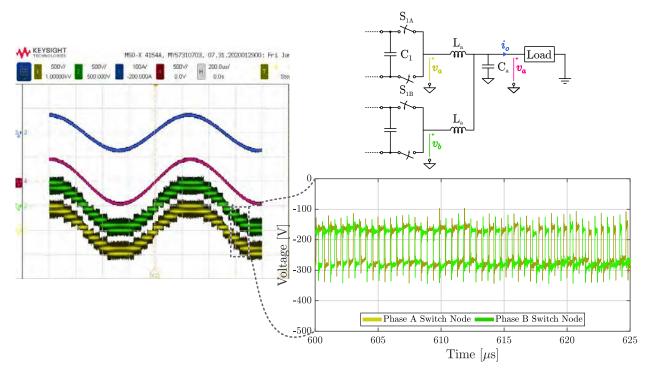

| 2.22 | Interleaved output voltage waveforms at 1 kV dc bus and 16.7 kW output power.                                                                                    |    |

|      | Waveforms are captured digitally on an oscilloscope and plot to enhance details,                                                                                 |    |

|      | but are shown next to the oscilloscope screen capture for additional context                                                                                     | 44 |

| 2.23 | Summary representation of how the design of this work meets aggressive perfor-                                                                                   |    |

|      | mance targets for more electric aircraft compared to the state-of-the-art                                                                                        | 46 |

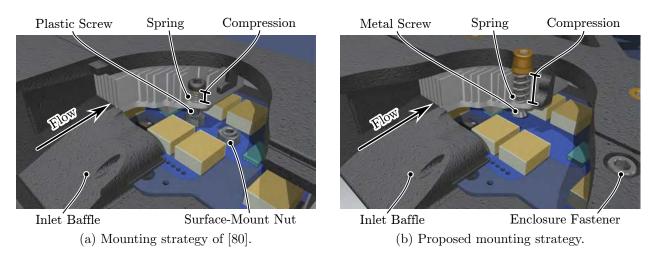

| 3.1  | Comparison of previous and proposed modular heat sink mounting strategies.                                                                                       |    |

| 0.1  | Note, the threaded insert in the right figure is only conceptual; the interference                                                                               |    |

|      | fit described later in this section made this specific consideration obsolete                                                                                    | 49 |

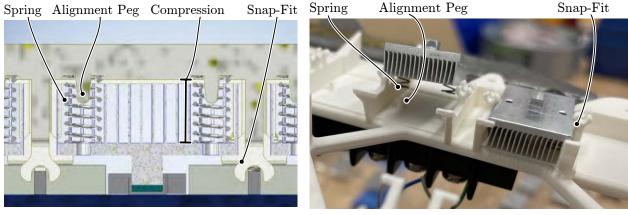

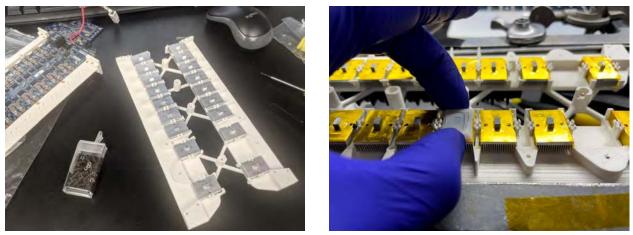

| 3.2  | Examples of the snap-fit concept with spring alignment and interference features.                                                                                | 50 |

| 3.3  | Installation of heat sinks on an entire face of a module with dual-sided cooling.                                                                                | 51 |

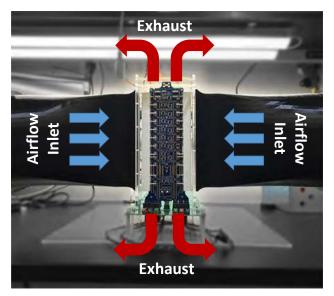

| 3.4  | Illustration of dual-inlet cooling of an FCML-based power module. One inlet is                                                                                   | -  |

|      | provided for each interleaved phase, with exhaust air designed to exit out the                                                                                   |    |

|      | middle of each module.                                                                                                                                           | 52 |

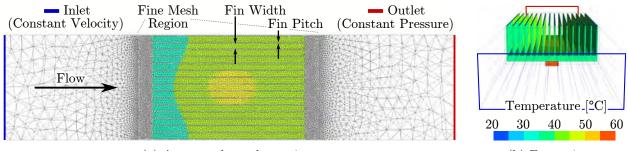

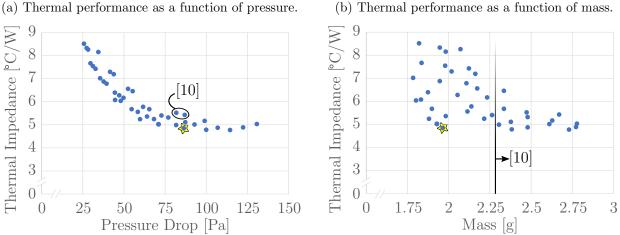

| 3.5        | Meshing and results of CFD for a single heat sink. A finer mesh is used in the region around the heat sink. Fin width, fin pitch and fin count were parametrically varied and the system was systematically re-meshed and solved to find the best configuration.                                                                                                                   | 53 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

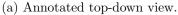

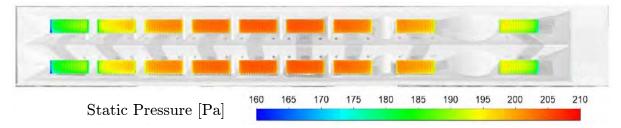

| 3.6        | Results of the parametric sweep of heat sink fin count, pitch and width                                                                                                                                                                                                                                                                                                            | 54 |

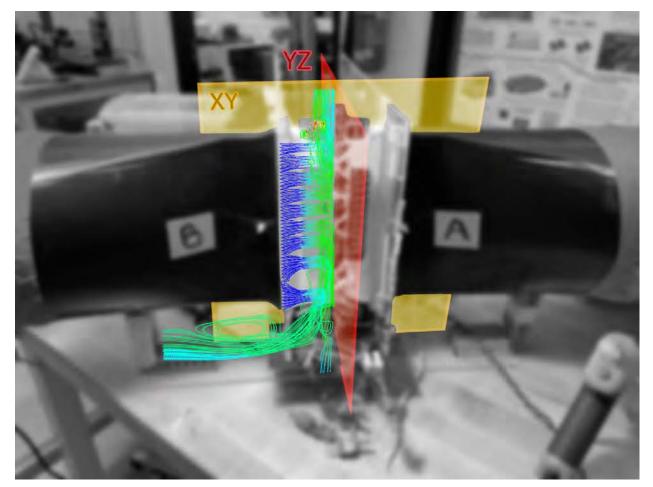

| 3.7        | Composite rendering of air particle tracks from the quarter-symmetric fluid sim-<br>ulation.                                                                                                                                                                                                                                                                                       | 55 |

| 3.8        | Composite image of the inlet at one side of the module, where the color map indicates static pressure at the inlet of each individual heat sink. Up to a $14\%$ variation in pressures yields commensurate variation in mass flow, and therefore                                                                                                                                   |    |

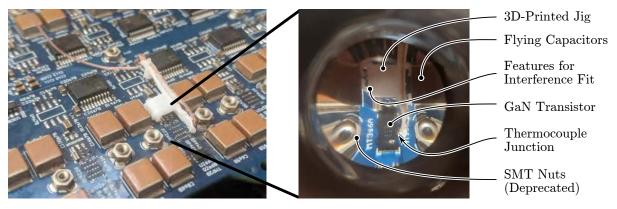

| 3.9        | cooling capacity                                                                                                                                                                                                                                                                                                                                                                   | 56 |

| 3.10       | devices                                                                                                                                                                                                                                                                                                                                                                            | 57 |

|            | of the reverse conduction and do not exist in the physical system                                                                                                                                                                                                                                                                                                                  | 58 |

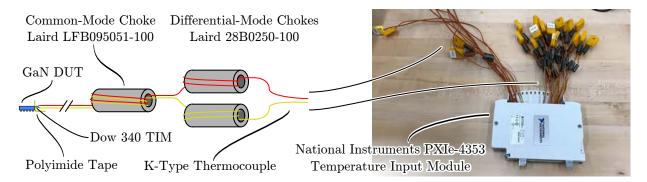

| 3.11       | Common- and differential-mode ferrites installed on the temperature sensors                                                                                                                                                                                                                                                                                                        | 59 |

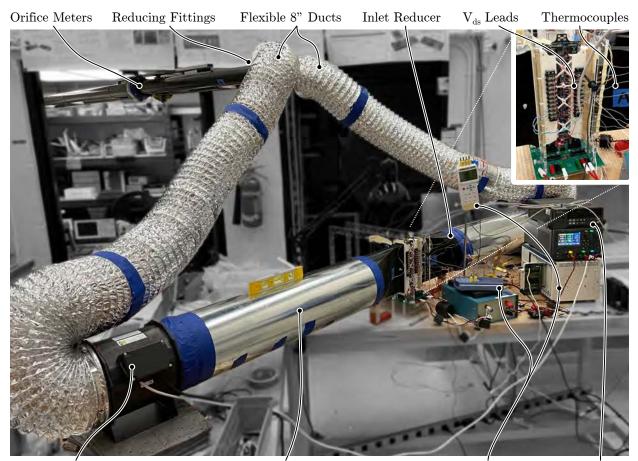

|            | Custom test fixtures, instrumentation and scripted acquisition equipment for<br>measuring thermal performance of a complete inverter module. Variable speed<br>blowers provide cooling air, drawing air through a custom mass flow meter. The<br>module (inset) is wired with thermocouples and drain-source voltage monitors<br>per the test procedure described in this section. | 61 |

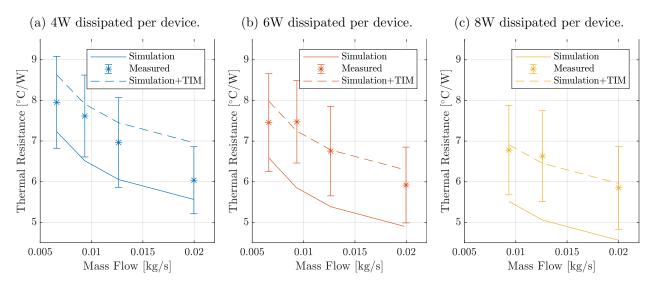

| 3.13       |                                                                                                                                                                                                                                                                                                                                                                                    | 63 |

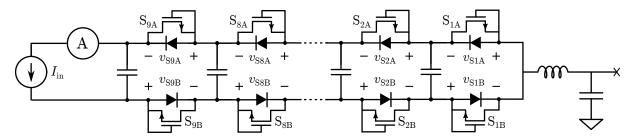

| 4.1        | Schematic representation of how $M$ interleaved 10-level FCML inverters can be interleaved within a phase-leg.                                                                                                                                                                                                                                                                     | 65 |

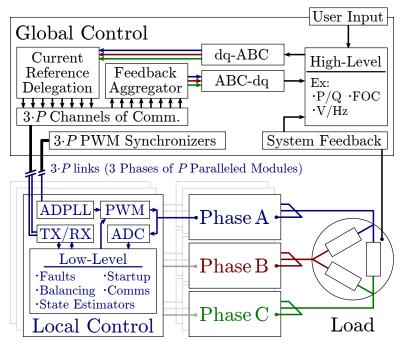

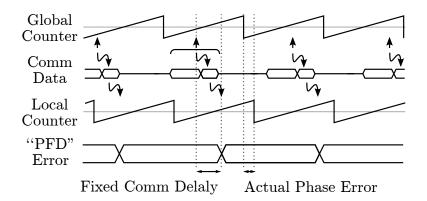

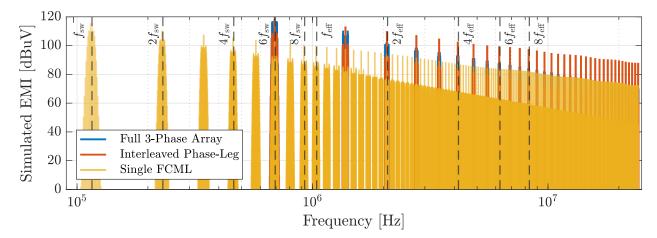

| 4.2        | High-level illustration of the hierarchical control structure, configured here to                                                                                                                                                                                                                                                                                                  |    |

| 4.3        | drive a three-phase load                                                                                                                                                                                                                                                                                                                                                           | 66 |

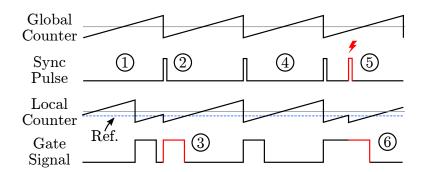

|            | PWM peripherals.                                                                                                                                                                                                                                                                                                                                                                   | 68 |

| 4.4<br>4.5 | Illustration of a synchronization scheme using a communication link and ADPLL.<br>Calculated output current spectra in the region of interest (i.e., harmonics of $f_{\text{eff}}$<br>for $N = 10$ ). The unit circles are normalized to the switching period, where<br>arrows indicate the phase shift of interleaved modules. Green ticks mark each                              | 69 |

|            | full cycle at the effective output frequency per switching period                                                                                                                                                                                                                                                                                                                  | 71 |

| 4.6          | Calculated input current spectra in the region of interest (i.e., harmonics of $f_{sw}$ )<br>for $N = 10$                                                                                                                                           | 72       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.7          | Calculated input current harmonic content using double Fourier analysis and assuming sinusoidal output current.                                                                                                                                     | 73       |

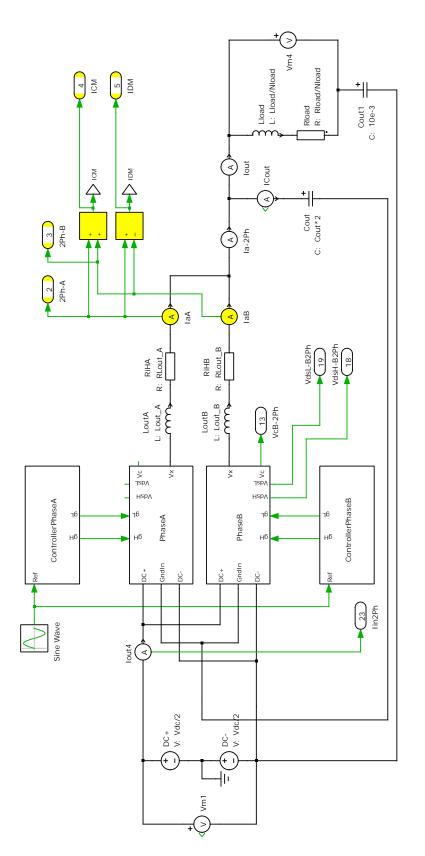

| 4.8          | PLECS Blockset schematic of a dual-interleaved, 10-level FCML for Monte Carlo                                                                                                                                                                       | 10       |

|              | simulations. The two interleaved converter phases are the modules labeled Phase A and Phase B and contain the switches and flying capacitors whose parameters are varied throughout the simulation. Measurements of interest (pertaining to         |          |

|              | current sharing) are highlighted: the two respective phase currents, as well as<br>their respective common- and differential-modes. The RMS values of these mea-<br>surements, as well as the average of output power into Rload, are computed in a |          |

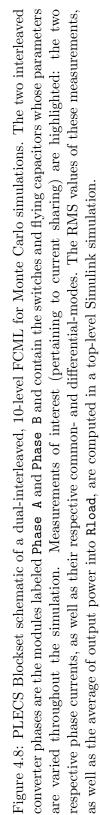

| 4.9          | top-level Simulink simulation                                                                                                                                                                                                                       | 74<br>76 |

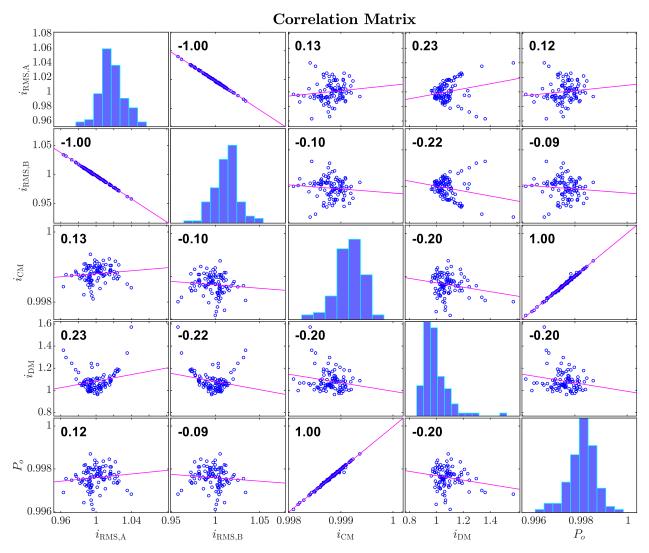

| 4.10         |                                                                                                                                                                                                                                                     | 77       |

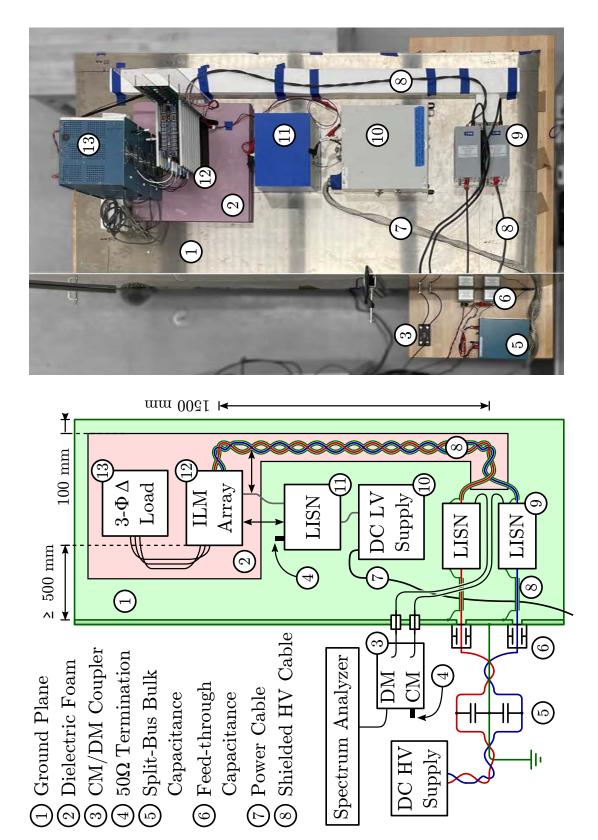

| 4.11         | Electromagnetic compatibility pre-compliance experimental setup for measuring                                                                                                                                                                       |          |

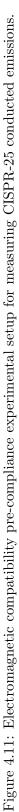

| 4 19         | CISPR-25 conducted emissions                                                                                                                                                                                                                        | 79       |

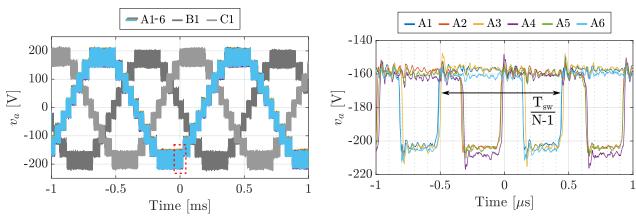

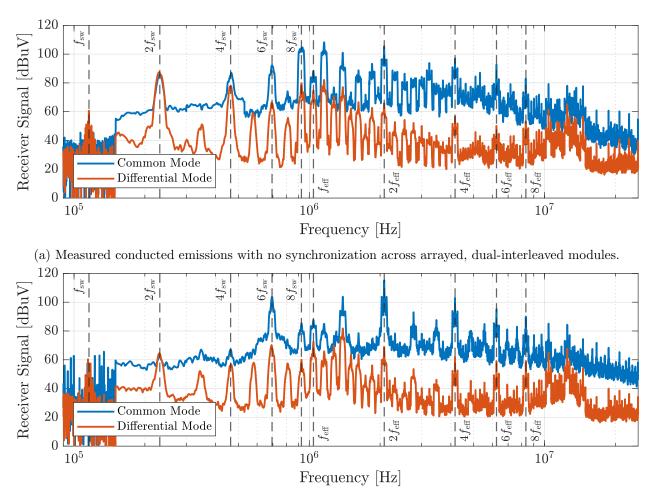

| 4.12         | without a common mode choke installed on the connection between the ILM array and the LV LISN.                                                                                                                                                      | 80       |

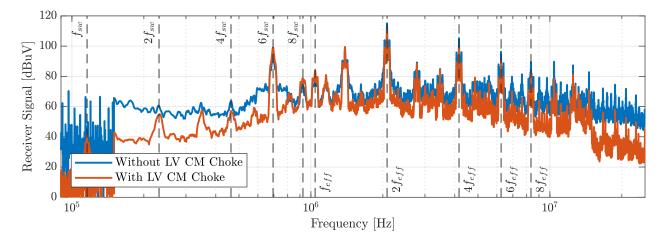

| 4.13         | Hardware photographs for the dual-interleaved module (ILM, on left) and three-<br>phase, 18 converter array (right).                                                                                                                                | 81       |

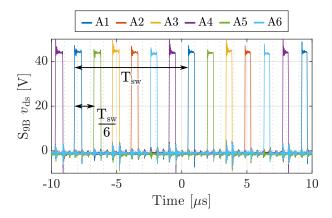

| 4.14         | Six $v_{ds}$ waveforms of the S <sub>9B</sub> low-side switches (closest to the DC bus) measured<br>for the converters of Phase A illustrate that 6-fold interleaving is achieved at the                                                            | 01       |

| 4 1 5        | input                                                                                                                                                                                                                                               | 82       |

| 4.15         | Experimental waveforms at 400 V DC and 6 kW output power for the 3-phase array comprised of nine dual-interleaved FCML modules (16 arrayed converters).                                                                                             | 82       |

| 4.16         | Common-mode and differential-mode conducted emissions measurements of the three-phase segmented drive operating at a 400 V DC bus and 6 kW output                                                                                                   |          |

|              | power, measured at the HV terminals of the test setup                                                                                                                                                                                               | 83       |

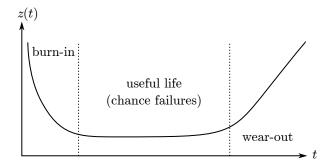

| 5.1          | The bathtub curve.                                                                                                                                                                                                                                  | 85       |

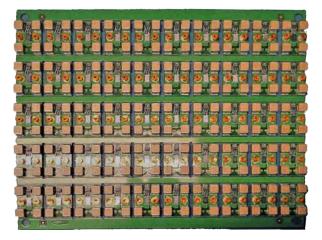

| $5.2 \\ 5.3$ | Panelized and contract assembled array of switching cell daughter boards<br>Panelized converter module circuit boards with features (routing and breakaway                                                                                          | 86       |

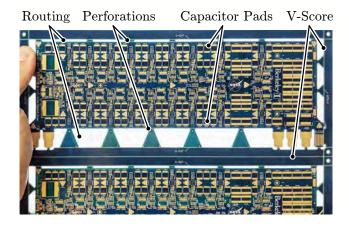

| 5.4          | tabs) to mitigate mechanical stress from post-assembly depanding                                                                                                                                                                                    | 87       |

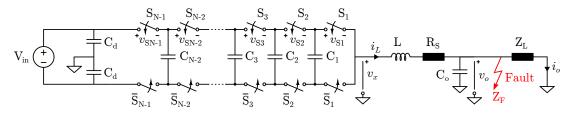

|              | split dc bus. The output filter capacitor is connected back to the dc-link midpoint.<br>A short-circuit occurs with a sudden connection of fault impedance, $Z_F$                                                                                   | 89       |

vii

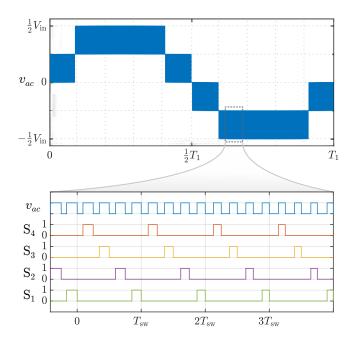

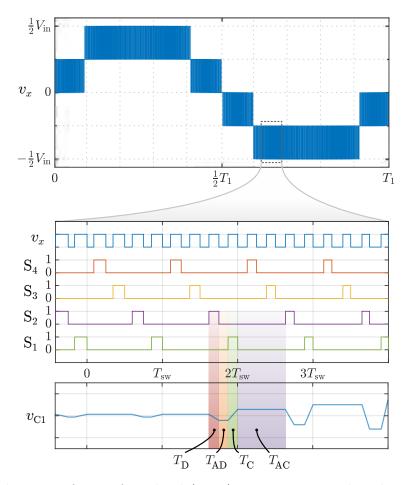

| 5.5         | Switching waveforms of a 5-level $(N=5)$ inverter. $v_x$ is plotted over a fundamental period $T_1$ , while the zoomed view illustrates the high effective frequency and                                                                                                                                                                     |     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | gate signals obtained using PSPWM. The bottom plot illustrates the charge and                                                                                                                                                                                                                                                                |     |

|             | discharge of a flying capacitor over each switching period, with a short-circuit                                                                                                                                                                                                                                                             |     |

|             | fault introduced between between $T_{sw}$ and $2T_{sw}$ .                                                                                                                                                                                                                                                                                    | 90  |

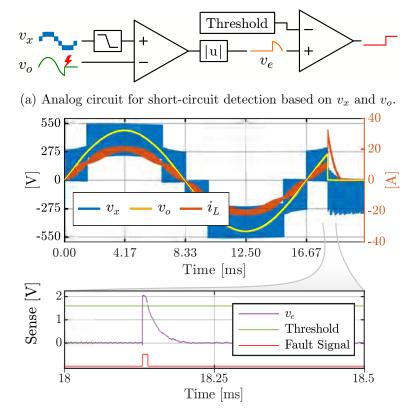

| 5.6         | Analog detection of short-circuit fault from the mismatch between estimated                                                                                                                                                                                                                                                                  |     |

|             | output voltage and actual output voltage                                                                                                                                                                                                                                                                                                     | 94  |

| 5.7         | PLECS simulation of the model-predictive approach for the 5-level converter from [60] at power factor of 0.8. The detection time, $t_{\rm FD}$ , is the model time-step, $T_s$ – after which mitigating, action (described in Section 5.1.3) is taken. For comparison, the dashed line shows the trajectory of the inductor current, $i_L$ , |     |

|             | without mitigation.                                                                                                                                                                                                                                                                                                                          | 96  |

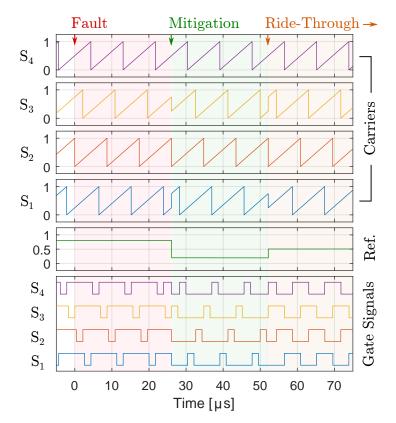

| 5.8         | Representative time-reversed, complementary switching strategy to reset inductor                                                                                                                                                                                                                                                             |     |

|             | fault current for $N=5$                                                                                                                                                                                                                                                                                                                      | 97  |

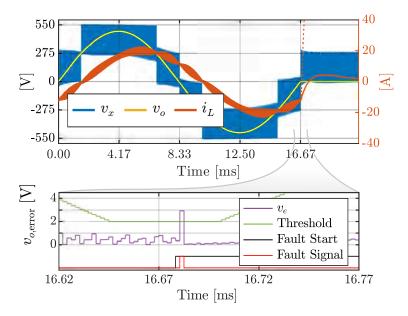

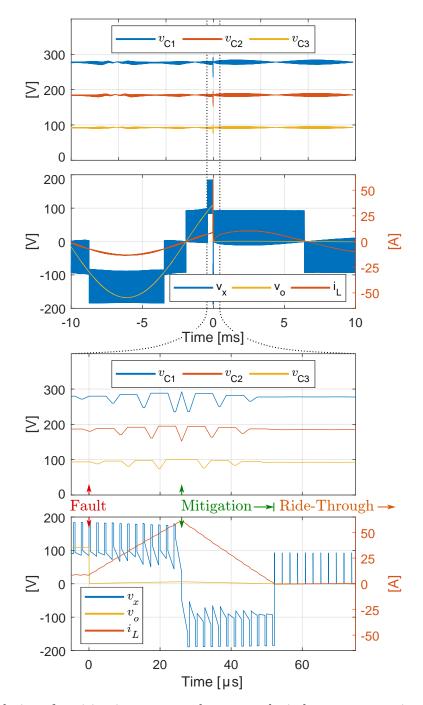

| 5.9         | Simulation of a mitigation strategy that resets the inductor current via reverse                                                                                                                                                                                                                                                             |     |

|             | capacitor charge/discharge actions.                                                                                                                                                                                                                                                                                                          | 99  |

| 5.10        | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                        |     |

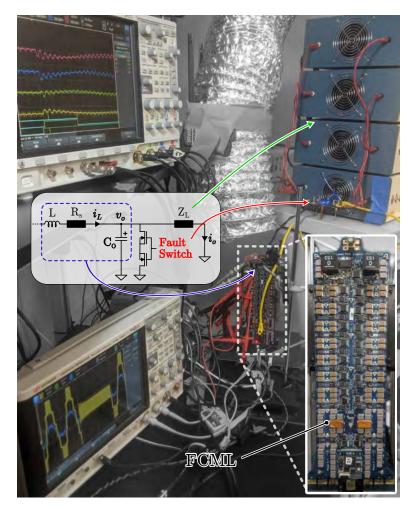

|             | cooling system. The inset highlights the converter hardware from [1] used in the                                                                                                                                                                                                                                                             |     |

|             | tests                                                                                                                                                                                                                                                                                                                                        | 101 |

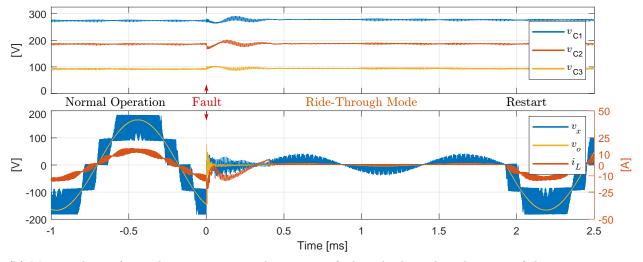

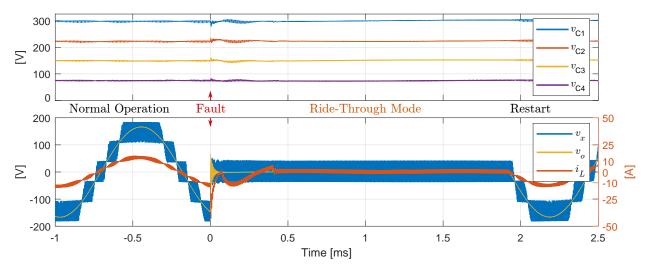

| 5.11        | 1                                                                                                                                                                                                                                                                                                                                            |     |

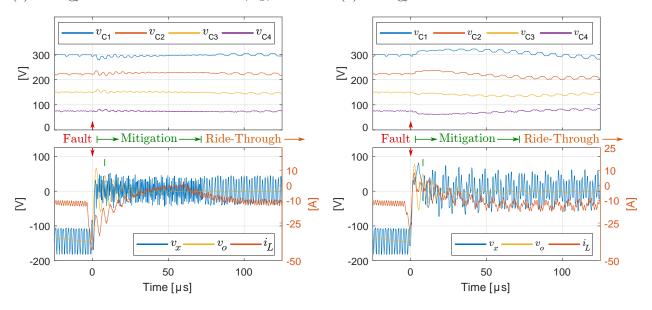

|             | through at 1.1 kW output power.                                                                                                                                                                                                                                                                                                              | 102 |

| 5.12        | Zoomed experimental waveforms showing short-circuit transient for the two mit-                                                                                                                                                                                                                                                               | 100 |

| <b>F</b> 10 | igation actions for a 6-level FCML.                                                                                                                                                                                                                                                                                                          | 103 |

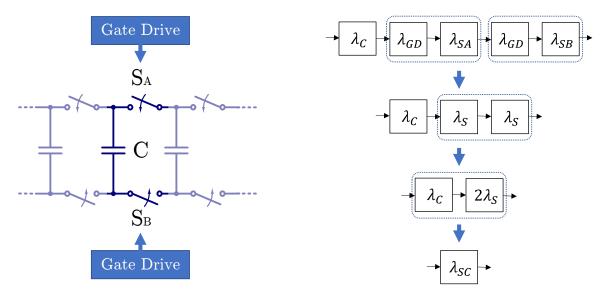

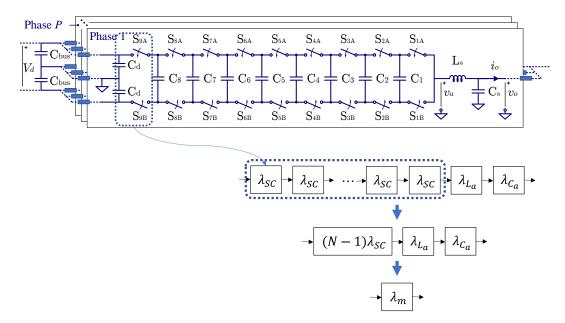

|             | Switching cell reliability structure for analyzing cell-level failures and redundancy.                                                                                                                                                                                                                                                       | 104 |

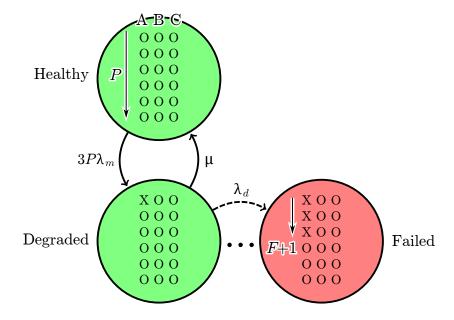

| 5.14        |                                                                                                                                                                                                                                                                                                                                              | 107 |

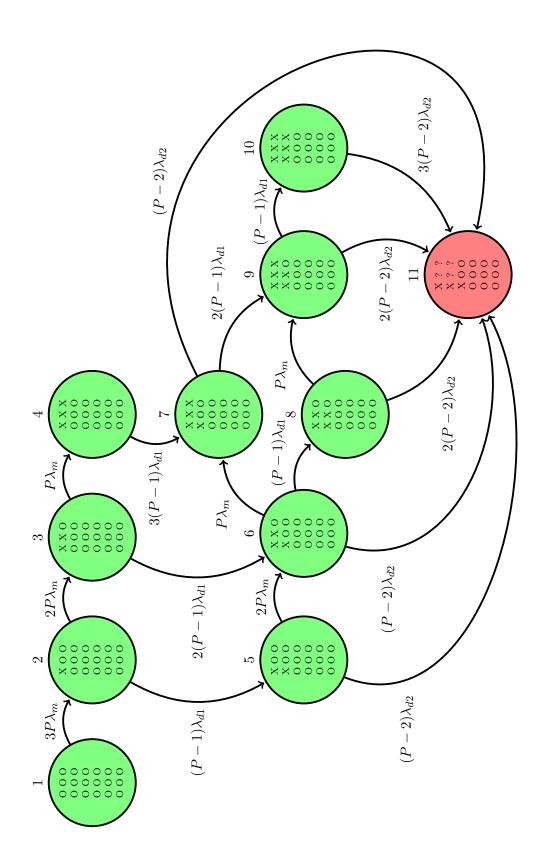

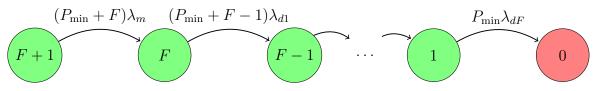

| 5 1 5       | modules $(P = 6)$                                                                                                                                                                                                                                                                                                                            | 107 |

| 0.10        | failures in a single phase-leg have complex relationship with the overall system                                                                                                                                                                                                                                                             |     |

|             | reliability. State 1 is the <i>healthy</i> state and state 11 is the <i>failed</i> state, with the                                                                                                                                                                                                                                           |     |

|             | remaining states indicating some degree of system degradation.                                                                                                                                                                                                                                                                               | 109 |

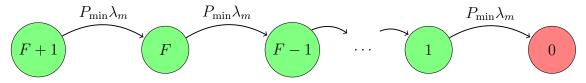

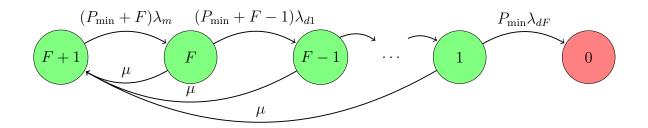

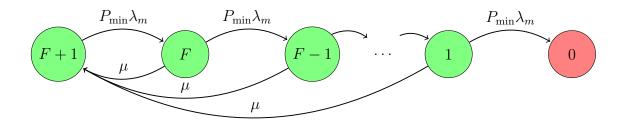

| 5.16        | Markov reliability model for a phase-leg implementing active redundancy.                                                                                                                                                                                                                                                                     | 110 |

|             | Markov reliability model for a phase-leg implementing cold standby                                                                                                                                                                                                                                                                           | 111 |

|             | Markov reliability model for a repairable phase-leg implementing active redundancy.                                                                                                                                                                                                                                                          |     |

|             | Markov reliability model for a repairable phase-leg implementing cold standby.                                                                                                                                                                                                                                                               | 112 |

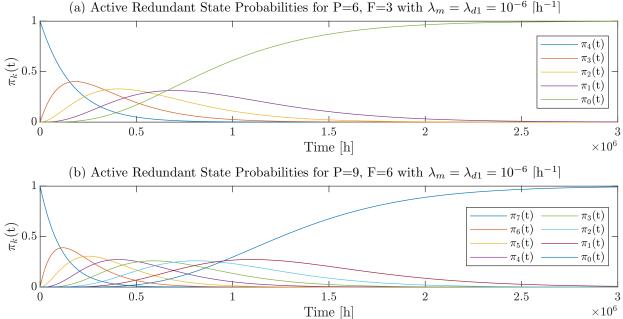

|             | State probabilities over time using (5.21) and $\Gamma$ from (5.17).                                                                                                                                                                                                                                                                         | 113 |

|             | A phase-leg of the three-phase, 3-level ANPC for illustrating switch count per                                                                                                                                                                                                                                                               |     |

|             | module.                                                                                                                                                                                                                                                                                                                                      | 115 |

| 5.22        | Module series reliability structure, dominated by the switching cell failure rate                                                                                                                                                                                                                                                            | 116 |

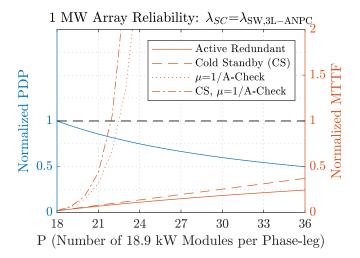

| 5.23        | Reliability and power density of a 1 MW array with various levels of redundancy.                                                                                                                                                                                                                                                             | 117 |

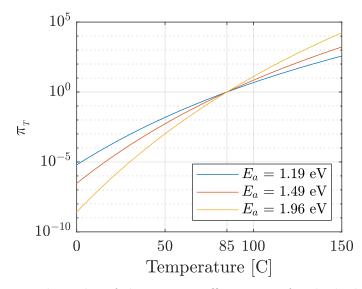

| 5.24        | Temperature-dependent failure rate coefficient, $\pi_T$ , for the high-k ceramic capac-                                                                                                                                                                                                                                                      |     |

|             | itors considered in this work.                                                                                                                                                                                                                                                                                                               | 119 |

| 6.1 | Highlight of the large area occupied by the gate drive circuitry in this work      | 122  |

|-----|------------------------------------------------------------------------------------|------|

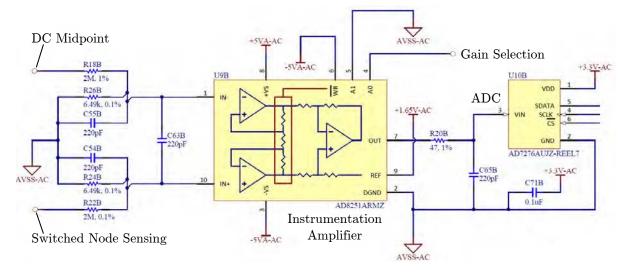

| 6.2 | Instrumentation amplifier used to capture the high-frequency and high-dynamic-     |      |

|     | range waveform at the switched-node of the FCML. Gain can be toggled between       |      |

|     | 1 and 2 to enhance resolution near zero-crossings or at low modulation             | 123  |

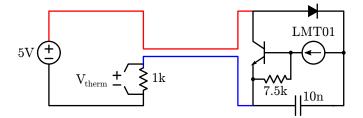

| 6.3 | Current amplifier for the LMT01 temperature sensors on the modules in this work    | .125 |

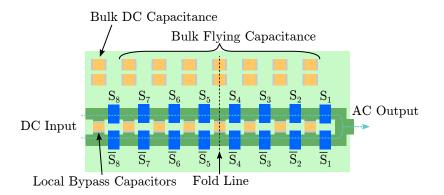

| 6.4 | A conceptual illustration of how layouts that implement remote flying capacitance  |      |

|     | can improve the routing of switching currents in a 9-level FCML.                   | 126  |

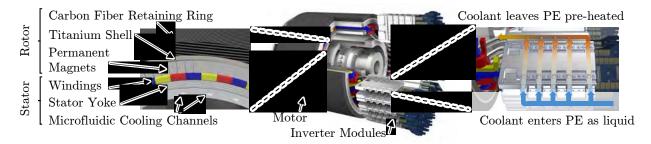

| 6.5 | Conceptual mock-up of how the converter array of this work might be scaled and     |      |

|     | integrated with the motor of [227]. In the rendering, a liquid cooling system and  |      |

|     | cold-plate is used to cool the module versus the individual, air-cooled heat sinks |      |

|     | presented in Chapter 3                                                             | 127  |

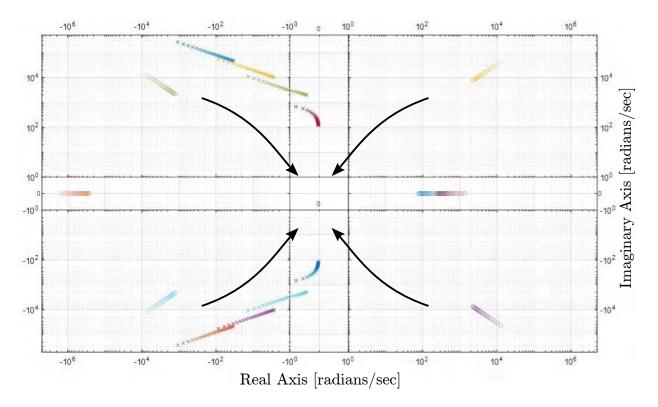

| 6.6 | A root locus plot for the input-to-state transfer function for one of the flying   |      |

|     | capacitors of the 10-level converter of this work, as the switching frequency is   |      |

|     | swept from 20 kHz to 115 kHz. The arrows indicate the direction of the pole and    |      |

|     | zero movement as frequency increases, while the colors indicate pole-zero pairs.   | 128  |

# List of Tables

| 1.1 | NASA key performance parameters for an electric drivetrain [27]                  | 4  |

|-----|----------------------------------------------------------------------------------|----|

| 1.2 | Key 2025 targets in the US Drive 2025 electric powertrain roadmap [32]           | 5  |

| 1.3 | Key benefits of the FCML topology [57]                                           | 10 |

| 2.1 | Capacitor selections per interleaved phase.                                      | 14 |

| 2.2 | Converter bill of materials                                                      | 15 |

| 2.3 | Converter mass breakdown.                                                        | 16 |

| 2.4 | Experimentally measured commutation loops for various switching cells            | 38 |

| 2.5 | Key performance metrics for the design of this work.                             | 45 |

| 3.1 | Selection of appropriately sized miniature springs from Acxess Spring            | 51 |

| 3.2 | Components used in the orifice meter for measuring mass flow                     | 60 |

| 5.1 | Table of key parameters and critical fault clearing times for recently published |    |

|     | converters                                                                       | 92 |

#### Acknowledgments

Much of this work was both motivated and funded by the Advanced Air Transport Technology (AATT) Project at the National Aeronautics and Space Administration (NASA) through cooperative agreement NNX14AL79A. Particular thanks are due to Andrew Provenza of NASA Glenn Research Center for providing guidance and feedback during monthly program reviews, and support through the entire length of the program – especially during a major change in research campuses. Additional support and constructive conversations were provided by Ralph Jansen, Dr. Cheryl Bowman and Dr. Nateri Madavan, and their generosity in sharing their time is greatly appreciated.

Additional support has been provided by the Vehicle Technologies Office in the United States Department of Energy through the Electric Drive Technologies Consortium (EDTC) under Award Number DEEE0008712. Advice and guidance from Dr. Vipin Gupta was particularly appreciated as the research in this work began to transition from a proof-ofconcept towards hardware that would be ready for integration in demanding automotive environments.

Several members of the Pilawa Group deserve special mention for their direct contributions to the NASA project or the EDTC project that supported this work: Pourya Assem for his work in designing the control cards used in this work, writing the initial versions of code for each, and for his insight in analog and digital circuits; Chris Barth for trailblazing the first implementations of high-level-count, high-voltage, flying capacitor multilevel converters and inverter array architectures (as well as spinning a machine with an early build of the hardware in this work); Thomas Foulkes for leading an effort to characterize dynamic on-resistance (a significant loss mechanism noted in Chapter 2) and fostering collaborations; Samantha Coday for assisting in all aspects of converter module design and test; Joseph Schaadt for his contributions to the thermal design, fabrication and eventual experimental measurements (with fruits of these labors in Chapter 3); Avinash Jois for continuing to advance the control architecture and occasionally getting roped into assembly tasks; Mads Taul for his work on short-circuit fault analysis and mitigation (much of which was successfully tested for Chapter 5); Amanda Jackson for learning so much in such a short amount of time to help design a system that speeds up testing of converters like those in this work; Logan Horowitz for taking over all of the low-inductance commutation loop design, analysis and measurement that has only just begun; and Roderick Bayliss, who joined the group just in time to help with a myriad of conducted emissions tests (presented in Chapter 4) and inherit a pile of mostly working converters. Dr. Tomas Modeer, who as post-doc with the group developed the first precursor to the module and methods of Chapter 2, also provided continuing technical guidance, encouragement and journal edits over the course of this work.

Of course, in addition to the technical support, all of the group members above – as well as Kelly, Rose, Maggie, Rahul, Nathan B., Nathan E., Ting, Francesca, Derek, Zitao, Zichao, Joseph L., Enver, Andrew and Pei – provided a wonderful social circle for hikes, barbecues, and happy hours. Derek and Zitao were especially valuable technical, professional and personal sounding boards as part of the same (if not just a bit earlier) graduating cohort.

Much credit is also due to the professors serving on the committee of this work – beyond the time they volunteered so generously. Teaching power electronics as a Graduate Student Instructor for Prof. Sanders provided valuable experience and perspective with previously familiar concepts, while his comments in both research meetings and graduate seminars stimulated interest in areas that were less familiar. Taking Prof. Callaway's low-inertia power systems seminar provided valuable insight into both low-level and systems-level challenges – and opened a door to working with his students for a summer; Jose, Ciaran and Rodrigo shared both their technical understanding and modeling expertise, and taught so much through example on how to architect and manage a software development project for research. Additionally, the coursework, review of prior work, and one-on-one meetings with Prof. Dominguez-Garcia provided immensely useful experience with both reliability concepts and modeling dynamical and stochastic systems in general. This informed much of Chapters 5 and 6, as well as much of the work to follow in the professional career of the author.

Finally, Prof. Pilawa-Podgurski: for carefully reading every digest and manuscript, then providing feedback to improve precision and clarity of technical language, add motivation and background that appeals to all readers, and catch a typo here and there; for ensuring funding was never an issue, and that the lab was always well equipped; for providing personal support and understanding when research, grad school, or just life seemed to be going pretty poorly; for organizing or joining lunches, power hours or other social events; for allowing a mutual trust and frankness all discussions, both professional and personal; for the first introductory power electronics lecture on a blackboard in LEES more than a decade ago; for giving an opportunity to a student who did not have the best undergraduate academic record but was willing to make up for it with a lot of hard work in grad school. Thank you.

# Chapter 1

# Vehicle Drivetrain Electrification

Portions of this chapter are adapted in part from [1] and [2].

In his 2018 book on the future of electric vehicles, *Three Revolutions*, Professor Daniel Sperling notes that, although electric vehicles have been in around since the 1830s, they were not always the "objects of desire" that Tesla, Rivian and other breakthrough manufacturers have made them today [3]. Indeed, after many early pitfalls and the limited range of debut models, it was only through decades of advancement in technologies – primarily in battery energy storage, but also power electronics – that the tide has turned toward mass vehicle electrification. While a complex mix of technological challenges, policy decisions and a fickle consumer market seemed to have "killed the electric car" as recently as 2006 [4], new marking campaigns by General Motors lauding thirty all-electric vehicle models by 2025 [5] show industry inertia is far greater now than when the single EV1 model was announced in the mid-1990s. At the same time, major transportation network companies like Lyft are announcing goals of migrating their fleets to zero-emission vehicles as early as 2030 [6]. Market moves like these signal a paradigm shift on a drastic scale and aggressive timeline.

Yet, it is possible this shift cannot come soon enough. As of 2017 estimates, transportation accounted for 22% of the global carbon dioxide emissions in the energy sector [7]. Since then, it is estimated that the slow pace taken to address this crisis means global warming is highly likely to reach *at least* 1.5 °C between 2030 and 2052 [8]. As such, an aggressive drawdown in emissions from fossil fuel use in transportation of nearly 90% is required between 2019 and 2070 to reach a sustainable development scenario [9]. While Sperling notes that mass vehicle electrification is only part of the solution, steps taken by fleets, municipalities and motorists can help decarbonize the vast spread of medium- to heavy-duty vehicles to passenger cars alike.

Although electrification of cars, trucks and other road and off-road vehicles has at least become a much more tangible prospect, aviation remains a subset of the transportation sector that is still difficult to decarbonize. Over the past two decades, agencies such as the National Aeronautics and Space Administration (NASA) in the United States and the European Commission have driven research to support more fuel-efficient air travel [10, 11].

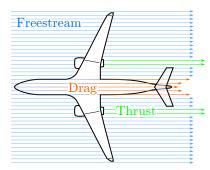

(a) Illustration of a traditional commercial aircraft design, with two large combustion turbines providing thrust. The air stream that flows along the boundary layer of the aircraft fuselage is slowed compared to the freestream, causing drag and inefficient flight [13].

(b) Illustration of a turboelectric aircraft based on the NASA STARC-ABL concept [12]. Two large combustion turbines provide thrust as well as electrical power to drive an aft thruster that ingests and re-energizes the slowed boundary layer, reducing net drag.

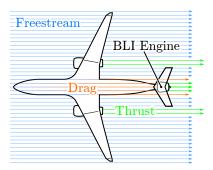

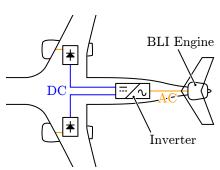

(c) A potential electrical bus design to support more electric aircraft propulsion. Alternating current from the turbogenerators is rectified and distributed over a highvoltage dc bus. This work addresses the inverter design for the subsequent conversion back to ac.

Figure 1.1: Depictions of more electric aircraft propulsion leveraging boundary layer ingestion, as adapted from concepts and figures in [12] and [13]. For illustrative purposes, contributions to drag from the wings of the aircraft are assumed to be less than that of the fuselage and are ignored.

In particular, through the NASA Advanced Air Transport Technology program, a decadeslong research program has already contributed to more efficient combustion turbines, while several innovative concepts have been proposed to further reduce emissions – including bold changes in airframe design and hybrid propulsion architectures [12].

Extensive discussion of aircraft is beyond the scope of this work, but it is worth noting two disruptive technologies in particular: boundary layer ingestion and distributed propulsion. In short, the former is when air along the boundary layer (air at the boundary of the airframe) is ingested in a propulsor and "re-energized." A leading concept places a 1-2.6 MW electric motor at the aft of the aircraft where drag otherwise caused by the wake of the aircraft can be reduced, increasing propulsive efficiency [14]. This concept of boundary layer ingestion (BLI) is illustrated in Fig. 1.1. Distributed propulsion, in which many propulsors are installed across a wing (instead of the typical two large engines) can also provide an aerodynamic boost and enable drastically different shapes in airframe design [15]. Both of these approaches are best facilitated through the use of electric motors, which can be more compact and allow for better design freedom than their combustion counterparts [12, 16]. Yet, while small electric aircraft are in commercial development, only concepts exist for larger aircraft (e.g., greater than 150 passengers) that carry a majority of all air traffic – and performance of electrical systems needs to advance nearly an order of magnitude to realize them [17]. Nonetheless, with industry giants like General Electric and Rolls Royce even engaged in some of the most promising research in commercial electric aircraft, this challenge is being taken seriously [18].

Partially or fully electrifying vehicles while still meeting the demands of industry roadmaps

and consumers alike poses both engineering challenges as well as many human factors. This thesis will focus on just one but very important aspect of vehicle electrification: the inverter drivetrain. This important building block of the vehicle is what is converts stored energy into energy that actually spins a motor. This may mean converting energy stored in batteries in an electric car or energy from a high voltage dc bus supplied by generators in a turboelectric aircraft [12]. While it is worth noting that some concepts explore superconducting systems [19] with motors [20] and power electronics [21, 22] operating at cryogenic temperatures, this work is confined to realizations at standard atmospheric conditions. As such, both automotive and aircraft systems share key design requirements, manufacturing challenges and scalability goals for meeting aggressive electrification needs. In addition to meeting specific input voltage, peak output power and power density targets codified in industry roadmaps (which are reviewed in the following section), the concurrent goals of thermal management and reliability are also paramount to these applications.

This work thus proceeds as follows: the remainder of this chapter will review the key performance requirements of future electric propulsion systems. Several prominent and promising topologies will be reviewed, highlighting recent advances in both wide band-gap semiconductor development and integration. Then, an unconventional approach will be introduced that contrasts with much of the prior work – but holds promise to achieve the order-ofmagnitude improvements required by the industry targets, and spur the rapid innovation necessitated by the climate crisis [23]. After that, the remaining chapters will provide an indepth look at the design and analysis of the electrical (Chapter 2) and thermal (Chapter 3) performance, followed by scalability (Chapter 4) and reliability (Chapter 5) of the proposed architecture. Finally, Chapter 6 concludes the thesis and presents potential extensions to the work in future studies.

## **1.1** Constraints and Performance Criteria

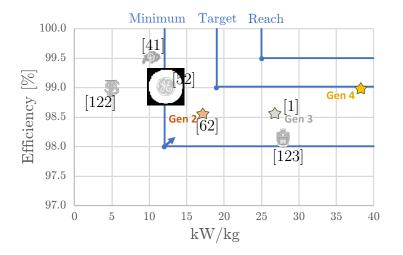

To focus on reducing emissions of single-aisle, twin-engine aircraft, which make up a significant proportion of all air travel, NASA has conducted several studies to estimate how the various interconnected systems on an aircraft might benefit from full, or at least partial, electrification [24–26]. The primary figure of merit is the fuel burn rate, which is a factor of both the weight of the aircraft (more thrust is necessary to keep a heavier aircraft aloft) and efficiency of the propulsion system (which allows travel of greater miles per gallon, as it were). Lower efficiency also means more fuel is required for a given flight, and is thus coupled to the aircraft weight. These studies produced key performance parameters for the electric drivetrain and identified a target design space – in spite of the series of energy conversions involved in a hybrid architecture (chemical to mechanical to electrical back to mechanical) – where a drive designed beyond the break-even frontier would lead to an increase in aircraft propulsive efficiency upwards of 10%. This frontier is defined as a trade-off between efficiency and gravimetric power density (lightweight, yet still supplying the required output power), and culminated in program targets specified in Table 1.1. The minimum targets correspond

|                | Minimum   | Target    | Stretch   |

|----------------|-----------|-----------|-----------|

| Specific Power | 12  kW/kg | 19  kW/kg | 25  kW/kg |

| Efficiency     | 98.0%     | 99.0%     | 99.5%     |

Table 1.1: NASA key performance parameters for an electric drivetrain [27].

to the break-even frontier; technology here would demonstrate the concept is plausible, while meeting the reach goal would indicate propulsive efficiency gains are indeed achievable.

In addition to these targets that directly drive vehicle efficiency, two higher-level constraints must also be met. First, a sophisticated electrical distribution system is required for any more electric aircraft, and the weight and efficiency of this system must also be optimized. Several studies considered both ac and dc bus systems up to 6 kV, where higher voltages can be traded against lower currents (and therefore lower conductor mass) at the same power level [28, 29]. A synchronous, high-voltage, ac grid had been shown to be the most efficient implementation, but the synchronous nature tightly couples the generator and propulsor speeds and removes a significant degree of freedom in system design. Conversely, a high-voltage, dc bus, with independent rectifiers and variable speed drives providing power conversion as needed, but trades some efficiency for added flexibility [30]. Nonetheless, flexibility was preferred for the designs pertaining to this work, so a dc grid was selected as the lowest mass option, illustrated in Fig. 1.1c. While dc voltages of up to 3 kV will continue to provide system level benefits, 1 kV represents the knee of the performance curve relating input voltage to power density [28] and was established as an appropriate target for this work in [27].

Finally, the high specific power (HSP) motors for this application also pose unique challenges: lightweight, "iron-less" (typically permanent magnet) machines have very low inductance and require a low total harmonic distortion (THD) drive current, while brush-less dc and switched reluctance variants require a carefully shaped current waveform. Some inverter designs in Section 1.2 have made exciting progress towards addressing this application and these motors. However, unconventional hybrid architectures may ultimately provide the great leaps in performance necessary for electric flight.

Recently, the U.S. Department of Energy launched a similar research program to accelerate electrified propulsion through the Advanced Research Projects Agency – Energy (ARPA-E) program titled ASCEND (Aviation-class Synergistically Cooled Electric-motors with iNtegrated Drives) [31]. This aggressive program demands similar performance to that defined by NASA, but also provides a target flight profile to benchmark against (as done in Chapter 2). Additionally, this program further requires compliance with DO-160, a standard covering everything from environmental conditions to electromagnetic emissions. While the former is outside of the scope of this work, the latter is addressed in Chapter 4.

In the past few years, there has also been a similar push to advance electric vehicle technologies. To cater to diverse consumer preferences and use cases, and to forge a path towards energy efficiency and reliability of transportation choices, the U.S. DRIVE (Driving Research

| Power                 | Peak             | Average   | Efficiency | Voltage    | Fundamental |

|-----------------------|------------------|-----------|------------|------------|-------------|

| Density               | Power            | Power     |            | Rating     | Frequency   |

| $100 \ \mathrm{kW/L}$ | 100-200 $\rm kW$ | 55-110 kW | >98 %      | 900-1200 V | 2 kHz       |

Table 1.2: Key 2025 targets in the US Drive 2025 electric powertrain roadmap [32].

and Innovation for Vehicle efficiency and Energy sustainability) consortium has sought to foster collaboration between government organizations, private companies and academic institutions to establish a vision for vehicle research and development [33]. Through regular consortium meetings facilitated by the Vehicle Technologies Office in the United States Department of Energy, an Electrical and Electronics Technical Team Roadmap was produced to guide such efforts [32]. This document ties many of the high level goals of emissions reductions, vehicle range and peak power, price point and lifetime to key requirements of future electric drivetrains, several of which are listed in Table 1.2.

The first target of note is the power density. While gravimetric power density and volumetric power density are both important objectives to maximize, the volumetric density is more heavily weighted for automotive applications. This is because the space in automobiles is limited; where it is not used for passenger or cargo, it would otherwise be used for batteries to extend the range of the vehicle. The high power density of 100 kW/L represents an order of magnitude increase compared to what has been possible with extant automotive technologies. The related goal of a high output power is also necessary to ensure desirable acceleration characteristics as well as satisfy towing and other high-torque applications served by conventional utility vehicles. Additionally, the powertrain must be highly efficient to get the most range out of each charge.

The remaining milestones are again, slightly more nuanced. For instance, while currentgeneration electric vehicles typically host a 400 V dc bus, higher voltages are increasingly more appealing – especially with the advent of wide-bandgap power semiconductors that support these voltage ratings [34]. Although there are system and energy density benefits gained by moving to higher bus voltages, the targets upwards of 800 V dc are actually in support of fast dc charging; there is less loss "at the pump," as it were, when pushing charge rates above 350 kW [35]. That said, high-voltage drives have also shown performance boosts in heavy-duty vehicles – with a recent demonstration by John Deere of a 200 kW industrial loader featuring a dc bus over 1 kV [34]. As for the motors, most high-specific-power machines have tended to feature a high pole count, and therefore high electrical frequency – upwards of several kilohertz [36–38]. As such, the inverter system must provide the corresponding modulated waveform – necessitating either a much higher switching frequency or additional harmonic filtering.

# 1.2 Survey of Topologies

The challenges outlined above have motivated an exploration of diverse converter technologies and topologies. While this section is not meant to provide an exhaustive list, it does highlight many inverter implementations that have achieved significant performance against the targets, or otherwise have desirable attributes. In general, these systems have been enabled by wide-bandgap devices [39], and 2- and 3-level designs are ubiquitous – mostly improving in step with devices and packaging technology [40].

### 1.2.1 Two-Level Half-Bridge

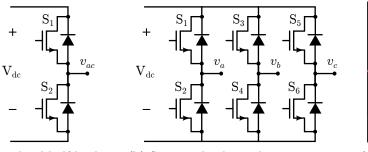

The traditional half-bridge, or six switch module in a three-phase converter, is is the 2level system common to extant electric vehicle drivetrains. This topology is illustrated in Fig. 1.2b, where the ac output node can toggle between the positive and negative rail of the dc bus (i.e., the levels of the 2-level waveform). While silicon insulated-gate bipolar transistors (IGBTs) have been the workhorses of such converters at both high-voltage and high-current for some time, these devices are accompanied with high switching losses and thus limit the switching frequency. As such, significant filtering of the output of each line phase would be required to drive an HSP machines described above.

However, silicon carbide devices – which allow for very high blocking voltages with commensurate conduction losses and significantly lower switching loss as silicon IGBTs – have expanded the operating range for these converters [41]. Additionally, very high output currents (and therefore torque) can be achieved when the devices are paralleled [42]. This is evident in the Tesla Model 3 powertrain [34], the first commercial electric vehicle to use silicon carbide. However, other than paralleling novel devices, there is little room for innovation on this straightforward, but limited topology. Additionally while these devices have reduced intrinsic, dynamic parasitics (e.g., gate charge and output capacitance), switching transition speeds and frequencies are still typically limited to under 100 kHz. While the lower parasitics do reduce switching energy, the fact that the devices must charge and discharge

(a) 2-level half-bridge (b) Six-switch, three-phase converter. phase-leg.

(c) A representative 2-level waveform over one fundamental period. The switched node,  $v_{ac}$ , alternates between V<sub>dc</sub> and 0 V.

Figure 1.2: The common, 2-level bridge topology, with corresponding single-phase output waveform.

to the entire bus voltage each commutation is the dominant factor, as switching loss scales with the square of this voltage. This large rate of change in voltage, dv/dt, also means a significant amount of effort must be spent on output filter design if it is meant to interface with any HSP machines requiring sinusoidal input current. As such, much of the literature is spent optimizing magnetics and switching parameters to find the frontier of this space [43].

A significant amount of effort has also been spent minimizing dc bus inductance to allow for faster switching. This parasitic inductance on the dc side of the switches stores energy while the device is in the on state. When the device switches off, this energy charges the switch drain-source capacitance. If the parasitic inductance is large enough, at high currents this stored energy can cause detrimental overshoot of the device. Unless this inductance can be reduced, the only other recourse is to slow the speed of the device transition, though this would incur greater overlap loss (see Chapter 2). As such, the best designs use indepth modeling, careful routing and innovative manufacturing methods to achieve a lowinductance, simulated (though not measured) to be as low as 6 nH for 1 kV designs [44].

#### 1.2.2 Three-Level T-Type

The 3-level T-Type converter phase-leg is illustrated in Fig. 1.3a. Here, the dc bus is divided into three levels,  $+V_{dc}/2$  and  $-V_{dc}/2$  as well as a neutral midpoint. The four switches in each phase leg (12 switches total in a three-phase converter) connect the ac output to these levels in a sequence defined by the specific modulation strategy to generate the waveform shown Fig. 1.3c. Note, a four-quadrant switch is needed at the midpoint connection to prevent selfcommutation (through the diodes) to the wrong state when inductively loaded. For example, a positive current flowing out of the  $v_{ac}$  node would always turn on D3 before D4 without the

(c) A representative 3-level, PWM waveform over one fundamental period. The switched node,  $v_{ac}$ , alternates between  $+V_{dc}$  and 0 V or  $-V_{dc}$  and 0 V depending on the point in the line cycle.

reverse switch S2 to selectively prohibit this path as needed when driving positive current at the negative half of the line cycle. Since the four-quadrant switch only sees half of the dc bus voltage, lower voltage devices may be used – but the other two devices will need to block the full dc bus voltage. Additionally, complementary switch pairs S1/S3 and S2/S4 only commutate during half of the cycle, so implementations with silicon IGBTs can still yield improved performance [45].