### Extending Temporal-Vector Microarchitectures for Two-Dimensional Computations

Colin Schmidt

#### Electrical Engineering and Computer Sciences University of California, Berkeley

Technical Report No. UCB/EECS-2021-186 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2021/EECS-2021-186.html

August 12, 2021

Copyright © 2021, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Extending Temporal-Vector Microarchitectures for Two-Dimensional Computations

by

Colin Schmidt

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Krste Asanović, Chair Borivoje Nikolić Robert C. Leachman

Summer 2021

### Extending Temporal-Vector Microarchitectures for Two-Dimensional Computations

Copyright 2021 by Colin Schmidt

#### Abstract

Extending Temporal-Vector Microarchitectures for Two-Dimensional Computations

by

Colin Schmidt Doctor of Philosophy in Computer Science University of California, Berkeley Krste Asanović, Chair

Modern computing is shaped by technology trends, like a slowing Moore's law and lack of Dennard scaling, as well as application trends, like mass application of machine learning. Technology has constrained modern computer architectures to focus on energy-efficiency in order to improve, battery life, total cost of ownership, and even performance. Emerging deep-learning applications require computation volumes that increase exponentially and yet change in structure substantially every few years. One solution for both of these problems is specialized programmable architectures, that can adapt to new applications while specializing for the commonalities, and thus improving energy-efficiency.

This thesis presents a set of two-dimensional architecture extensions for Hwacha an existing vector-fetch architecture designed to improve energy-efficiency on two-dimensional computation while remaining fully programmable. This thesis discusses the constraints modern CMOS process technologies place on such an architecture, and describes several silicon implementations of similar architectures. Finally, this thesis presents the physical implementation of such extensions and their realized energy-efficiency gains on select applications. To Sloka, who always believed in me and made the long nights worth it.

# Contents

| Co | Contents           |                                                                     |               |

|----|--------------------|---------------------------------------------------------------------|---------------|

| Li | st of              | Figures                                                             | iii           |

| Li | st of              | Tables                                                              | v             |

| 1  | <b>Intr</b><br>1.1 | oduction<br>Energy Efficiency, Specialization, and Programmability  | $\frac{1}{2}$ |

|    | 1.1<br>1.2<br>1.3  | General-Purpose Data-Parallel Programmable Specialization           | $\frac{2}{3}$ |

| 2  |                    | a-parallel Architectures                                            | э<br>5        |

| 4  | 2.1                | Fixed-Width Packed-SIMD Architectures                               | <b>5</b><br>7 |

|    | $\frac{2.1}{2.2}$  | Many-Threaded SIMT Architectures                                    | 8             |

|    | $\frac{2.2}{2.3}$  | Traditional Vector Architectures                                    | 10            |

|    | $2.3 \\ 2.4$       | Implementation-time variable-length vector packed-SIMD Architecture | 10            |

|    | $2.4 \\ 2.5$       | RISC-V Vector Architecture                                          | 13            |

|    | $2.0 \\ 2.6$       | Vector-Fetch Architecture                                           | 13<br>14      |

| 3  |                    | ti-Dimensional Vector Applications and Architectures                | 17            |

|    | 3.1                | Origins of Two-Dimensional Architectures                            | 18            |

|    | 3.2                | Multi-dimensional Applications and Libraries                        | 20            |

|    | 3.3                | Deep Neural Network Operations                                      | 21            |

|    | 3.4                | Modern Two-Dimensional Architecture Extensions                      | 22            |

| 4  | 1 8                |                                                                     | <b>24</b>     |

|    | 4.1                | Modern Technology Constraints on Digital Design                     | 24            |

|    | 4.2                | Vector Architecture Design Constraints                              | 28            |

|    | 4.3                | Hwacha Architecture Details                                         | 38            |

|    | 4.4                | Hwacha Microarchitecture Implementation Choices                     | 40            |

| ٠ | ٠ | ٠ |

|---|---|---|

| 1 | 1 | 1 |

|   |   |   |

| 5       | Silicon Implementations of Hwacha         5.1       Hurricane-1                                                                                                                                                                                         | <b>51</b><br>51<br>58<br>66<br>78       |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|

| 6       | Design of a Two-dimensional Extension to Hwacha6.1Vector-Transpose Matrix Multiply6.2Sub-matrix Memory Operations6.3Future Extensions for Deep Learning                                                                                                 | <b>85</b><br>85<br>87<br>90             |  |  |  |

| 7       | RTL and Physical Implementation of Two-Dimensional Extension to<br>Hwacha7.1Two-Dimensional Control Structures7.2Latch and Reuse for VTMM7.3Sub-matrix load micro operations7.4Future Extensions for Machine Learning7.5Physical Implementation Results | <b>93</b><br>93<br>95<br>96<br>97<br>98 |  |  |  |

| 8<br>D: | Conclusion         8.1       Thesis Summary of Contributions         8.2       Future Work         Biography                                                                                                                                            | <b>104</b><br>104<br>105<br><b>106</b>  |  |  |  |

| Bi      | Bibliography 1                                                                                                                                                                                                                                          |                                         |  |  |  |

# List of Figures

| 2.1 | CSAXPY as C code with a single vectorizable loop                           | 6  |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | CSAXPY kernel mapped to a scalar architecture.                             | 6  |

| 2.3 | CSAXPY kernel mapped to the packed-SIMD assembly programming model         | 8  |

| 2.4 | CSAXPY kernel mapped to the SIMT assembly programming model                | 9  |

| 2.5 | CSAXPY kernel mapped to the traditional vector assembly programming model. | 10 |

| 2.6 | CSAXPY kernel mapped to the implementation-time variable-length vector ar- |    |

|     | chitecture.                                                                | 12 |

| 2.7 | CSAXPY kernel mapped to the RISC-V vector extension programming model      | 13 |

| 2.8 | CSAXPY kernel mapped to the vector-fetch programming model                 | 15 |

|     |                                                                            |    |

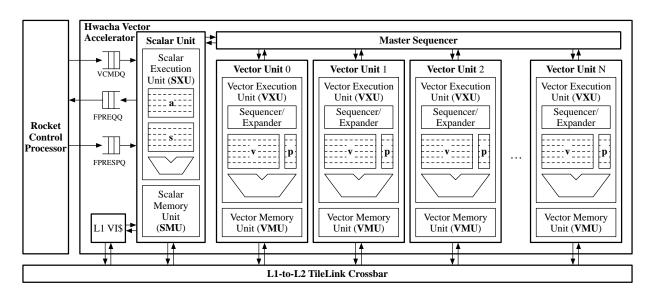

| $4.1 \\ 4.2$ | A high level diagram of the Hwacha microarchitecture                                                                                                            | $38 \\ 41$ |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

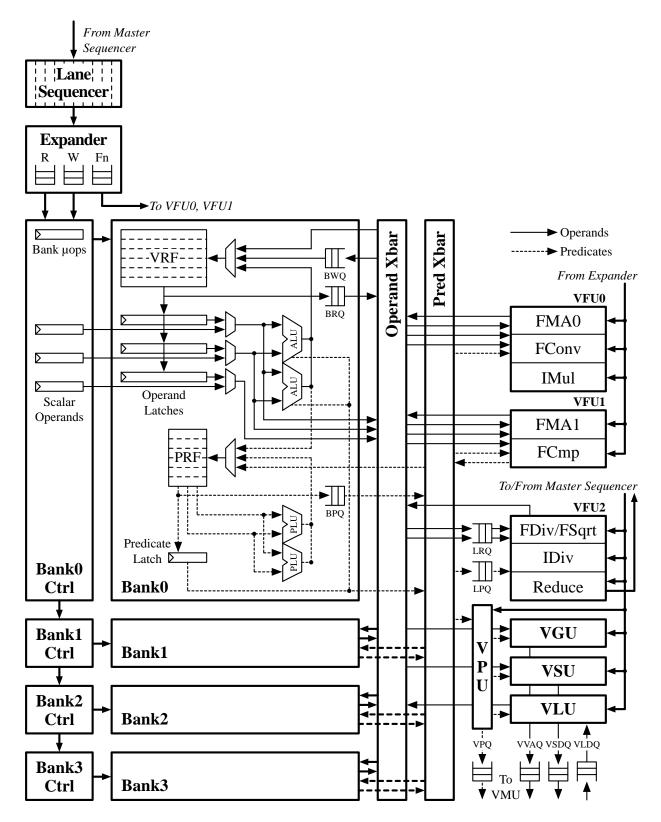

| 4.3          | A detailed diagram of Hwacha's vector data and predicate register files.                                                                                        | 43         |

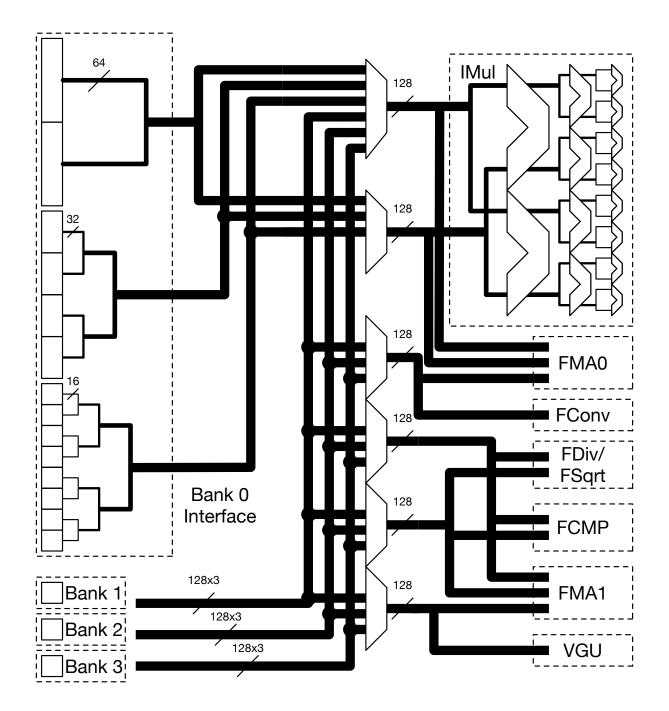

| 4.4          | A detailed diagram of Hwacha's shared functional units.                                                                                                         | 46         |

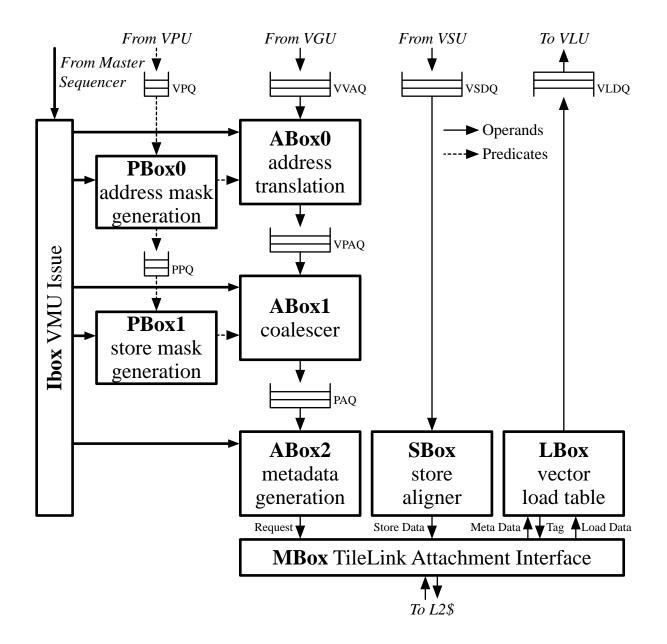

| 4.5          | A detailed diagram of Hwacha memory unit                                                                                                                        | 49         |

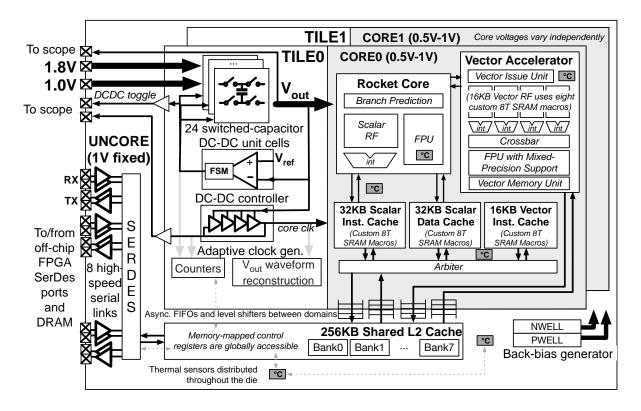

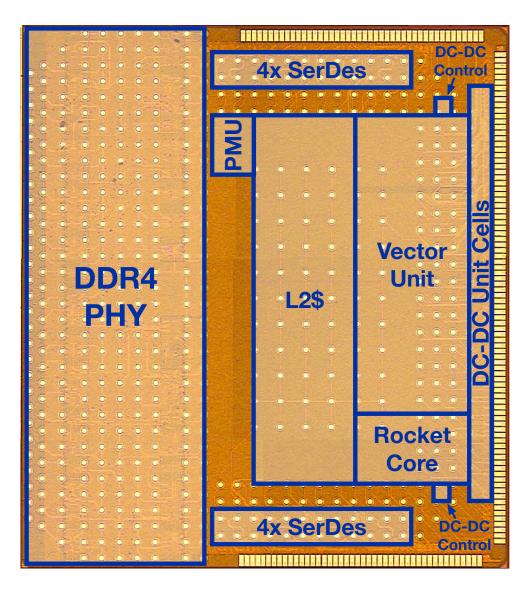

| 5.1          | An overview of the Hurricane-1 SoC and its components [97]                                                                                                      | 52         |

| 5.2          | Example of Hwacha's predicate register file congestion in Hurricane-1                                                                                           | 55         |

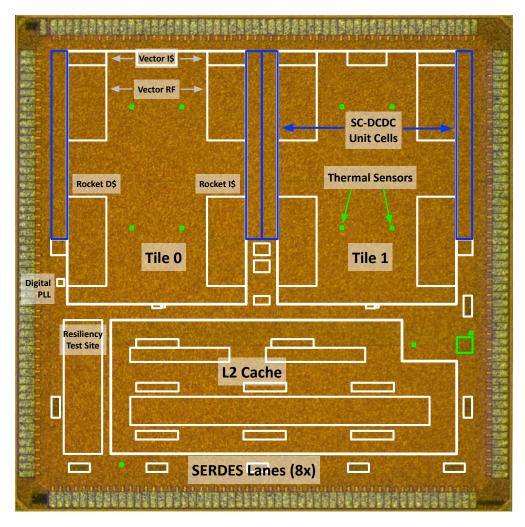

| 5.3          | An annotated diephoto of the Hurricane-1 SoC.                                                                                                                   | 56         |

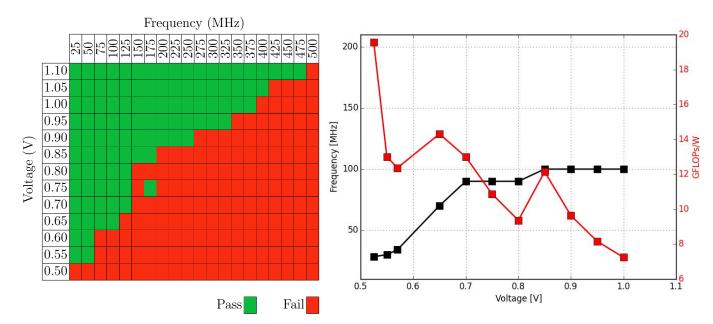

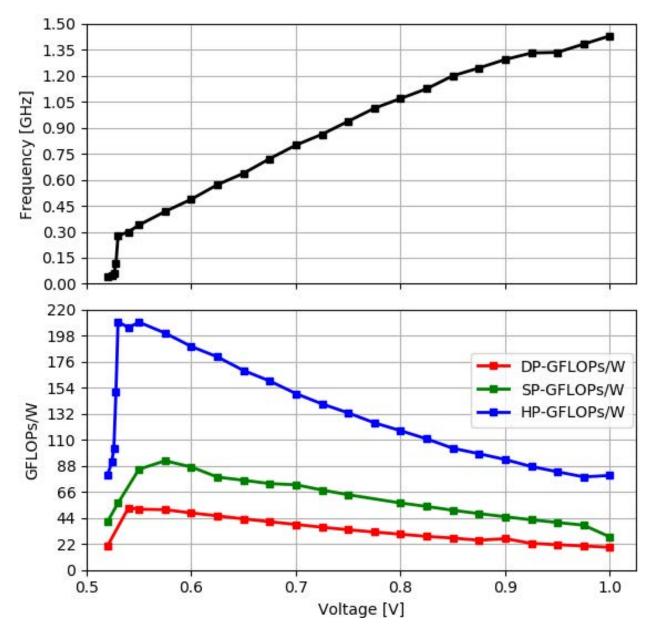

| 5.4          | Hurricane-1 frequency and efficiency at different operating voltages.                                                                                           | 57         |

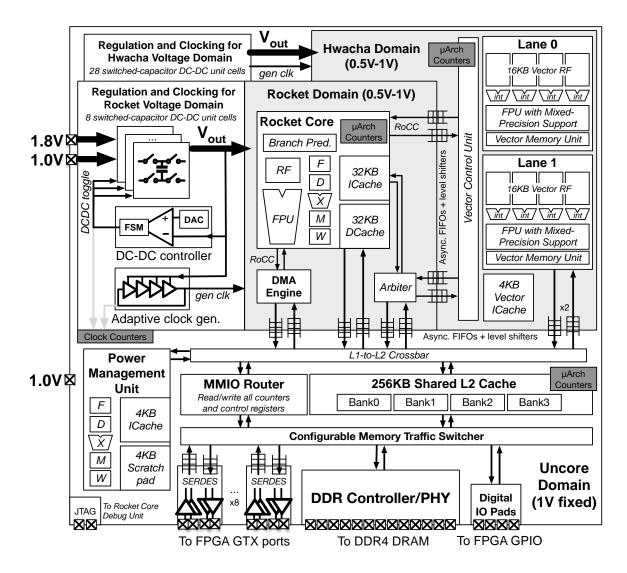

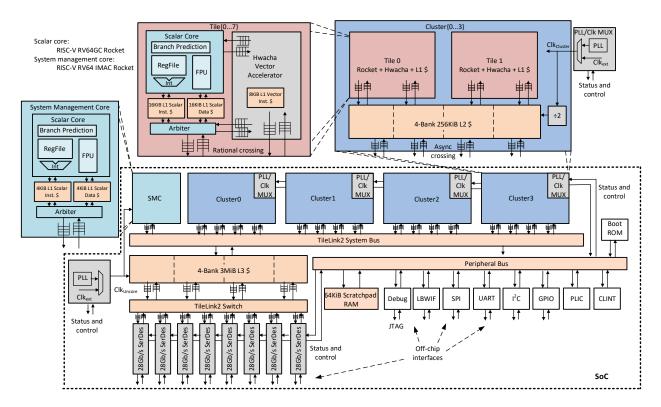

| 5.5          | An overview of the Hurricane-2 SoC and its components.                                                                                                          | 59         |

| 5.6          | An annotated diephoto of the Hurricane-2 SoC.                                                                                                                   | 61         |

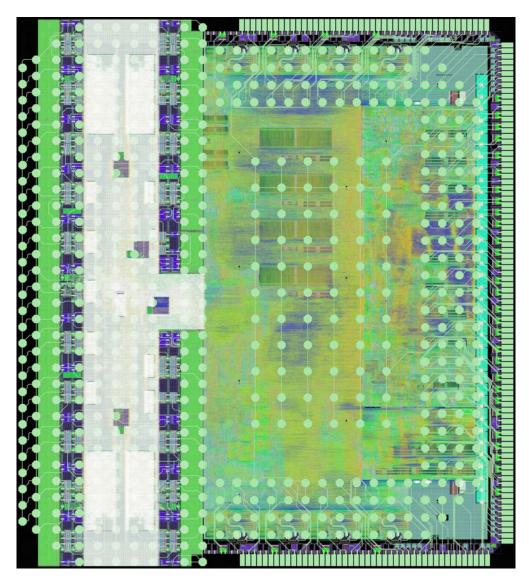

| 5.7          | A detailed GDS plot of the Hurricane-2 SoC                                                                                                                      | 63         |

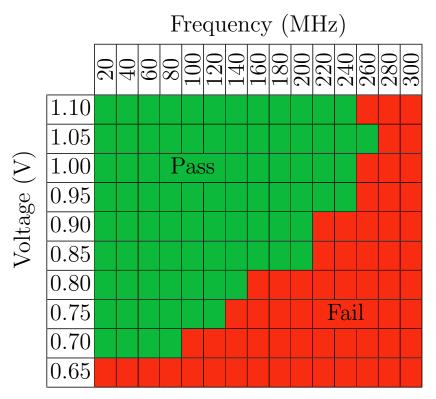

| $5.8 \\ 5.9$ | A shmoo plot showing valid Hurricane-2 voltage-frequency operating point<br>A comparison of DVFS algorithms on synthetic GEMM benchmarks on Hurricane-          | 64         |

|              | 2                                                                                                                                                               | 65         |

| 5.10         | 0                                                                                                                                                               | 67         |

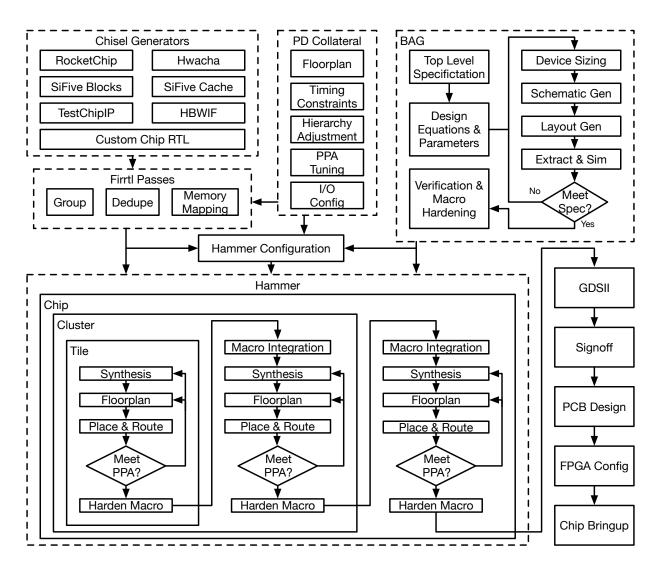

| 5.11         | The composition of Eagle's Generators. Dotted line boundaries correspond to                                                                                     |            |

|              | classes of generators.                                                                                                                                          | 69         |

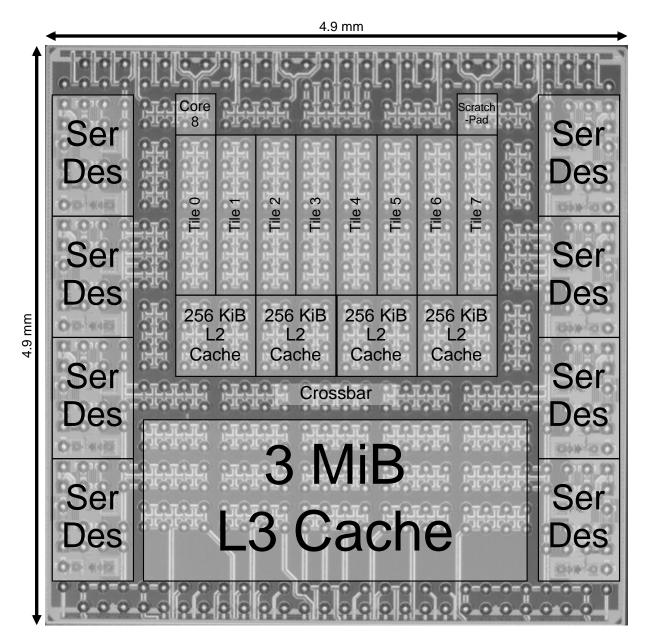

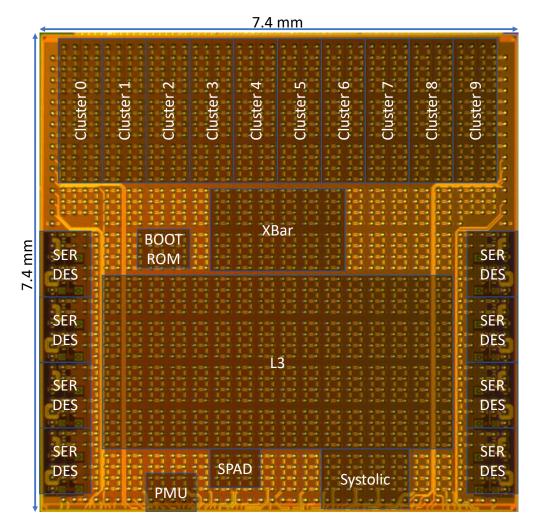

|              | An annotated diephoto of the Eagle SoC                                                                                                                          | 71         |

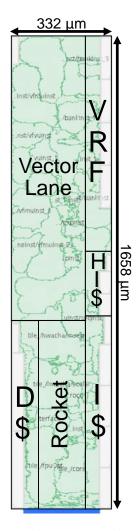

|              | Eagle annotated tile floorplan.                                                                                                                                 | 73         |

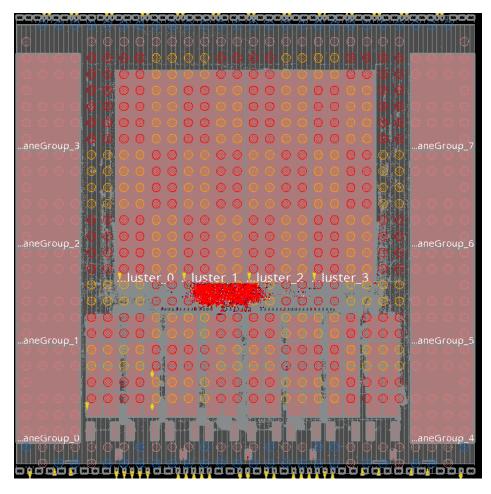

| 5.14         | An example of the congestion experienced in the initial eight-bank L3 Eagle design. The red and white are regions of over-congestion that will result in shorts |            |

|              | and other LVS failures                                                                                                                                          | 74         |

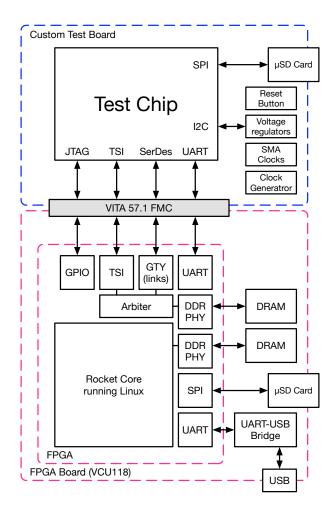

| 5.15         | A block diagram of Eagle's bring-up platform. The FPGA is at the bottom<br>surrounded by red and uses its fixed peripherals to aid in chip bring-up. A few      |            |

|              | small on-board components are next to the test chip outlined in blue                                                                                            | 76         |

| 5.16         |                                                                                                                                                                 |            |

| - 1 -        | precision general matrix multiplication.                                                                                                                        | 77         |

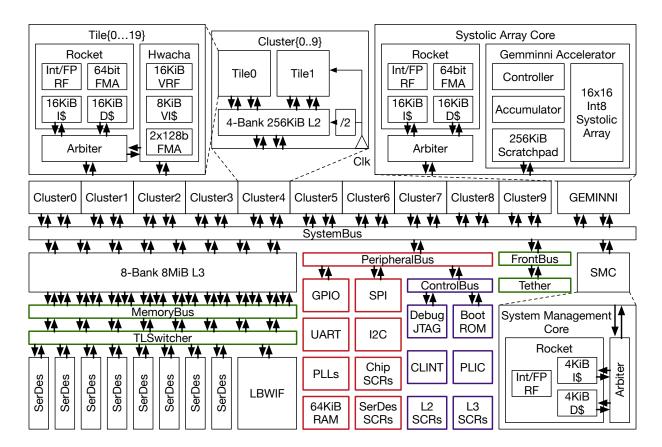

|              | EagleX blockdiagram.                                                                                                                                            | 79         |

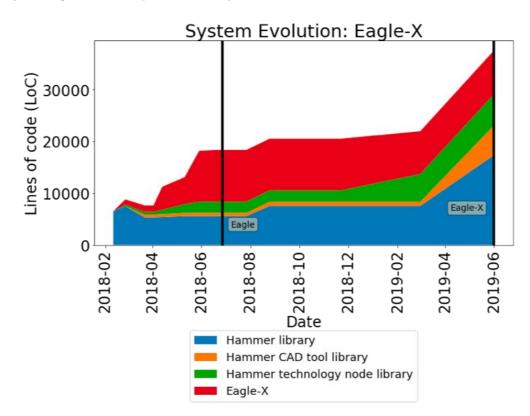

|              | The change over time of various portions of the Eagle/EagleX Hammer code base.                                                                                  | 80         |

|              | An annotated diephoto of EagleX SoC                                                                                                                             | 82         |

| 6.1          | The encoding of the VTMM worker-thread instruction.                                                                                                             | 86         |

| 6.2          | An example of the denser instruction stream made possible by the VTMM in-<br>struction.                                                                         | 87         |

| 6.3          | The encoding of the sub-matrix load worker-thread instruction.                                                                                                  | 87         |

| 6.4          | An example of the denser instruction stream made possible by the VLSM instruc-<br>tion.                                                                         | 88         |

| 6.5          | The encoding of the depth-only load worker-thread instruction.                                                                                                  | 00<br>89   |

| 6.6          | The encoding of the depth-only sub-matrix load worker-thread instruction                                                                                        | 89<br>89   |

| 0.0          | The choosing of the dependency sub-matrix four worker through histration,                                                                                       | 00         |

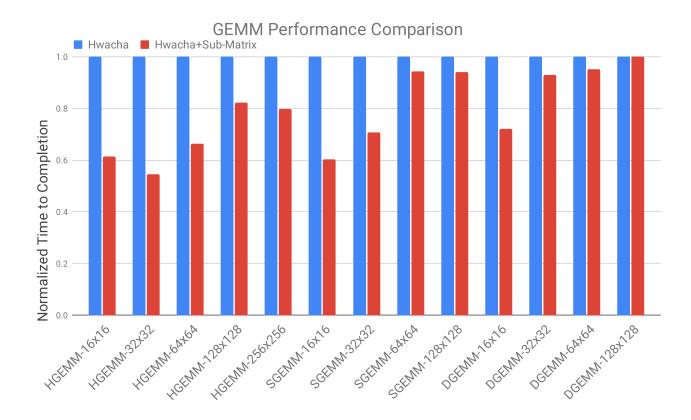

- 7.1 A comparison of the performance for various precision and matrix size GEMMs. 100

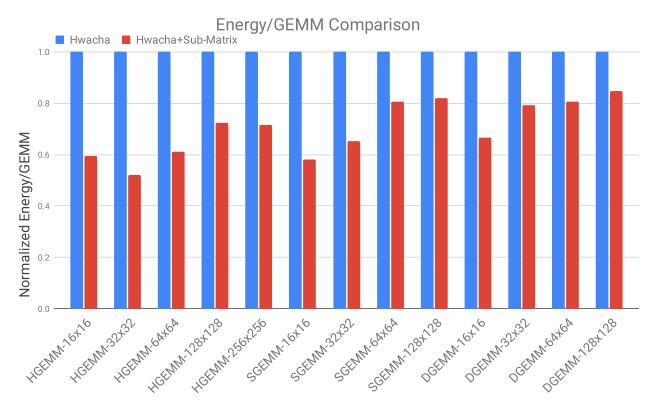

- 7.2 A comparison of the energy efficiency for various precision and matrix size GEMMs. 101  $\,$

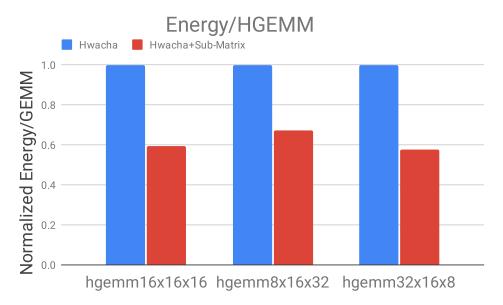

- 7.3 A comparison of the energy efficiency for various shapes of half-precision GEMMs.102  $\,$

### List of Tables

4.1 Comparison table of scaling for various register file implementation techniques. . 30

#### Acknowledgments

The work in this thesis would not have been possible without collaboration with many students, staff and faculty at U.C. Berkeley. I would like to thank everyone who contributed time, ideas, or support to me throughout this process.

First, and foremost, I would like to thank my advisor, Krste Asanovi, for his belief in me from the beginning to the end. His technical advice on vector architectures is second to none, and he provided me with expert guidance throughout my time at Berkeley. I'd also thank to thank Krste for giving me the freedom to explore so many different aspects of computer science, and his grand visions of projects that span the discipline. I would also thank to thank Bora Nikolic who, although not technically an advisor, played a crucial role in much of my work. In particular, his entrusting me with leading large chip projects, coaching me through copius chip paper submissions, and always encouraging me to find the thesis chapters in the work I was doing. Finally, I'd like to thank Robert Leachman as the final member of my thesis committee for his advice and support throughout this process.

I'd like to also specially thank Yunsup Lee and Ben Keller for being mentors to me in my Ph.D. work and in life. Yunsup brought me into the world of vectors, tapeouts, and making things work. Ben showed me how to build chips, manage a team, and do actual science. Without the guidance of both of them I would not be the researcher and individual I am today.

I've worked on several large projects during my time at Berkeley, each instrumental to my growth and an important part of the journey of my Ph.D. The Rocket-Chip generator was my first introduction to the team of amazing graduate students in the ASPIRE lab. All of the students I interacted with in the ASPIRE lab made it a welcoming, engaging, and exciting place to work, but some of the students I spent more time with deserve special mention. Andrew Waterman always provided excellent technical direction, personal guidance, and a friendly ear. Henry Cook helped me envision more expansive and radical projects, and show me what graduate student life could be. Scott Beamer demonstrated the power in writing papers, and that the path through Krste's group didn't always need to be microarchitecture. Chris Celio showed me that dedication to a single project can lead stellar results.

Simultaneously to the Rocket-Chip project, I began work on the fourth version of the Hwacha vector-fetch architecture and implementation. This project was lead by Yunsup but was truly a team effort with Albert Ou and myself, and led to a lot of the work during my Ph.D. The scope of this team project showed me that coming to Berkeley for the collaborative environment was an excellent decision. Getting to learn from Yunsup's in-depth knowledge of previous vector architectures and designs was priceless. Albert's detailed and methodical microarchitecting, and immense knowledge of unix systems and utilities always made me strive for better from my own designs and scripts.

The first pair of test-chips I contributed more than verification and testing to were Hurricane-1 and -2. The leadership of Ben Keller showed me the benefits of organization and I always strove to manage the Eagle chips half as well as Ben did the Hurricane chips. Palmer Dabbelt's never ending desire to write and re-write software to solve intensly complex problems directly led to the tool building work I did after the Hurricane project. Howard Mao always had an impressive desire to write RTL whenever the larger projects architected themselves into a corner, and was a huge help.

The Eagle and Eagle-X projects were my first foray into more of a leadership role and I couldn't have done it without all of the team members. Neither chip would have been possible without the tireless work of John Wright. We spent many late nights on calls together debugging chip, flow, and tool issues. John was an indispensible partner and I'm glad we were able to barely hold each others sanity together throughout both chips. Zhongkai Wang and Eric Chang were excellent partners on the analog side of the Eagle project. Sean Huang was helpful during and after the tapeout process, and continues to help with getting Eagle-X tested.

The Hammer project was critical to getting the Eagle project out the door successfully, and I hope the tool itself can live on at Berkeley and beyond. Edward Wang, the lead designer of Hammer showed excellent leadership and technical vision for the core principles of Hammer. John and I wouldn't have been able to contribute nearly as much physical design expertise without Edward's thorough and flexible design. Daniel Grubb, and Harrion Liew have admirably taken up the mantle of Hammer development and I'm excited to see them use it for future tapeouts and papers.

The latest project I've been involved with at Berkeley is Chipyard. Chipyard is designed to integrate all of the previous projects in an easy to use manner to make test-chips like Eagle and Eagle-X easier for those outside Berkeley to build, test, and verify. Obviously many students are involved in this project but I'd like to thank a few specially. I've worked with Jerry Zhao since he was an undergrad and he has shown nothing but dedication, intelligence and amazing execution throughout the many projects he has worked on. It has also been great to work with Abe Gonzalez, and see him learn to manage an entire tape out himself. David Biancolin has shown the consistency and commitment to his ambitious goals that has helped drive me to the finish line. Albert Magyar has always been a friend, a great discussion partner, and an excellent cube-mate. Sagar Karandikar's leadership of the Firesim project has shown me how to manage a wildly popular open-source project, and has always been generous with his time. I'd also like to thank the system administrators in both the ADEPT/ASPIRE lab, Kostadin Ilov, and the BWRC, Brian Richards, for dealing with all of my requests and keeping everything running smoothly even when I was working feverishly to overload them. The process of graduating with a Ph.D. is not a simple one but the administrative staff of the lab and the department have made it smooth and painless. Thank you to Roxana Infante, Tamille Chouteau, Ria Briggs, and Jean Nguyen for all their assistance in helping me reach the end of this journey.

I'd like to again thank all of my co-authors for the guidance and assistance in producing much of the work in this thesis. I'd also like to thank all of the funding sponsors of my research. Particularly the industrial sponsors of the ASPIRE lab, the ADEPT lab, and the BWRC. The fabrication of the Hurricane testchips was donated by STMicroelectronics. Portions of this research was supported by the DARPA PERFECT grant, HR0011-12-2-0016, the DARPA CRAFT grant, HR0011-16-C0052, and the Intel iSTC on Agile Design.

Graduate school has been a long journey for me and I would not have been able to succeed without the love and support of my friends and family. I've found many new friends on the west coast but I was lucky enough to bring one of my best all the way from Cornell. Adam Izraelevitz, has grown from an early lab partner to an amazing friend. I relish any opportunity to work together with him and deeply admire his thoughtful and caring response to any situation. I'm also grateful for all the other friendships I've made and continued during graduate school. They've helped me keep a balance between life and work even when all I can think about is research.

My entire family has always been extremely supportive of me and I know are waiting excitedly yet patiently for this work to be done. My parents have always been believed in me, and encouraged me endlessly to pursue my education. I think without the drive enstilled in me by them from a young age this journey would have been nearly impossible. Thank you so much for everything. My brother was the instigator of my entire computing career. By showing me his school projects he got me interested in programming, and the love and support he has shown me throught all of my schooling has been wonderful. I'd also like to thank my wife Sloka's family for their support and their ceaseless interest in understanding even the most complex portions of my work. Finally, I'd like to thank my wife Sloka. Our journey together to california wasn't planned in advance but it makes me feel like the luckiest man on earth every day. Thank you for dealing with the late nights working and writing, and for making sure I got the job done in the end. Thank you for all of your love and support.

# Chapter 1 Introduction

Computing has seen a rapid and fundamental shift in the past decade, away from single companies dictating the direction of the entire industry, and towards a more meritocratic space where ideas are easier than ever to prove out and the number of companies producing custom hardware has rapidly expanded. This is the result of many factors but the largest factors are likely the end of Dennard scaling in the mid 2000s, and more recently, a potential slowing of Moore's law. The cost of producing a new design in cutting edge nodes [61] and the reduced gains of moving to new nodes has encouraged a proliferation of designs on technology nodes several steps behind.

In addition to the underlying technology changes, the rise of open source hardware designs, in particular RISC-V, has led to a revitalization of explorative architectures. Designers now have the ability to build on top of existing hardware and software stacks, leveraging the work of large communities to make their designs more effective and usable. This time and cost savings allows for more focus on innovation rather than focus on catching up to the state of the art.

Lastly, the near-singular focus of modern applications on machine learning has enabled more specialized designs to proliferate. Deep learning is now being applied to nearly all applications in computing and requires orders of magnitude more computation than previous methods. Applications of deep learning are thus required to be highly concerned with performance, and as a consequence, energy efficiency. Designers then can direct their specialization at a relatively small problem, deep learning, and still see wide adoption across applications and also a strong need for their improvements in efficiency.

This chapter describes the recent trends that have lead to this shift, how computer architects have adapted, and the role programmable data-parallel architectures are playing in this transformation. This thesis provides a particular method, and example, of building programmable architectures designed to exploit these industry trends and future directions. Finally, section 1.3 outlines the contributions of this thesis, and the remaining chapters.

### 1.1 Energy Efficiency, Specialization, and Programmability

The slowing, and eventual end, of Dennard scaling means that energy efficiency is now the most important metric for a new design or architecture. In any power limited setting, mobile handset, desktop computer, server rack, the energy efficiency has become a proxy for performance. With a fixed power budget increased performance can only occur alongside an increase in performance per watt. And now all settings have become power limited, even supercomputers, as the cooling and power distribution problem for individual components continues to be a difficult problem to solve in the general case.

This change in focus for systems from pure performance to performance per watt has had a great impact on computer architecture. There must now be a continuing focus on getting every operation possible out of a given set of transistors. Specialization, where a design reduces the set of computations it supports, naturally eliminates large sets of operations that are no longer possible. The elimination of these other operations greatly improves the efficiency of the design as long as it is handling appropriate computations. A combination of distinct designs each focused separate types of computation can then compose into a system with higher overall energy efficiency.

As a consequence the number of specialized designs or hardware block in common products has proliferated dramatically in the last decade [78]. The integration of these diverse blocks can cause many problems that reduce the efficiency gains from adding additional blocks. Improving the interconnect between the blocks, or the mechanism by which data is shared between blocks, can alleviate some of these issues. However, a different approach, in which blocks are combined or new blocks are proposed that maintain some diversity in computational support via software, can also improve on efficiency of the system. In addition, these flexible designs also address the fundamental challenge of specialization, by enabling the applications supported to differ or change in ways that aren't known at design time.

As the advanced nodes have become more expensive and design cycles become longer the lack of flexibility has become a larger disadvantage for fixed-function accelerators. Applications continue to change faster as computers are integrated into ever more aspects of life. The rapid change in applications becomes critical to system design when the applications also demand a large amount of computation. In these cases, e.g. machine learning, a fixed function design's efficiency is needed but the rigidity would make designs obsolete soon after they are available. As a result, there has been a focus on programmable accelerators for those workloads that demand high computing power.

### 1.2 General-Purpose Data-Parallel Programmable Specialization

The primary work of this thesis is related to these programmable accelerators, their development, and implementation. The approach is essentially a middle-ground straddling the extreme demands for efficiency of modern applications, and the rapid development of new and unique applications which necessitates flexibility. These architectures should not be fully general or the benefits will be lost, so a common relatively large domain is computation on multi-dimensional data. This application domain covers not only deep learning, but also image and video processing, and scientific compute.

Many different implementations of such extensions exist by using various data-parallel architectural paradigms as their baselines. The work in this thesis utilizes the vector-fetch paradigm as its baseline rather than the more common paradigms recent commercial designs have been built with. The decoupled and runtime configurable nature of the vector-fetch architecture enables the desired specialization, for two primary reasons. First, the decoupling ensures that well written software is already built not to expect low latency communication with the data-parallel portions of the code. Expecting a larger latency enables more flexibility in performing longer running specialized tasks without hindering common software applications. Second, the runtime configuration of vector-fetch architectures ensures that programmers are already setting up the machine based on their current application. This setup code can then be reused or replaced to enable certain specialization features or other energy-efficiency improvements. Finally, a temporal microarchitecture for the vector-fetch paradigm can further enable specialization by giving the freedom to process the multiple dimensions of the data over time without significantly changing the normal control flow of the design.

### 1.3 Thesis Outline

The confluence of these factors leads to this thesis' central hypothesis, that a temporal vectorfetch microarchitecture would be an excellent candidate for multi-dimensional specialization on top of an existing programmable data-parallel architecture.

- Chapter 2 provides background on popular data-parallel architectures, comparing features and goals of each architecture. This includes representative code samples and a brief analysis of the architectures' programming models.

- Chapter 3 describes the history and current state of two-dimensional and some multidimensional architectures. A brief summary of multi-dimensional applications with a focus on machine learning is also provided.

- Chapter 4 presents the challenges associated with building data-parallel architectures in modern advanced technology nodes. An analysis of the constraints placed on such

architectures and techniques to mitigate or address these constraints is presented. The chapter also includes a description of the Hwacha architecture, microarchitecture, and the design decisions made during its implementation.

- Chapter 5 accounts several silicon test-chip implementations of the Hwacha architecture. The technologies and methodologies used to realize these implementations are presented. In addition, a description of physical design challenges for each chip and their solutions is included. Finally, a summary of results and measurements for each design is presented.

- Chapter 6 describes a two-dimensional extension to the Hwacha architecture, and how it would interact with the architecture's constraints. Also included is the encoding, operation, and a code sample for each of the new instructions. The chapter concludes with a brief discussion of possible future extensions and their design considerations.

- Chapter 7 presents the implementation of the two-dimensional extension for both the microarchitecture and the physical design aspects. A brief discussion of the previous potential future extension's implementation is also included. Finally, the chapter concludes with a presentation and analysis of the performance and energy-efficiency of different operations on the baseline and extended implementation.

- Chapter 8 concludes the work by summarizing the contributions of the thesis and providing a set of topics suitable for future exploration of two-dimensional programmable architectures.

### Chapter 2

### **Data-parallel Architectures**

A classical approach to improving performance in computer architecture is to focus on parallelism and attempt to do as much work as is reasonable at once. This exploitation of parallelism is often categorized into instruction-level parallelism (ILP), data-level parallelism (DLP), thread- or task-level parallelism (TLP) [38].

These types of available parallelism in computer programs has fostered many specific design paradigms, from ILP sparking very-long instruction-word (VLIW) and out-of-order execution (OoO) machines, to TLP spawning simultaneous multi-threading and many core processors, and DLP has proven no different. The primary data parallel design paradigms can be classified as fixed-width packed single-instruction multiple-data (SIMD), many-threaded single-instruction multiple-thread (SIMT), and variable-length vector. Nearly all computer systems manufactured today include some component designed for DLP. Even small deeply embedded processors often have small SIMD or digital-signal processing (DSP) units [100], small consumer devices like cell phones or tablets include SIMD units, graphics processing units (GPUs), and lately machine learning accelerators [3], server class processors have high performance SIMD implementations sometimes with on-chip GPUs [4], and high-performance compute clusters include even higher performance SIMD or vector units[99].

This chapter identifies characteristics common to each of these DLP paradigms, enabling a comparison and an understanding of the design-space. Sections 2.1, 2.2, and 2.3 describe the three primary paradigms from above, some of their implementation trade-offs, their primary use cases, and how they are intended to change over implementation iterations. The chapter continues by giving the same treatment to some of the newer and less common paradigms. Section 2.4 covers another newer paradigm, implementation-time variable-length vector packed-SIMD, which is exemplified by ARM's scalable vector extensions (SVE). Section 2.5 describes the latest data-parallel architecture the RISC-V vector extension and how it mixes some of the above paradigms. And finally, section 2.6 describes an additional more uncommon paradigm, vector-fetch, which is used by Hwacha the baseline architecture for the extensions described in the remaining chapters.

In order to discuss the differences in these architectural paradigms and how it affects their programming models a single example code will be compared across each of them. This frag-

```

void csaxpy(size_t n, bool c[], float a, float x[], float y[])

{

for (size_t i = 0; i < n; ++i)

if (c[i])

y[i] = a*x[i] + y[i];

}</pre>

```

Figure 2.1: CSAXPY as C code with a single vectorizable loop.

```

csaxpy_scalar:

stripmine_loop:

% Load c[i]

lb

t0, 0(a1)

% branch around work

t0, skip

beqz

% Load x[i]

lw

t1, 0(a3)

lw

t2, 0(a4)

% Load y[i]

t2, t1, a2, t2

% y[i] += a * x[i]

fma

t2, 0(a4)

% Store y[i]

s₩

skip:

a1, a1, 1

% update c pointer by 1 byte

add

% update x pointer by 4 bytes

a3, a3, 4

add

a4, a4, 4

% update y pointer by 4 bytes

add

% update remaining elements

a0, a0, 1

subi

bnez

a0, stripmine_loop % continue loop

ret

```

Figure 2.2: CSAXPY kernel mapped to a scalar architecture.

ment implements a simple linear algebra routine, and common benchmark CSAXPY, that multiplies a scalar a times a vector x, of length n, and sums that result with another vector y, this multiplication and summation are conditional on a third vector c. A non-vectorized implementation of this loop is presented in Figure 2.2, and all following implementations will follow the same calling convention. The number of elements n is passed in the first argument register a0, a pointer to the byte-packed condition vector c is passed in a1, the scalar value a is passed in a2, and the two vectors x and y are passed in a3 and a4 respectively. The scalar implementation is relatively straightforward, branching around the loads and math based on the condition, and unconditionally updating all the pointers and loop count.

There exist more optimized implementations of this loop using unrolling and or software pipelining but they would vary based on the specific implementation. One of the benefits of many of these data-parallel implementation strategies is that a relatively simple code can scale it's performance based on the underlying architecture, and so the codes presented below maintain this style of straightforward implementation. In addition, rather than using the assembly syntax of any particular architecture from the paradigms, and be forced to introduce new syntax for each code example, the code presented below is in a generic assembly syntax highlighting only the important distinctions.

### 2.1 Fixed-Width Packed-SIMD Architectures

This architectural paradigm is one of the earliest data-parallel architectures [24], and one of the most popular due to Intel's adoption of it for their data-parallel extensions. The core idea of this paradigm is to enable the user to reference subdivisions of a larger register, hence the packed moniker, in computations. This is a popular methodology because it initially allowed the use of registers that were already available and simply added parallelism to the handling of the register's bits. Over time, many implementations have added dedicated registers for this purpose as they grew in size past the natural word length of general purpose processors. Functional units such as multipliers scale quadratically with input bit-width while the number of subdivisions of a register only scales linearly so adding the required number of functional units to process an entire register's subdivisions at once can be smaller than the functional unit that uses all of the registers bits as a single input. These additional functional units allow for an increase in operations per cycle assuming the computation can make use of smaller, sub-register, data types. Additional instructions to handle these wider registers and common DLP operations are often added to make it easier to map high-level code to the architecture.

Figure 2.3 shows CSAXPY written for a fixed-width packed-SIMD architecture. Because the architecture has a fixed width of four words for each register, there is a fragment of code, elided above, at the end of the loop that would handle the remaining one, two, or three elements. This fixed width also shows up in the specific opcodes used, and in the register names. In addition, because the architecture does not support interaction between the scalar registers and the vector registers the user must explicitly replicate the scalar value into a vector register. Recently fixed-width SIMD architectures adopted full predication [27], and so are able to avoid some extra processing that has been unavoidable in the past.

In order to understand how a data parallel architecture will evolve over time it is useful to imagine how a current algorithm or code would need to be changed for new implementations. For example, what would happen if a new implementation were to be built with more or less processing power available. In the packed-SIMD approach if an implementation wants to perform more operations per cycle the instruction-set-architecture (ISA) will need to be extended to include a new set of opcodes for the wider registers and increased operations. This slow but constant increase in opcodes as a packed-SIMD architecture evolves creates several issues. Old binaries that are run on newer machines will not take advantage of the improved performance, and will need to be recompiled or potentially rewritten. Also because new opcodes continue being added they will tend to be longer in bit-width, the latest Intel extension AVX512 required an extra byte of prefix. This prefix EVEX is 4 bytes compared

```

csaxpy_simd:

slli

a0, a0, 2

% Scale number of elements to number of bytes

a0, a0, a3

% Calculate end address for loop body

add

vsplat4 v4w0, a2

% Fill a vector register with replicas of a

stripmine_loop:

vlb4

v4w1, (a1)

% Load the condition vector c[i:i+3]

vcmpez4 vp0, v4w1

% Fill a predicate register based on c

v4w1, (a3)

!vp0 vlw4

% Load x[i:i+3] under the c predicate

!vp0 vlw4

v4w2, (a4)

% Load y[i:i+3] under the c predicate

v4w1, v4w0, v4w1, v4w2 % y[i:i+3] += a * x[i:i+3] under the c predicate

!vp0 vfma4

!vp0 vsw4

% Store y[i:i+3] under the c predicate

v4w1, (a4)

addi

a1, a1, 4

% Increment c pointer by 4 elements

addi

a3, a3, 16

% Increment x pointer by 4 elements

a4, a4, 16

% Increment y pointer by 4 elements

addi

a3, a0, stripmine_loop

bleu

% handle edge cases

% when (n % 4) != 0 ...

ret

```

Figure 2.3: CSAXPY kernel mapped to the packed-SIMD assembly programming model.

to the shorter two and three byte VEX prefix used by AVX and AVX2. [45]. These prefixes encode operand and operation type but do not include the arguments so each instruction will be significantly longer.

Overall, the packed-SIMD paradigm is popular but has several downsides, some of which could be avoided if legacy codes could be left unsupported. The remaining paradigms all have mechanisms to avoid this central problem of directly encoding the width and number of elements in the architectures opcodes.

### 2.2 Many-Threaded SIMT Architectures

Another highly prevalent architecture is the many-threaded SIMT architecture implemented in some GPUs, including Nvidia's standalone GPUs, ARM's mobile GPUs, and AMD's integrated GPUs. This architecture was initially designed to enable per-pixel operation and so is focused on independent control of each thread. This design lends itself to an efficient and easy to scale physical design, given a large set of independent problems. The engines that handle threads will be replicated many times on a single chip and so the physical design of these units can be very detailed and well optimized, when compared to a more monolithic packed-SIMD engine that is only a portion of a general purpose processor. Physical design and scaling have often lead to SIMT architectures being one of the first designs on new

```

csaxpy_simt:

t0, tid

% Retrieve the current thread id

mv

% Branch around work for fringe elements

t0, a0, skip

bgeu

add

t1, a1, t0

% Setup c pointer

t1, (t1)

% Load c[tid]

lb

beqz

t1, skip

% Branch around work for masked elements

slli

t0, t0, 2

% Scale elements to bytes

add

a3, a3, t0

% Setup x pointer

add

a4, a4, t0

% Setup y pointer

% Load x[tid]

t1, (a3)

lw

% Load y[tid]

lw

t2, (a4)

fma

t0, a2, t1, t2

% y[tid] += a * x[tid]

SW

t0. (a4)

% Store y[tid]

skip:

stop

```

Figure 2.4: CSAXPY kernel mapped to the SIMT assembly programming model.

technology nodes and therefore one of the least-expensive options in terms of GFLOPS/W which is a component of total cost of ownership and therefore cost [73].

Figure 2.4 shows CSAXPY written for a SIMT architecture. The SIMT architecture relies on independent threads and a scheduler distributing these many threads to identical resources so the implementation looks similar to the scalar implementation. The largest differences are the lack of a loop, because the parallelism is implicit, and in the presence of a branch based on thread id to avoid executing any tail elements. One major drawback with this model is that the loads and stores are not expressed as vector loads in the code. Instead the microarchitecture is responsible for coalescing these individual loads and stores into more efficient operations for the memory system if the performance is to be recovered. In addition, the address calculations for these loads and stores is done in each thread and must be materialized into each thread's register file. This code example does not show the outer control processor code that would setup and launch this code onto the pool of SIMT execution units. This portion of code is highly variable per implementation and often includes privileged code, as the SIMT units are often exposed as devices. As with the edge case code for the packed-SIMD paradigm, the hiding of this code an optimistic view of the SIMT paradigm but focuses the comparison on the data-parallel portions of code.

The benefit of this many-threaded model is that with so many threads the microarchitecture is free to use each pipelines resources for any number of other threads if one becomes stalled on memory or another long latency operation. This does mean that in order to operate efficiently SIMT architectures often require large amounts of work to be schedule at once, as no individual thread is designed to be able to execute to completion without stalling.

This paradigm partially addresses the issue of direct bit-width encoding but the indepen-

```

csaxpy_tvec:

stripmine_loop:

% Set vector length for loop

vsetvl

t0, a0

vv0, (a1)

% Load vl elements from c

vlb

vcmpez

vp0, vv0

% Setup predicate for c[i:i+v1]==0

% Load y[i:i+vl] under c predicate

!vp0 vlw

vv0, (a3)

!vp0 vlw

vv1, (a4)

% Load x[i:i+v1] under c predicate

vv0, vv0, a2, vv1 % y[i:i+v1] += a * x[i:i+v1] under c predicate

!vp0 vfma

!vp0 vsw

vv0, (a4)

% Store y[i:i+v1] under c predicate

% Update c pointer by elements completed

a1, a1, t0

add

slli

t1, t0, 2

% Convert number of elements to bytes for x and y

add

a3, a3, t1

% Update y pointer by elements completed

% Update x pointer by elements completed

add

a4, a4, t1

a0, a0, t0

% Reduce remaining number of elements

sub

a0, stripmine_loop

bnez

ret

```

Figure 2.5: CSAXPY kernel mapped to the traditional vector assembly programming model.

dent nature of the threads still incurs some redundant processing and is unable to represent the uniform nature of DLP operations. The remaining paradigms are able to resolve both this representation issue and the direct encoding problem by using a programmatic number of elements to be processed.

### 2.3 Traditional Vector Architectures

Another type of data-parallel architectures that have been around for a long time are traditional long vector machines pioneered by Cray in supercomputers in the 1980s [74]. These architectures are characterized by run-time variable-length vectors, often taking multiple cycles for a single operation to complete, hence the long vector distinction. Currently these architectures are less common but do still show up in supercomputers [99] as at their origin. Eventually architectures like the IBM VF [16] added programmatic vector-lengths to this paradigm, which enables different physical implementations of the same ISA can run the same binary code. This enables a designer to produce many more design points along the performance spectrum without linearly increasing the amount of software needed for the designs. Longer vector architectures can also be more tolerant of memory system latency and have more freedom in their pipeline microarchitecture since the number of instructions need per application-level operation is greatly reduced.

Figure 2.5 shows the same CSAXPY kernel implemented on a hypothetical traditional vector architecture. Since this model allows for an explicit, but runtime varied, number of

elements to be processed at once it avoids several issues from the fixed-width packed-SIMD and SIMT designs. The initial setting of vector length vl sets the number of elements for the remainder of the loop. This setting can be an arbitrary value so the need for code to handle the tail of the vector is eliminated. In addition, because the vector length is explicit there is no need for extra management code or structures to figure out how many threads to launch as in the SIMT designs. The explicit parallelization also means that the memory operations explicitly encode the access patterns without needing something to recover and coalesce the accesses. Unlike the previous two paradigms there is no extra code needed for this function to run completely and correctly, which shows another benefit of this paradigm.

One issue with this model is that there are often a few extra instructions inside the loop to setup vector length, but this is offset by the lack of tail code. In addition, depending on the constraints of the specific ISA, the programmer may be able to assume a certain vector length is always available and for short application vectors avoid some of these extra instructions. Another issue is that modern compiler infrastructure is mostly used to dealing with fixed-width parallelization, or has special code for SIMT machines and uses the GPU runtime code to manage the variable amount of parallelism [64] [43]. And lastly without additional ISA features it can be difficult to fully utilize the register file particularly with small bit-width data types or mixed-precision computations.

This paradigm is able to avoid the fixed encoding, and redundant computation problems of the previous two models but still leaves room for improvement with regards to mixedprecision computations. A solution that solves all of these problems elegantly is not widely accepted and the final three paradigms discussed each take a different approach to work towards such a solution.

### 2.4 Implementation-time variable-length vector packed-SIMD Architecture

This paradigm introduces variable-length vectors that unlike the traditional vector architectures do not vary at runtime but vary at implementation time, and is embodied by the new ARM vector architecture SVE. Each implementation is allowed to have a different total number of bits in each vector register. The register size variance is quantized to 128 bits in order to restrict the ISA design and to make software easier to write, and has an upper limit in the architecture of 2048 bits. In order to provide the flexibility for arbitrary-length vectors the architecture provides predication and many specialized operations to set and update these predicate registers.

Figure 2.6 shows the CSAXPY kernel mapped to an implementation-time variable-length vector packed-SIMD architecture. The code shows the hybrid nature of the paradigm by needing to refer to subsets of vector registers with the .b and .w suffix, but not explicitly encoding the number of elements each iteration of the loop will process. The use of predicates as the means for programmatic vector length requires multiple named predicate registers and

```

csaxpy_sve:

t0, 0

% Initialize i

mov

whilelt vp0, x0, a0

% Initialize vl predicate for indexes < n

% Splat scalar into vector reg under vl predicate

!vp0 splat

v2.w, a2

stripmine_loop:

v0.b, (a1)

!vp0 vlb

% Load elements from c under vl predicate

vp1, v0.b

% Setup predicate for c[i:i+v1]==0 under v1 predicat

!vp0 vcmpez

!vp1 vlw

v0.w, (a3)

% Load vl elements from y under c predicate

!vp1 vlw

v0.w, (a4)

% Load vl elements from x under c predicate

v0.w, v0.w, v2.w, v1.w % y[i:i+v1] += a * x[i:i+v1] under c predicate

!vp1 vfma

% Store vl elements of y under c predicate

!vp1 vsw

v0.w, (a4)

% Update c pointer by elements completed

incvb

a1

% Update y pointer by elements completed

incvw

aЗ

% Update x pointer by elements completed

incvw

a4

t0

% Update remaining number of elements

incvw

% Update vector length predicate

whilelt vp0, t0, a0

bnempty vp0, stripmine_loop

% Continue loop if there are more elements

ret

```

Figure 2.6: CSAXPY kernel mapped to the implementation-time variable-length vector architecture.

a set of dedicated predicate generation instructions like *whilelt*. These predicate instructions are essentially substitutions for the *vsetvl* instructions of the traditional vector paradigm. Because the paradigm does not expose the number of elements explicitly in a scalar register, special increment instructions are included for different data widths, and branching must be based on the predicate register.

The primary benefit of this architecture is the ability to retain the sub-register SIMD programming model while enabling implementations to scale to different performance points. This scaling also enables more portable software that can maintain performance across implementations.

Unfortunately, there are still a few issues effectively using all the bits in these wide registers. When mixing different width data types extra instructions will often be needed to split the wider vector into multiple registers, and then align the narrower vector with more splits. In the code example above if the result were meant to be accumulated into a double-precision register the instruction count more than doubles for the inner loop.

This is evidence that despite approaching a better solution this paradigm still has potential for improvement. The last two architectures discussed move closer to the traditional vector style but with better support for mixed precision and sub-word parallelism.

```

csaxpy_rvv:

stripmine_loop:

vsetvl

t0, a0, e8,m1

% Set element to bytes

vlb

v1, (a1)

% Load vl elements from c

% Setup v0 as a mask for c

vcmpez

v0, v1

vsetvl

x0, a0, e32,m4

% Set element to words keeping SEW/LMUL constant

v1, (a3)

% Load y[i:i+v1] under c predicate

!v0 vlw

!v0 vlw

v2, (a4)

% Load x[i:i+v1] under c predicate

% y[i:i+vl] += a*x[i:i+vl] under c predicate

!v0 vfma

v1, v1, a2, v2

v1, (a4)

% Store y[i:i+v1] under c predicate

!v0 vsw

add

a1, a1, t0

% Update c pointer by elements completed

% Convert number of elements to bytes for x and y

t1, t0, 2

slli

a3, a3, t1

% Update y pointer by elements completed

add

a4, a4, t1

% Update x pointer by elements completed

add

a0, a0, t0

% Reduce remaining number of elements

sub

a0, stripmine_loop

bnez

ret

```

Figure 2.7: CSAXPY kernel mapped to the RISC-V vector extension programming model.

### 2.5 **RISC-V** Vector Architecture

The RISC-V vector extension (RVV) has a new architectural model that is similar to traditional vectors with some elements of the fixed width packed-SIMD architectural paradigm. This discussion is based on the 1.0 version of the specification which has changed dramatically from the early versions, over the few years of specification history.

The general programming model is still one of explicit runtime configurable vector length. However, rather than the location of these elements being opaque to the programmer the location of the bits are made explicit, as with the previously discussed architectures. This allows for using the same registers as different bit-width values without clearing the machines configuration. The vector unit is still configured before operation, but it is lightweight and does not cause any register state to change. The main components of the configuration are the current element width (SEW), and the vector length multiplier (LMUL), which determines the number of physical registers present in a register group. Rather than encoding the width of elements explicitly in the instruction opcode as in all previous architectures, encoding space is saved by using the ahead of time configuration (SEW) to specify the element bitwidth for most operations. There are many exceptions to this rule especially with respect to memory operations, but most arithmetic operations do not explicitly encode the bit-width of operations. Some arithmetic operations consume or produce elements of a twice as wide or twice as narrow bit-width relative to the current element width, which along with changing the current element width allow for relatively efficient mixed precision code. Figure 2.7 shows the CSAXPY kernel mapped to the RISC-V vector extension. The noticeable differences in this sequence are the additional *vsetvl* instructions needed before operations on different data widths, and the use of a regular vector register *v*0 as the predicate. The extra configuration instructions allow for the computation instructions to be encoded without an explicit data type. The vector length multiplier allows for wider data types to use more architectural registers while maintaining mixed-precision computation by matching the ratio of multiplier to element width.

The primary benefit of this architecture over the previous designs is that it enables more complete use of the vector register file with the vector length multiplier, without using additional instruction bandwidth. This architecture still allows for programmatic vector length changes and predication for more complex control flow, maintaining most of the benefits of the previous architectures. Considering the code change from above where the accumulator is now double precision, the addition of widening operations means that only a single instruction needs to be added to the loop.

One downside of this architecture is that the data layout for the vector register file is exposed which puts some limits on the microarchitecture. This is a clear trade-off to allow the kinds of sub-register SIMD along with mixed-precision operation in a small amount of encoding space. In addition, the programmer's model of execution is more complex than the original three paradigms due to the mixing of explicit and implicit element widths and potential non-obvious configuration constraints.

Overall, the RISC-V vector extension design provides a very attractive architecture for general purpose data-parallel execution. It provides good code efficiency, expressive primitives, and allows for many differently performant implementations. The last data-parallel architecture to discuss provides similar features but makes some concessions on code size to provide more room to experiment with new architecture ideas, and is thus the basis for the work in the later chapters.

#### 2.6 Vector-Fetch Architecture

The vector-fetch architectural paradigm [56] is a non-standard scheme that moves the traditional vector instructions out of the scalar control thread and into separate blocks, unlike all of the previous paradigms discussed. The goal of this change is to more effectively decouple the vector operations from the scalar operations. This decoupling allows the scalar core to run ahead calculating addresses and loading scalar data and resolving control flow that will be needed for future iterations of the vector execution loop. One crucial idea that allows the decoupling to occur is that several of the setup instructions including the *vsetvl* instruction exist in the scalar control stream and the vector unit can calculate the available vector length regardless of the code block that will be sent later.

In the vector-fetch paradigm, the control thread is responsible for setting up the vector unit by configuring its registers (vsetcfg), moving scalar data and addresses into the vector register file (vmcs, vmca), setting the vector length (vsetvl), and launching the worker

```

csaxpy_hwacha:

vsetcfg t0

% Set up vector register for number and precision

vmcs vs1, a2

% Move the scalar a to vector unit

stripmine_loop:

% Set vector length for loop

vsetvl t0, a0

vmca va2, a1

% Move &x to vector unit

vmca va0, a3

% Move &y to vector unit

% Move &c to vector unit

vmca va1, a4

% Launch vector-fetch block

vf

csaxpy_vf

% Update number of elements completed

a1, a1, t0

add

% Convert number of elements to bytes for x and y

t1, t0, 2

slli

add

a3, a3, t1

% Update x pointer

add

a4, a4, t1

% Update y pointer

% Update number of remaining elements

a0, a0, t0

sub

a0, stripmine_loop % Continue if needed

bnez

ret

csaxpy_vf:

vpset vp0

% Initalize predicate register

vlb vv2, (va2)

% Load c[i:i+1]

% Setup predicate for c[i:i+v1]==0

vcmpez vp0, vv2

\% Load vl elements from y under c predicate

!vp0 vlw vv0, (va0)

% Load vl elements from x under c predicate

!vp0 vlw vv1, (va1)

!vp0 vfma vv0, vv0, vs1, vv1

% y[i:i+vl] += a * x[i:i+vl] under c predicate

!vp0 vsw vv1, (va1)

% Store vl elements of y under c predicate

vstop

```

Figure 2.8: CSAXPY kernel mapped to the vector-fetch programming model.

thread's code block (vf). The worker thread contains the memory, compute, and predicate operations. These worker thread instructions are fetched from memory, decoded, and then executed in an independent unit.

Figure 2.8 shows the same CSAXPY kernel implemented on the vector-fetch architecture. It contains two sets of instructions: one set for the control thread, and a second set for the vector worker thread. The control thread instructions are similar to a traditional vector architecture with the addition of the scalar and address data moves, and the vector-fetch launch. The worker thread instructions are also very similar but with a *vstop* instruction at the end to denote the end of the worker thread. After the stop, the vector unit is idle until another vector-fetch block is issued and could be clock-gated or potentially power-gated.

This paradigm also supports the same binary to have extended vector lengths on new im-

plementations, and additionally supports configuring the number and data-widths of vector registers This vector register configuration allows for efficient use of the register file as well as straightforward mixed-precision computation. Changing the summation array to doubleprecision does not increase the number of instructions in the loop at all, as the configuration instruction is the only one that changes.

The obvious downsides of this model are the increased code size, and the required moves for scalar data used in the vector unit. In addition, the separate stream of vector execution will increase the latency for short vector sequences more commonly used in non data-parallel code.

However, the vector-fetch architectures separation of the vector unit and loose encoding allow for easy experimentation with new architectural or microarchitectural ideas. In addition, an open-source implementation of the entire vector-fetch design significantly reduces the overhead of establishing a baseline architecture for further experiments. Overall, the vector-fetch architecture provides an excellent platform to propose and evaluate more data-parallel extensions.

### Chapter 3

# Multi-Dimensional Vector Applications and Architectures

The definition of DLP does not restrict the parallelism to single dimensional operations and is often used for dense linear algebra where the dimensionality of data can be very high. Fortunately, all these high-dimension operations can be decomposed into one dimensional vector operations or even scalar operations, and so can be computed on even the simplest of hardware. The downside to this decomposition is an inherent loss of context. When these computations are broken down into their elements and run individually on a piece of hardware the pattern that is expressed by the higher-level operations is lost. The hardware no longer be aware that it is processing rows of a matrix or slices of a tensor. These patterns, when exploited, can provide efficiency and performance improvements in myriad ways, from not materializing intermediate results to generating fewer memory requests. This lure of efficiency and performance has fostered many research projects, products, and architectures to move the data-level parallelism abstractions above simple one dimensional operations.

This chapter describes the fundamental components of some popular multi-dimensional applications, how these applications can be mapped to hardware, and what types of hardware has been designed for these applications. Section 3.1 discusses some of the original array-based SIMD designs that often included a 2D interconnect, but were widely varied in the programming models and supported operands. Section 3.2 describes the linear algebra routines that eventually standardized what operations data-parallel architectures were expected to provide and perform well on and are the basis of most multi-dimensional compute. Section 3.3 discusses the core set of operators that have been used to build most of the prevalent machine learning architectures, and how these relate to the linear algebra routines.

With these applications in mind and the knowledge that they continue to demand more computing resources year after year, much time has been spent developing custom architectures or additional functional units in existing architectures that can accelerate these applications. Section 3.4 concludes the chapter by discussing the different extensions that have been explored and how they impact the architecture and programming model.

### 3.1 Origins of Two-Dimensional Architectures

Single-instruction multiple-data architectures and two-dimensional architectures have a long shared history. An early branch of designs was taking advantage of the physical world to lay out physically distributed components in a grid or array. These architectures had their physical structure built into their programming model with nearest-neighbor connections, and the applications envisioned for them. This specialization also extended to the processing elements (PEs) initially with bit-serial implementations being very popular as it allowed applications to map more efficiently to the array regardless of its bit-width. As with many designs constructed during the early decades of computing compatibility between different designs was non-existent, but eventually standard word-length processing elements became popular, presaging large networked computers as in data-centers and supercomputers. As with many computing designs increasing levels of device integration leads to more PEs being packed into each package and the 2D grid was replicated in on chip connections. These machines paved the way for both the modern fixed function processing arrays, the more general purpose 2D architecture extensions, and even reconfigurable gate arrays, and processing in memory.

An early 2D machine, the Illiac-IV, was designed to tackle many of the applications mentioned at the start of this chapter, linear algebra, scientific computing and signal processing [12]. At the time explicit parallelism was rare, but the designers recognized it would help increase the computing power of the machine such that their large target applications would be tractable. Having been designed before large scale on-chip integration was possible the physical structure of the machine matches the logical structure, a homogeneous grid of processing elements with connections to its neighbors. This introduced several ideas that eventually became common for SIMD architectures. The Illiac-IV is capable of using predicates based on elements as control flow. The addressing scheme is also based on a local PE register, making its addressing computations similar to those of SIMT machines. However, it avoids some of the redundant storage and computation of the SIMT paradigm with a constant broadcast bus that each PE can use directly, which is more similar to the traditional vector designs. Finally, there is was lot of focus on decoupling the control unit for the PEs which is similar to the vector-fetch paradigm. All of these one-dimensional data-parallel concepts are augmented by the 2D interconnect between PEs. These direct connections enable more complex algorithms such as matrix inversion to proceed directly on the PE without higher level coordination [57]. However the 2D organization is mostly used to speed up long routing as most algorithms use the memory as the 2D structure holding an array but spread columns among the PEs in a more linear fashion.

Other early machines experimented with the connectivity of the array and the bit-width of the PEs, to improve utilization. The Distributed Array Processor (DAP), reduces the bit-width of each PE to a single bit, and adds several other features to address low utilization scenarios [72]. The limits that apply to array processors are still present in today's architectures and include: non-uniform memory access for non-local storage; small problem sizes underutilizing the array; idle time during setup due to I/O, configuration, or loading; and edge cases in computation due to reductions or boundary conditions leaving most of the array idle. The bit-serial approach of the DAP aims to help problem size array matching. The lower cost of a bit-serial PE enables more memory to be attached to each PE, allowing for fewer slow non-local accesses, and more problems to fit entirely in the system removing the need for reconfiguration. An additional neighbor connection, half way across a row and column, increases the speed of data transfer among the PEs. Because not all data movement in 2D applications is regular, Amdahl's Law warns that if these irregular movements take a very long time they can still dominate array performance. The DAP's organization is also programmable enabling different organizations of PEs to be changed during execution. These optimizations show the architecture striving to increase efficiency by reducing the idle periods of the array, which will continue to be an issue for future 2D or array processors.

Another bit-serial approach but more in line with modern array processors and the Illiac-IV is the Massively Parallel Processor (MPP), which makes only a few modifications besides once again scaling up the peak processing power [13]. MPP returns to 4-way nearest neighbor connectivity, but maintains the programmable topology from the DAP. Of interest for future 2D machines is a global reduction tree that reduces the underutilization involved in a reduction computed directly on the array. There is also more attention paid to loading data into the array and it can mostly proceed in parallel with the processing, an important aspect of all data-parallel workloads especially those operating on large portions of data like 2D grids.

Another unique approach to a 2D processor that was targeted more directly towards artificial intelligence tasks was the Connection Machine [39]. The connection machine is again bit serial at each PE, with 4 nearest neighbor connections, and an or-reduction tree. The most important change from an architecture perspective is the great increase in dimensionality of the non-direct connections. The CM-1 prototype connection machine has a 12-dimensional network between the processing elements. This network takes a variable number of cycles to traverse but enables much higher overall bandwidth compared to the simple two dimensional network of the nearest neighbor connections. Managing connectivity between elements in a data-parallel architecture is a balancing act between the expense of the network which scales with the machines parallelism and the expressiveness provided by the additional connections. The connection machine pushed this expressiveness considerably further than previous bitserial machines.

Unfortunately, all of these early designs suffer from difficult programming models where they needed to invent a whole new set of abstractions to provide programmers with something usable for general software development. The MasPar MP-1 moves towards a more usable and common set of interfaces while maintaining the massively parallel SIMD architecture [15]. It adopts a RISC-like instruction set for the PEs with standard data types but still with an instruction broadcast mechanism such that it operates similar to the SIMT paradigm. The PEs also have registers that are accessible by sub-words, bits, bytes, half words, words, and double words, in a similar manner to future packed-SIMD architectures. It is explicitly designed to support high-level languages like C and be more easily programmable, a trend that continues with future array processors. The MP-1 also adds indexed loads and stores to enable mapping more applications efficiently, such as indirection or lookup tables. The architecture is designed to be scalable as well, such that each set of PEs added also adds memory and communication bandwidth keeping the machine balanced. Although this doesn't go as far as ensuring old binaries can run on scaled up architectures it is still progress towards the performance portability that DLP architectures strive for. Finally, the MP-1 increases the neighbor connections to 8-way and more importantly adds an all-to-all network for the PEs that although slower than the neighbor communication still greatly reduces the average distance of nodes.

As VLSI integration increases in the mid 1990s these SIMD array processors begin to divide into two groups, microprocessors where an entire, often 1D, SIMD processor fits onto a single chip [5], and smaller processors in large networked configurations [83]. We see both of these trends emerge in the MasPar MP-1 because it has both sub-word SIMD registers just as in Intel MMX from 1996 [70], and each PE is a RISC-like processor with a three hop global network between them. Both of these groups of highly parallel architectures begin to adapt their programming models towards more standard software and targeting from high level languages, which is aided by the previous decade's creation and study of the basic linear algebra subprograms (BLAS) as discussed in the next section.

### 3.2 Multi-dimensional Applications and Libraries

While these SIMD array processors were being developed, built, and used for a wide variety of applications, one of these application domains at the base of much multi-dimensional compute, linear algebra, was being standardized with high-level software APIs. The initial set of proposed basic linear algebra subprograms (BLAS) included only single dimensional operations [62], but still provided an API for higher level software to conform to and hardware to implement efficiently. Over the next decade higher dimensional BLAS routines were developed until level-3 BLAS in 1990 [28]. Shortly after this, a specific set of BLAS functions were combined into a benchmark suite LINPACK which is now used to identify the highest performing computers on the TOP 500 list [29]. This standard set of subprograms is often provided by vendor specific extremely well tuned software packages such as MKL for Intel CPUs and CuBLAS for Nvidia GPUs.

Many different application domains have come to rely on these routines and the software is often built on top of BLAS APIs. A large consumer of the TOP500 compute is scientific computing focused on aiding scientists by modeling or simulating real world physical systems. These models can be so large that they will only fit or be computationally tractable on supercomputers, and are mostly responsible for driving the development of supercomputers. As mentioned before supercomputers have focused on DLP from the beginning with SIMD, vectors, and SIMT architectures making up nearly all of the TOP500.

Other smaller applications more appropriate for a workstation also rely on multi-dimensional compute. Computer-aided design tools, image and video processing and rendering, and engineering simulations all make use of highly parallel often multi-dimensional compute [84] [20].