# Design for Performance and Reliability in Advanced CMOS Structures

Fei Ding

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2020-41 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2020/EECS-2020-41.html

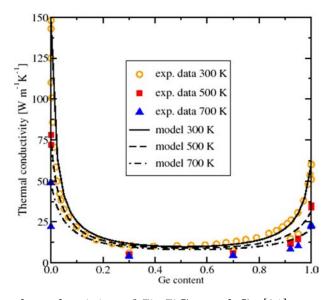

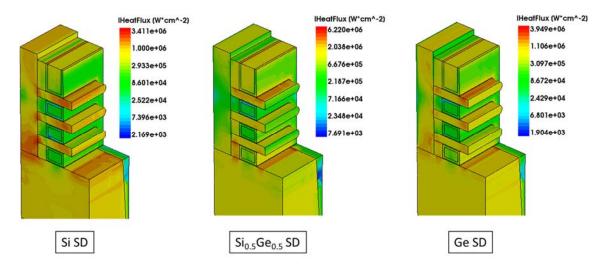

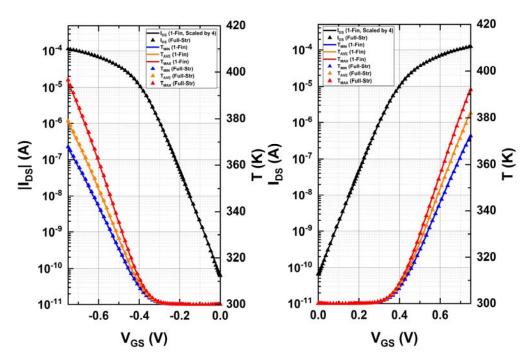

May 5, 2020

Copyright © 2020, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

by

Fei Ding

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Tsu-Jae King Liu, Chair Professor Junqiao Wu Professor Ming Wu

Spring 2020

## Design for Performance and Reliability in Advanced CMOS Structures

Copyright 2020

by

Fei Ding

#### Abstract

Design for Performance and Reliability in Advanced CMOS Structures

by

Fei Ding

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Tsu-Jae King Liu, Chair

In the past few decades, the central theme of the electronics industry is to increase the transistor density by reducing the transistor area, as required by the Moore's Law. The paradigm shift from the planar CMOS technology to the FinFET technology sustains this area scaling trend into sub-20nm era. The enhancement in the transistor electrostatics in the FinFET enables further scaling of the gate length and hence the contacted poly pitch (CPP). Meanwhile, the quest for area scaling also comes from the width (or fin pitch) and height dimensions. By reducing the fin pitch and increasing the fin height, the current density of the FinFET can be improved. Consequently, circuit designers can use fewer fins to meet the same current requirement and save area simultaneously, a scheme commonly referred to as "fin-depopulation." However, the aforementioned approaches start to show diminishing returns and meet excessive fabrication challenges. To further improve the current density and reduce the area, novel channel materials with high mobility (e.g., SiGe) and/or new structures with even better electrostatics (e.g., Inserted-oxide FinFET (iFinFET), Gate-All-Around FET, Nanosheet FET) are projected to be used in the future.

In the first part of the talk, the performance of a p-channel FinFET comprising a heterogeneous silicon (Si) and silicon-germanium (Si<sub>0.9</sub>Ge<sub>0.1</sub>) channel region is evaluated using 3-D TCAD simulations. It is shown that the heterochannel design provides for larger current density while maintaining comparable electrostatic integrity as the conventional Si FinFET design due to the valence band (VB) offset between SiGe and Si.

Secondly, a scheme for controllably adjusting transistor drive strength in iFinFET technology is proposed, to enable cell ratio tuning for a minimally sized

six-transistor SRAM (6-T Static Random Access Memory) cell. It is demonstrated, via 3-D TCAD simulation, that this scheme can reduce the minimum cell operating voltage ( $V_{\min}$ ) and facilitate further cell area scaling.

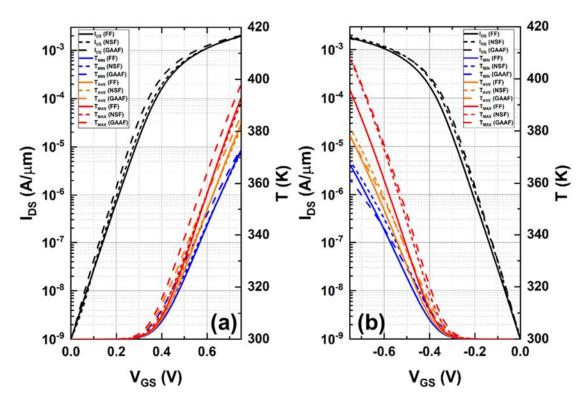

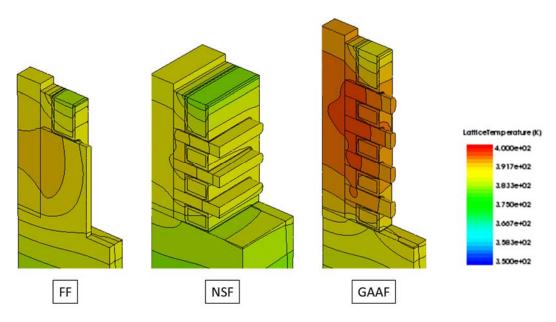

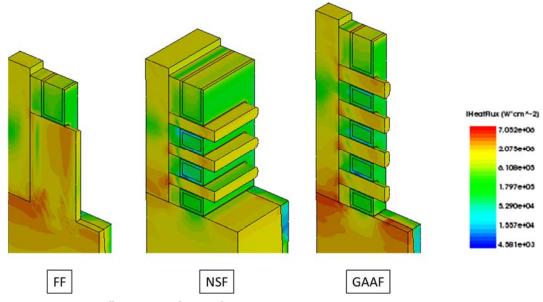

Lastly, as the transistor area continues to shrink, self-heating effects of these small-geometry transistors have been of great concern as it limits the electrical performance and degrades the reliability of transistors. It is important to understand how self-heating may be for these new transistor structures as compared to FinFETs. The performance of advanced transistor structures (i.e., FinFET, Gate-All-Around FET, and Nanosheet FET) is simulated and compared under the constraints of the self-heating. An optimization guideline for nanosheet FETs is also proposed based on the study of various design parameters on the self-heating effects.

# To my family

for their ceaseless support along the journey.

# Contents

| 1 | Introduction1                                                                                                                    |                                                                    |    |  |  |

|---|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----|--|--|

|   | 1.1                                                                                                                              | IC Chip Area Scaling – The Central Theme                           | 1  |  |  |

|   | 1.2                                                                                                                              | Transistor Design Techniques to Facilitate Further Area Scaling    | 6  |  |  |

|   | 1.3                                                                                                                              | Research Objectives and Thesis Overview                            | 9  |  |  |

|   | 1.4                                                                                                                              | References                                                         | 10 |  |  |

| 2 | Si/Si <sub>1-x</sub> Ge <sub>x</sub> /Si Hetero-Channel FinFET for Enhanced P-Channel<br>Performance in Low-Power Applications14 |                                                                    |    |  |  |

|   | 2.1                                                                                                                              | Introduction                                                       | 14 |  |  |

|   | 2.2                                                                                                                              | Hetero-Channel (Si/Si <sub>0.9</sub> Ge <sub>0.1</sub> /Si) FinFET | 15 |  |  |

|   | 2.3                                                                                                                              | Hetero-Channel FinFETs with Varying Ge Molefraction                | 22 |  |  |

|   | 2.4                                                                                                                              | Conclusion                                                         | 24 |  |  |

|   | 2.5                                                                                                                              | Appendix: Process Simulation in Sentaurus Process                  | 25 |  |  |

|   | 2.6                                                                                                                              | References                                                         | 26 |  |  |

| 3 | Cell Ratio Tuning for High-Density SRAM Voltage Scaling with Inserted-Oxide FinFETs (iFinFETs)30                                 |                                                                    |    |  |  |

|   | 3.1                                                                                                                              | Introduction                                                       | 30 |  |  |

|   | 3.2                                                                                                                              | Inserted-Oxide FinFET (iFinFET)                                    | 31 |  |  |

|   | 3.3                                                                                                                              | 6-T SRAM High Density Cell Design                                  | 34 |  |  |

|   | 3.4                                                                                                                              | High Density Cell Ratio Tuning Using Doped-Nanowire iFinFET        | 41 |  |  |

|   | 3.5                                                                                                                              | Conclusion                                                         | 54 |  |  |

|   | 3.6                                                                                                                              | Appendix: Doped-Nanowire iFinFET Fabrication Process Issues        | 54 |  |  |

|   | 3.7                                                                                                                              | References                                                         | 58 |  |  |

| 4 |                                                                                                                                  | omparison of Self-Heating Effects in Different Transistor ctures   | 63 |  |  |

|   | 4.1                                                                                                                              | Introduction                                                       | 63 |  |  |

|   | 4.2                                                                                                                              | Simulation Methodology                                             | 64 |  |  |

|   | 4.3                                                                                                                              | Results and Discussion                                             | 67 |  |  |

|   | 4.4          | Optimization of P-Channel NSF                                                  | 78  |

|---|--------------|--------------------------------------------------------------------------------|-----|

|   | 4.5          | Conclusion                                                                     | 94  |

|   | 4.6<br>Simul | Appendix: Validity of Using a 1-Fin FF/GAAF with AreaFactor late 4-Fin FF/GAAF |     |

|   | 4.7          | References                                                                     | 98  |

| 5 | Conc         | clusion                                                                        | 101 |

|   | 5.1          | Summary and Contributions of This Work                                         | 101 |

|   | 5.2          | Future Directions                                                              | 104 |

|   | 5.3          | References                                                                     | 105 |

#### Acknowledgements

During the past four and a half years as a Ph.D. student, I am very fortunate to meet and work with a group of outstanding people. As I am concluding the entire course of my graduate study with this dissertation, I would like to use this opportunity to thank all the people that have helped me along the journey. Without them, this dissertation would not have been possible.

First and foremost, I am extremely grateful to my thesis advisor, Prof. Tsu-Jae King Liu, for her excellent mentorship and guidance throughout my graduate study. Her broad and deep knowledge in semiconductor device technology can always point us to the right direction when it comes to solving a difficult research problem. In addition, her enthusiasm in this field has always motivated us to explore new opportunities and take on new challenges. Outside research, she is also a role model for us. Her elegance, kind personality, and efficient use of time have always set an example for us to follow.

Secondly, I want to thank Prof. Ming Wu and Prof. Junqiao Wu for sitting on my dissertation committee, and Prof. Borivoje Nikolic for serving as a member of my qualifying exam committee. Their feedback and guidance during the qualifying exam was invaluable. And I also appreciate Prof. Muhammad M. Hussein's kindness for giving me the opportunity to TA the graduate solid-state devices course (EE230B).

All the research topics in this dissertation are a direct result of collaborations with many research partners. The invaluable discussions with Yi-Ting Wu are instrumental for me in understanding modern MOSFET concepts. These concepts are fundamental to all of my research topics presented in this dissertation. I am very grateful for his patience and clarity in explaining difficult technical details. The doped if in FET SRAM project would not have come to fruition without Dr. Daniel Connelly and Dr. Peng Zheng. Their expertise in electronics has helped me clear many technical hurdles. I appreciate Prof. Hiu-Yung Wong's guidance and support on the self-heating project. I would also like to thank Prof. Nattapol Damrongplasit and Dr. Nuo Xu for their research guidance in the last two years of my undergraduate study. Members from Atomera Inc., especially Hideki Takeuchi, Dr. Robert Mears, also have offered constructive feedback in my research. In addition, I appreciate the help from the staff members (Joanna Bettinger, Dr. Allison Dove, Richelieu Hemphill, Ryan Rivers, and Dr. William Flounders) from Marvell Nanolab at UC Berkeley during my short stay there working on transistor fabrication.

I also want to thank all other current and graduated members in Prof. Liu's group, in particular, Dr. Sergio Almeida, Hoonsung Choi, Tsegereda Esatu, Xiaoer Hu, Prof. Sangwan Kim, Chanmin Lee, Benjamin Osoba, Dr. Chuang Qian, Dr. Thomas Rembert, Dr. Kimihiko Sato, Urmita Sikder, Lars Tatum, Alice Ye, and Dr. Xi Zhang, for many interesting discussions in research and life topics. In addition, I would also like to thank many current and previous "sitting" members of Cory 373: Qiutong Jin, Yafei Li, Dr. Ruonan Liu, Dr. Jalal Nilchi, Dr. Alper Ozgurluk, Kieran Peleaux, Qianyi Xie. They have made Cory 373 a wonderful workplace.

In addition to the above, I have also received much help from the administrative staff in the EECS department. In particular, I would like to thank Shirley Salanio, Charlotte Jones, and Nicole Song for their support in handling administrative matters.

Finally, I would like to sincerely express my gratitude to my family. The Ph. D. experience would not have been complete without confusion, frustration, and self-doubt from time to time. It is their ceaseless support that has emboldened me to live through many dark moments during these years. Thank you!

# Chapter 1

## Introduction

## 1.1 IC Chip Area Scaling – The Central Theme

#### 1.1.1 Moore's Law and Dennard's Scaling Law

In 1965, Gordon Moore observed that the number of transistors on the most advanced integrated circuit "chip" roughly doubled every year; this trend eventually became known as Moore's law [1]. In practice, this is almost equivalent to steady doubling of transistor density because the area of a chip cannot be increased much due to manufacturing cost considerations [2]. Therefore, Moore's law implicitly requires the transistor area to be roughly halved with each new generation ("node") of manufacturing process technology. In 1974, Robert Dennard and his colleagues proposed the constant-field scaling rule, which serves as a set of guidelines for scaling metal oxide semiconductor field-effect transistors (MOSFETs) [3]. In this rule, also known as the Dennard's scaling law, various transistor design parameters are scaled according to a factor  $(\alpha)$  so that the peak electric field within the transistor is kept relatively constant across technology generations.

|                                                               | Constant Field Scaling |

|---------------------------------------------------------------|------------------------|

| Physical dimensions: $L_{gate}$ , $W$ , $T_{ox}$ , wire pitch | 1/α                    |

| Body doping concentration                                     | α                      |

| Voltage                                                       | 1/α                    |

| Circuit density                                               | $1/\alpha^2$           |

| Capacitance per circuit                                       | 1/α                    |

| Circuit speed                                                 | α                      |

| Circuit power                                                 | $1/\alpha^2$           |

| Power density                                                 | 1                      |

| Power-delay product                                           | $1/\alpha^2$           |

Table 1.1-1. Dennard scaling law for transistors. Adapted from [4].

As shown in Table 1.1-1, following the constant field scaling approach, circuit performance is increased at a rate of  $\alpha$  as we scale the transistor area by  $1/\alpha^2$ .

However, the industry stopped following the Dennard's scaling law around 2005 because of practical limits and non-ideal effects that become significant as the transistor lateral dimensions are scaled down. For example, Dennard's scaling law requires the body doping concentration to be increased by the scaling factor,  $\alpha$ . But as the doping concentration increases, impurity-induced carrier scattering increases and degrades carrier mobility and hence transistor on-state current. In addition, the scaling of physical gate length also started to meet fabrication challenges. More importantly, gate length scaling is limited by short-channel effects (SCE) in conventional planar MOSFET structures. Poor SCE also limit reductions in the supply voltage. To mitigate SCE at sub-30nm gate lengths, FinFETs were introduced.

# 1.1.2 Challenges for Area Scaling in the FinFET Era and Beyond (Post-Dennard Scaling)

The FinFET has been the transistor design of choice in the semiconductor industry since Intel's 22nm technology node [5] and other foundry's 16/14nm technology node [6] thanks to its superior electrostatic integrity as compared to the planar MOSFET. However, FinFETs are much more difficult to fabricate, which results in increasing wafer cost.

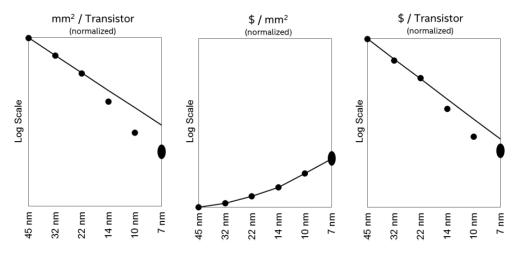

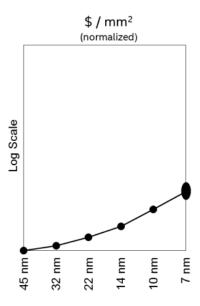

Figure 1.1-1. Fabrication cost increases at a fast pace in small technology nodes. Adapted from [7].

Figure 1.1-1 illustrates the trend of increasing cost per area due to more complicated fabrication process. From a business standpoint, in order to justify the need for a smaller technology node, the transistor area must be aggressively scaled (shown on the left) so that the effective cost per transistor is reduced. However, scaling the transistor area in FinFET-era becomes even more challenging.

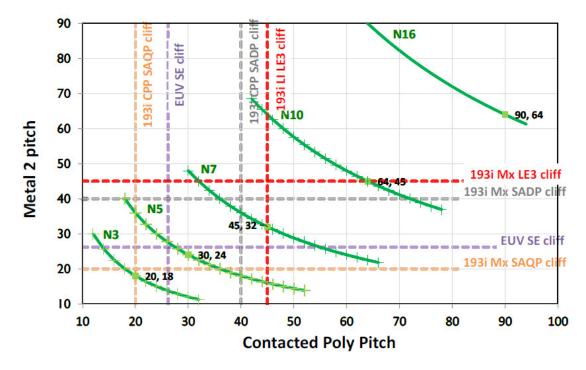

Scaling the area in the length direction requires reduction of the contacted (gate electrode) poly-Si pitch (CPP). Generally speaking, the CPP is defined via photo lithography. In order to reduce CPP, more complicated patterning processes are required, as shown in Figure 1.1-2.

Figure 1.1-2. Limits (cliffs) of different patterning techniques. Adapted from [8]. Note that Metal 2 Pitch (MMP) is directly related to Fin Pitch via gear ratio. Gear ratio is usually 4:3 (=MMP:FP).

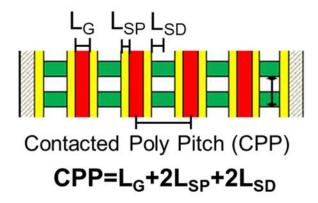

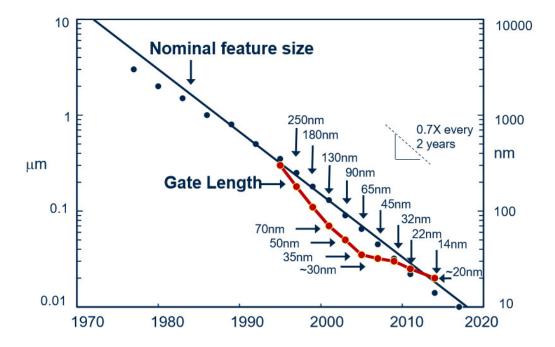

More specifically, CPP has 3 components (Figure 1.1-3).  $L_G$  is the physical gate length,  $L_{SP}$  is the length of sidewall spacer, and  $L_{SD}$  is the length of source/drain. As shown in Figure 1.1-4, physical gate scaling has almost stalled in recent generations. On the other hand, reducing gate-sidewall spacer length ( $L_{SP}$ ) can lead to increase in the gate-to-drain capacitance and may result in transistor reliability issues. In addition, reducing the source/drain length ( $L_{SD}$ ) can reduce the effectiveness of source/drain stressor, which degrades transistor on-state

current and hence circuit performance. There are also process complications when  $L_{\rm SD}$  is reduced.

Figure 1.1-3. Definition of CPP. Adapted from [9] with modifications.

Figure 1.1-4. Physical gate length scaling. Adapted from [10]. Data points are taken from various presentations from Intel Corp..

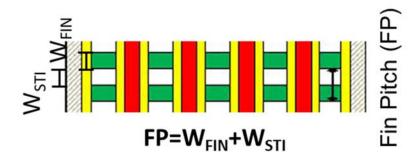

Scaling in the width direction requires reducing the fin pitch (FP). FP consists of two parts (Figure 1.1-5).  $W_{FIN}$  is the fin width and  $W_{STI}$  is the width of STI region. Fin width is already sub-10nm and there is not too much room for further reduction. An extremely thin (narrow) fin could lead to performance degradation due to non-idealities like excessive surface carrier-scattering effects. On the other hand, reducing  $W_{STI}$  could potentially meet fabrication challenges

due to the need for conformal deposition of oxide to fill trenches with higher aspect ratio.

Figure 1.1-5. Definition of FP. Adapted from [9] with modifications.

Table 1.1-2 summarizes the important process parameter values for 3 generations of FinFETs from Intel Corp. [5, 11, 12, 13].

|                       | 22nm [5] | 14nm [11]  | 10nm [12, 13]       |

|-----------------------|----------|------------|---------------------|

| CPP (nm)              | 90       | 70 (0.78X) | 54 (0.77X)          |

| FP (nm)               | 60       | 42 (0.7X)  | 34 (0.81X)          |

| W <sub>FIN</sub> (nm) | ~8       | ~8         | ~7                  |

| H <sub>FIN</sub> (nm) | 34       | 42 (1.24X) | 46-53 (1.10X-1.25X) |

Table 1.1-2. Summary of process parameters in 3 generations of FinFETs from Intel Corp. The number in parentheses is the scaling factor compared to the last generation. For 10nm technology node, a 46nm  $H_{FIN}$  was stated in [12] and a 53nm  $H_{FIN}$  was found in [13].

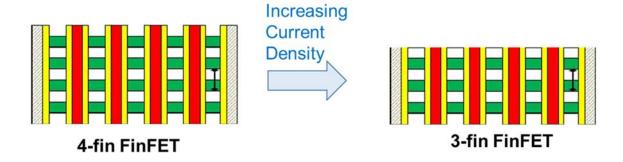

### 1.1.3 Fin-Depopulation for Further Area Scaling

Recognizing the aforementioned challenges of conventional area scaling, the industry has moved to the third dimension (i.e., out of the plane of the silicon wafer surface). In FinFETs, the height of the fin is (almost) directly proportional to the transistor's conductive strength. By increasing the fin height, the current density per layout area can be increased. To meet the same current specification as set by the circuit designers, a smaller number of taller fins is sufficient. As a result, the total layout width can be reduced without significantly adding process complexity. This approach is commonly referred to as "fin depopulation," as

shown in Figure 1.1-6. But the fin height cannot be increased without limitation due to added process complexity and increased parasitic resistance between the metal contacts at the top of the fins in the source/drain regions to the bottom of the fin. To continue to improve the current density, new transistor structures or novel high-mobility channel material are necessary.

Figure 1.1-6. Fin depopulation. Adapted from [9] with modifications.

# 1.2 Transistor Design Techniques to Facilitate Further Area Scaling

#### 1.2.1 Advanced Transistor Structures

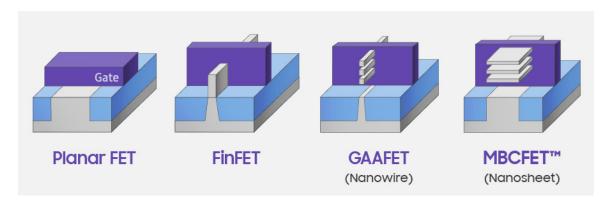

Figure 1.2-1. Advanced transistor structures. Adapted from [14].

Due to excessive short channel effects, conventional bulk Si planar FETs cannot sustain further gate length scaling. Therefore, advanced transistor structures are required. These transistor structures can suppress the short channel effects through better gate control over the channel (Figure 1.2-1).

FinFETs (more specifically, bulk silicon FinFETs) were first introduced in mass production at Intel's 22nm technology node [5]. The rest of the industry then followed. FinFETs are multi-gate transistors in which the gate electrodes cover three sides (left, right, and top) of the fin channel region. This results in better gate control than in planar FETs. In addition, since FinFETs are a variant of thin-body transistors, they feature narrow fins to provide for physical confinement of carriers in the channel region. A smaller fin width is generally preferred for better electrostatic integrity. But FinFET performance might be degraded if the fin is too narrow due to the loss of inversion carrier density and excessive surface roughness scattering [15]. On the other hand, the effective channel width of a FinFET is directly proportional to the outer perimeter of the exposed fin. In high aspect ratio FinFETs, the gate on the top side contributes less so that they are essentially double-gate MOSFET structures.

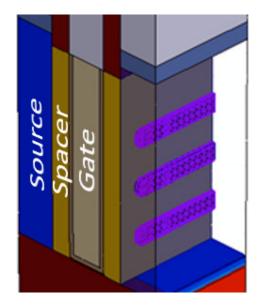

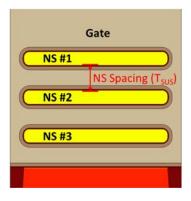

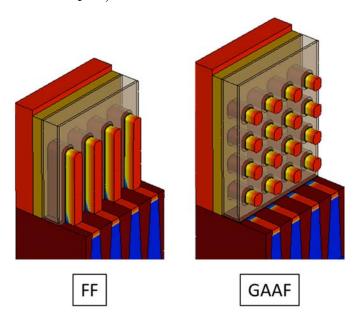

As mentioned in Section 1.1.3, to facilitate further scaling to sub-5nm technology nodes, novel transistor structures (e.g., Gate-All-Around FET (GAAFET) and Nanosheet FET (NSFET)) are generally expected to be adopted. These advanced structures are expected to achieve even better electrostatic integrity than FinFET.

GAAFETs have gates covering all 4 sides of the nanowire/channel region, which provide for superior electrostatic integrity. Due to the small geometry of the nanowires, in order to meet the drive current requirement, multiple ( $\geq 3$ ) nanowires must be used. In practice, GAAFETs generally require a large spacing between adjacent nanowires to accommodate the gate stack. Therefore, the aspect ratio of the entire channel stack is much higher than that of the fin in FinFETs, posing potential fabrication challenges. In addition, due to more exposure between the gate and source/drain regions, the parasitic gate-to-drain capacitance [16] is much larger compared to FinFETs.

To address the issues of GAAFETs, NSFETs (also called Multi-Bridge Channel FETs (MBCFETs)) have been proposed. In NSFETs, the gate still covers all 4 sides of the nanosheet/channel. However, since the NSFETs are usually wide, the left and right gates do not contribute much; hence, the electrostatic integrity of NSFETs is between that of FinFETs and GAAFETs. NSFETs can achieve better layout efficiency than FinFETs by eliminating the STI regions between adjacent fins. More importantly, the channel (sheet) width of the NSFETs can be lithographically defined, as opposed to the spacer-defined

width in the case of FinFETs and GAAFETs. This gives more flexibility to circuit designers for adjusting transistor drive strength.

Other evolutionary FinFET structures also have been proposed. For example, the inserted-oxide FinFET (iFinFET) [16] can achieve better electrostatic integrity than the FinFET without adding too much parasitic capacitance. The details of iFinFETs are discussed in **chapter 3**.

### 1.2.2 High Mobility Channel Materials

The advanced structures described in Section 1.2.1 help with transistor area scaling by mitigating the short channel effects for small gate lengths. In this section, another possibility is discussed: achieving higher current density using high mobility channel materials to enable scaling in the width direction through fin depopulation.

| Materials              | $ m Electron~Mobility \ (cm^2/Vs)$ | $egin{array}{l} 	ext{Hole Mobility} \ (	ext{cm}^2/	ext{Vs}) \end{array}$ |

|------------------------|------------------------------------|--------------------------------------------------------------------------|

| Si                     | 1400                               | 470                                                                      |

| Ge                     | 3900                               | 1900                                                                     |

| GaAs                   | 8500                               | 400                                                                      |

| InAs                   | 40000                              | 500                                                                      |

| $In_{0.53}Ga_{0.47}As$ | 12000                              | 300                                                                      |

Table 1.2-1. Summary of electron and hole mobility in conventional high mobility channel materials (bulk).

For n-channel transistors, most III-V alloys such as GaAs, InAs, and InGaAs can achieve very high electron mobility (Table 1.2-1). However, from a process integration perspective, these III-V channels are hardly practical at this point. Due to the large lattice mismatch between the Si and most III-V materials, a thick epitaxial stress relax buffer (SRB) is generally required to gradually reduce the mismatch [17]. Recent advancement in the aspect ratio trapping (ART) technique [18] could facilitate the integration of these exotic materials into a standard CMOS manufacturing process.

The desire for high hole mobility materials is much stronger due to the fact that the embedded SiGe source/drain stressor becomes less effective as we scale

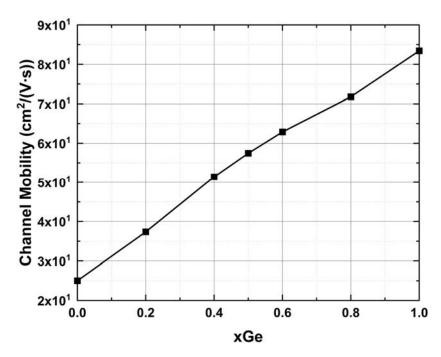

down the volume of these stressors with transistor miniaturization. SiGe alloys and Ge are usually considered the most promising candidates due to their compatibility with a Si-based CMOS manufacturing process. Ge fins can be fabricated on the Si substrate using ART [19], but the Ge fin sidewalls might still suffer from surface passivation problems. On the other hand, low Ge molefraction SiGe becomes attractive as a channel material in p-channel FinFETs due to smaller lattice mismatch with the Si substrate. Even though alloy scattering effects in SiGe cannot be ignored, the combined stress from the Si substrate (or strain-relaxed SiGe buffer layer) and the source/drain regions makes low Ge molefraction SiGe achieve higher hole mobility and hence higher performance than the strained Si [20, 21].

## 1.3 Research Objectives and Thesis Overview

This dissertation addresses challenges for continued transistor area scaling as follows.

In **chapter 2**, a hetero-channel FinFET design comprising  $Si/Si_{1-x}Ge_x/Si$  is evaluated and benchmarked against conventional Si FinFET and  $Si_{1-x}Ge_x$  FinFET. In particular, x (i.e., Ge molefraction) is chosen to be small so that  $Si_{1-x}Ge_x$  can be directly fabricated on top of a conventional silicon wafer substrate via epitaxial growth.

In **chapter 3**, a cell ratio tuning scheme for iFinFET 6-T SRAM high density cell (HDC) design is proposed. Specifically, the top nanowire(s) can be selectively doped via ion implantation to precisely reduce the transistor drive strength and hence fine tune the bit cell ratio. The feasibility of this approach is validated via a process simulator, Sentaurus Process [22]. The transistor performance and impact of process variations are simulated using a 3-D TCAD software, Sentaurus Device [22]. Finally, the yield of 6-T SRAM is estimated via an in-house developed software [23].

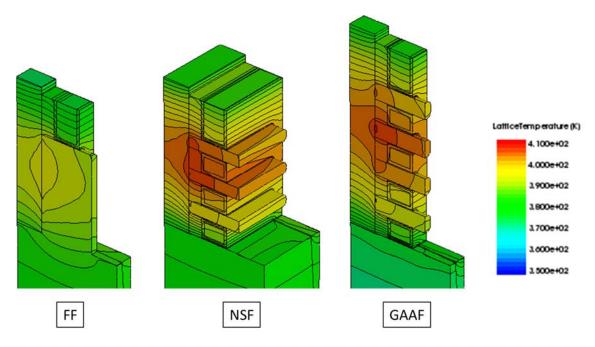

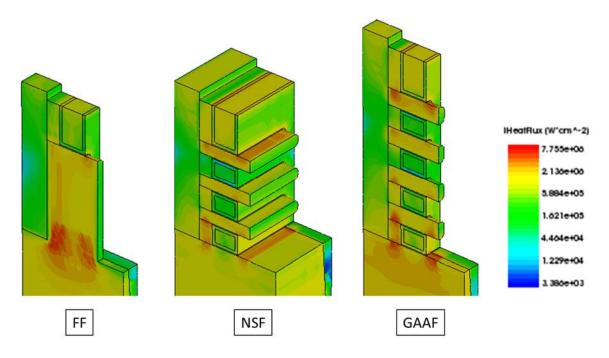

In the first half of **chapter 4**, a comparison of advanced transistor structures with regard to self-heating effects (SHE) is presented. In particular, the performance of FinFETs (FFs), Nanosheet FETs (NSFs), and Nanowire Gate-All-Around FETs (GAAFs) are benchmarked under the constraint of identical peak temperature. To ensure a fair comparison, the design parameters are set for FFs and GAAFs so that their on-state current are similar to that of NSFs. The

difference in SHEs for n-channel vs. p-channel transistors is investigated. In addition, the influence of various transistor design parameters on SHE is also investigated. In the end, the operating voltages of NSFs and GAAFs are lowered so that they have the same maximum temperature as that in FFs. Under this scenario, the performance of FFs, NSFs, and GAAFs are compared. In the second half of **chapter 4**, various design parameters are optimized in order to minimize SHE in NSFs.

### 1.4 References

- [1] G. E. Moore, "Cramming more components onto integrated circuits, Reprinted from Electronics, volume 38, number 8, April 19, 1965, pp.114 ff.," in IEEE Solid-State Circuits Society Newsletter, vol. 11, no. 3, pp. 33-35, Sept. 2006. doi: 10.1109/N-SSC.2006.4785860.

- [2] M. Bohr, "A 30 Year Retrospective on Dennard's MOSFET Scaling Paper," in IEEE Solid-State Circuits Society Newsletter, vol. 12, no. 1, pp. 11-13, Winter 2007. doi: 10.1109/N-SSC.2007.4785534.

- [3] R. H. Dennard, F. H. Gaensslen, Hwa-Nien Yu, V. L. Rideout, E. Bassous and A. R. Leblanc, "Design Of Ion-implanted MOSFET's with Very Small Physical Dimensions," in Proceedings of the IEEE, vol. 87, no. 4, pp. 668-678, April 1999. doi: 10.1109/JPROC.1999.752522.

- [4] W. Haensch, E. J. Nowak, R. H. Dennard, P. M. Solomon, A. Bryant, O. H. Dokumaci, A. Kumar, X. Wang, J. B. Johnson and M. V. Fischetti, "Silicon CMOS devices beyond scaling," in IBM Journal of Research and Development, vol. 50, no. 4.5, pp. 339-361, July 2006. doi: 10.1147/rd.504.0339.

- [5] C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, M. Buehler, V. Chikarmane, T. Ghani, T. Glassman, R. Grover, W. Han, D. Hanken, M. Hattendorf, P. Hentges, R. Heussner, J. Hicks, D. Ingerly, P. Jain, S. Jaloviar, R. James, D. Jones, J. Jopling, S. Joshi, C. Kenyon, H. Liu, R. McFadden, B. McIntyre, J. Neirynck, C. Parker, L. Pipes, I. Post, S. Pradhan, M. Prince, S. Ramey, T. Reynolds, J. Roesler, J. Sandford, J. Seiple, P. Smith, C. Thomas, D. Towner, T. Troeger, C. Weber, P. Yashar, K. Zawadzki and K. Mistry, "A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM

- capacitors," 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, 2012, pp. 131-132. doi: 10.1109/VLSIT.2012.6242496S.

- [6] S. Y. Wu, C. Y. Lin, M. C. Chiang, J. J. Liaw, J. Y. Cheng, S. H. Yang, S. Z. Chang, M. Liang, T. Miyashita, C. H. Tsai, C. H. Chang, V. S. Chang, Y. K. Wu, J. H. Chen, H. F. Chen, S. Y. Chang, K. H. Pan, R. F. Tsui, C. H. Yao, K. C. Ting, T. Yamamoto, H. T. Huang, T. L. Lee, C. H. Lee, W. Chang, H. M. Lee, C. C. Chen, T. Chang, R. Chen, Y. H. Chiu, M. H. Tsai, S. M. Jang, K. S. Chen and Y. Ku, "An enhanced 16nm CMOS technology featuring 2nd generation FinFET transistors and advanced Cu/low-k interconnect for low power and high performance applications," 2014 IEEE International Electron Devices Meeting, San Francisco, CA, 2014, pp. 3.1.1-3.1.4. doi: 10.1109/IEDM.2014.7046970.

- [7] M. T. Bohr, "Logic Technology Scaling to Continue Moore's Law," 2018 IEEE 2nd Electron Devices Technology and Manufacturing Conference (EDTM), Kobe, 2018, pp. 1-3. doi: 10.1109/EDTM.2018.8421433.

- [8] J. Ryckaert, P. Raghavan, P. Schuddinck, H. B. Trong, A. Mallik, S. S. Sakhare, B. Chava, Y. Sherazi, P. Leray, A. Mercha, J. Bömmels, G. R. McIntyre, K. G. Ronse, A. Thean, Z. Tökei, A. Steegen and D. Verkest, "DTCO at N7 and beyond: patterning and electrical compromises and opportunities," Proc. SPIE 9427, Design-Process-Technology Co-optimization for Manufacturability IX, 94270C (18 March 2015). doi: 10.1117/12.2178997.

- [9] S. K. Marella, A. R. Trivedi, S. Mukhopadhyay and S. S. Sapatnekar, "Optimization of FinFET-based circuits using a dual gate pitch technique," 2015 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, 2015, pp. 758-763. doi: 10.1109/ICCAD.2015.7372646.

- [10] B. Nikolic. (2019). Advanced Digital Integrated Circuits: Lecture 1 Intro [Powerpoint Slides].

- [11] S. Natarajan, M. Agostinelli, S. Akbar, M. Bost, A. Bowonder, V. Chikarmane, S. Chouksey, A. Dasgupta, K. Fischer, Q. Fu, T. Ghani, M. Giles, S. Govindaraju, R. Grover, W. Han, D. Hanken, E. Haralson, M. Haran, M. Heckscher, R. Heussner, P. Jain, R. James, R. Jhaveri, I. Jin, H. Kam, E. Karl, C. Kenyon, M. Liu, Y. Luo, R. Mehandru, S. Morarka, L. Neiberg, P. Packan, A. Paliwal, C. Parker, P. Patel, R. Patel, C. Pelto, L. Pipes, P. Plekhanov, M. Prince, S. Rajamani, J. Sandford, B. Sell, S. Sivakumar, P. Smith, B. Song, K. Tone, T. Troeger, J. Wiedemer, M. Yang and K. Zhang, "A 14nm logic

- technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size," 2014 IEEE International Electron Devices Meeting, San Francisco, CA, 2014, pp. 3.7.1-3.7.3. doi: 10.1109/IEDM.2014.7046976.

- [12] C. Auth, A. Aliyarukunju, M. Asoro, D. Bergstrom, V. Bhagwat, J. Birdsall, N. Bisnik, M. Buehler, V. Chikarmane, G. Ding, Q. Fu, H. Gomez, W. Han, D. Hanken, M. Haran, M. Hattendorf, R. Heussner, H. Hiramatsu, B. Ho, S. Jaloviar, I. Jin, S. Joshi, S. Kirby, S. Kosaraju, H. Kothari, G. Leatherman, K. Lee, J. Leib, A. Madhavan and K. Maria, "A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects," 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2017, pp. 29.1.1-29.1.4. doi: 10.1109/IEDM.2017.8268472.

- [13] (2017) Intel Technology and Manufacturing Day. [Online]. Available: https://newsroom.intel.com/newsroom/wp-content/uploads/sites/11/2017/03/Kaizad-Mistry-2017-Manufacturing.pdf.

- [14] (2019) Samsung Foundry Forum. [Online]. Available: https://news.samsung.com/global/samsung-electronics-leadership-in-advanced-foundry-technology-showcased-with-latest-silicon-innovations-and-ecosystem-platform.

- [15] X. He, J. Fronheiser, P. Zhao, Z. Hu, S. Uppal, X. Wu, Y. Hu, R. Sporer, L. Qin, R. Krishnan, E. M. Bazizi, R. Carter, K. Tabakman, A. K. Jha, H. Yu, O. Hu, D. Choi, J. G. Lee, S. B. Samavedam and D. K. Sohn, "Impact of aggressive fin width scaling on FinFET device characteristics," 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2017, pp. 20.2.1-20.2.4. doi: 10.1109/IEDM.2017.8268427.

- [16] P. Zheng, D. Connelly, F. Ding and T. J. K. Liu, "FinFET Evolution Toward Stacked-Nanowire FET for CMOS Technology Scaling," in IEEE Transactions on Electron Devices, vol. 62, no. 12, pp. 3945-3950, Dec. 2015. doi: 10.1109/TED.2015.2487367.

- [17] R. Oxland, X. Li, S. W. Chang, S. W. Wang, T. Vasen, P. Ramvall, R. Contreras-Guerrero, J. Rojas-Ramirez, M. Holland, G. Doornbos, Y. S. Chang, D. S. Macintyre, S. Thoms, R. Droopad, Y.-C. Yeo, C. H. Diaz, I. G. Thayne and M. Passlack, "InAs FinFETs With \$\textrm {H}\_{\textrm {H}}\_{\textrm {fin}}}=20\$ nm

- Fabricated Using a Top-Down Etch Process," in IEEE Electron Device Letters, vol. 37, no. 3, pp. 261-264, March 2016. doi: 10.1109/LED.2016.2521001.

- [18] J. G. Fiorenza, J.-S. Park, J. Hydrick, J. Li, J. Li, M. Curtin, M. Carroll and A. Lochtefel, "Aspect Ratio Trapping: A Unique Technology for Integrating Ge and III-Vs with Silicon CMOS," ECS Trans. 2010 volume 33, issue 6, 963-976. doi: 10.1149/1.3487628.

- [19] M.J.H. van Dal, G. Vellianitis, G. Doornbos, B. Duriez, T. M Shen, C. C. Wu, R. Oxland, K. Bhuwalka, M. Holland, T. L. Lee, C. Wann, C. H. Hsieh, B. H. Lee, K. M. Yin, Z. Q. Wu, M. Passlack and C. H. Diaz, "Demonstration of scaled Ge p-channel FinFETs integrated on Si," 2012 International Electron Devices Meeting, San Francisco, CA, 2012, pp. 23.5.1-23.5.4. doi: 10.1109/IEDM.2012.6479089.

- [20] C. Jeong, H.-H. Park, S. Dhar, S. Park, K. Lee, S. Jin, W. Choi, U.-H. Kwon, K.-H. Lee and Y. Park, "Physical understanding of alloy scattering in SiGe channel for high-performance strained pFETs," 2013 IEEE International Electron Devices Meeting, Washington, DC, 2013, pp. 12.2.1-12.2.4. doi: 10.1109/IEDM.2013.6724614.

- [21] D. Guo, G. Karve, G. Tsutsui, K-Y Lim, R. Robison, T. Hook, R. Vega, D. Liu, S. Bedell, S. Mochizuki, F. Lie, K. Akarvardar, M. Wang, R. Bao, S. Burns, V. Chan, K. Cheng, J. Demarest, J. Fronheiser, P. Hashemi, J. Kelly, J. Li, N. Loubet, P. Montanini, B. Sahu, M. Sankarapandian, S. Sieg, J. Sporre, J. Strane, R. Southwick, N. Tripathi, R. Venigalla, J. Wang, K. Watanabe, C. W. Yeung, D. Gupta, B. Doris, N. Felix, A. Jacob, H. Jagannathan, S. Kanakasabapathy, R. Mo, V. Narayanan, D. Sadana, P. Oldiges, J. Stathis, T. Yamashita, V. Paruchuri, M. Colburn, A. Knorr, R. Divakaruni, H. Bu and M. Khare, "FINFET technology featuring high mobility SiGe channel for 10nm and beyond," 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, 2016, pp. 1-2. doi: 10.1109/VLSIT.2016.7573360.

- [22] Sentaurus User's Manual, Version L-2016.03, Synopsys, Inc., Mountain View, CA, USA.

- [23] A. E. Carlson, "Device and circuit techniques for reducing variation in nanoscale SRAM," Ph.D. dissertation, Dept. Elect. Eng. Comput. Sci., Univ. California Berkeley, Berkeley, CA, USA, 2008.

# Chapter 2

# Si/Si<sub>1-x</sub>Ge<sub>x</sub>/Si Hetero-Channel FinFET for Enhanced P-Channel Performance in Low-Power Applications

#### 2.1 Introduction

The FinFET structure was adopted for high-volume manufacture of digital integrated circuits beginning at the 22 nm technology node because of (1) its superior electrostatic integrity as compared with the conventional planar MOSFET structure as well as (2) benefits from layout width scaling [1]. As conventional gate length scaling becomes more difficult, alternative approaches to decreasing the layout area of a FinFET, such as fin de-population [2], will be needed.

To increase the drive current per fin and thereby allow for a reduction in the number of fins required, FinFETs incorporating of high-mobility channel materials such germanium (Ge) [3], and III-V compound semiconductors [4] have been investigated. However, these are not as scalable to sub-10 nm gate length (i.e., beyond the 5 nm technology node) as silicon (Si) FinFETs, due to their lighter carrier tunneling effective mass (which results in degraded subthreshold swing) and larger dielectric permittivity (which results in greater drain-induced barrier lowering). Furthermore, these high-mobility channel materials are difficult to grow with low defect density on silicon wafer substrates, due to their lattice mismatch with silicon, even with the aspect ratio trapping technique (ART) [3].

Recently, silicon-germanium (SiGe) FinFET has been demonstrated to have better on-state performance than Si based FinFET [5]. Despite additional alloy scattering [6], a low Ge mole fraction SiGe fin grown on a Si substrate can still provide for higher hole mobility than a Si fin due to enhanced stress [7]. To further improve the performance of a SiGe FinFET, we propose herein a heterogeneous FinFET design in which only the inner portion of the gated fin channel region is replaced by Si<sub>1-x</sub>Ge<sub>x</sub>, as illustrated in Figure 2.1-1. Such a hetero-channel structure can be fabricated using a conventional fabrication process flow by starting with a silicon wafer substrate with an epitaxial layer of

Si<sub>1-x</sub>Ge<sub>x</sub>, if the Ge mole fraction x is low such that the epitaxial layer is thinner than the critical thickness for strain relaxation to occur. The structure also can be fabricated using aspect ratio trapping (ART) as described in [3].

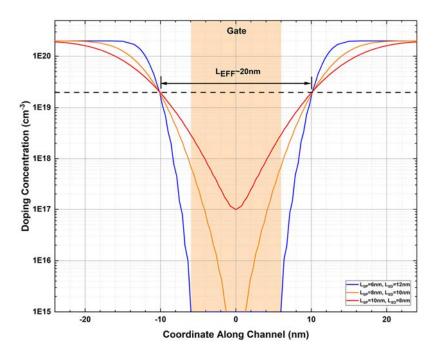

Figure 2.1-1. Double cutaway views of the two transistor structures studied in this work. (Left: Control Si FinFET, middle: Hetero-Channel FinFET, right: Control SiGe FinFET). The dashed lines circumscribe the hetero-channel. Different colors are used for the  $\mathrm{Si}_{1\text{-x}}\mathrm{Ge}_x$  in the channel region vs. the  $\mathrm{Si}_{1\text{-y}}\mathrm{Ge}_y$  in the embedded source and drain regions, to denote different Ge mole fractions. In this work,  $\mathrm{Si}_{0.5}\mathrm{Ge}_{0.5}$  is used for the source/drain contact regions. The fin height is defined to be the height of the fin above the shallow trench isolation (STI). Leff, the effective channel length, is defined to be the lateral distance between the locations where the S/D dopant concentration falls to  $2\times10^{19}$  cm<sup>-3</sup>.

## 2.2 Hetero-Channel $(Si/Si_{0.9}Ge_{0.1}/Si)$ FinFET

The hetero-channel FinFET design parameter values used in this work (summarized in Table 2.2-1) are based on the ITRS 6/5nm technology node, for an off-state leakage specification  $I_{\rm off}=100~{\rm pA/(\mu m}$  fin pitch) [8]. Due to even tighter feature pitch than described in [9], we expect the epitaxially grown  $Si_{0.5}Ge_{0.5}$  source and drain regions to merge between fins, so that they are more box shaped than diamond shaped. The fin width of 7 nm was selected based on the average fin width in [10].

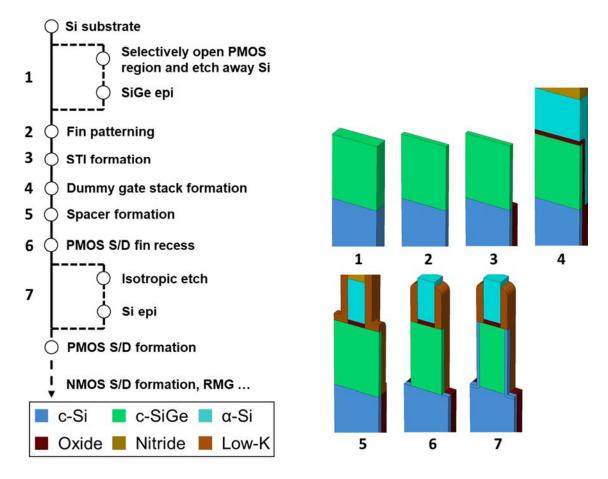

The Ge mole fraction in the channel region is first chosen to be 10% so that the fin height is thinner than the critical thickness [11]. The hetero-channel FinFET can be fabricated using a process similar to that for a conventional bulk-Si FinFET, with the following extra steps: (1) after the source/drain regions are etched back, an isotropic etch is used to laterally recess the Si<sub>0.9</sub>Ge<sub>0.1</sub> underneath the gate-sidewall spacers, (2) Si is epitaxially grown to fill in the laterally recessed regions, prior to epitaxial growth of the Si<sub>0.5</sub>Ge<sub>0.5</sub> source/drain regions. It should be noted that such an isotropic etch has been proposed for a bulk-Si FinFET process, to increase channel stress [12]. The recess length therefore corresponds to the Si thickness in the hetero-channel region. See appendix for the more detailed description on process flow.

To achieve an equivalent oxide thickness (EOT) of 0.6 nm, the gate dielectric comprises a 0.4 nm-thick interfacial layer (i.e.,  $SiO_x$  for the control Si FinFET and  $Si_{0.9}Ge_{0.1}O_x$  for the hetero-channel FinFET) and a 1.28 nm-thick high-permittivity layer (k = 25). The nominal supply voltage (V<sub>DD</sub>) is 0.65 V and the drain voltage for linear operation (V<sub>DLIN</sub>) is 50 mV. Sentaurus Process [13] is used to model stress inside the transistor structures.

Transistor performance is simulated using Sentaurus Device with the drift-diffusion transport model, ballistic mobility model, density gradient quantum correction model with orientation dependent coefficients, stress-dependent mobility model, and band-to-band tunneling model [13]. Such models have been calibrated to non-equilibrium Green function (NEGF) simulations [14]. The gate-sidewall spacer (k=5) length, source/drain region length, and punch-through stopper location are co-optimized to provide for the highest on-state current in the control Si FinFET for the given  $I_{\rm off}$  specification, within the constraints of gate pitch and fin pitch. The same design parameter values are used for the hetero-channel FinFET and Si<sub>0.9</sub>Ge<sub>0.1</sub> FinFET.

|                             | Si FinFET | Hetero-Channel<br>FinFET | $ m Si_{0.9}Ge_{0.1}\ FinFET$ |

|-----------------------------|-----------|--------------------------|-------------------------------|

| Gate Pitch (nm)             |           | 32                       |                               |

| Fin Pitch (nm)              |           | 20                       |                               |

| Gate Length (nm)            | 12        |                          |                               |

| Low-k Spacer<br>Length (nm) | 5         |                          |                               |

| Raised S/D<br>Height (nm)   |           | 3                        |                               |

| Recess Length (nm)          | N/A       | 1/2/3/4                  | N/A                           |

| EOT (nm)                    |           | 0.6                      |                               |

| Fin Width (nm)              | 7         |                          |                               |

| Fin Height (nm)             | 46        |                          |                               |

Table 2.2-1. Design parameter values for transistors. Note that as a corner case, a hetero-channel FinFET with 0nm recess length is essentially the same as the SiGe FinFET since there are no regrown Si regions near the source and drain regions. EOT is the equivalent oxide thickness, which is calculated by adding the interfacial layer thickness (i.e., 0.4nm) to the equivalent SiO<sub>2</sub> thickness of the high-k HfO<sub>2</sub> layer (i.e., 0.2nm = 1.28nm/25×3.9). Due to the low Ge molefraction (i.e., 0.1) used in the designs, we assume the Si<sub>0.9</sub>Ge<sub>0.1</sub>O<sub>x</sub> has the same permittivity as SiO<sub>2</sub>.

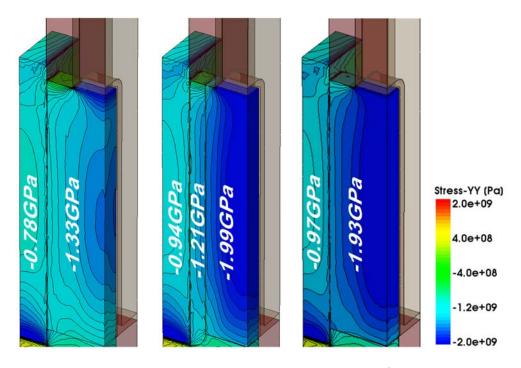

Figure 2.2-1 shows the longitudinal stress profiles and average values within each semiconductor region. Hetero-channel FinFETs has higher, in magnitude, average longitudinal compressive stress underneath the gate (i.e.,  $\mathrm{Si_{0.9}Ge_{0.1}}$  region) due to additional stress from the underlying Si substrate as well as the regrown Si region. The  $\mathrm{Si_{0.9}Ge_{0.1}}$  FinFET also experiences higher (in magnitude) longitudinal compressive stress in the channel also due to the fact that the lattice mismatch comes from the source/drain  $\mathrm{Si_{0.5}Ge_{0.5}}$  regions and the bottom Si substrate.

Figure 2.2-1. Longitudinal stress contours from S-Process. (Left: Si FinFET, middle: Hetero-Channel FinFET, right:  $Si_{0.9}Ge_{0.1}$  FinFET). A stress dependent mobility model is used in the subsequent S-Device 3-D TCAD simulations. The average longitudinal stress in S/D and channel are annotated over the corresponding regions.

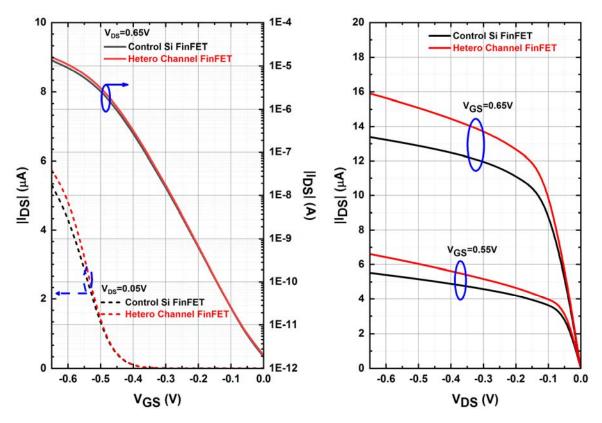

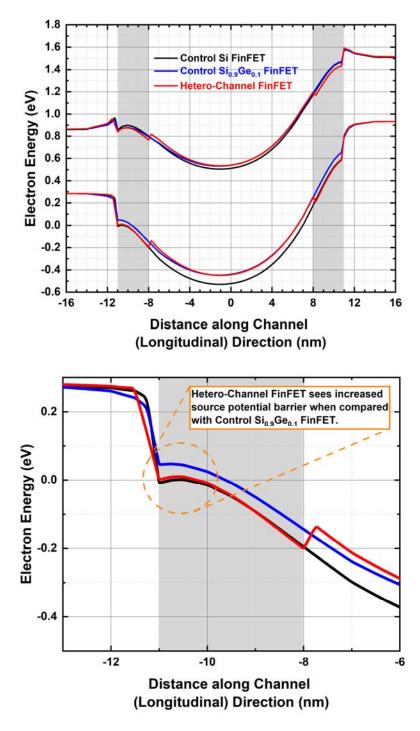

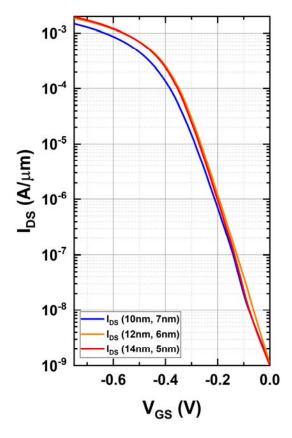

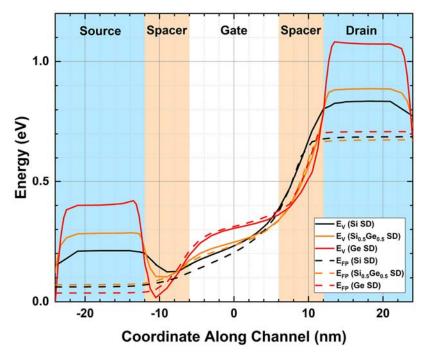

Figure 2.2-2 shows the simulated FinFET transfer and output characteristics, and Table 2.2-2 provides a summary comparison of key performance parameters. The enhanced performance of the hetero-channel FinFET stems from the valence band (VB) offset between Si<sub>0.9</sub>Ge<sub>0.1</sub> and Si along two directions: In the vertical (depth) direction, the VB offset provides for lower sub-threshold leakage because it poses a barrier for holes to enter the Si sub-fin region. Figure 2.2-3 shows the energy band diagram along the channel direction: The regrown Si regions underneath the gate-sidewall spacers, corresponding to the shaded regions in Figure 2.2-3, have higher hole potential energy, as compared to Si<sub>0.9</sub>Ge<sub>0.1</sub>. Hence, as shown in Figure 2.2-3 (b), in a (p-channel) hetero-channel FinFET, holes see increased source-side diffusion barrier in the off-state when compared with the control Si<sub>0.9</sub>Ge<sub>0.1</sub> FinFET (i.e., a baseline "hetero-channel" FinFET with zero recess length case). The source side barrier in the hetero-channel FinFET is the same as that in the case of Si FinFET. This effect is similar to that of the "halo" implant in a planar MOSFET [15].

Figure 2.2-2. Simulated transfer (left) and output (right) characteristics for control Si FinFET and hetero-channel FinFET. Output characteristics are simulated at  $V_{\rm GS}=0.55 V$  and 0.65 V.

To decouple the effects of the two valance band offsets, results for the aforementioned control Si<sub>0.9</sub>Ge<sub>0.1</sub> FinFET are also included in the third column of Table 2.2-2. A comparison shows that the vertical VB offset near the top of the STI accounts for 9% of the improvement in on-state current, while the longitudinal VB offset accounts for an additional 7%.

Figure 2.2-3. Band diagram along channel (longitudinal) direction. The shaded region indicates Si (higher bandgap) material in the hetero-channel FinFET. Band diagrams of control Si FinFET and SiGe FinFET (with same molefraction as in channel SiGe in hetero-channel) are also included for reference.

| Metric                                                             | Si<br>FinFET | $egin{aligned} 	ext{Hetero-Channel FinFET} \ 	ext{(Recess Length} &= 2 	ext{nm} \ \end{aligned}$ | $ m Si_{0.9}Ge_{0.1} \ FinFET$ |

|--------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------|--------------------------------|

| I <sub>off</sub>   (pA)                                            | 2.0          |                                                                                                  |                                |

| I <sub>on</sub>   (uA)                                             | 13.8         | 16.0 (+16%)                                                                                      | 15.1 (+9%)                     |

| I <sub>eff</sub>   (uA)                                            | 5.98         | $6.91 \; (+16\%)$                                                                                | 6.62 (+11%)                    |

| V <sub>t,sat</sub> (V)                                             | -0.36        | -0.36                                                                                            | -0.37                          |

| V <sub>t,lin</sub> (V)                                             | -0.40        | -0.40                                                                                            | -0.41                          |

| DIBL (mV/V)                                                        | 67           | 67                                                                                               | 67                             |

| ${ m SS}_{ m sat}~({ m mV/dec})$                                   | 74           | 73                                                                                               | 75                             |

| C <sub>gg</sub> (aF)                                               | 44.6         | 44.2                                                                                             | 43.7                           |

| $ m C_{gg} V_{gg} / I_{on}  \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ | 2.11         | 1.80 (-15%)                                                                                      | 1.89 (-11%)                    |

Table 2.2-2. Comparisons of transistor performance metric ( $V_{dsat}=V_{dd}=0.65V$ ,  $V_{dlin}=0.05V$ ).  $^{a}V_{T}$  is extracted at  $100nA\times W_{pitch}/L_{eff}=0.113uA$ .  $W_{pitch}$  is the fin pitch. The percentage in parentheses is relative to the control Si FinFET result.

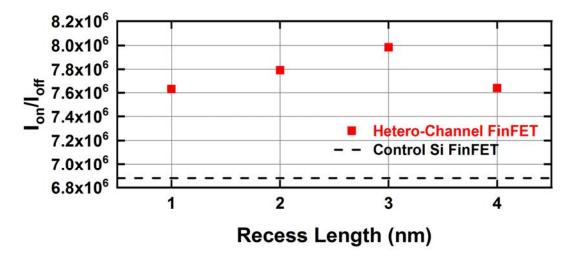

In general, hetero-channel FinFETs with larger recess length exhibit steeper subthreshold swing. However, there exists a design tradeoff between improved electrostatic integrity and increased on-state resistance, for the recess length. Figure 2.2-4 shows how the on/off current ratio varies with recess length. The optimal design, with recess length = 3 nm, has similar subthreshold swing and drain-induced barrier lowering values as for the control Si FinFET.

Figure 2.2-4. Impact of recess length (in nm) on the performance of heterochannel FinFET.

There is little difference in total gate capacitance ( $C_{gg}$ ) since a relatively low Ge mole fraction is used in the channel region. Therefore, the intrinsic delay is reduced by 15% for the optimized hetero-channel FinFET vs. the control Si FinFET.

# 2.3 Hetero-Channel FinFETs with Varying Ge Molefraction

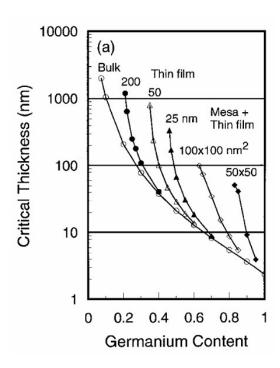

In Section 2.2, the hetero-channel design featuring  $Si_{0.9}Ge_{0.1}$  is presented. In this section, we extend this study to different Ge molefractions. Modern FinFETs generally require a fin height of more than 40nm. As shown in Figure 2.3-1, in order to grow  $Si_{1-x}Ge_x$  thick enough for fin height directly on top of the silicon substrate, the Ge molefraction should be less than 0.25 so that the critical thickness of  $Si_{1-x}Ge_x$  is above 100nm. Otherwise, complicated processes such as ART might be required.

In this study, the Ge molefraction is varied from 0.05 to 0.25, while the high bandgap channel region is fixed to silicon. Table 2.3-1 summarizes the performance of different hetero-channel FinFET designs featuring different Ge molefraction  $\mathrm{Si}_{1\text{-}x}\mathrm{Ge}_x/\mathrm{Si}$  channels.

Figure 2.3-1. Critical thickness of Si<sub>1-x</sub>Ge<sub>x</sub> alloy as a function of germanium content on different substrates. Adapted from [11].

From Table 2.3-1, it is shown that with increasing Ge molefraction, the control SiGe FinFET has worse electrostatic integrity due to smaller bandgap and higher permittivity. However, the on-state current of control SiGe FinFET can be steadily improved due to increased compressive stress in the channel. For hetero-channel FinFET designs, the best performance case always happens when the Si channel region is 3nm thick for all Ge molefractions under study. With the Ge molefraction being 0.15 or 0.2, the best hetero-channel design can achieve +17% improvement over the control Si FinFET. However, as the Ge molefraction increases, the sensitivity of performance to the recess length becomes much larger. For example, when the Ge molefraction is 0.25, if the recess length is 4nm, the on-state current of the hetero-channel FinFET is only 55% of that of the control Si FinFET. This is due to the large bandgap difference between Si and Si<sub>0.75</sub>Ge<sub>0.25</sub> region and in the on-state, hole injection becomes more difficult and hence degrades the transistor performance. Therefore, considering the performance sensitivity, the optimal Ge molefraction is 0.1.

| xGeFin | Recess Length (nm) | Ion  (µA) | %Ion | ${ m SS_{SAT}} \ ({ m mV/dec})$ |

|--------|--------------------|-----------|------|---------------------------------|

| 0      | Si-FF              | 13.8      | 100% | 74                              |

|        | 4                  | 15.2      | 110% | 74                              |

|        | 3                  | 15.4      | 112% | 73                              |

| 0.05   | 2                  | 15.1      | 109% | 74                              |

|        | 1                  | 14.9      | 108% | 74                              |

|        | SiGe-FF            | 14.5      | 105% | 74                              |

|        | 4                  | 15.3      | 111% | 73                              |

|        | 3                  | 15.9      | 116% | 73                              |

| 0.1    | 2                  | 15.6      | 113% | 74                              |

|        | 1                  | 15.2      | 110% | 75                              |

|        | SiGe-FF            | 15.0      | 109% | 75                              |

|        | 4                  | 14.1      | 102% | 73                              |

|        | 3                  | 16.2      | 117% | 73                              |

| 0.15   | 2                  | 15.7      | 114% | 74                              |

|        | 1                  | 15.4      | 112% | 75                              |

|        | SiGe-FF            | 15.3      | 111% | 75                              |

|        | 4                  | 11.0      | 80%  | 73                              |

|        | 3                  | 16.2      | 117% | 73                              |

| 0.2    | 2                  | 15.8      | 114% | 74                              |

|        | 1                  | 15.3      | 111% | 76                              |

|        | SiGe-FF            | 15.4      | 112% | 76                              |

|        | 4                  | 7.6       | 55%  | 73                              |

|        | 3                  | 15.8      | 114% | 73                              |

| 0.25   | 2                  | 15.5      | 112% | 75                              |

|        | 1                  | 15.1      | 109% | 76                              |

|        | SiGe-FF            | 15.4      | 112% | 76                              |

Table 2.3-1. Performance summary of hetero-channel designs featuring varying Ge molefraction SiGe. xGeFin is the Ge molefraction used for Si<sub>1-x</sub>Ge<sub>x</sub> channel in both the control SiGe FinFET and the hetero-channel FinFETs. "Si-FF" represents the control Si channel FinFET. "SiGe-FF" in the second column represents the control SiGe channel FinFET with the same Ge molefraction as in the corresponding hetero-channel designs. SiGe-FF can be thought of hetero-channel design with 0nm recess length.

### 2.4 Conclusion

In Section 2.2, the performance of a p-channel FinFET comprising a heterogeneous silicon (Si) and silicon-germanium (Si<sub>0.9</sub>Ge<sub>0.1</sub>) channel region is evaluated using three-dimensional (3-D) TCAD simulations, and benchmarked against a conventional p-channel Si FinFET and SiGe FinFET (with the same Ge content). The results show that the optimal hetero-channel design provides for larger on-state current while maintaining comparable electrostatic integrity as the conventional design due to the valence band (VB) offset between Si<sub>0.9</sub>Ge<sub>0.1</sub> and Si. The enhanced performance is achieved with relatively low Ge mole fraction (10%) in the channel region, for ease of manufacture.

In Section 2.3, hetero-channel designs featuring varying Ge molefraction (x = 0 - 0.25) are investigated. It is shown that at x = 0.15 or 0.2, even though the best cases (i.e., recess length = 3nm) can achieve better performance than that in x = 0.1, the performance sensitivity to the recess length becomes much larger, making them less favorable for fabrication.

Therefore, the hetero-channel FinFET featuring Si/Si<sub>0.9</sub>Ge<sub>0.1</sub>/Si is a promising candidate for future low-power applications.

# 2.5 Appendix: Process Simulation in Sentaurus Process

Since the hetero-channel consists of two different materials (i.e., Si and SiGe), it is important to model the channel stress correctly. And the final stress in the channel depends on the ordering of processing steps in the process flow. Therefore, the process simulator, Sentaurus Process (S-Process), is used to construct the hetero-channel FinFET structure. The Sentaurus advanced calibration is also turned on to accurately model the stress [16].

Figure 2.5-1 shows the process flow for constructing the hetero-channel FinFETs. This process is largely similar to the conventional bulk Si FinFET, except for step 1 and 7. In step 1, since only a low Ge molefraction SiGe is used, it can be deposited directly on top of the silicon substrate via epitaxy growth. Aspect ratio trapping (ART) growth technique is not required. In step 7, after the fin recess to make room for the SiGe source/drain regions, an isotropic etching process is performed, followed by the Si epitaxy. This Si refills the vacancy left by the prior isotropic etching process and form the high bandgap region as required in the hetero-channel design. Afterwards, the embedded

source/drain is grown via SiGe epitaxy. The rest of the process (e.g., replacement metal gate) stays the same as in a Si FinFET process.

Figure 2.5-1. The process flow in S-Process to construct the hetero-channel FinFETs. S/D epitaxial growth for p-channel MOSFETs and subsequent replacement metal gate (RMG) process are not shown since they are the same as in the conventional bulk Si FinFET process.

#### 2.6 References

C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, M. Buehler, V. Chikarmane, T. Ghani, T. Glassman, R. Grover, W. Han, D. Hanken, M. Hattendorf, P. Hentges, R. Heussner, J. Hicks, D. Ingerly, P. Jain, S. Jaloviar, R. James, D. Jones, J. Jopling, S. Joshi, C. Kenyon, H. Liu, R. McFadden, B. McIntyre, J. Neirynck, C. Parker, L. Pipes, I. Post, S. Pradhan, M. Prince, S. Ramey, T. Reynolds, J. Roesler, J. Sandford, J. Seiple, P. Smith, C. Thomas, D. Towner, T. Troeger, C. Weber, P. Yashar, K. Zawadzki and K.

- Mistry, "A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors," 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, 2012, pp. 131-132. doi: 10.1109/VLSIT.2012.6242496S.

- [2] J. Ryckaert, P. Raghavan, P. Schuddinck, H. B. Trong, A. Mallik, S. S. Sakhare, B. Chava, Y. Sherazi, P. Leray, A. Mercha, J. Bömmels, G. R. McIntyre, K. G. Ronse, A. Thean, Z. Tökei, A. Steegen and D. Verkest, "DTCO at N7 and beyond: patterning and electrical compromises and opportunities," Proc. SPIE 9427, Design-Process-Technology Co-optimization for Manufacturability IX, 94270C (18 March 2015). doi: 10.1117/12.2178997.

- [3] M. J. H. van Dal, G. Vellianitis, B. Duriez, G. Doornbos, C.-H. Hsieh, B.-H. Lee, K.-M. Yin, M. Passlack and C. H. Diaz, "Germanium p-Channel FinFET Fabricated by Aspect Ratio Trapping," in IEEE Transactions on Electron Devices, vol. 61, no. 2, pp. 430-436, Feb. 2014. doi: 10.1109/TED.2013.2295883.

- [4] A. V. Thathachary, G. Lavallee, M. Cantoro, K. K. Bhuwalka, Y.-C. Heo, S. Maeda and S. Datta, "Impact of Sidewall Passivation and Channel Composition on InxGa1-xAs FinFET Performance," in IEEE Electron Device Letters, vol. 36, no. 2, pp. 117-119, Feb. 2015. doi: 10.1109/LED.2014.2384280.

- [5] D. Guo, G. Karve, G. Tsutsui, K-Y Lim, R. Robison, T. Hook, R. Vega, D. Liu, S. Bedell, S. Mochizuki, F. Lie, K.Akarvardar, M. Wang, R. Bao, S. Burns, V. Chan, K. Cheng, J. Demarest, J. Fronheiser, P. Hashemi, J. Kelly, J. Li, N. Loubet, P. Montanini, B. Sahu, M. Sankarapandian, S. Sieg, J. Sporre, J. Strane, R. Southwick, N. Tripathi, R. Venigalla, J. Wang, K. Watanabe, C. W. Yeung, D. Gupta, B. Doris, N. Felix, A. Jacob, H. Jagannathan, S. Kanakasabapathy, R. Mo, V. Narayanan, D. Sadana, P. Oldiges, J. Stathis, T. Yamashita, V. Paruchuri, M. Colburn, A. Knorr, R. Divakaruni, H. Bu and M. Khare, "FINFET technology featuring high mobility SiGe channel for 10nm and beyond," 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, 2016, pp. 1-2. doi: 10.1109/VLSIT.2016.7573360.

- [6] M. V. Fischetti and S. E. Laux, "Band structure, deformation potentials, and carrier mobility in strained Si, Ge, and SiGe alloys," Journal of Applied Physics, 1996, 80:4, 2234-2252, doi: 10.1063/1.363052.

- [7] C. Jeong, H.-H. Park, S. Dhar, S. Park, K. Lee, S. Jin, W. Choi, U.-H. Kwon, K.-H. Lee and Y. Park, "Physical understanding of alloy scattering in SiGe channel for high-performance strained pFETs," 2013 IEEE International Electron

- Devices Meeting, Washington, DC, 2013, pp. 12.2.1-12.2.4. doi: 10.1109/IEDM.2013.6724614.

- [8] (2015) International Technology Roadmap for Semiconductors (ITRS). [Online]. Available: http://www.itrs2.net/itrs-reports.html.

- [9] G. Enemana, D. P. Bruncoa, L. Wittersa, B. Vincenta, P. Faviaa, A. Hikavyya, A. D. Keersgietera, J. Mitarda, R. Looa, A. Velosob, O. Richarda, H. Bendera, W. Vandervorsta, M. Caymaxa, N. Horiguchib, N. Collaerta and A. Theana, "Stress Simulations of Si- and Ge-Channel FinFETs for the 14 nm-Node and Beyond," ECS Trans. 2013 volume 53, issue 1, 225-236. doi: 10.1149/05301.0225ecst.

- [10] C. Auth, A. Aliyarukunju, M. Asoro, D. Bergstrom, V. Bhagwat, J. Birdsall, N. Bisnik, M. Buehler, V. Chikarmane, G. Ding, Q. Fu, H. Gomez, W. Han, D. Hanken, M. Haran, M. Hattendorf, R. Heussner, H. Hiramatsu, B. Ho, S. Jaloviar, I. Jin, S. Joshi, S. Kirby, S. Kosaraju, H. Kothari, G. Leatherman, K. Lee, J. Leib, A. Madhavan and K. Maria, "A 10nm high performance and low-power CMOS technology featuring 3<sup>rd</sup> generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects," 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, 2017, pp. 29.1.1-29.1.4. doi: 10.1109/IEDM.2017.8268472.

- [11] F. Y. Huang, "Theory of Strain Relaxation for Epitaxial Layers Grown on Substrate of a Finite Dimension,", in Phys. Rev. Lett., vol. 85, no. 4, pp. 784-787, July. 2000. doi: 10.1103/PhysRevLett.85.784.

- [12] M. Garcia Bardon, V. Moroz, G. Eneman, P. Schuddinck, M. Dehan, D. Yakimets, D. Jang, G. Van der Plas, A. Mercha, A. Thean, D. Verkest and A. Steegen, "Layout-induced stress effects in 14nm & Enp. 10nm FinFETs and their impact on performance," 2013 Symposium on VLSI Circuits, Kyoto, 2013, pp. T114-T115.

- [13] Sentaurus User's Manual, Version L-2016.03, Synopsys, Inc., Mountain View, CA, USA.

- [14] M. Choi, V. Moroz, L. Smith and J. Huang, "Extending drift-diffusion paradigm into the era of FinFETs and nanowires," 2015 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Washington, DC, 2015, pp. 242-245. doi: 10.1109/SISPAD.2015.7292304.

- [15] C. Gupta, H. Agarwal, S. Dey, C. Hu and Y. S. Chauhan, "Analysis and modeling of capacitances in halo-implanted MOSFETs," 2017 IEEE Electron Devices Technology and Manufacturing Conference (EDTM), Toyama, 2017, pp. 198-200. doi: 10.1109/EDTM.2017.7947563.

- [16] Advanced Calibration for Process Simulation User Guide, Version L-2016.03, Synopsys, Inc., Mountain View, CA, USA.

## Chapter 3

## Cell Ratio Tuning for High-Density SRAM Voltage Scaling with Inserted-Oxide FinFETs (iFinFETs)

#### 3.1 Introduction

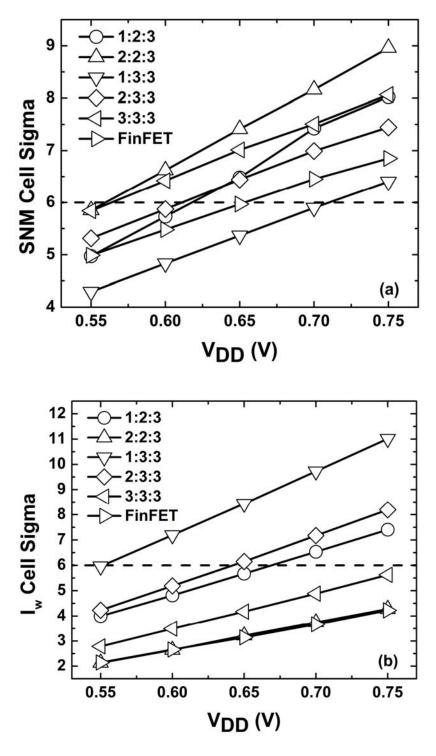

Today bulk-silicon FinFET technology is used for high-volume manufacturing of sub-20 nm-generation CMOS integrated circuits [1, 2]. Due to the {110} finsidewall (channel surface) crystallographic orientation and a higher level of mechanical strain induced in the channel region by embedded silicon-germanium source/drain regions, the drive strength of a p-channel (PMOS) FinFET is comparable to that of an n-channel (NMOS) FinFET of the same fin height [1]. Although this may be favorable for high-speed digital logic applications, it results in poor write-ability of a minimally sized six-transistor (6-T) static memory (SRAM) cell comprising two single-fin PMOS pull-up (PU) FinFETs, two singlefin NMOS pass-gate (PG) FinFETs, and two single-fin NMOS pull-down (PD) FinFETs [3]. The drive strength of the PU FinFETs can be reduced by making their effective fin height shorter; however, methods such as selectively adjusting the physical height of the gated fin by selectively adjusting the recess depth of the shallow trench isolation (STI) oxide [4] or by adjusting the depth of the punchthrough-stopper (PTS) fin doping profile are susceptible to significant process-induced variations which result in lower manufacturing yield. Therefore, circuit-level "assist" techniques are commonly used to enhance the cell read margin and/or write margin to allow for lower minimum cell operating voltage  $(V_{MIN})$  [5].

Inserted-oxide FinFET (iFinFET) technology was proposed to provide an evolutionary pathway for continued transistor scaling [6]. The electrostatic integrity of an iFinFET (*i.e.* gate control of the electrostatic potential in the channel region) is superior to that of a FinFET due to gate fringing electric fields through the inserted oxide (SiO<sub>2</sub>) layers. Although the gate-all-around (GAA) field-effect transistor (FET) can achieve even better electrostatic integrity, this comes at the cost of a larger intrinsic delay [6]. Also, to achieve comparable

layout area efficiency as a FinFET, a GAAFET should comprise multiple nanowires (NWs) that are vertically stacked apart by 10 nm or more (to allow sufficient room for the dielectric/metal/dielectric gate stacks in-between the NWs), necessitating the formation of higher-aspect-ratio fin structures during the device fabrication process. In contrast, the inserted-oxide layers in an iFinFET can be very thin (less than 5 nm), and also can serve effectively as dopant diffusion barriers [7]. In this chapter, a scheme for controllably reducing the drive strength of an iFinFET is proposed and demonstrated via three-dimensional (3-D) device simulations and a calibrated compact model that to provide for lower V<sub>MIN</sub> of a minimally sized 6-T SRAM cell, for high-density cache memory.

### 3.2 Inserted-Oxide FinFET (iFinFET)

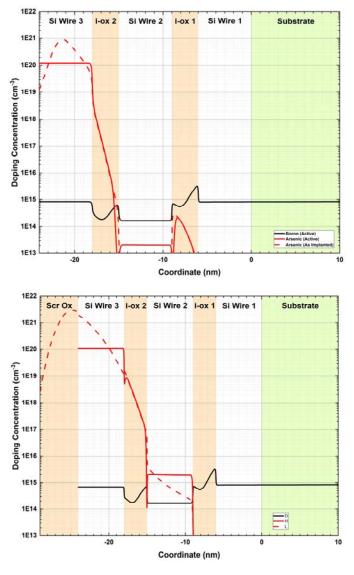

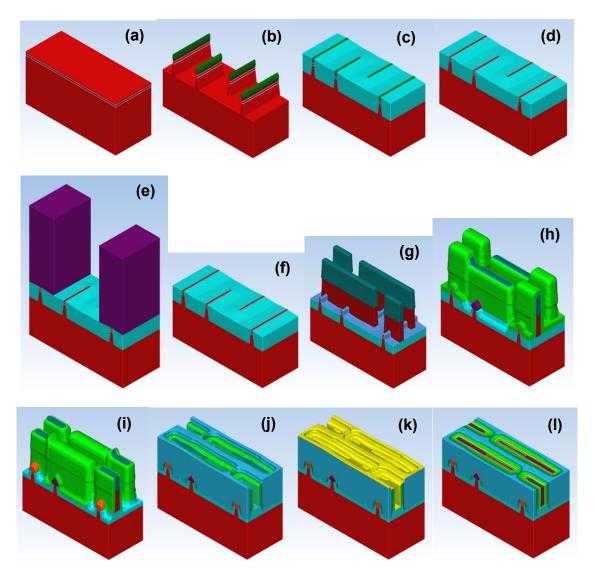

It is generally expected that some form of gate-all-around transistor structure (GAAFET) will be used in the future to enable further reductions in gate length with adequate suppression of short-channel effects. To achieve similar or superior on-state current per unit layout area, the GAAFET must comprise multiple stacked nanowire (NW) channel regions. In practice, this is done by growing a "sandwich" of multiple  $\mathrm{Si/Si_{1-x}Ge_x}$  layers using multiple alternating epitaxy growth steps. The  $\mathrm{Si_{1-x}Ge_x}$  layers are later selectively etched away and replaced by the gate dielectric and gate metal layer stack. To accommodate these layers, the  $\mathrm{Si_{1-x}Ge_x}$  sacrificial layers must be relatively thick (~10nm). As a result, to form a GAAFET, a very high aspect ratio (height:width > 6:1) fin structure must be formed. To further improve the current density, more stacked NWs may be required, which means the aspect ratio will be even higher posing a greater fabrication challenge.

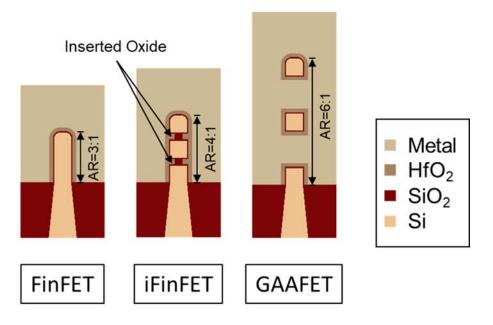

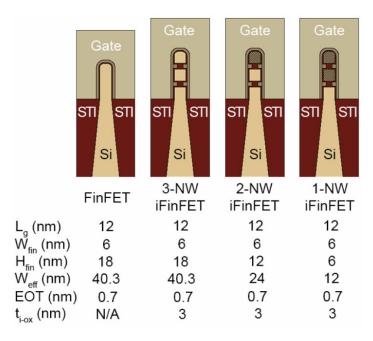

Figure 3.2-1. A comparison of the 3 transistor structures (Cross-sectional views across the channel regions). The fin widths are each 6nm, and the total Si height is 18nm. The inserted-oxide thickness is 3nm. The spacing between adjacent NWs in GAAFET is 10nm.

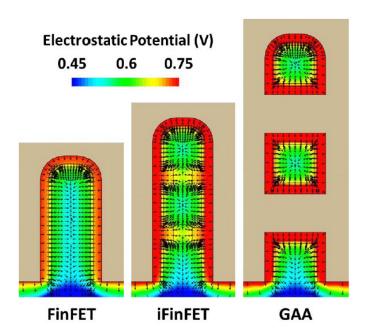

To mitigate these issues, an evolutionary FinFET design - the inserted-oxide FinFET (iFinFET) [6, 8, 9] is proposed (Figure 3.2-1). iFinFET exhibits superior electrostatic integrity by allowing the gate fringing field to penetrate the inserted-oxide and control the bottom of the NWs (except for the bottom NW), as shown in Figure 3.2-2. The performance can be further improved by recessing the inserted-oxide in the middle to replace portion of the inserted-oxide (k = 3.9) with  $HfO_2$  (k = 25). This can be done after the dummy oxide removal and before the high-k dielectric ( $HfO_2$ ) deposition in the replacement metal gate (RMG) module. Due to the small thickness (3nm) of the inserted-oxide, the gate metal will not be present in the recessed portion, and hence the increase in total capacitance is small. In addition, compared to the GAAFET, the aspect ratio of the fin structure that needs to be formed to make an iFinFET is much smaller.

The fabrication process of the iFinFET is identical to that of the conventional bulk-Si FinFET, except that a multi-SOI (silicon-on-insulator on silicon-on-insulator) wafer instead of a bulk-Si wafer is used as the starting substrate. As shown in [10], the 2-NW iFinFET also offers the benefit of superior electrostatic integrity over that of FinFET. In that case, a conventional SOI wafer can be used.

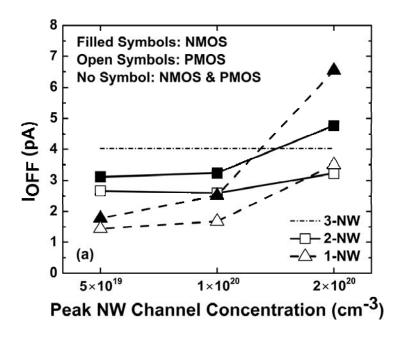

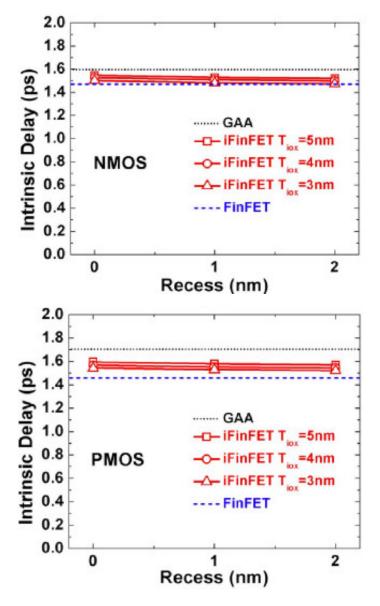

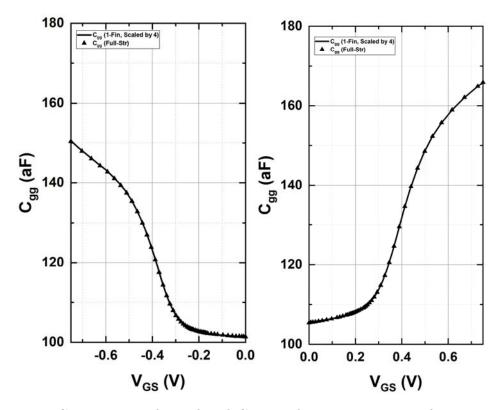

As shown in Figure 3.2-3, the subthreshold swing (SS<sub>SAT</sub>) and drain-induced barrier lowering (DIBL) of the iFinFET is better than that of the FinFET, but worse than those of GAAFET. The situation is the same for the on-state currents and the intrinsic gain ( $g_m/g_{ds}$ ). The gate-to-drain ( $C_{gd}$ ) and total gate ( $C_{gg}$ ) capacitance in iFinFET are larger than those of FinFET due to larger overlap between gate and the drain. This situation is exacerbated in the GAAFET. The n-channel iFinFET can achieve a similar intrinsic delay ( $C_{gg}V_{DD}/I_{ON}$ ) as the FinFET. It should be noted that in this study an aggressively thin NW spacing of 6nm is assumed for the GAAFET. In practice this would be challenging to achieve.

Figure 3.2-2. Electrostatic potential and electric field lines (arrows) in the linear regime ( $V_{GS}=0.75V$ ,  $V_{DS}=0.05V$ ) in the 3 transistor structures. It can be seen the iFinFET achieves good gate control over the electrostatic potential at the bottom of the NW (except for the bottom-most channel region). Adapted from [6].

With regard to process-induced variations, it has been shown that the performance of the iFinFET is relatively insensitive to variations in the thicknesses of the inserted-oxide and the inserted-oxide recess [6].

| Device Parameter                       | FinFET / iFinFET / GAA |  |

|----------------------------------------|------------------------|--|

| Nominal Gate Length, $L_{ m g}$ (nm)   | 12                     |  |

| Fin/NW Width, W <sub>fin</sub> (nm)    | 6                      |  |

| Total Si Height above STI (nm)         | 18                     |  |

| Gate Pitch (nm)                        | 35                     |  |

| <b>Equivalent Oxide Thickness (nm)</b> | 0.7                    |  |

| Inserted-Oxide Thickness (nm)          | 0/3/0                  |  |

| Metal Thickness between NWs (nm)       | 0/0/6                  |  |

| Specific Contact Resistivity (Ω-cm²)   | 3.5×10 <sup>-9</sup>   |  |

|                                          | FinFET |      | iFinFET |      | GAA  |      |

|------------------------------------------|--------|------|---------|------|------|------|

|                                          | N      | P    | N       | P    | N    | P    |

| $ I_{ m OFF} $ (pA)                      | 0.8    | 0.8  | 0.8     | 0.8  | 0.8  | 0.8  |

| $ I_{\rm ON} $ ( $\mu A$ )               | 15.1   | 14.7 | 18.1    | 16.9 | 21.7 | 19.5 |

| $I_{\rm EFF} $ ( $\mu A$ )               | 7.1    | 7.1  | 8.6     | 8.2  | 10.4 | 9.5  |

| $ V_{\mathrm{T,SAT}} $ (V)               | 0.42   | 0.42 | 0.41    | 0.40 | 0.40 | 0.39 |

| DIBL (mV/V)                              | 40     | 36   | 32      | 28   | 23   | 20   |

| SS <sub>SAT</sub> (mV/dec)               | 78     | 78   | 75      | 75   | 71   | 71   |

| $C_{\rm gd}$ (aF)                        | 8.1    | 7.8  | 9.2     | 8.9  | 12.0 | 11.6 |

| $C_{\rm gg}$ (aF)                        | 29.7   | 28.7 | 35.6    | 34.2 | 46.4 | 44.4 |

| $C_{\rm gg}V_{\rm DD}/ I_{\rm ON} $ (ps) | 1.47   | 1.45 | 1.47    | 1.52 | 1.60 | 1.70 |

| $g_{ m m}/g_{ m ds}$                     | 22.4   | 28.2 | 25.7    | 30.1 | 30.6 | 36.3 |

Figure 3.2-3. Design parameter values and simulated transistor performance values for the 3 different transistor structures (n-channel and p-channel). Adapted from [6].

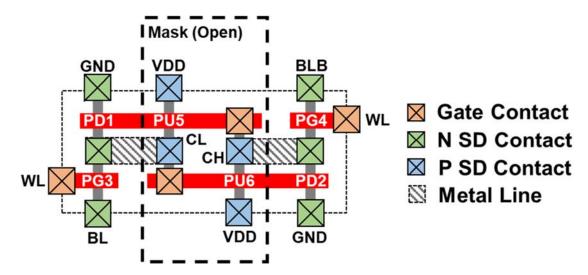

### 3.3 6-T SRAM High Density Cell Design

## 3.3.1 6-T SRAM Operations

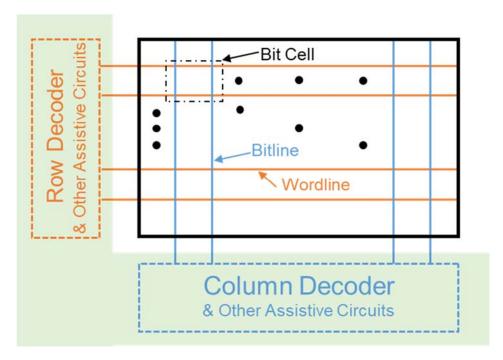

An SRAM circuit mainly consists of two parts: (1) the bit cells and (2) the peripheral circuits (Figure 3.3-1). The bit cells are arranged in rows and columns and each bit cell stores 1 bit of information. The peripheral circuits are circuits that surround the bit cells and are used to store and access information from the bit cells. Some specific functions of the peripheral circuits include (1) charging and discharging the bitlines (BLs and BLBs) and wordlines (WLs), (2) sensing the difference between BL and BLB potentials, (3) decoding inputs, etc. In

modern SRAM, complex peripheral circuits are also used to assist SRAM read and write operations [11, 12], at the cost of a larger layout area and greater power consumption.

Figure 3.3-1. Block-level schematic of SRAM circuitry.

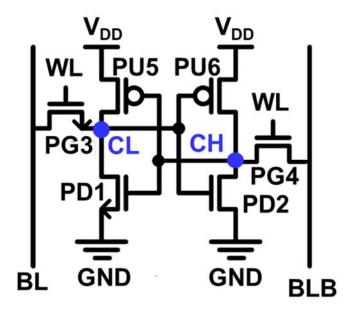

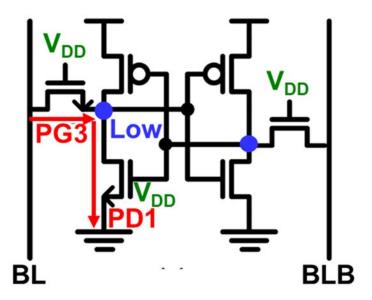

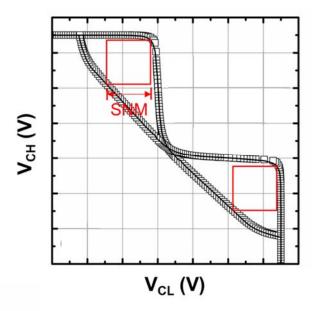

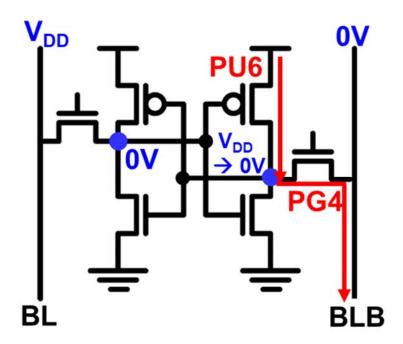

Figure 3.3-2. Circuit schematic of a 6-T SRAM bit cell.

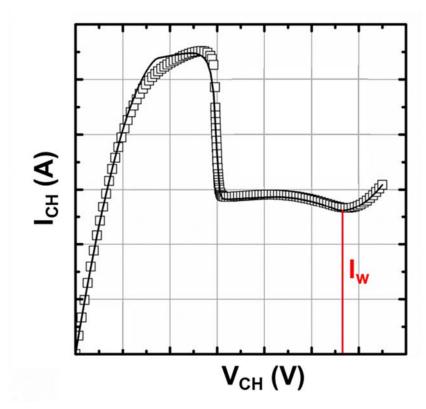

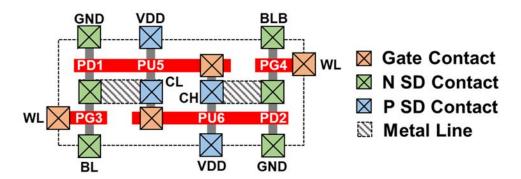

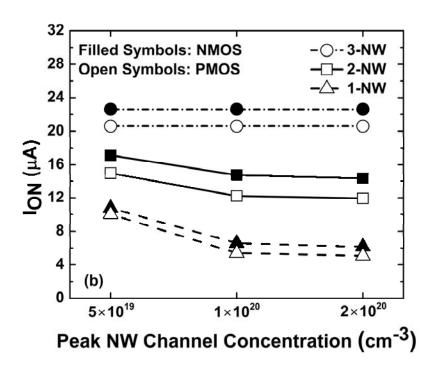

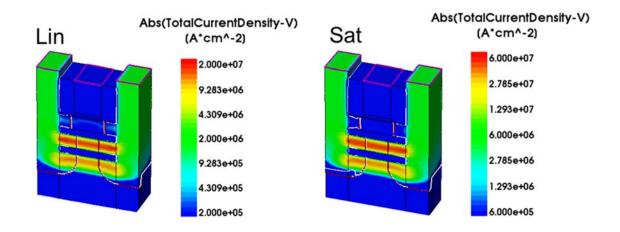

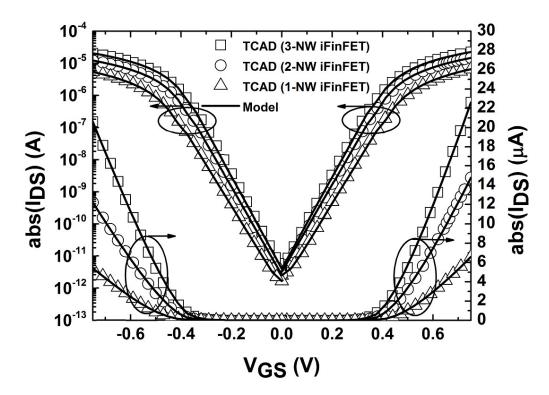

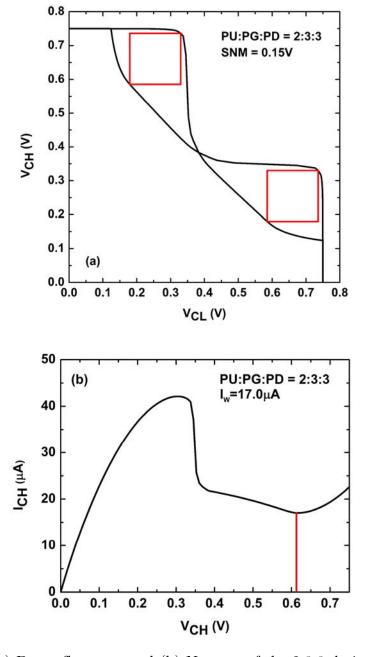

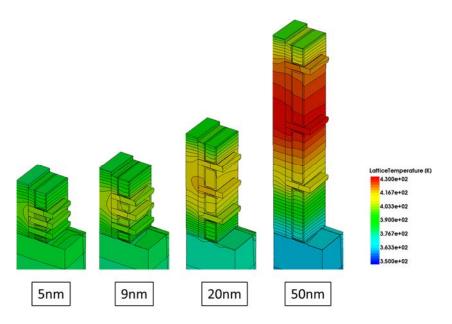

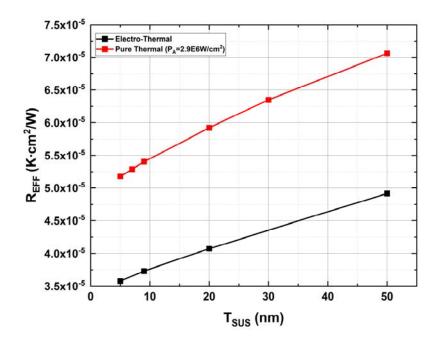

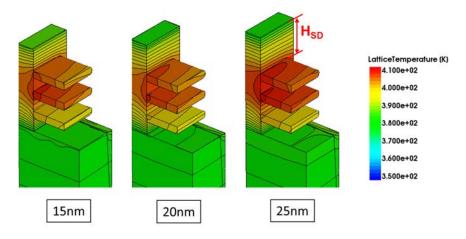

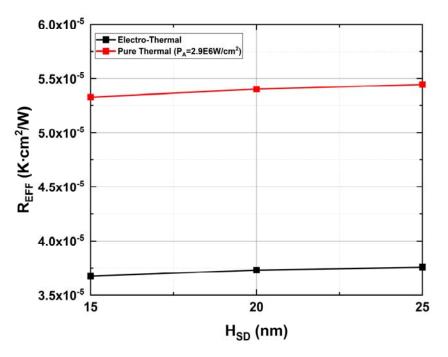

In a 6-T SRAM, each bit cell comprises 6 transistors: (1) 2 pull-down (PD) n-channel and 2 pull-up (PU) p-channel transistors to form a pair of cross-coupled inverters, and (2) 2 pass-gate (PG) n-channel transistors to enable read and write access to the cross-coupled inverters. Figure 3.3-2 shows the schematic of a conventional 6-T SRAM bit cell. Information is stored at the output of the inverters (CL and CH).