## Monolithic Wireless Transceiver Design

*Filip Maksimovic Kristofer Pister, Ed. Ali Niknejad, Ed.*

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2020-33 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2020/EECS-2020-33.html

May 1, 2020

Copyright © 2020, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Monolithic Wireless Transceiver Design

by

Filip Maksimovic

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Science

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Kristofer S.J. Pister, Chair Professor Ali M. Niknejad Professor Stephen D. Glaser

Fall 2018

The dissertation of Filip Maksimovic, titled Monolithic Wireless Transceiver Design, is approved:

| Chair | <br>Date |  |

|-------|----------|--|

|       | <br>Date |  |

|       | <br>Date |  |

University of California, Berkeley

## Monolithic Wireless Transceiver Design

Copyright 2018 by Filip Maksimovic

#### Abstract

#### Monolithic Wireless Transceiver Design

by

Filip Maksimovic

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Science

University of California, Berkeley

Professor Kristofer S.J. Pister, Chair

Recently, there has been an increasing push to make everything wireless. In contrast to high-performance cellular communication, where the demand for enormous quantities of data is skyrocketing, these small wireless sensor and actuator nodes require low power, low cost, and a high degree of system integration. A typical CMOS system-on-chip requires a number of off-chip components for proper operation, namely, a crystal oscillator to act as an accurate frequency reference, and an antenna. The primary goal of this thesis is to address the hurdles associated with operating without these components at as low a power level as possible. This is a step towards the ubiquitous presence of wireless communication.

In this work, an evaluation of transceiver performance is performed with power, performance, and physical size in mind. Operation of a low-power standards compatible 2.4 GHz transmitter (TX) is demonstrated without the use of an off-chip frequency reference. These 2.4 GHz transceivers (TRX), called the single chip motes, operate at low power levels without an off-chip frequency reference. The first single chip mote demonstrated RF chip-to-chip communication in the presence of local oscillator drift caused by temperature variation. It used a free-running LC tank oscillator that was calibrated against drift with periodic network traffic. The next single chip mote was a 2.4 GHz, 802.15.4 TRX, BLE advertising TX system-on-chip with integrated digital baseband and a Cortex M0. Once again, the chip uses no off-chip frequency reference. Finally, a design of high frequency transceiver with integrated antenna is presented, paving the way for a fully on-chip solution.

To no one in particular

# Contents

| Co       | onten | ts                                              | ii |

|----------|-------|-------------------------------------------------|----|

| Li       | st of | Figures                                         | v  |

| Li       | st of | Tables                                          | x  |

| 1        | Intr  | oduction                                        | 1  |

|          | 1.1   | Wireless Communication in the $21^{st}$ Century | 1  |

|          | 1.2   | Radio Miniaturization                           | 2  |

|          | 1.3   | Wireless Standards                              | 3  |

|          |       | Bluetooth Low Energy                            | 4  |

|          |       | 802.15.4, OpenWSN                               | 5  |

|          |       | WiFi                                            | 6  |

|          | 1.4   | A Typical Mote                                  | 6  |

|          |       | Timing and Frequency Specificity                | 7  |

|          |       | Power                                           | 8  |

|          |       | Antenna                                         | 8  |

|          | 1.5   | Thesis Organization                             | 9  |

| <b>2</b> | On-   | chip Frequency Synthesis                        | 11 |

|          | 2.1   | Receiver and Transmitter Architectures          | 11 |

|          |       | Resonant Oscillator Basics                      | 11 |

|          |       | Phase Noise                                     | 13 |

|          | 2.2   | Passive Design                                  | 14 |

|          |       | Inductors                                       | 14 |

|          |       | Capacitive Tuning                               | 16 |

|          | 2.3   | LC Tank Oscillator Topologies                   | 16 |

|          |       | Topology Overview                               | 18 |

|          |       | Tuning Resolution                               | 21 |

|          |       | Phase Noise                                     | 23 |

|          |       | Supply Noise                                    | 26 |

|          |       | Implications for LDO design                     | 29 |

|          | 2.4                | IQ Synthesis                                                                                                                                      |

|----------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                    | Integer Dividers                                                                                                                                  |

|          |                    | A Brief Comment on PLLs and FLLs                                                                                                                  |

| ი        | These              | 20                                                                                                                                                |

| 3        | <b>1 ra</b><br>3.1 | nsmitters 36<br>Matching Networks                                                                                                                 |

|          |                    | 0                                                                                                                                                 |

|          | 3.2                | 1 1 0                                                                                                                                             |

|          |                    |                                                                                                                                                   |

|          | กก                 | Class D and E                                                                                                                                     |

|          | 3.3                | Switching Transients                                                                                                                              |

| 4        | The                | Single Chip Mote v1 44                                                                                                                            |

|          | 4.1                | Chip Overview                                                                                                                                     |

|          |                    | Local Oscillator Design and Measurements                                                                                                          |

|          |                    | Temperature Compensation                                                                                                                          |

|          |                    | Test Setup $\ldots \ldots \ldots$ |

|          | 4.2                | The Single Chip Mote v2                                                                                                                           |

|          |                    |                                                                                                                                                   |

| <b>5</b> |                    | Single Chip Mote v356                                                                                                                             |

|          | 5.1                | Chip Overview                                                                                                                                     |

|          | 5.2                | Supply Conditioning and Bias Generation                                                                                                           |

|          |                    | Bias generation                                                                                                                                   |

|          |                    | LDO design 64                                                                                                                                     |

|          | 5.3                | Local Oscillator                                                                                                                                  |

|          |                    | Tuning and Modulation Tone Spacing    68                                                                                                          |

|          |                    | Polyphase Filter                                                                                                                                  |

|          |                    | Phase Noise         71                                                                                                                            |

|          | 5.4                | Power Amplifier and RF Modulation                                                                                                                 |

|          |                    | Matching Network                                                                                                                                  |

|          |                    | Power Amplifier                                                                                                                                   |

|          |                    | Efficiency                                                                                                                                        |

|          | 5.5                | Divider                                                                                                                                           |

|          |                    | Tunable Dynamic Pre-Scaler    80                                                                                                                  |

|          | 5.6                | Local Oscillator Calibration                                                                                                                      |

|          |                    | Tuning                                                                                                                                            |

|          |                    | Monotonic Tuning Characteristic                                                                                                                   |

|          |                    | Process, Voltage, and Temperature                                                                                                                 |

|          |                    | Two-point Calibration                                                                                                                             |

|          |                    | Temperature Calibration                                                                                                                           |

|          |                    | Calibration in an 802.15.4 Network                                                                                                                |

|          | 5.7                | System Demonstrations                                                                                                                             |

|          |                    | Bluetooth Low Energy                                                                                                                              |

|          |                    |                                                                                                                                                   |

|    |       | Antenna considerations           | 92              |

|----|-------|----------------------------------|-----------------|

| 6  | Mo    | nolithic Transceiver Integration | 96              |

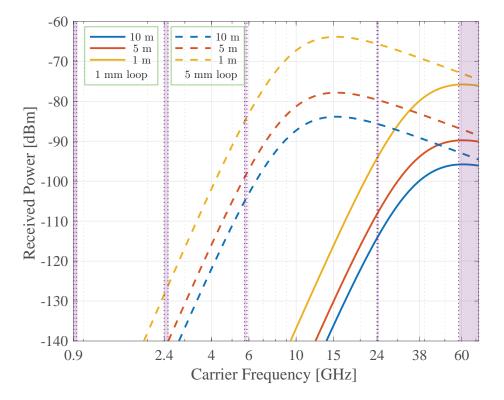

|    | 6.1   | Selection of Carrier Frequency   | 96              |

|    | 6.2   | Antenna Design                   | 01              |

|    | 6.3   | Transceiver Design               | 02              |

|    |       | System Architecture              | 02              |

|    |       | Transmitter                      | 03              |

|    |       | Receiver                         | 04              |

|    |       | RX-TX co-integration             | 05              |

|    | 6.4   | Measured Results                 | 06              |

| 7  | Con   | clusions and Future Work 1       | 09              |

| •  | 7.1   |                                  | 09              |

|    | 7.2   |                                  | 09              |

|    |       |                                  | 09              |

|    |       |                                  | 10              |

|    |       |                                  | 10              |

|    | 7.3   |                                  | 11              |

| Bi | bliog |                                  | 13              |

| ٨  | SCI   | A v3 Documentation 1             | 22              |

| A  |       |                                  | <b>44</b><br>22 |

|    | A.1   |                                  | 22<br>24        |

|    | A.2   |                                  |                 |

|    | A.3   |                                  | 25              |

|    | A.4   |                                  | 27              |

|    | A.5   |                                  | 28              |

|    |       |                                  | 28              |

|    |       |                                  | 29              |

|    |       | Transmit Mode - BLE              | 29              |

iv

# List of Figures

| 1.1  | An illustration demonstrating various communication modalities for wireless sensor deployments                                                                                                                                                                                                                       | 2          |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.2  | The OpenWSN stack [15]. As long as the wireless transceiver adheres to the requirements set by the 802.15.4e standard, and as long as on-chip digital hardware is capable of running the MAC and protocol layer packet assembly (TX) and disassembly (RX) and the scheduling, the device can operate in an internet- |            |

| 10   | connected wireless sensor network                                                                                                                                                                                                                                                                                    | 4          |

| 1.3  | Board-level implementations of wireless communication nodes. Left is [22] a typ-<br>ical commercial wireless node. Right is [23] the smallest wireless node in research                                                                                                                                              | 7          |

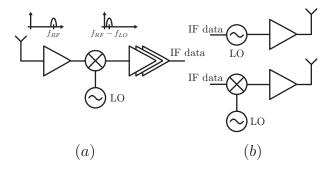

| 2.1  | Block diagram of Armstrong's super-heterodyne receiver (a) a direct modulation<br>and upconversion transmitter (b)                                                                                                                                                                                                   | 12         |

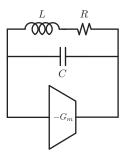

| 2.2  | Simple circuit of a LC tank oscillator. The $R$ represents the total series loss of the magnetic component. Capacitive losses are not shown because capacitor loss is significantly lower than inductor loss with on-chip components at frequencies                                                                  | 14         |

|      | below $\tilde{10}$ GHz (this number is an<br>ecdotal and process dependent)                                                                                                                                                                                                                                          | 12         |

| 2.3  | Phase noise in oscillators                                                                                                                                                                                                                                                                                           | 13         |

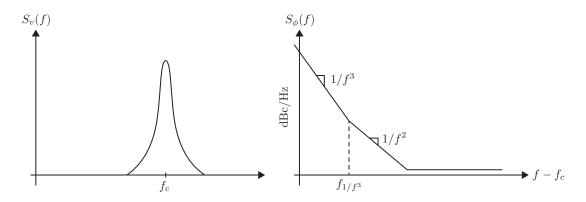

| 2.4  | Examples of on-chip inductors and a simple equivalent circuit model [33]                                                                                                                                                                                                                                             | 15         |

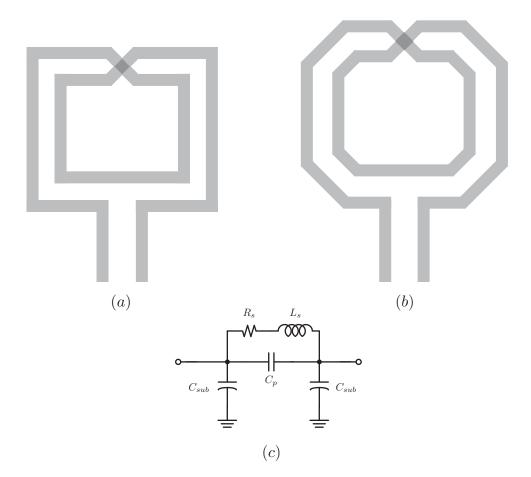

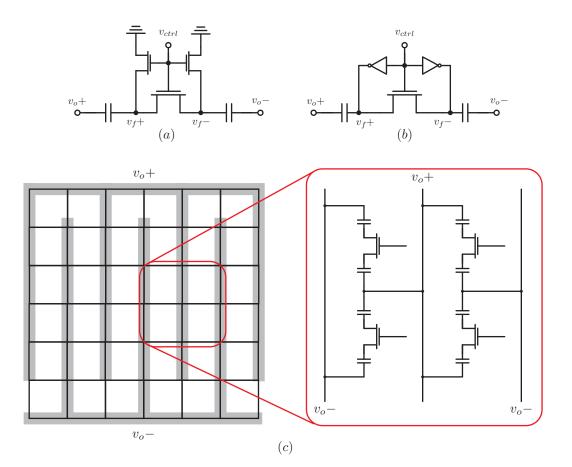

| 2.5  | Capacitor tuning in an LC tank oscillator. (a) Shows an appropriate way to bias                                                                                                                                                                                                                                      |            |

|      | the floating node to prevent $v_f$ from swinging low enough to turn off the pass                                                                                                                                                                                                                                     |            |

|      | device when its gate is high. (b) Shows a similar technique that also prevents                                                                                                                                                                                                                                       |            |

|      | the pass device from being turned on while its gate is low. (c) Shows a common                                                                                                                                                                                                                                       | . –        |

|      | method to lay out a capacitive DAC                                                                                                                                                                                                                                                                                   | 17         |

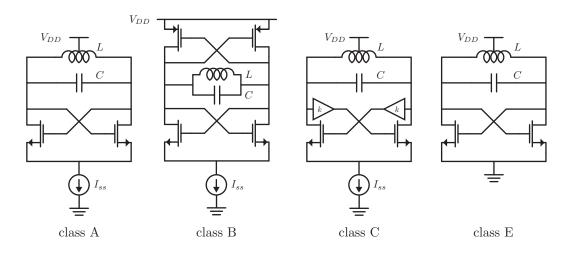

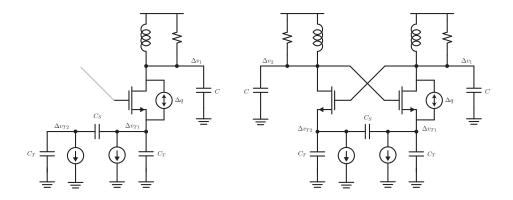

| 2.6  | Four oscillator topologies                                                                                                                                                                                                                                                                                           | 18         |

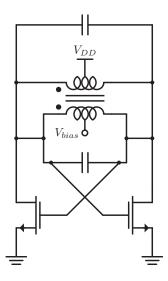

| 2.7  | Class F style oscillator with transformer boosting of loop gain                                                                                                                                                                                                                                                      | 21         |

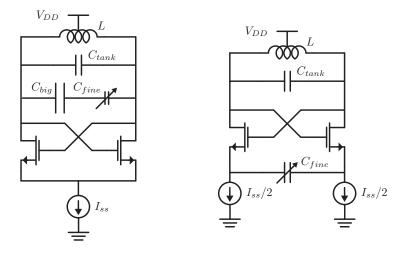

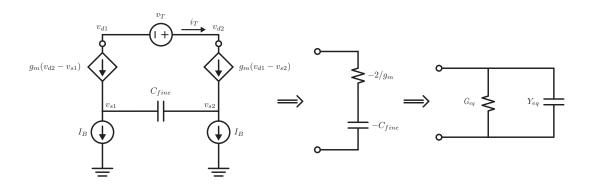

| 2.8  | Two strategies for fine frequency tuning                                                                                                                                                                                                                                                                             | 22         |

| 2.9  | Equivalent circuit for the degenerated capacitor technique                                                                                                                                                                                                                                                           | 22         |

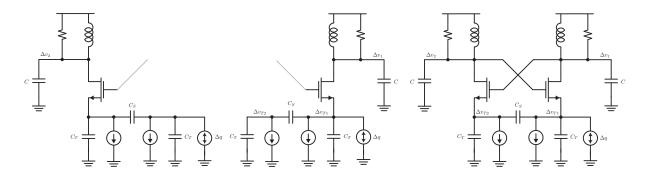

| 2.10 | Effective circuits in various oscillator operating regions for calculating phase noise                                                                                                                                                                                                                               | 2.4        |

| 0.11 | from one negative $g_m$ device                                                                                                                                                                                                                                                                                       | 24         |

| 2.11 | Effective circuits in various oscillator operating regions for calculating phase noise                                                                                                                                                                                                                               | <u>م</u> ۲ |

|      | from the tail current source                                                                                                                                                                                                                                                                                         | 25         |

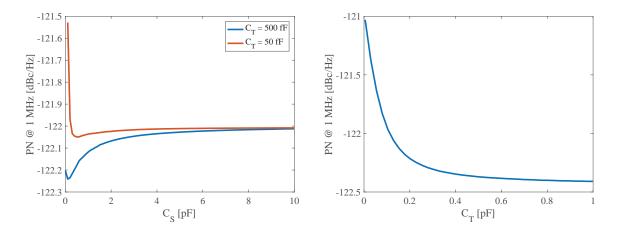

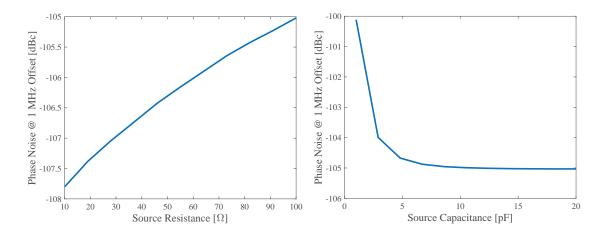

| 2.12 | Phase noise at 1 MHz from carrier with varying tail capacitance and degenerated source capacitance                                                                  | 26              |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

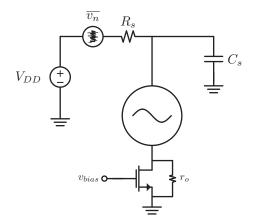

|      | High-level schematic of supply noise simulation $\dots \dots \dots$ | $\frac{20}{27}$ |

| 2.14 | and source capacitance (right) in a class-A NMOS LC tank oscillator                                                                                                 | 27              |

| 2.15 | Influence of a fixed 500 k $\Omega$ noise resistance with varying source resistance (left) and source capacitance (right) in a class-B CMOS LC tank oscillator      | 28              |

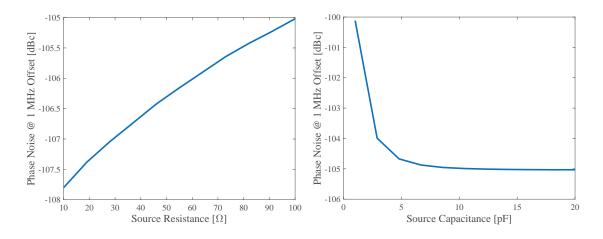

| 2.16 | Phase noise degradation of a class-E oscillator with varying quantities of supply noise                                                                             | 29              |

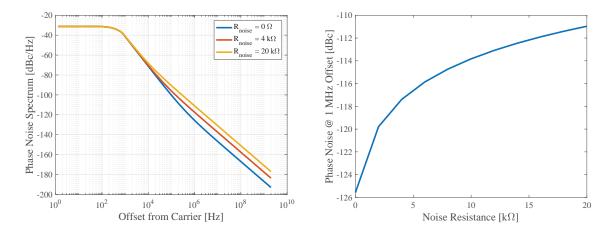

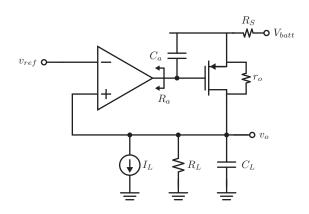

| 2.17 | A typical LDO schematic used to derive line regulation, load regulation, and stablity criteria                                                                      | -•<br>29        |

| 2.18 | Impact of LDO amplifier noise on class-B oscillator phase noise                                                                                                     | $\frac{20}{32}$ |

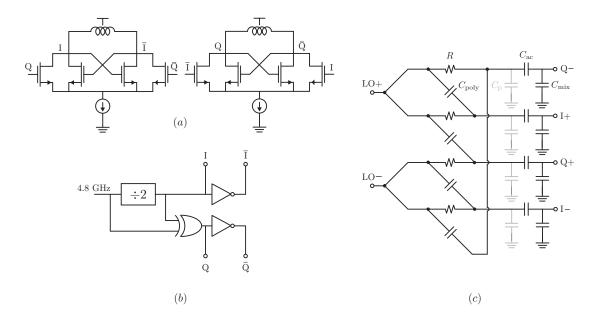

|      | Various techniques for generating in-phase and quadrature oscillation                                                                                               | 33              |

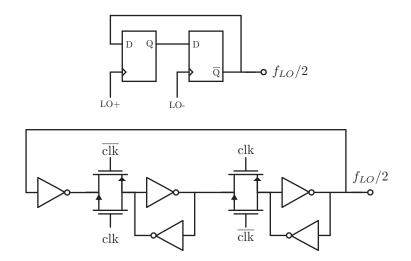

|      | Latch-based frequency divider and traditional CMOS implementation                                                                                                   | 34              |

|      | Faster divider topologies                                                                                                                                           | 35              |

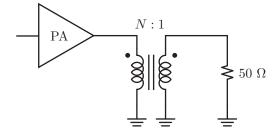

| 3.1  | A generic amplifier and broadband matching network. The transformer steps                                                                                           |                 |

|      | down the voltage for low power operation, making the load impedance seen by<br>the PA larger                                                                        | 37              |

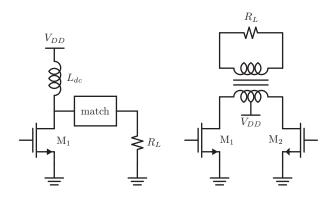

| 3.2  | Class A and B linear power amplifiers                                                                                                                               | 38              |

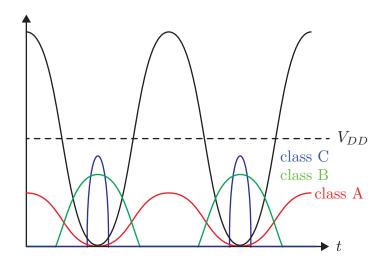

| 3.3  | Transistor drain waveforms. The voltage waveform is in black, and the current                                                                                       |                 |

|      | waveforms are colored and correspond to the three different power amplifiers                                                                                        | 39              |

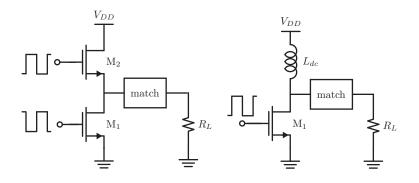

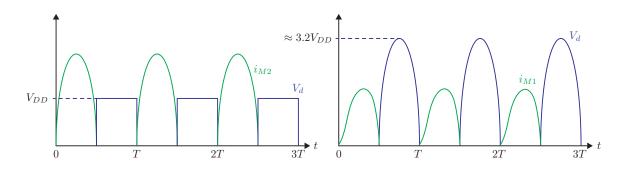

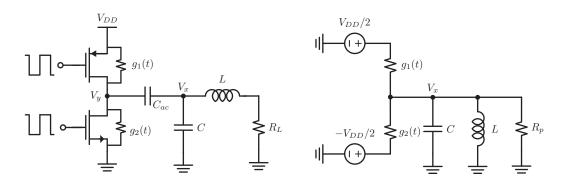

| 3.4  | Schematics of the class D (left) and class E (right) power amplifiers                                                                                               | 40              |

| 3.5  | Ideal class D (left) and class E (right) waveforms                                                                                                                  | 40              |

| 3.6  | Schematic of Class D power amplifier with annotated switch conductances (left)                                                                                      |                 |

|      | and Thevenin equivalent model (right)                                                                                                                               | 41              |

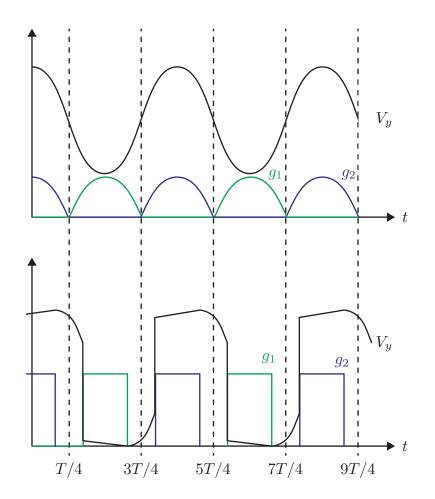

| 3.7  | "Class D" waveforms with weak sinusoidal drive and low duty-cycle drive. The                                                                                        |                 |

|      | lack of inductor to maintain a fixed current results in undesirable performance                                                                                     |                 |

|      | both when the gates are resonant-driven (top) and square-driven with reduced                                                                                        |                 |

|      | duty cycle (bottom).                                                                                                                                                | 42              |

| 4.1  | Single Chip Mote v1 Block Diagram                                                                                                                                   | 45              |

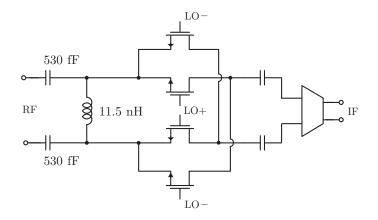

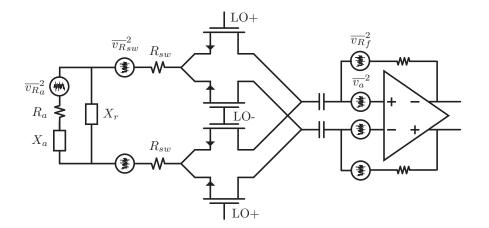

| 4.2  | Single Chip Mote v1 Mixer-First Receiver                                                                                                                            | 46              |

| 4.3  | Single Chip Mote v1 Class-D Power Amplifier                                                                                                                         | 46              |

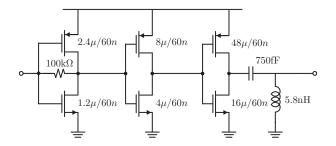

| 4.4  | Overview of the Single Chip Mote v1's digitally controlled oscillator                                                                                               | 47              |

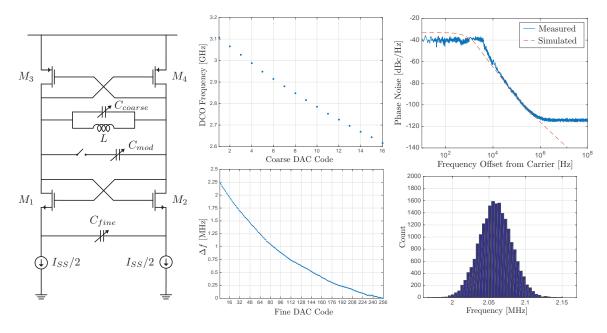

| 4.5  | Single Chip Mote v1 transmitter performance. The transmitter EVM is 3.4%.                                                                                           |                 |

|      | The required transmitter EVM for $802.15.4$ is $35\%$                                                                                                               | 47              |

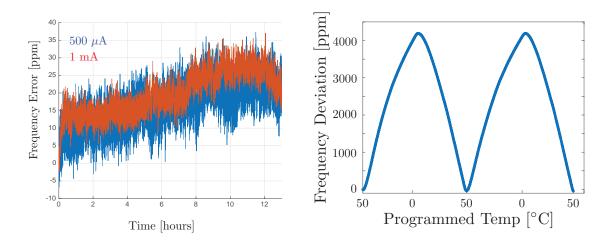

| 4.6  | Variation in the Single Chip Mote v1's oscillator frequency in a temperature                                                                                        |                 |

|      | controlled environment (left) and in a programmed temperature chamber (right)                                                                                       | 48              |

| 4.7  | Variation in the Single Chip Mote v1's oscillator frequency in a temperature                                                                                        |                 |

|      | controlled environment (left) and in a programmed temperature chamber (right)                                                                                       | 49              |

vi

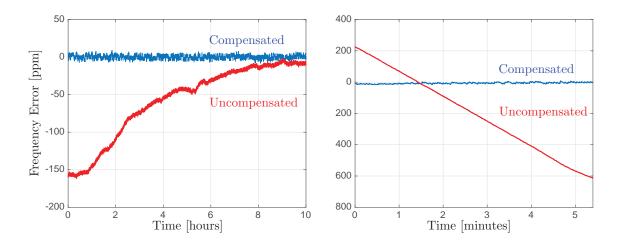

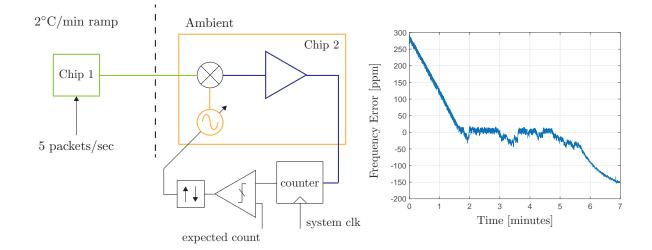

| 4.8         | Block diagram of packet-level temperature compensation (left) and resulting receiver frequency error (right)                                                                                                                                                                                              | 50         |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

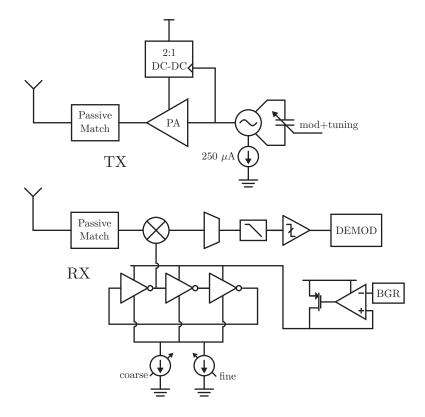

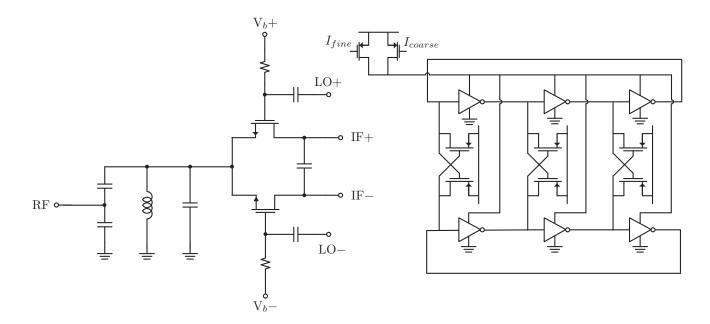

| 4.9         | Top-level schematic of the SCM v2 TRX                                                                                                                                                                                                                                                                     | $50 \\ 52$ |

| 4.10        |                                                                                                                                                                                                                                                                                                           | $52 \\ 53$ |

| 4.11        | Detailed schematic of SCM v2 front-end and oscinator $\dots \dots \dots$                                                                                                                                  | 54<br>55   |

| 1.12        |                                                                                                                                                                                                                                                                                                           | 00         |

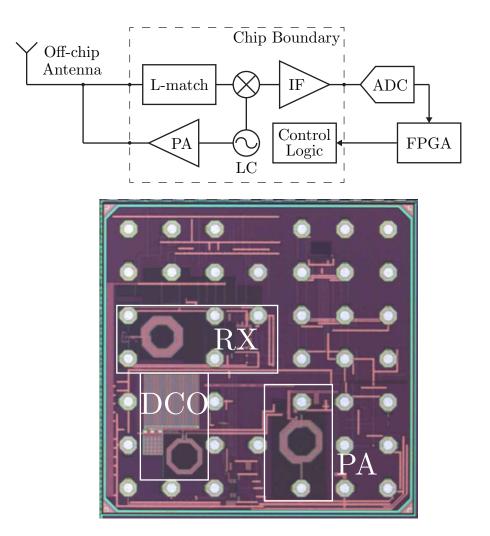

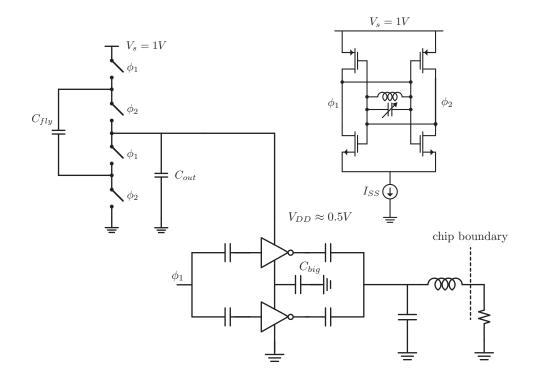

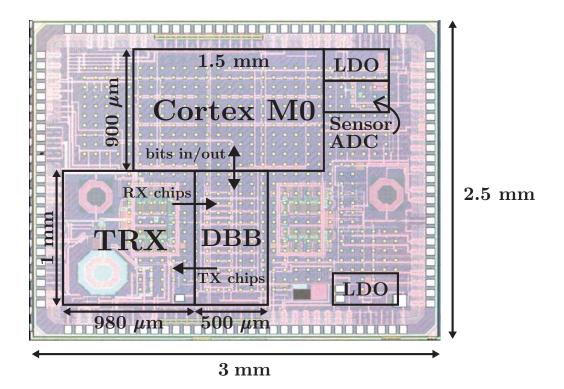

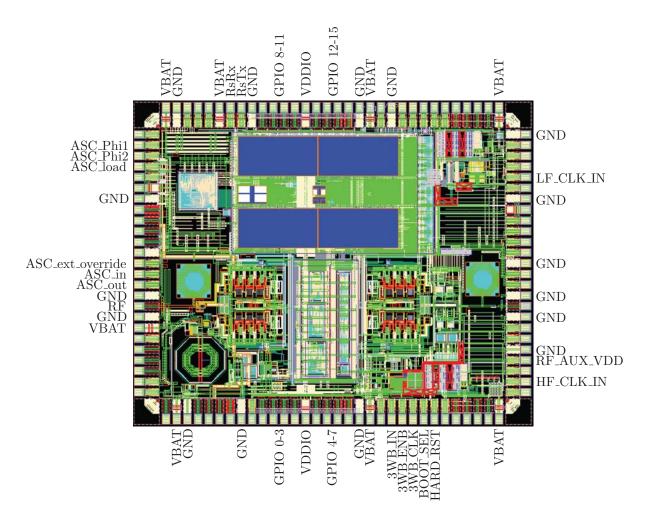

| 5.1         | Annotated SCM v3 die photo. The entire chip was 7.5 mm <sup>2</sup> . The transceiver active area was approximately 0.98 mm <sup>2</sup> . The total active area (counting LDO decoupling capacitance, but not global supply decoupling capacitance or sensor ADC) was approximately 3.06 mm <sup>2</sup> | 57         |

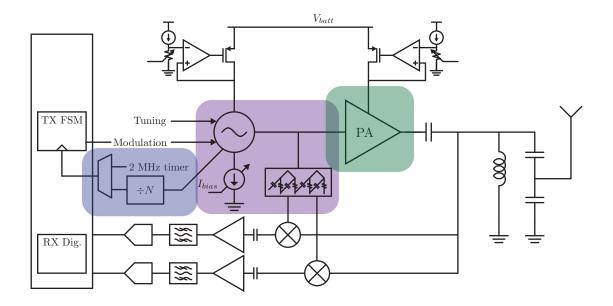

| 5.2         | Block diagram of the transceiver                                                                                                                                                                                                                                                                          | 58         |

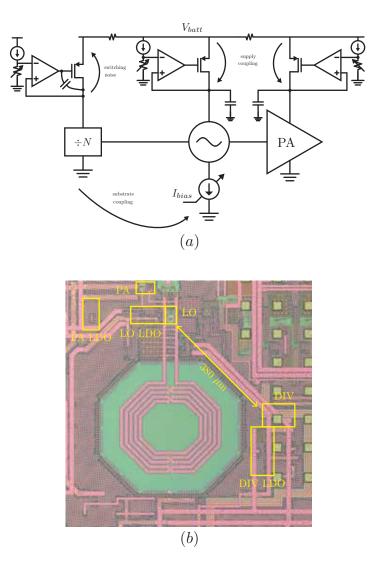

| 5.3         | Power supply network showing the most likely sources of coupling (a) and the                                                                                                                                                                                                                              |            |

|             | physical layout of the transmitter (b) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                   | 59         |

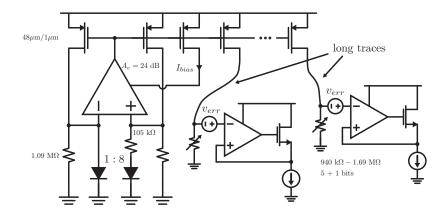

| 5.4         | Reference routing network. The bias current for the band gap generator amplifier                                                                                                                                                                                                                          |            |

|             | is mirrored from the mirrored PMOS current (shown in the figure as $I_{bias}$ )                                                                                                                                                                                                                           | 60         |

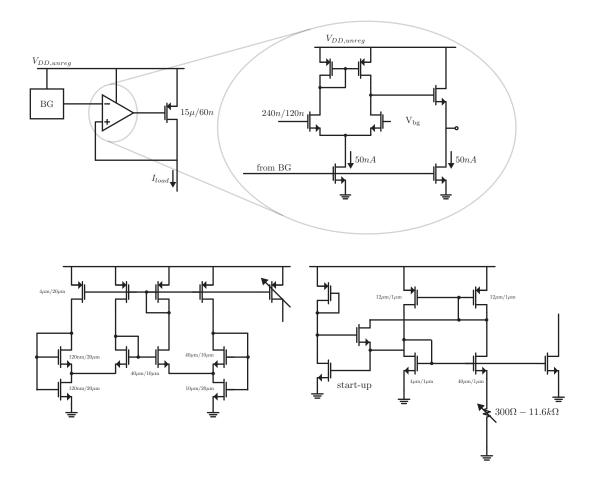

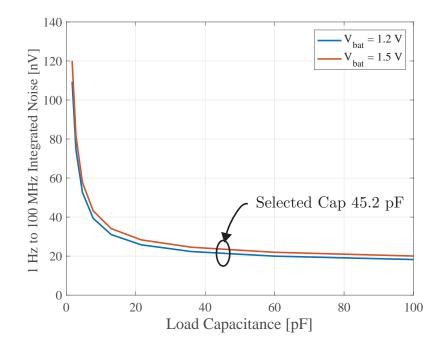

| 5.5         | Band gap reference noise/area tradeoff                                                                                                                                                                                                                                                                    | 61         |

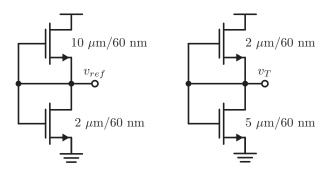

| 5.6         | Schematic of temperature invariant $v_{ref}$ and PTAT $v_T$ circuits with annotated                                                                                                                                                                                                                       | co         |

| 5.7         | transistor dimensions                                                                                                                                                                                                                                                                                     | 62         |

| •           | mV to 850 mV (in 5 mV steps) and with $\pm 10$ mV of threshold mismatch                                                                                                                                                                                                                                   | 63         |

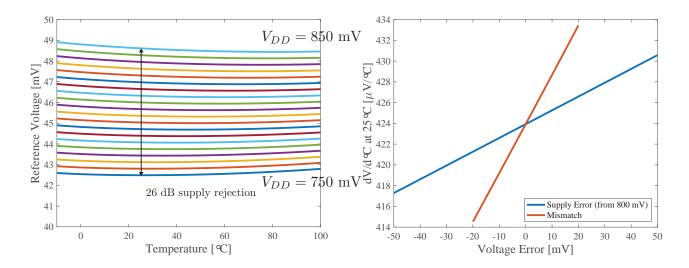

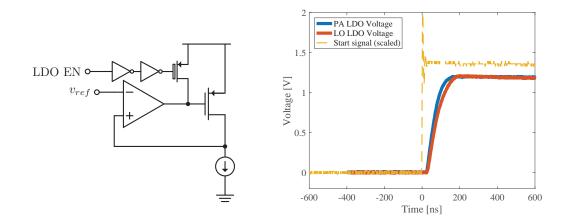

| 5.8         | Local oscillator LDO and current source startup transients - the LO and PA are                                                                                                                                                                                                                            | co         |

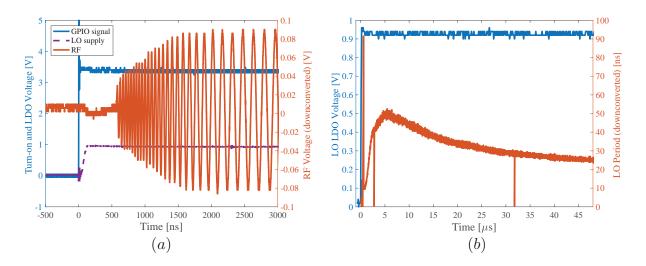

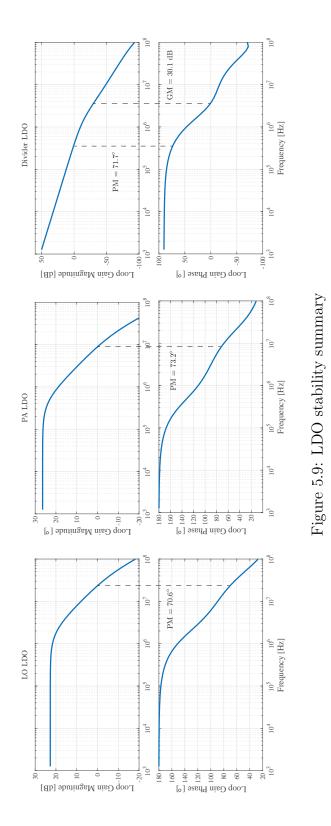

| 5.0         | cold-started at $t = 0$ to 800 mV settings                                                                                                                                                                                                                                                                | 63<br>66   |

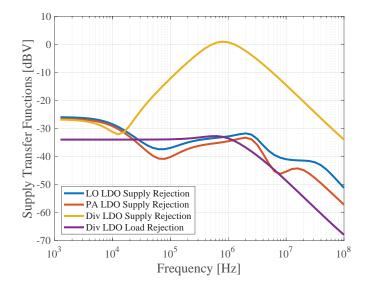

| 5.9<br>5.10 | LDO stability summary                                                                                                                                                                                                                                                                                     | 66<br>67   |

| 5.11        |                                                                                                                                                                                                                                                                                                           | 07         |

| 0.11        | signal that pulls the LDO pass device gate to the source also disables the LDO                                                                                                                                                                                                                            |            |

|             | amplifier's bias                                                                                                                                                                                                                                                                                          | 67         |

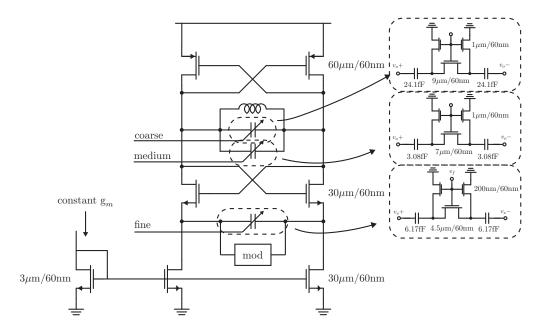

| 5.12        | Local Oscillator Schematic                                                                                                                                                                                                                                                                                | 68         |

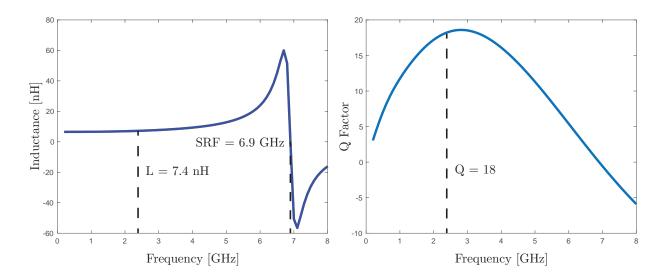

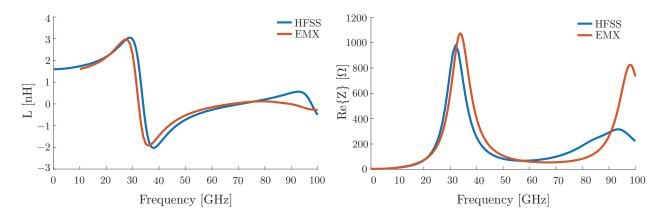

|             | Simulated inductance and Q of LO inductor. Simulation was performed using                                                                                                                                                                                                                                 |            |

|             | Integrand EMX                                                                                                                                                                                                                                                                                             | 69         |

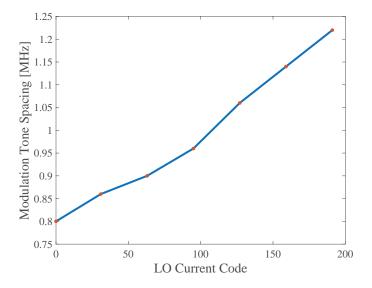

| 5.14        | Tone spacing vs. current code for 802.15.4 modulation. The current varies from                                                                                                                                                                                                                            |            |

|             | 170 $\mu$ A to 850 $\mu$ A over this range                                                                                                                                                                                                                                                                | 70         |

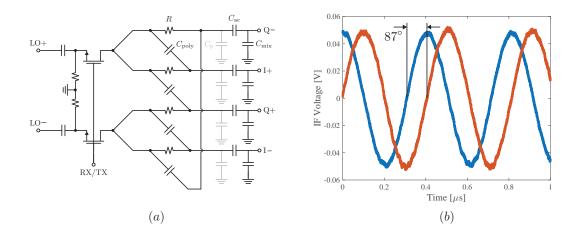

| 5.15        | Polyphase filter schematic and measured downconverted phase error                                                                                                                                                                                                                                         | 71         |

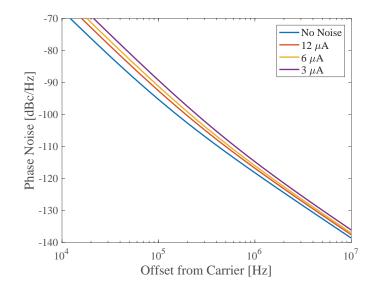

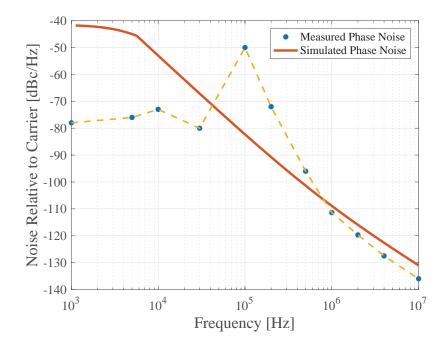

|             | Measured and simulated LO phase noise (need to re-take this data) $\ldots$ .                                                                                                                                                                                                                              | 72         |

|             | Radio Front-End Schematic                                                                                                                                                                                                                                                                                 | 73         |

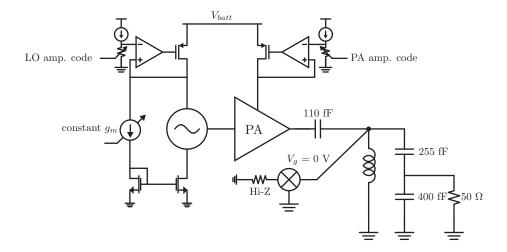

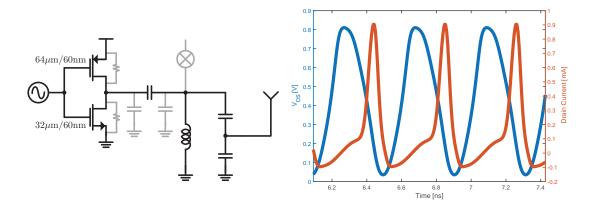

| 5.18        | PA schematic (sources of efficiency loss shown in grey) and simulated transient drain voltage and drain current of the NMOS device                                                                                                                                                                        | 74         |

|   | ٠ | • | ٠ |

|---|---|---|---|

| V | 1 | 1 | 1 |

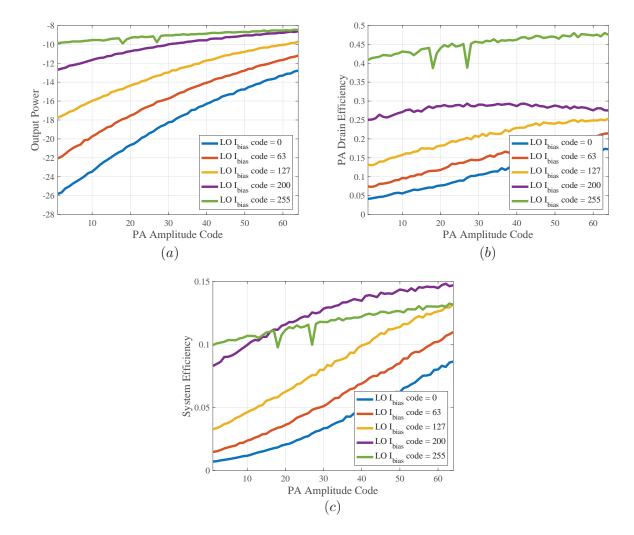

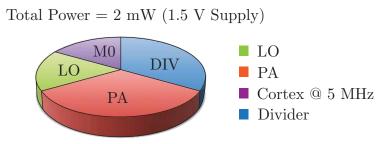

|      | Measured PA output power, PA drain efficiency, and TX system efficiency $\ldots$ .<br>Measured $2^{nd}$ and $3^{rd}$ order harmonic distortion at varying LO swing levels at (a)                                                                                                                                                                                                                                                    | 75  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | 750 mV LO supply and (b) 900 mV LO supply                                                                                                                                                                                                                                                                                                                                                                                           | 76  |

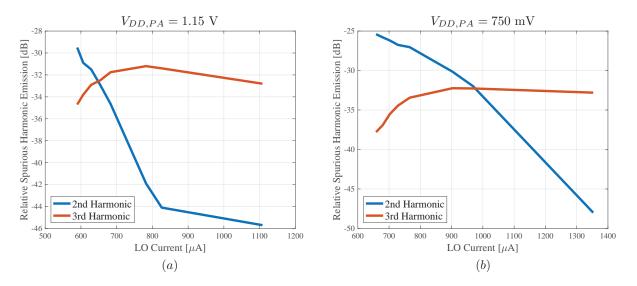

| 5.21 | Measured power consumption                                                                                                                                                                                                                                                                                                                                                                                                          | 76  |

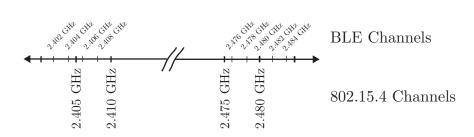

| 5.22 | BLE and 802.15.4 channel frequencies                                                                                                                                                                                                                                                                                                                                                                                                | 79  |

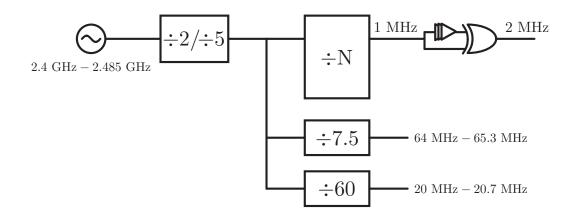

|      | Top-level divider block diagram                                                                                                                                                                                                                                                                                                                                                                                                     | 79  |

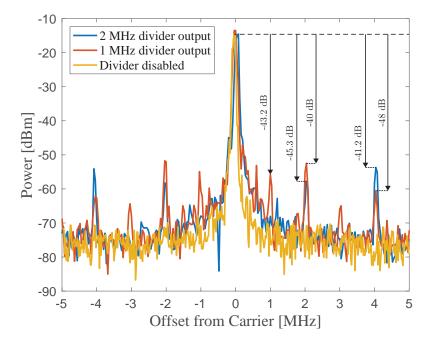

|      | Measured output spectra with dividers running                                                                                                                                                                                                                                                                                                                                                                                       | 80  |

|      | Divider pre-scaler schematics. (a) Shows a static divide-by-2 circuit using a flip<br>flop. (b) Shows a static divide-by-5 circuit using flip flops and combinational<br>logic. (c) Shows an intentionally slowed injection-locked divider. The tail current<br>dictates how much charge is removed from the output capacitor, which sets the<br>frequency divide ratio. It works a bit like a resetting charge-domain counter. (d) |     |

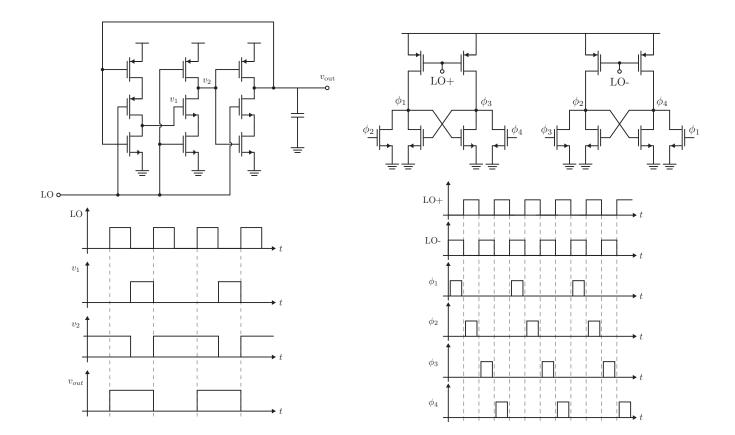

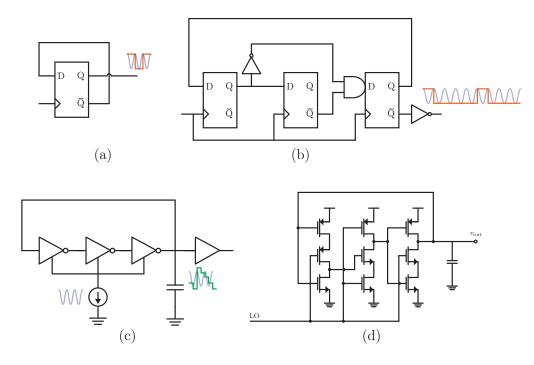

|      | Shows the transistor-level implementation of the "charge counter" from (c)                                                                                                                                                                                                                                                                                                                                                          | 81  |

| 5.26 |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 82  |

| 5.27 |                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

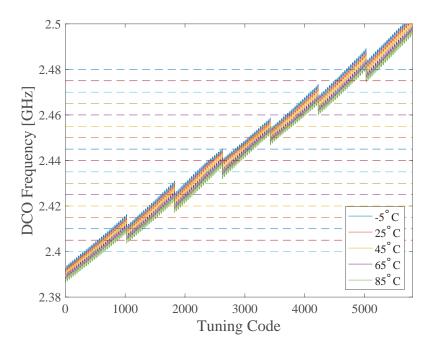

|      | zontal lines indicate 802.15.4 channel frequencies                                                                                                                                                                                                                                                                                                                                                                                  | 83  |

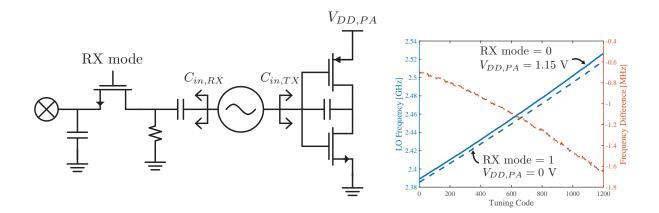

| 5.28 | Effects of receiver and transmitter load pulling on TX and RX DCO tuning                                                                                                                                                                                                                                                                                                                                                            |     |

|      | characteristics. These are static frequency offsets caused by nonlinear amplitude-                                                                                                                                                                                                                                                                                                                                                  |     |

|      | dependent capacitances. Large RF signals at the antenna port cause injection                                                                                                                                                                                                                                                                                                                                                        |     |

|      | pulling (at around -30 dBm) and injection locking (at around -20 dBm)                                                                                                                                                                                                                                                                                                                                                               | 86  |

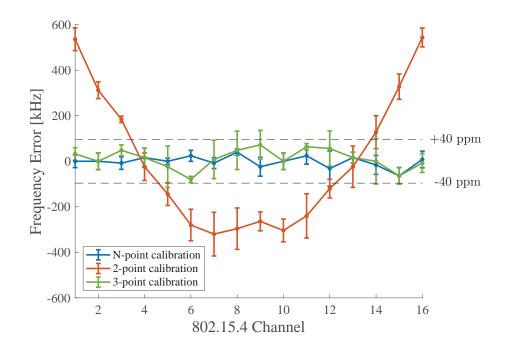

| 5.29 | Frequency error at 802.15.4 channels with various calibration techniques                                                                                                                                                                                                                                                                                                                                                            | 87  |

|      | Open-loop oscillator frequency on the lab bench (a) and with varying temperature                                                                                                                                                                                                                                                                                                                                                    |     |

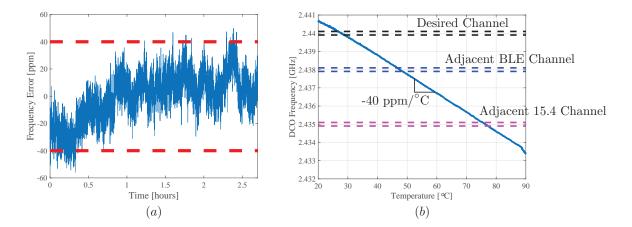

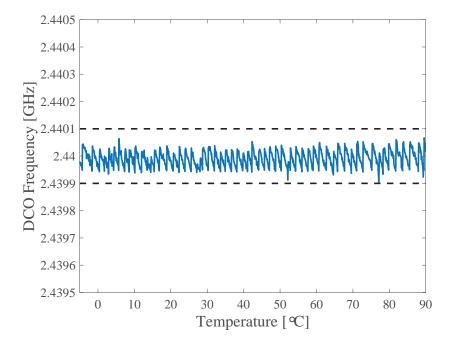

|      | $(b) \ldots \ldots$                                                                                                                                                                                                                                                                                          | 88  |

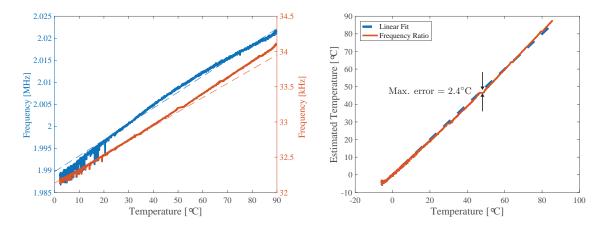

| 5.31 | Low frequency temperature response of the on-chip 32 kHz and 2 MHz oscillators and a linear fit of their ratio                                                                                                                                                                                                                                                                                                                      | 88  |

| 5.32 | Results of idealized calibration conditions                                                                                                                                                                                                                                                                                                                                                                                         | 89  |

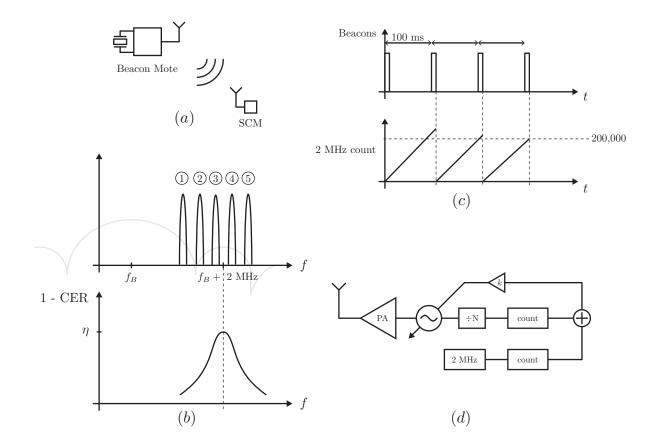

|      | Illustration of potential network calibration strategy                                                                                                                                                                                                                                                                                                                                                                              | 90  |

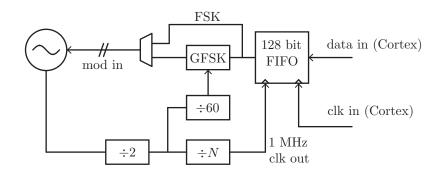

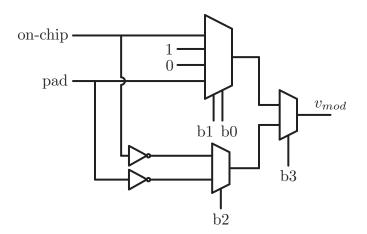

|      | On-chip BLE modulation schematic                                                                                                                                                                                                                                                                                                                                                                                                    | 91  |

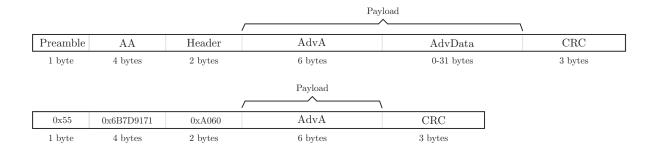

|      | Bluetooth Low-Energy general advertising packet structure (top) and minimum-                                                                                                                                                                                                                                                                                                                                                        | 01  |

| 0.00 | number-of-bits packet structure (bottom)                                                                                                                                                                                                                                                                                                                                                                                            | 92  |

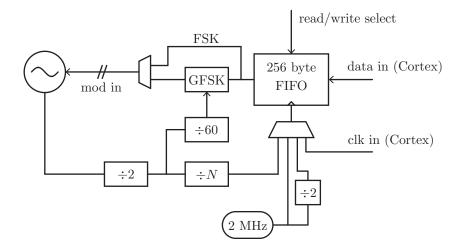

| 5.36 | Off-chip BLE modulation schematic. In this diagram, only the FIFO itself is off                                                                                                                                                                                                                                                                                                                                                     |     |

| 0.00 | chip. All clocks and control signals are generated on chip                                                                                                                                                                                                                                                                                                                                                                          | 93  |

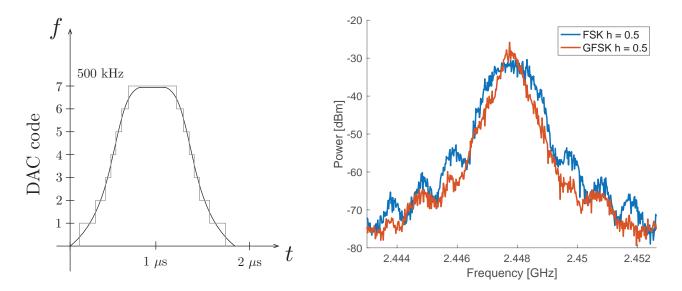

| 5.37 |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00  |

| 0.01 | rate of 1 Mbps, with both generic FSK and Gaussian FSK                                                                                                                                                                                                                                                                                                                                                                              | 94  |

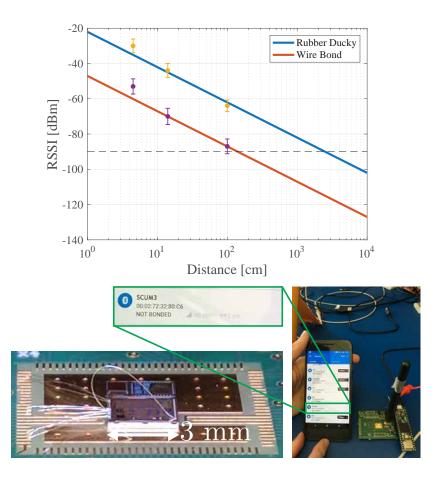

| 5.38 |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 01  |

| 0.00 | stration of BLE advertising capability                                                                                                                                                                                                                                                                                                                                                                                              | 95  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                     | 00  |

| 6.1  | Illustration of Link Budget                                                                                                                                                                                                                                                                                                                                                                                                         | 97  |

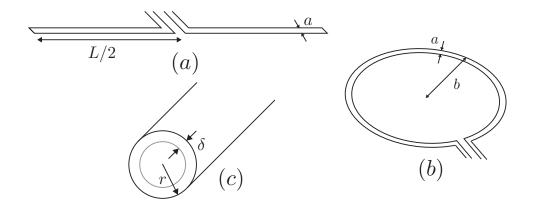

| 6.2  | Antenna dimensions for (a) a dipole and (b) a loop; and (c) the cross-section of                                                                                                                                                                                                                                                                                                                                                    |     |

|      | the antenna conductor                                                                                                                                                                                                                                                                                                                                                                                                               | 98  |

| 6.3  | Received power in the symmetrical link                                                                                                                                                                                                                                                                                                                                                                                              | 99  |

| 6.4  | Simulated antenna performance                                                                                                                                                                                                                                                                                                                                                                                                       | 101 |

| 6.5  | Simulated antenna performance                                                                                                                  | 102 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

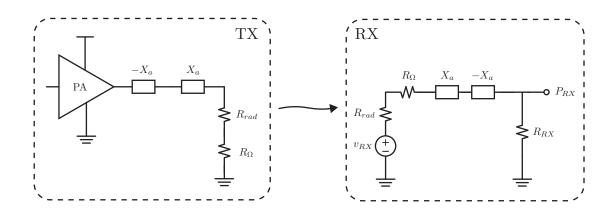

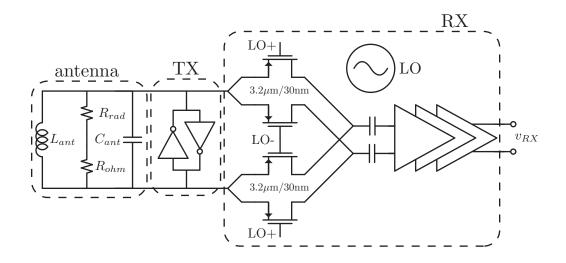

| 6.6  | 24 GHz transceiver schematic with shared antenna interface. $R_{rad}$ and $R_{ohm}$ are                                                        |     |

|      | transformed parallel resistances.                                                                                                              | 103 |

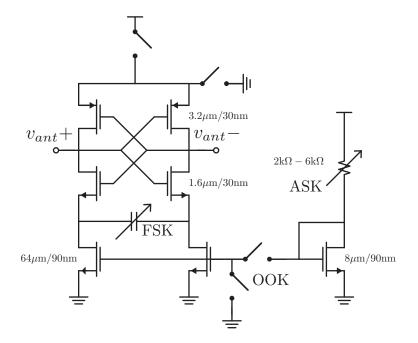

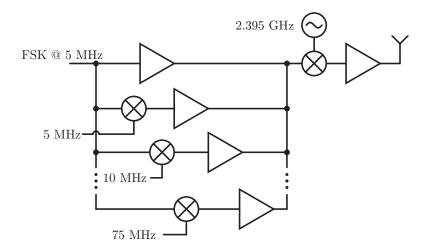

| 6.7  | Transmitter schematic (antenna not shown) with annotated modulation                                                                            | 104 |

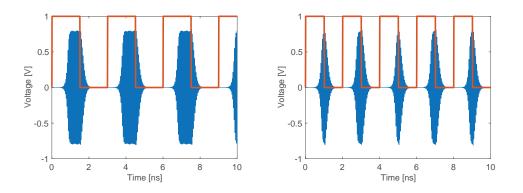

| 6.8  | Simulated OOK modulation of the transmitter at 667 Mbps (left) and 1 Gbps                                                                      |     |

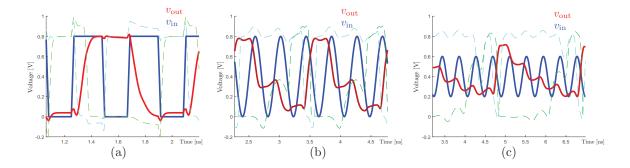

|      | $(right) \ldots \ldots$ | 104 |

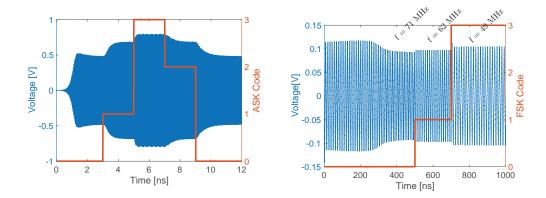

| 6.9  | Simulated ASK (left) and FSK (right) modulation of the transmitter. The FSK                                                                    |     |

|      | shows the output of the mixer in a loop-back test                                                                                              | 105 |

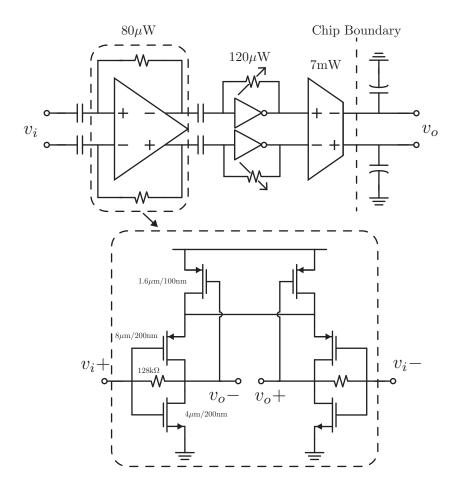

| 6.10 | Baseband stage schematics and estimated power consumption                                                                                      | 106 |

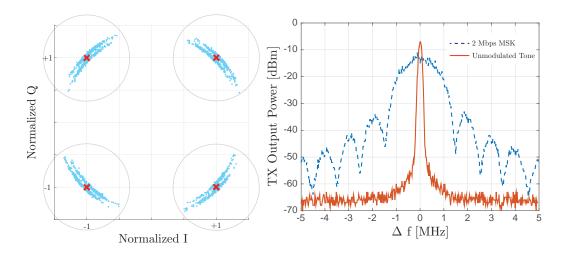

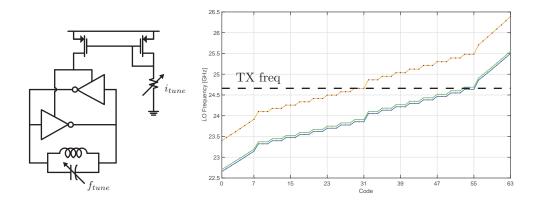

| 6.11 | Local oscillator and tuning characteristic                                                                                                     | 107 |

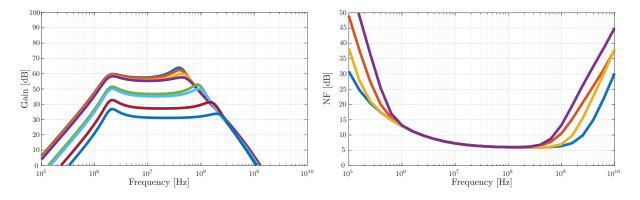

| 6.12 | Simulated receiver transfer function and noise figure (with mixer) at various gain                                                             |     |

|      | settings                                                                                                                                       | 107 |

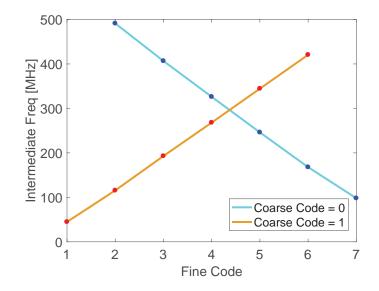

| 6.13 | Intermediate Frequency versus LO code in a loopback test                                                                                       | 108 |

| 7.1  | Block diagram of multi-band transmitter                                                                                                        | 111 |

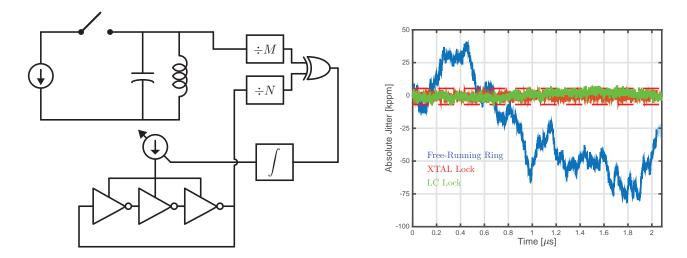

| 7.2  | Schematic and simulated result of a ring oscillator with and without period cor-                                                               |     |

|      | rection with LC tank. In this simulation, the LC tank is continuously running                                                                  | 112 |

| A.1  | Pad diagram of the single chip mote v3                                                                                                         | 123 |

| A.2  | Inputs to the Matlab scan function                                                                                                             | 125 |

| A.3  | 802.15.4 Modulation Logic Schematic                                                                                                            | 127 |

| A.4  | Divider registers, bit by bit                                                                                                                  | 128 |

| A.5  | Oscillator frequency tune registers, bit by bit                                                                                                | 128 |

# List of Tables

| 5.1 | Performance summary of 802.15.4 and BLE transceivers and transmitters oper- |    |

|-----|-----------------------------------------------------------------------------|----|

|     | ating in the sub-10 mW regime                                               | 78 |

#### Acknowledgments

First and foremost, I would like to thank Kris and Ali, for being my advisors. Kris was always so enthusiastic about research and so genuinely excited when things worked. Ali would always help debug difficult circuits problems and explain complicated subjects to me. His mindset and group culture made me a better designer, and his patience and positive demeanor were traits that I will always try to aspire to. Other influential faculty were Elad Alon, who helped teach me circuits, and Anant Sahai, who was the instructor (with Ali) for EE 16A, one of the most enjoyable experiences of my PhD. I would also like to thank Steve Glaser for serving on my qualifying exam and dissertation committees, and for asking the hardest question in my qualifying exam.

Brad Wheeler and I worked together almost every day for the past five years, and it was an enormous priviledge. If I could put a second author on my dissertation, I would put his. I'd also like to thank the other members of the  $SC\mu M$  team, David Burnett, Osama Khan, and Sahar Mesri. The single chip motes were ambitious, by academic standards, and I'm not sure if it would have been possible with a different group of people. Towards the end of my PhD I also had the opportunity to work with Sashank Krishnamurthy who is a phenomenal designer.

Even though I never worked with this next group of people in a technical capacity, their importance to my graduate school experience cannot be understated. Joey Greenspun, Claire Lochner, and Ozzy LaCaille, thank you for being my very best friends. Joey, your oppressive optimism never went unappreciated. Claire, it was really fun to grow up with you (in the graduate student sense). And Ozzy, thanks for all of the venting and bar-napkin circuits. Go Nuggets! Thank you roommates, Luke Latimer, Daniel Gerber, Andrew Townley, Stephen Twigg, and Joe Corea, for always keeping it real, and for always being down for a beer after a rough day, which was almost every day. I also owe thanks to a number of students now far-removed from Berkeley: Matthew Spencer, Mike Lorek, Stephan Adams, Hanh Phuc Le, and Alberto Puggelli. Each one of you helped me find my bearings early on in grad school. And Alberto, thanks for getting me out of that bit of trouble in Italy. I owe you one. There are also members of the Pister and Niknejad groups who I have not thanked elsewhere. Lorenzo, Yi-An, Nima, and Bo from Ali's group, and Lydia, Alex, Dan and Daniel, Hani, Craig, Brian, and Nathan from Kris's group.

Legendary wizard Archibald Harris Jr. would never allow me to submit this dissertation without thanking his companions: Kody (Joey), Nara (Claire), Deeba (Daniel Contreras), Wakunda (Balthazar Lechene), and dungeon master Daniel Drew. The "weekly" pizza and escapism helped me a great deal. Over the year, Archibald became a part of me, and I have all of you to thank (or maybe curse) for it.

When you see a fence post with a turtle post balanced on top, you know he didn't get up there by himself. So, thank you, mom and dad, for putting me on the post. Thank you brothers, Nikola and Stevan, for always laughing at my terrible attempts at humor. And, of course, thank you, Rale and Djole. I'll see you both again soon. Konstantinovici (Duda, Neda, Veca, i Mile) volim vas sve.

# Chapter 1

## Introduction

## 1.1 Wireless Communication in the 21<sup>st</sup> Century

Wireless connectivity has evolved considerably from the first data transmissions of Hertz, Tesla, and Marconi. In 2017, 4.66 billion people own a mobile phone [1]. Cellular technology and its rapidly increasing throughput demands fuel technological innovation and development of new, high data rate, long range wireless communications. The proposed mm-wave backhaul network necessary for 5G is one example. Verizon and AT&T's purchase of significant swaths of licensed spectrum in the 28-39 GHz band confirms this trend. Lying in stark contrast to the high-performance cat-video-streaming wireless networks (like LTE, 5G, and modern WLAN), lurks the increasing presence of low power wireless devices. These devices, often referred to as part of the so-called "Internet of Things" consume minimal power, communicate with low data rates, should be physically small, and cost infinitesimally little. And, of course, there will be a lot of them. Over twenty billion by 2020, if you believe [2]. The enormous Mirai DDOS attack [3] that crippled Dyn DNS (that serves Amazon Cloud Services, among other popular web services and sites) in October of 2016 was fueled by a botnet of millions of compromised wireless devices. From an economic perspective, recent market analyses predict upwards of \$300 million revenue for the IoT industry [4], which is comparable to the advanced energy industry in the United States [5].

Although current commercial applications of these wireless devices have gained little traction, industrial, urban, and medical applications show some promise. In the oil refining industry, for example, [6] has demonstrated automatic localization of gas leaks with 1 meter spacial resolution using a distributed network of gas sensors. In medicine and personal health, [7] has developed a wireless ingestible gas sensor that can estimate diets and assist with diagnosing gut disorders. Similarly, [8] has demonstrated a flexible, wireless, wearable medical device for constant monitoring of multiple vital statistics. And, finally, [9] describes the Padova Smart City project in which a network of wireless sensors attached to light poles throughout the municipality of Padova, Italy, collect sensor data (such as CO level, air temperature, humidity, vibrations, and sound levels). None of these technologies would

be possible without miniature (for ease of integration) and low-power (for increased battery life) wireless communication.

## 1.2 Radio Miniaturization

Gartner's hype assessment of IoT cites low-cost development boards as an integral technology for accelerating IoT beyond inflated expectations (I guess we're there now) to the trough of disillusionment [2]. If, instead of a development board, everything needed for a wireless transceiver were integrated on a single piece of silicon, the price would be negligible - as little as < \$0.05 per chip if produced in volume (approximated from [10]) - and the device could be interfaced easily with a sensor as part of a consumer product or industrial monitoring network. The ultimate goal of the work presented in this thesis is to build a single chip platform that could easily be used for any of the forementioned applications, and, potentially, unlock new, previously unexplored use cases.

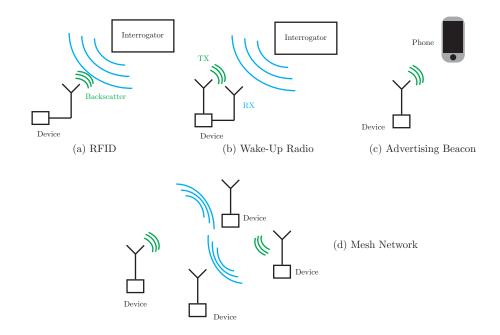

Figure 1.1: An illustration demonstrating various communication modalities for wireless sensor deployments

A number of potential types of wireless communication have been proposed for various applications, as shown in Fig. 1.1. RFID typically operates with either backscattering (modulation of the antenna impedance that creates a reflection) or by energy harvesting of the interrogator's RF transmission and subsequent side-channel transmission. The benefit is that the device can be completely passive, and consume zero power, when not in use. All of the energy in the system is provided by the high-power interrogator. The downside, of course, is that the interrogator is necessary for any communication, and that the data rates are extremely low if a high degree of power transfer is needed [11]. In a similar vein, wake-up radios [12] and [13] can operate at extremely low power levels and provide a similar function to RFID tags, but with higher performance. The interrogator sends a coded sequence. If the wake-up portion of the receiver hears it, it activates the dormant higher-power transceiver to communicate to the interrogator. This has two significant disadvantages in addition to requiring an interrogator: non-zero sleep power (the receiver is always listening), and the wake-up receiver needs to have similar sensitivity to the high-power receiver to reduce the probability of either erroneous wake-up or a missed reception (a proverbial hitting of the snooze button). In the advertising beacon example, the device acts exclusively as a transmitter and periodically sends packets that can be detected either by a specialized receiver or, more commonly, existing commercial hardware. This device would not require specialized equipment, but, unless heavily duty cycled (a tradeoff against data rate) could burn significant power. And, if compatibility with cellular phones or routers is needed for the application, it must adhere to wireless standards.

The mesh network is more useful in broad sensor deployments, such as in [6] and, in addition to generally requiring compatibility with existing wireless standards (both for reliability and for integration with existing infrastructure) requires symmetrical communication. Every node in the mesh must be able to transmit and receive data from other identical nodes.

## **1.3 Wireless Standards**

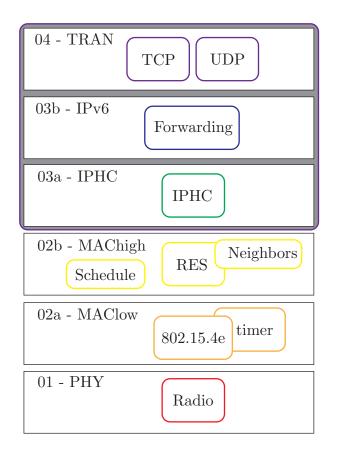

Fortunately, many standards already exist both for mesh networking and for beacon-style advertising. Typically, RFID is simple enough that standards are not needed, but the FCC does put limits on transmitted power in the unlicensed portions of the spectrum. Some wakeup standards have been proposed [14] but, if the radios do adhere to any particular standard, are generally built with IEEE 802.11 in mind. I will briefly summarize the requirements of two widely-used wireless communication standards, Bluetooth Low Energy, and 802.15.4, relevant to transmitter and frequency synthesizer design, as they are the dominant power consumers in a wireless transceiver. The decision to operate in accordance with existing standards was made for two reasons. The first was integration with existing hardware. On a fundamental level, the purpose of these transceivers was to make every sensor node tiny, low-power, and wireless. And that becomes a considerably more attractive proposition if these wireless sensors can exist in established networks and operate in conjunction with off-the-shelf hardware. The second reason is the stack that exists as part of many of these standards. Bluetooth, for instance, has become the standard for low datarate and low power interaction between wireless handsets and wireless peripherals. As a result, if the transceiver is compatible with Bluetooth, the device can communicate to phones and computers. IEEE 802.15.4 can be combined with various protocol stacks (such as WirelessHART, Zigbee, or OpenWSN) to connect a sensor to the internet.

Figure 1.2: The OpenWSN stack [15]. As long as the wireless transceiver adheres to the requirements set by the 802.15.4e standard, and as long as on-chip digital hardware is capable of running the MAC and protocol layer packet assembly (TX) and disassembly (RX) and the scheduling, the device can operate in an internet-connected wireless sensor network

#### **Bluetooth Low Energy**

Bluetooth Low Energy (co-compatible with the more common but more power intensive Bluetooth) is a 1 Mbps data rate link that uses Gaussian pulse-shaped frequency shift key with a modulation index of between 0.45 and 0.55. The standard mandates at most  $\pm 50$ ppm error on the transmitter clock. However, most commercial Bluetooth receivers can demodulate with data rate errors of nearly 500 Hz. BLE channels are spaced equally across the 2.4 GHz ISM band (between 2.4 GHz and 2.485 GHz) with 2 MHz channel spacing. This is a summary of relevant PHY-layer specifications for BLE:

• Minimum Output power of -20 dBm, maximum output power of +20 dBm (depends on class of device, ranges from +20 dBm for a class 1 device to 0 dBm for a class 3 device)

- Modulation is Gaussian Frequency Shift Key (GFSK) with a modulation index between 0.45 and 0.55.

- The frequency deviation during a 1010 sequence will be within 80% of a 00001111 sequence.

- The minimum frequency deviation (at 1 Msym/s) is 185 kHz and the maximum is 370 kHz.

- Symbol timing accuracy is  $\pm$  50 ppm.

- Zero crossing error must be less than  $\pm 1/8^{th}$  of a symbol period.

- FCC part 15.247 rules: the 6 dB bandwidth of the transmitter spectrum must be 500 kHz.

- At 1 Msym/s modulation, spurious power at 2 MHz away from the channel must be, at maximum, an absolute -20 dBm. At 3 MHz or further, it must be, at maximum, and absolute -30 dBm.

- At 2 Msym/s modulation (fast data rate), spurious power at 4 MHz away must be, at a maximum, an absolute -20 dBm. At 5 MHz, it must also be less than -20 dBm. At 6 MHz or greater, it must be -30 dBm.

- Deviation of center frequency cannot exceed  $\pm$  150 kHz including both starting frequency and drift. During a packet, the frequency cannot drift more than 50 kHz, and the drift rate must be less than 400 Hz/ $\mu$ s.

#### 802.15.4, OpenWSN

802.15.4 is an IEEE-maintained standard designed for use in low data rate personal area networks. It is a 2 Mbps data rate link modulated by orthogonal quadrature phase shift key (equivalent to minimum shift key, a special case of frequency shift key with modulation index of 0.5 [16]). The standard mandates at most  $\pm 40$  ppm of error on the 2 MHz data clock. However, recent network-level innovations [17] have demonstrated a high degree of timing accuracy even without a high quality timing reference. 802.15.4 is also spread evenly across the 2.4 GHz ISM band with 5 MHz channel spacing.

Various network protocols exist on top of the 802.15.4 standard, primarily, WirelessHART, Zigbee, and OpenWSN [18]. These complete network stacks are designed specifically for multi-hop wide-area mesh networks. And, all three of them use time and frequency channel diversity in the form of a schedule. That way, many devices can communicate either simultaneously on different channels (FDMA) or at different times on the same channel (TDMA)

#### CHAPTER 1. INTRODUCTION

without interfering with one another. This schedule requires a high degree of channel selectivity in the presence of varying environmental conditions, and precise timekeeping over potentially long periods (network data rate dependent). Here I summarize relevant PHYlayer specifications for 802.15.4.

- Sixteen channels with channel spacing of 5 MHz.

- Modulation is offset-quadrature phase-shift key (equivalent to MSK)

- Modulation is performed at 2 Mchips/s (which is derived from an actual data rate of 250 kb/s)

- There is a relative limit of -20 dB (relative to carrier power) at a distance of 3.5 MHz from the channel

- The phase noise of the local oscillator (derived from receiver specifications) is -102 dBc/Hz at a 3.5 MHz offset, and -103.5 dBc/Hz at a 10 MHz offset [19]

Note that for the summaries of both BLE and 802.15.4, some of the requirements come directly from the specification document, and some are derived from specifications to translate more easily to circuit-level requirements.

#### WiFi

WLAN is currently adopting an offshoot of its wireless standard intended for compatibility with low-performance devices [20]. This is an appealing target, as WiFi is present in nearly all indoor environments. While [21] demonstrated a method to fake a minimalist 802.11a packet using exclusively FSK modulation, 802.11 is fundamentally based on a constellation of phase and amplitude modulation whose EVM specifications are difficult to meet without a precise timing or frequency reference. In addition, aside from the simple BPSK case, uses variable amplitude modulation, which considerably complicates transmitter and power amplifier design.

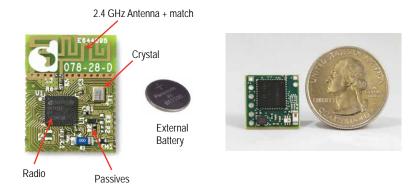

## 1.4 A Typical Mote

If the goal is to integrate a radio onto a single CMOS die, all of the external components associated with a typical mote must be either removed or worked around. The crystal is used as a precise time and frequency reference for phase-locked and frequency-locked loops. Unfortunately, because of the difficulty of performing energy harvesting to the degree needed to power a radio, an external power source is still needed. However, it is still important to reduce power as much as possible so that the lifetime of this power source is maximized. The antenna serves to transfer power from an electrical signal in a conductor to a propagating electromagnetic wave. Its size compared to the wavelength of the carrier frequency is an integral part of its efficiency.

Figure 1.3: Board-level implementations of wireless communication nodes. Left is [22] a typical commercial wireless node. Right is [23] the smallest wireless node in research

#### Timing and Frequency Specificity

Removing the crystal means that the radio no longer has a timing reference that is insensitive to variations in temperature and voltage. In addition, no low-power CMOS timer exists that has jitter or frequency drift comparable to a crystal oscillator (this is a consequence of the crystal's high mechanical Q factor). This has dire consequences for scheduled mesh networks, as every node needs to have an accurate knowledge of the global network time. In addition, without an accurate data clock, transceiver performance is compromised (EVM is degraded for the transmitter, and sensitivity is degraded depending on the CDR bandwidth of the receiver). Some work has been done on network-level compensation of low frequency timers [17] and frequency synthesizers [24].

Removing the crystal reference has the added benefit of reducing system power consumption as it eliminates the phase locked loop (PLL). Without a reference of comparable or superior quality to the RF oscillator, it does not make sense to use a PLL or FLL. And without a PLL, there is no need for a high-power frequency divider. As a side note, because the RF oscillator is the highest quality frequency generated on chip, there could be some benefit to using a divider to generate a higher quality low frequency oscillation. However, to reiterate, the primary reasons for eliminating the crystal reference from a modern standards compliant transceiver are cost, and size (ease of integration).