# HAMMER: A Platform For Agile Physical Design

Edward Wang

# Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2020-28 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2020/EECS-2020-28.html

May 1, 2020

Copyright © 2020, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

Acknowledgement

This work was funded in part by the DARPA CRAFT program (HR0011-16-C-0052).

# Contents

| 1 | Keywords                                                                                                                                                                                                                                            | 4                                                                                                          |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 2 | Motivation and Background2.1Background2.2Existing Solutions Are Inadequate2.3Agile Hardware Design to the Rescue2.4Challenges                                                                                                                       | 4<br>4<br>6<br>9<br>12                                                                                     |

| 3 | HAMMER: A Platform to Enable Agile Physical Design3.1Design Philosophy3.2Overview3.3Python Driver3.4Shell/CLI Driver3.5Physical Design IR / Configuration System3.6Tool Abstractions3.7Technology Abstractions3.8Agile RTL transformations and DSLs | <ol> <li>15</li> <li>15</li> <li>16</li> <li>18</li> <li>19</li> <li>22</li> <li>25</li> <li>26</li> </ol> |

| 4 | Evaluation         4.1       Sample Flows                                                                                                                                                                                                           | <b>29</b><br>29<br>33<br>34                                                                                |

| 5 | Related Work                                                                                                                                                                                                                                        | 35                                                                                                         |

| 6 | Lessons Learned                                                                                                                                                                                                                                     | 35                                                                                                         |

| 7 | Future Directions                                                                                                                                                                                                                                   | 36                                                                                                         |

| 8 | Conclusion                                                                                                                                                                                                                                          | 37                                                                                                         |

| A | opendices                                                                                                                                                                                                                                           | 39                                                                                                         |

| A | Reproducibility                                                                                                                                                                                                                                     | 39                                                                                                         |

| в | Hammer Tool and Driver API Documentation                                                                                                                                                                                                            | 39                                                                                                         |

| С | Hammer IR/Configuration Library Documentation                                                                                                                                                                                                       | 60                                                                                                         |

| D | Hammer Technology API Documentation                                                                                                                                                                                                                 | 64                                                                                                         |

| E | Floorplanning DSL documentation                                                                                                                                                                                                                     | 67                                                                                                         |

| G | ossary                                                                                                                                                                                                                                              | 90                                                                                                         |

| A | cronyms                                                                                                                                                                                                                                             | 90                                                                                                         |

## 1 Keywords

VLSI, software engineering (SE), physical design, digital design, CAD/EDA, design methodology

# 2 Motivation and Background

#### 2.1 Background

After looking at the ENIAC, the state of the art computer in 1945, it would be difficult to imagine that this monstrous beast could ever fit inside the tip of a pen. ENIAC contained approximately 18000 vacuum tubes (electronic switches), weighed 30 tons, occupied a 30x50 foot room, and consumed about 150 kW of power (equivalent to operating about 37 electric ovens at the same time[1]). At its peak operating efficiency, the ENIAC could perform about 5000 instructions (calculations) per second.[2][3]

In contrast, the Intel Core i7-8700K, a representative top-end desktop computer CPU in 2017, is capable of executing about 39,000 million instructions per second using 2 billion<sup>1</sup> transistors (electronic switches), and consumes only 95W of power[5]. The total chip package weighs 3 ounces, and its dimensions are less than 4x5 inches<sup>2</sup>.[6]

This miracle of computing is usually explained via the phenomenon known as Moore's law. In the 1960s, Gordon Moore (co-founder of Intel) made an observation (now known as Moore's law) that the number of transistors on a computer chip doubles about every two years. His observation has held true until recently, bringing computing from the crude machines of the 1960s/1970s to today's smartphones, intelligent thermostats, and data centers.[7]

To first order, Moore's law was significant in that it predicted performance would double, while at the same time, area and power consumption would remain constant. With this power of doubling, software developers were able to add more features and produce reasonably-performant software in a shorter amount of time. This phenomenom occurred because they could now program in increasingly productive higher-level languages (e.g. Java instead of assembly/machine code), focus on non-performance aspects of computing such as user interfaces, and exert less man-power on low-level performance optimization.[8] As Jeff Atwood noted in 2008, "until the day that Moore's Law completely gives out on us, one thing's for sure: hardware is cheap - and programmers are expensive." [9]

Recently, however, Moore's law has slowed in delivering the promised performance gains. A companion trend called Dennard scaling allowed transistors to shrink in size and consume proportionally less power, meaning that the number of transistors per area could quadruple, while the chip as a whole still consumed the same amount of power.[10]. Around the mid-2000s, however, Dennard scaling was the first trend to violate expectations when computer chips hit the single-core "power wall" - the phenomenon where a chip would consume more power than could be adequately dissipated via a heatsink. This meant that clock speeds and single-threaded performance could no longer follow the exponential gain described by

$<sup>^{1}</sup>$ The actual number is unclear since Intel does not publish official transistor counts for this chip - estimates range from 1 to 3 billion transistors.[4]

<sup>&</sup>lt;sup>2</sup>Retail dimensions include consumer packaging and other overhead.

Moore's law. Since then, processor vendors like Intel have continued to pack more transistors onto individual dies by increasing the number of cores instead of trying to increase the clock frequency for a single core.[11]

Unfortunately, even Moore's Law itself is under siege. As transistors approach atomic limits where classical physics break down, we can observe the difficulties in process costs - e.g. photolithography, tooling, and yield all become challenging, resulting in higher fabrication costs. Despite the shrinkage of transistors, the cost per million gates stops dropping after 28nm. In fact, the cost per million gates actually starts to slightly increase.[12] [13] Recently, the semiconductor community has been debating whether there will be any significant process nodes past 7nm, heralding the death of Moore's law.[14] While many exotic (non-CMOS silicon-based) technologies such as carbon nanotubes and quantum computing exist, they do not function in the same environmental conditions with the same performance and accuracy characteristics.Hence, since software can no longer automatically rely on Moore's law (either via single or multi-core scaling), we must develop custom hardware and accelerators to continue reaping performance gains.

Chip making, however, is very expensive, ranging from \$50-\$300 million for conventional chip projects[14]. While manufacturing each chip costs some money, this amount may not account for most of the cost in low to moderate-volume products, which is dominated by non-recurring engineering costs (NREs) - one-time overhead costs required to design a chip which remain constant regardless of the number of units manufactured. In particular, for large chips, the cost is dominated by design complexity in all areas (software, hardware design, and physical design). This design complexity results in high engineering effort which translates to high costs. For example, the CEO of a fabless semiconductor company noted that "engineering salaries are by far the biggest cost in SOC design". [15]

Developing software for programming new semiconductor devices dominates the cost of new products, followed by hardware costs like verification, validation, IP qualification, and physical design. Fabrication and other overhead (e.g. marketing) come afterwards.[16] [15] In other aspects of new semiconductor projects such as software, re-use helps bring down cost, while current physical design methodology prevents physical design efforts from being effectively re-used across nodes/projects/tools. Other work such as domain-specific languages like Halide [17] can help reduce the cost of developing software for new semiconductor products. This work focuses on addressing the hardware-related portions of the NRE.

On the hardware front, we hypothesize that a number of factors contribute to high hardware design NREs, such as sub-optimal programming interfaces in CAD tools (TCL), inefficient abstractions, and CAD tool vendor oligopolies. Another factor which could contribute to high hardware design NREs is the disconnect between RTL and physical design. By creating a platform for agile hardware design, we hope to tackle the hardware design NREs. This work focuses mainly physical design, but also addresses validation, IP qualification, and verification concerns by exploring inefficient programming interfaces and poor abstractions.

Why do we need these additional abstractions? RTL alone is not sufficient to tape out a chip. RTL provides details regarding logic that goes on the chip, but almost completely abstracts the physical implementation of the chip.<sup>3</sup> The information required for physical

<sup>&</sup>lt;sup>3</sup>Some CAD tool vendors support custom Verilog inline attributes to specify certain constraints, but as we will discuss later, this is not portable nor necessarily desirable.

implementation includes placement, clocks, power, port constraints, pads/bumps, but also off-chip/integration concerns like packaging. While automatic place and route tools can do most of the logic cell placement, large hard macros such as memories or analog blocks need to be manually placed<sup>4</sup> to achieve optimal efficiency. To tape out any real chip, this information needs to be passed on to the CAD tools somehow.

While there are some existing solutions, they still prevent hardware innovation by making the NRE cost high, mostly by non-portable or inefficient methodologies. Even in the presence of previous tapeouts, creating a new chip project remains inefficient and frustrating, which translates to high design engineering costs. We want to examine why this inefficiency occurs, and propose a modular<sup>5</sup> platform to enable hardware innovation and make new chip projects less frustrating.

#### 2.2 Existing Solutions Are Inadequate

Many large institutions have created internal scripts and flows<sup>6</sup> to create chips. These scripts hard-code information from 3 different sources that are mixed in together: 1) Technology process design kit (PDK) (Process Design Kit) paths and references; 2) RTL/project-specific paths; 3) CAD tool vendor-specific commands. In addition, many scripts are commonly implemented using programming languages like GNU Make, bash scripting, sed, and TCL. They lack abstractions like object-oriented programming, type systems, well-defined data structures, well-defined libraries, etc, which, at least from anecdotal evidence, makes maintaining them very difficult or frustrating<sup>7</sup>.<sup>8</sup>

While CAD tool vendors provide "example flows" or "reference methodologies" intended to be somewhat modular, the fact that customizations and additions to the flow happen directly in the flow by modifying or writing TCL commands/variables limits re-use by tying those commands to a specific CAD tool vendor, technology node, and chip project.

Some vendors have custom inline attributes in Verilog which encode physical annotations to CAD tools (e.g. FPGA tools, VCS, etc). These attributes are non-standard<sup>9</sup>, and variable

<sup>7</sup>While frustration and errors are hard to quantify, some commit messages (written by multiple individuals) from an internal chip repository include "Fixing [person]'s stupid typos", "fixing carriage return in [person]s block", "Derpa doo", "CAPS LOCK CUZ I HAVE ANGER ISSUES AND IM STILL SALTY THAT FLIPCHIP IN [CAD tool] IS THE WORST", "Jesus f\*\*\* [CAD tool]", "Last edit. Last commit. Plzzz" (of course, there were (many) more fixes required afterwards), and "Stupid stupid stupid".

<sup>8</sup>PLSI was a previous attempt at creating a modular flow. During our attempt to use it for a tapeout and maintaining it afterwards, we found it difficult to avoid making errors like simple typos, global variable dependencies, esoteric syntax, etc that made it hard to use. In addition, the flow was very monolithic and it was difficult to re-use portions of it but not others.

<sup>9</sup>Section 4.4: "There are no standard attributes in the Verilog-2001 standard; Software tools or other standards will define attributes as needed." [18]

<sup>&</sup>lt;sup>4</sup>Some CAD tool vendors may have some automatic macro placement but for the most part higher-level design information is required to do this realistically.

<sup>&</sup>lt;sup>5</sup>By modular here we mean that there should be a well-defined API to make it easy and safe to add new plugins for supporting technologies and CAD tools without requiring a comprehensive understanding of all the environment/shell/Make variables floating in a global namespace. We will discuss this further in the Existing Solutions and design sections.

<sup>&</sup>lt;sup>6</sup>Most of these scripts are non-general, institution-specific, and even if they were well engineered, they are not freely available, hindering re-use.

support across vendors makes it non-portable. Furthermore, not all physical design traits are possible to specify in inline extensions (e.g. no major ASIC tool vendor supports encoding clocks or SRAM placement).<sup>10</sup> Therefore, encoding physical design information in inline attributes is not a fully portable solution, and as we will see later, even if we could modify the source RTL to include attributes/annotations, this may not necessarily increase re-use.

Other previous attempts tended to follow the framework pattern as opposed to the library pattern. The key distinction between frameworks and libraries is the idea of "inversion of control" [19] - in the library pattern, the API provides a collection of functions/methods we can call, and the control flow is defined in our application. In contrast, the "framework [pattern] embodies some abstract design" pattern and programmers use it through a series of bindings or hook points in which to add application-specific functionality, and control is passed to the framework via some form of "main loop".[20] Fowler (2005) calls this phenomenon the Hollywood Principle - "Don't call us, we'll call you".[20]<sup>11</sup>

In terms of a VLSI flow, a framework-style approach involves calling the flow's "main function" (or entry point), and the flow is customized by injecting project-specific logic into certain binding/hook points which the flow will call at the appropriate point.Unfortunately, in the context of a VLSI flow, a framework approach makes it difficult to gradually adopt the tool, since the framework makes some assumptions about the abstract design of the flow that may not always hold when we are actually trying to use the tool. Here are a few examples of situations where a framework-style design is problematic:

- Writing a design space exploration loop for a sub-step of place-and-route (e.g. clock tree synthesis) this will be difficult/annoying to do with a framework which assumes a linear run through synthesis and place-and-route without repeating any steps in between and does not provide programmatic, easy-to-use APIs to control the steps. In contrast, a library would allow us to write such a program very easily since we can control when portions of tools run.

- Integrating a build system for managing CAD tool runs integrating complex build systems which are often framework-style proves difficult when both the VLSI tool and the build system assume ownership of control.

- Customizing specific methods and processes within the flow the flow may embody a specific model for adapting generic RTL to technology-specific RTL suitable for tapeout (more on this later), but the project may have its own specific ways of generating or adapting the RTL to the technology, and having a tool which assumes ownership of calling those processes will be hard to re-use.

- Generating small digital blocks for analog our VLSI flow may assume an abstract model of generating a full digital-top chip with top-level I/Os, but we may want to use the tool to only generate some small analog blocks without any top-level integration or checks, resulting in a conflict of what the flow model should be.

<sup>&</sup>lt;sup>10</sup>To our knowledge.

<sup>&</sup>lt;sup>11</sup>Some examples of framework-style libraries include GUI libraries and JUnit.[20]

When a framework lacks sufficient binding/hook points for fully controlling its behaviour, often the only recourse is to create a fork (a local copy of the code) and modify those portions of the code. This causes a large software maintenance burden since the modifications need to be kept up to date with the upstream code in order to benefit from bug fixes and new features in the upstream code.[21]

Nonetheless, we recognize that frameworks exist and are useful because patterns do in fact repeat [19], and that not every use of a library is completely different. In order to address these needs, we build libraries that have both modular (library-like) and high-level (framework-like) APIs. However, the high-level APIs should be as thin as possible. The high-level APIs make it easier to get started with using the tool by embodying common patterns, and the modular APIs make it easy to build custom functions and extensions using the library. If we only provided modular APIs but no high-level APIs, there would be a proliferation of copy-paste in integrating all these modular APIs, making it difficult to add new features. For example, if customizing a place-and-route flow required creating a fully custom function and running each step individually, it would be difficult to re-use upstream changes e.g. when a new step is introduced.

Another challenge faced in creating VLSI flows is being backwards-compatible with the underlying languages/technologies we are trying to abstract - in this case, TCL and Verilog. Many programming languages owe some to all of their success in being backwards-compatibility with existing languages. For example:

- Chisel features compatibility with Verilog (the pre-existing technology) in both ways - it allows users to use Verilog modules with a BlackBox mechanism[22], and while Chisel's modules elaborate to Verilog by default, it provides mechanisms for users to define modules with fully customized port names and without the implicit clock and reset ports.

- Scala is Java-compatible to first-order, making it possible to use existing Java libraries/frameworks and develop libraries/frameworks which can be used in Java.[23][24]

- C (with many compilers) is backwards-compatible with assembly language, making it possible to (relatively) easily write and call assembly language routines from C.[25]

- High-level programming languages like Julia and Python all have C extensions. Languages not able to re-use optimized GEMM libraries will be at a disadvantage. Even Java has JNI to call native code and take advantage of optimized libraries in 'legacy' languages.

Hence, we aim to design a system which allows the use of TCL/Verilog for backwardscompatibility and adoption, while providing a platform to make it possible to encode as much of physical design knowledge at a higher level. Similarly, we aim to create a physical design IR that can either be generated from agile tools like FIRRTL/Chisel or be hand-written. In doing so, we aim to provide the infrastructure to use higher-order (e.g. Scala-based) generators for physical design information without forcing their use.

Finally, we aim to create a platform which is modular. With existing compiler frameworks like LLVM, instead of writing M \* N pieces of code for M input languages and N output

formats, we can write M + N pieces of code instead: M front-ends for input languages, and N code generation backends. Likewise, through our hardware IR, we aim to enable many different hardware "input passes" to generate physical design constraints that can be consumed by a number of different backend tool and technology plugins. For example, instead of writing a specific program to generate clock constraint TCL fragments for a specific CAD tool vendor from rocket-chip, we can leverage FIRRTL and our hardware IR to generate generic constraints which can be portably consumed by many different plugins.

#### 2.3 Agile Hardware Design to the Rescue

Electrical engineering/software engineering inherited waterfall-style planning from older engineering disciplines such as mechanical and civil engineering, where once execution of a project was started, it would be very difficult and expensive to change course.[26] In contrast, a group of software engineers published the Agile Manifesto in 2001, valuing small, close iterations, adaptiveness to change, and producing working software.[27] The software industry has benefitted from agile development - more specifically, from agile's recommendation to use small teams/projects and break down large projects into smaller projects - a 2013 study referenced by Fox and Patterson indicates that small projects are cancelled 4% of the time, in contrast to large projects which are cancelled 38% of the time.[28]

A traditional ASIC design process (e.g. as exemplified by [29] or [30]) involves a few sequential stages performed in order, waterfall-style. First, requirements are gathered for the chip project, and an architectural design is created at a block diagram level along with specifications for each of the major blocks. This is typically called the architectural stage of design. Next, this high-level architectural block diagram is passed to a group of engineers who implement blocks in the architecture at the RTL level (or schematics for analog designs) and then run simulations to verify that the blocks are correct<sup>12</sup>. Finally, the RTL and schematics are turned into a layout either using place-and-route tools for digital, or via manual layout for analog.<sup>13</sup> This is followed by post-layout simulations, final signoff (DRC/LVS), and then post-silicon test and bring-up.

We aim to bring agile ideas such as minimum viable product, fast feedback loop, and adaptable tools and systems to chip design. As we have shown in the Background section, conventional chip-making endeavours are \$50-300 million projects, well above the \$1 million threshold used by [28]. However, software is malleable - in principle, it can in principle be updated following initial deployment. In contrast, it is much harder to just "update" a custom chip broadly<sup>14</sup> deployed in datacenters, in the field, etc.<sup>15</sup> Nonetheless, the fabrication phase is still relatively short (say approximately 3-6 months) and most of the NRE cost and inefficiencies occur during the design phase of the project. As we note later, even producing a fabricatable chip design without actually fabricating it (called a tapein) is still

<sup>&</sup>lt;sup>12</sup>Exactly how "correct" a design needs to be and how we can show/prove a design is correct has a degree of freedom/controversy.

<sup>&</sup>lt;sup>13</sup>The spoiler alert here is that analog design is becoming more agile via generators like BAG[31].

<sup>&</sup>lt;sup>14</sup>This also implicitly assumes the "old Moore's law" business model of few products and high volume, but the same difficulties could also apply to limited-quantity, custom silicon like the TPU.

<sup>&</sup>lt;sup>15</sup>Of course, microchips can be programmable and have firmware/microcode, but that comes with its own set of deployment/security/logistical challenges.

very valuable for providing physical design/implementation feedback to other parts of the chip building endeavour. Chip design is still very much waterfall-based, which makes it hard to be adaptable, and increases the cost of designing a chip when changes need to be made.

Agility, defined as the ability for a project to quickly adapt to change, is essential both from a business perspective and a technical perspective. As a 2011 Harvard Business Review article notes, companies that "thrive are quick to read and act on signals of change". In particular, they note that companies which can experiment, manage complex systems, and mobilize quickly have an advantage from adaptability in the marketplace.[32]<sup>16</sup> These traits are also embodied in agile ideas - for example, adaptable tools and systems can help manage complexity, and the fast iteration loop allows us to quickly experiment and provide preliminary results for faster mobilization.

On the technical side, making a chip is a complex set of negotiations between all aspects of chip design, including process technology parameters, physical design, analog/mixed-signal blocks, and IP blocks/macros. For example, during a system-on-chip (SoC) design, the amount of space allocated to each portion of the chip varies over time as design progresses. But existing design mentality (e.g. freezing RTL) prevents changes and makes SoC design difficult, especially when later stages in the "waterfall" require changes to the chip. Instead of being agile and adaptive, the idea of fixed/frozen designs ("design freezes") being "thrown over the wall" to another team ties the hands of downstream teams and prevents their feedback from being effective in helping upstream teams in designing for downstream considerations.

For example, physical design (traditionally thought of as a "downstream" step from architecture/RTL) problems often require architectural changes to fix properly:

- During the BROOM (BOOMout-of-order processor with memory resilience) tapeout, a specialized register file was unimplementable with any reasonable QoR (space and critical path wise), requiring an architectural re-design to split the register file and break up the critical paths. Likewise, a cross-bar in the design turned out to be unroutable and required conversion to a tri-state cross-bar to be implementable.[34]

- During the Hurricane (codename for Berkeley DVFS research demonstration chips) tapeouts, not getting early feedback on how big certain cross-bars would be or how much congestion it would create resulted in delays in taping out and lowered QoR.<sup>17</sup>

- During the SPLASH (ASIC spectrometer) tapeout[35], we encountered the so-called SPLASH "ring of death"; a large ROM was mapped to gates in a way that does not work well for the place-and-route tool.

Generator-based design can help us achieve our goal of building systems adaptively with a fast feedback loop by facilitating re-use between blocks and projects. By providing a library of pre-written, parametrizable generators, designers can achieve a minimum viable product in

<sup>&</sup>lt;sup>16</sup>With regards to projections/forecasts, Warren Buffett opines that he has "no use whatsoever for projections or forecasts. They create an illusion of apparent precision. The more meticulous they are, the more concerned you should be." [33] Since the traditional waterfall model involves performing each step without returning to previous steps, it inevitably relies on projections or forecasts about downstream steps, casting doubt on the viability of a purely waterfall model of development.

<sup>&</sup>lt;sup>17</sup>Unfortunately, the author is not aware of pre-existing publications on this chip at the time of writing.

less time and obtain feedback in order to facilitate the agile feedback cycle. These generators encode a recipe or process for designing a family of circuits (digital or analog) and allow us to re-use work in a way that works for our current project, thereby avoiding the time-consuming phenomenon of having to re-write or modify instances to fit current project needs. [36]

Existing work such Chisel[22] and BAG[31] enable agile hardware design in RTL and analog circuits respectively. However, in order to make a chip, we need a backend VLSI flow which takes RTL, adds technology-specific mappings, and calls CAD tools for synthesis and place-and-route, all while providing the appropriate physical design information along the way. However, as outlined in the Existing Work section, we don't yet have an agile, re-usable, and principled<sup>18</sup> backend flow implementation. As a result, we can't directly leverage the fixes and lessons from previous tapeouts, meaning we have to repeat history by writing the same kind of RTL changes, the same kind of placement, etc over and over again, wasting time - the same problem analog design faced before BAG or digital design before Chisel (re-creating or tediously modifying existing instances from previous work to meet current project needs.)

More specifically, we recognize that physical design is a collection of many difficult problems - there is no single silver bullet. Hence, we aim to lower the barrier to solving these problems. Other tapeouts have dealt with these problems, but their solutions are not general or reusable. This makes it more difficult to produce a minimum viable product quickly, causing low adaptivity and a long feedback loop - physical design becomes a bottleneck in the agile hardware design ecosystem in the presence of agile generators like Chisel and BAG. It also explains why, for example, analog designers don't use place-and-route tools for generating useful pieces of logic like decoders, adders, and state machines.<sup>19</sup>.

To remedy this, we aim to provide a system to encourage designers to encode solutions in a more reusable way, so future tapeouts can leverage previous work (even with different technologies, CAD tools, or designs). For example, we fixed the "ring of death" and BOOM cross-bar problems with one-shot solutions, but had we encoded those solutions as generators, future designs could leverage those generators/solutions when the same type of issues appeared, reducing the time to minimum viable product.

In order to enable agile physical design, we provide many systems which designers leverage to encode information modularly and build re-usable flows. These include:

- A physical design IR (higher-level and CAD-tool independent directives) to facilitate the generation/description of physical design constraints separately from their underlying expression in imperative TCL commands. This tightens the feedback loop (by not requiring knowledge of tool TCL dialects to write constraints) and increasing adaptivity (by being independent from specific tool expressions).

- An abstraction on top of CAD tools in order to increase adaptivity and manage complexity by separating CAD tool concerns from physical design concerns.

- Higher-level technology abstractions to manage complexity (abstracting away the details of the technology and PDK) and tighten the loop (reducing the amount of time hunting

<sup>&</sup>lt;sup>18</sup>In terms of modularity, type safety, expressivity, etc. For example, a principled generator can provide huge productivity savings compared to an ad-hoc, one-time, non-reusable solution (Rocket vs OpenPiton).[36] <sup>19</sup>Anecdotally from speaking to analog designers at Berkelev.

for PDK paths in order to use a technology).

- Pre-provided drivers to capture common patterns of running physical design / VLSI flows and reduce the feedback loop by providing useful, out-of-the-box functions/APIs/shell commands to make getting started easier and faster.

- A mechanism to directly manipulate/introspect on RTL to synchronize physical design constraints with RTL generators and tighten the loop by connecting RTL generators to physical design generators.

We will elaborate further on these in the Design section of this work.

## 2.4 Challenges

There are a number of possible challenges to this approach.

- Time required to fab is quite large, so automating/optimizing the flow doesn't matter.

- Tapeouts aren't necessary for evaluation even doing a "tape-in" (performing the entire design process to the point of generating a fabricatable GDS but without sending it to the fab) will give us good design feedback to improve the architecture and RTL in an agile manner (tight feedback loop, minimum viable product).

- In academia, it is possible to publish papers with realistic LVS-clean designs.

- Run-times are long on complex designs, so automating/optimizing the flow doesn't matter.

- It's better to have safe and agile flows that will either work or fail early, rather than manually writing/modifying flows that may or may not work, or relying on copies of scripts of unknown origin.

- With re-usable generators, we can move towards getting things right the first time or earlier on with checks.

- We can also iterate on smaller chunks of the design being agile (e.g. Chisel with Hammer generator), we can easily generate a smaller version of the design that is faster to implement in order to get feedback faster.

- Also, this is not true for all use cases for example, when generating digital blocks for analog designers, the bottleneck is the configuration/environment setup and ease of specifying physical design constraints, not the actual place-and-route run time.

- Our abstraction may not always be relevant to everyone.

- We structure our tool/system in the library-style, enabling users to create custom tools and APIs which build new abstractions relevant to their specific use cases.

- In addition, we feature explicit backwards-compatibility with TCL, so users can also inject or use custom TCL blobs to achieve specific outcomes for certain cases.

- Since we aim to build an open source solution, users can always download and modify it (e.g. by making a pull request) to improve the solution. The next time someone faces the same problem, they don't have to solve or encode that aspect of expertise again. Having an open source platform reduces the barrier to sharing and re-using physical design solutions within an organization or in public, just as how the fact that FIRRTL hardware compiler framework[36] and LLVM reduce the effort required to share a compiler pass via standardization.

- If CAD tools can't do a good job without all these extra physical design constraints, then we should fix/optimize the CAD tools to do a good job automatically.<sup>20</sup>

- Placement[37] and routing[38] are both known to be NP-complete, requiring exponential time. In practice, CAD tools can use good heuristics to achieve decent results quickly enough, but often these optimizations need to be guided with human designer knowledge/insight.

- Hence, until P = NP is proven, if ever, we still face the problem of passing physical design constraints to CAD tools, and the associated problems of reusable VLSI flows to pass these constraints. We avoid placing belief in a magical tool/algorithm/compiler that will solve all problems by itself.

- Even if we could parallelize place-and-route across many machines (assuming it is a fully parallelizable task, which is unlikely), it would still require an exponentially increasing number of machines to perform flat place-and-route (versus hierarchical place-and-route).

- Furthermore, even if the underlying heuristics were sensible, a hard to compose, hard to use API still creates a barrier to encoding physical design knowledge in a reusable manner. Instead, our platform allows users to build generators an designs using it that are useful for everyone.

- Large institutions may not care as much since 1) they can hire a physical design person who is comfortable with inefficient design practices (their philosophy being either: "not my job and I don't care" or "I got used to the frustrations; it's a part of the job") or 2) have in-house custom/non-reusable scripts that work well enough for their environment.

- Every institution (whether a company or university) is paying different people to do the same/similar things. If every company/university is going to spend valuable engineer/graduate student time solving the same problem, why not capture this knowledge to save effort on everyone's part? In fact, co-operation/collaboration of this sort has precedence in computing history in the 1950s, users of IBM 704 machines founded SHARE (Society to Help Avoid Redundant Effort) in order to 1) share programs for the IBM 704 to reduce redundant effort across organizations;

2) share knowledge of the workings of the machine to avoid making the the same mistakes across different organizations.[39]

<sup>&</sup>lt;sup>20</sup>Personally the author would like to see a good open-source, modular, and extensible place-and-route platform that makes it easy to test out new heuristics, just as how LLVM is an extensible platform that allows us to test out compiler passes without having to re-write an entire compiler framework.

- Engineer hours spent on things that could be fixed with better tools 1) cost \$\$\$ to the organization; 2) waste time - time is money; 3) cause frustration for engineers which translates to stress, lower quality of life, boredom, poor morale, etc.

- Furthermore, in the agile spirit, we can also enable other members of the team (e.g. architects, RTL engineers, etc) to get feedback earlier and more quickly on their architectures/RTL. For example, computer architects designing caches, accelerators, etc can use our tool to quickly check to first order the viability of their designs. Our tool broadens the accessibility of physical design and VLSI to beyond those who perform physical design for a living.

- Writing TCL/low-level scripts directly don't seem to be that bad. Why spend all this effort developing abstractions?

- Firstly, there are productivity gains to be had from writing in higher-level languages. Generators yield immense productivity gains, as we've been with BAG[31] generators and the rocket-chipgenerator.

- More importantly, abstraction is fundamental to enabling us to keep track of and understand the entire work in our mind. Writing software (or software that produces hardware) does not scale well since it means that we must keep track of an increasing amount of information. By using abstraction, we lower the amount of detail we must keep track of in our mind, reducing mistakes and allowing us to focus on the larger picture. As Dijkstra once mentioned - "as a slow-witted human being I have a very small head and I had better learn to live with it and to respect my limitations and give them full credit, rather than try to ignore them, for the latter vain effort will be punished by failure" [40].

- Backends are proprietary and non-open source which will hinder re-use anyway.

- We aim to make it as easy as possible to re-use the core framework between different plugins/site configurations. BAG[31] deals with the same problem - the library itself is open source but it depends on proprietary local configurations and technologies.

- More importantly, our modular approach allows us to switch between different tool vendors - we will never acheive the same degree of portability by depending only on one tool vendor's APIs. Portability is a valued feature in both academia and industry, and can be achieved by building a better open-source API.

- Nonetheless, a modular approach is capable of supporting open source backends (e.g. yosys), so it does not detract from potential adoption of open source backend tools.

# 3 HAMMER: A Platform to Enable Agile Physical Design

## 3.1 Design Philosophy

HAMMER stands for Highly Agile Masks Made Easily from RTL, and here is our design philosophy.

- Lego Blocks: Instead of a monolithic framework or tool, we provide a series of abstractions, tools, and DSLs which work together to enable agile physical design. Modularity is king. Each part of the system should be able to be used independently from the rest, to the maximum extent possible, in order to increase adoption and usability.

- Incremental Progress: Evolution, not revolution. Provide ways for designers to progressively adopt the system without requiring an all-or-nothing. Provide suitable escape hatches to allow fine-grained custom control where it matters, or where abstractions are incomplete. We believe it is better to have to hardcode 30% than 90%, or to be 50% agile rather than 0% agile.

- <u>Safe, Principled Foundations</u>: Use modern programming languages' benefits (DSLs, type systems, object-oriented programming, software libraries, etc) to reduce errors in the design specification and implementation.

### 3.2 Overview

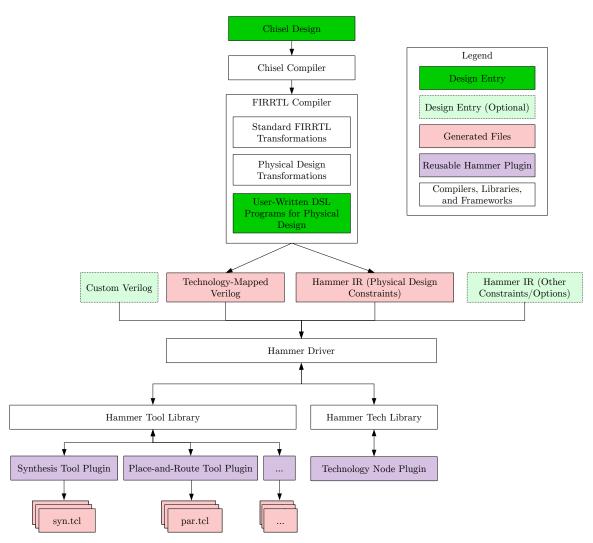

An agile physical design flow using the full Hammer methodology starts with design entry in Chisel.[22] Next, we run Chisel code to generate a circuit in the FIRRTL IR. We then run the FIRRTL compiler including technology-mapping/physical design generation transforms and user-written physical design generators (e.g. a floorplan generator), in addition to the standard FIRRTL to Verilog transforms. This generates a technology-mapped Verilog file ready for synthesis and place-and-route as well as fragment(s) of physical design information in Hammer IR. Next, the technology-mapped Verilog, physical design information, driver control information, and environment/tool settings are passed to the Hammer Driver (via the Hammer CLI Driver) which uses the Hammer Tool Abstraction library (hammer-vlsi) as well as the Technology Abstraction library to load and configure the required CAD tool plugins. Finally, depending on the type of action (e.g. synthesis, or synthesis and place-and-route, etc), the appropriate tool plugin is called to generate and run TCL scripts to implement its action subject to the given physical design constraints and tool settings.

Having said that, as outlined in our Philosophy section, we believe in incremental adoption. Instead of forcing users to use the entire Berkeley Scala-based (Chisel/FIRRTL) ecosystem, we allow users to start using backend Hammer abstractions (Tool, Technology, and Driver) with manual design entry in Verilog and manually written physical design constraints in YAML/JSON (Hammer IR) and incrementally move generation of constraints and designs to being generated from the FIRRTL-based passes and generators. We also support hybrid modes of operation - e.g. generating Verilog from Chisel/FIRRTL and manually writing constraints or using FIRRTL generating some constraints using transforms and writing

Figure 1: The overall architecture of the Hammer methodology showing the points of design entry, compilers/libraries, generated files/formats, and Hammer plugins, as well as the interactions between them.

other constraints by hand. This allows us to effectively support non-generator (Verilog and manually written physical design constraints) flows, Chisel/FIRRTL-based flows, other FIRRTL-compatible HCLs like Magma[41], or entirely separate modes of design entry (e.g. HLS).

## 3.3 Python Driver

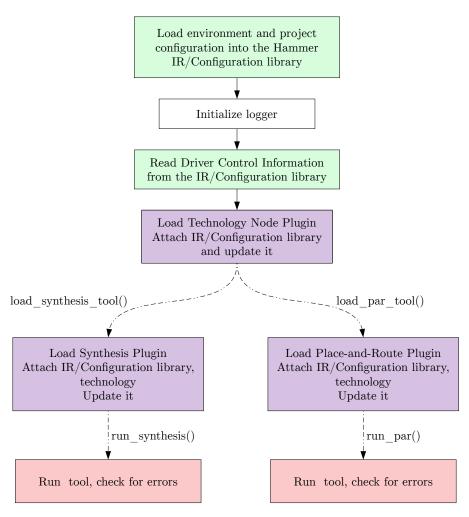

The Hammer Driver is a Python API which is at a 'higher-level' than the previous abstractions we have seen so far, since we recognized earlier the necessity of providing higherlevel/framework-style APIs in order to capture common patterns of abstractions and make it easier for users to get started with our system. The Hammer Driver uses the Driver Control Information and the Tool Control Information (see the IR section for more details) in order to load and instantiate the appropriate plugins in order to run a specific action.

Figure 2: The Hammer driver workflow at a glance.

The Hammer IR/Configuration library recognizes a sequence of IR snippets and combines them together into a large database. The Hammer Driver takes this abstraction a step up and provides a set of well-defined IR snippets and assembles them together in the following chain of precedence to the configuration system:

- builtins: Built-in variables defined by the Hammer Driver.

- core: Core settings defined by hammer-vlsi by default and available for overriding.

- tools: Settings provided by various tools.

- technology: Settings provided by various technologies.

- environment: User-supplied environment settings. (e.g. CAD tool paths, licence servers, etc)

- project: Settings specific to a run of hammer-vlsi.

The Hammer Driver API allows the latter two (environment and project) to be overridden; all other settings are defined by Hammer Tool libraries or the hammer-vlsi core (e.g. builtins, core). After running the appropriate action, the API returns an output copy of the project JSON along with the outputs in order to allow for modular re-use of hammer-vlsi. For example, the CLIDriver uses this API in order to implement a function that combines synthesis and place-and-route by using the output settings from synthesis to set the inputs for the place-and-route run.

### 3.4 Shell/CLI Driver

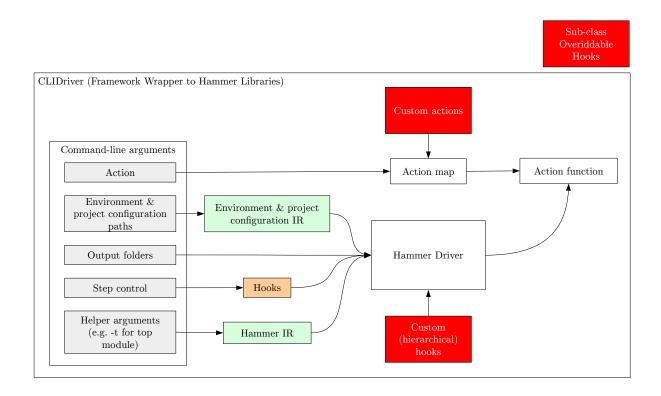

Figure 3: The Hammer CLIDriver framework class is intended to make developing CLI-based flow based on the Hammer Python driver easy.

The command line driver to Hammer, **CLIDriver**, is a framework-style command line wrapper to the (Python) Hammer Driver and the rest of the Hammer Tool Abstractions. The **CLIDriver** has a main function and is callable from the command line. It implements a set of actions which use the Hammer Driver API in order to achieve a specific purpose (e.g. run synthesis, run place-and-route, or run synthesis and place-and-route in the same action. The CLIDriver parses the shell arguments passed to it, sets up the environment and project configurations and passes them to the Hammer Driver for initializing the environment. It also sets the output folders for the Hammer Driver, in addition to parsing step control arguments which get translated into custom hooks and passed to the driver. Finally, helper arguments (e.g. input Verilog files, top module) which are translated to Tool Control Information IR snippets and passed to the Driver.

We created this class in order to 1) make it easy for new users to quickly start using Hammer; and 2) make it easy to add custom hooks and logic to customize the flow. While we recognize the power of the library-style APIs of Hammer in order to build fully custom generators and applications in novel contexts, we want to make it easy to start modifying the flow as a user, and providing this framework is the fastest way to inherit most of the default flow abstraction while slowly adding custom actions, hooks, and features.

With regards to hierarchical support - the default Hammer Tool Abstraction supports a hierarchical mode option but can only handle a single run in order to have maximum separation of concern and lightweightness. Likewise, the Hammer Driver abstraction does not add any additional capability to generate a hierarchical flow, though it facilitates manually writing a hierarchical flow programmatically. The CLIDriver interface, however, is capable of automatically generating hierarchical flows from Driver Control Information in the project Hammer IR.

### 3.5 Physical Design IR / Configuration System

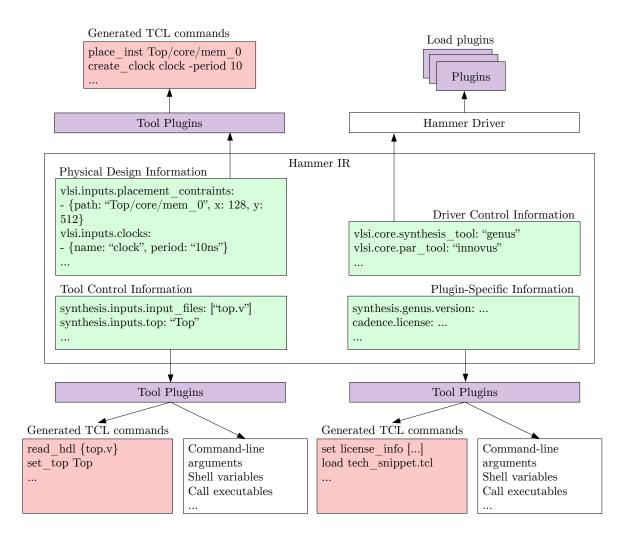

The Hammer IR is the primary data structure used for communicating information to and within the backend of the Hammer methodology. It encompasses four types of information:

- <u>Physical design information</u> physical design constraints (placement constraints, clock constraints, etc).

- <u>Driver control information</u> pointers for the Hammer Driver to load the appropriate plugins.

- <u>Tool control information</u> generic directives for the Hammer Driver on how to load-/launch/configure the tool type (e.g. for synthesis, we have top module, input files, etc).

- Plugin-specific information settings specific to a given tool/vendor (e.g. licensing, environment variables, tool versions, etc).

The Hammer IR is expressed as a key-value store, consisting of hierarchical keys stored as strings (e.g. "vlsi.inputs.placement\_constraints") with scalar (strings, numbers, booleans) or array/list values. Dictionaries cannot be stored directly as values, but can be stored inside arrays used as values. Each key-value pair is referred to as a **setting**.

Keys are strings with a hierarchy (e.g. "vlsi.inputs.test"), separated by periods. Legal key sub-parts are alphanumeric characters and underscores; periods are forbidden since the keys use periods to delimit sub-parts of the overall key. The Hammer IR/Configuration library will "unpack" hierarchies for ease of configuration. For example, the below snippet of IR, when loaded into the IR/Configuration library, will in the following settings (key-value pairs): "vlsi.inputs.supplies.VDD"  $\rightarrow$  "0.9V" and "vlsi.inputs.test"  $\rightarrow$  "bench".

```

{

"vlsi.inputs": {

"supplies": {

```

Figure 4: An overview of the four types of information represented in the Hammer IR, stored as a key-value store.

```

"VDD": "0.9V"

},

"test": "bench"

}

}

```

The IR/Configuration library accepts IR snippets stored in either the JSON (to facilitate programmatic generation of constraints) or the YAML format (to make it easier for humans to write). Configurations in YAML format will be converted to JSON and processed identically. When loading plugins, a default settings file in YAML defaults.yml if it exists, will be applied before the JSON default settings file (defaults.json).

Note: settings with names like "yes" and "no" do not work since JSON automatically converts them to True/False booleans as keys.

The IR/Configuration library, written in type-safe Python<sup>21</sup> reads in a sequence of IR snippets (YAML or JSON) in order to generate the database, a programmatic key-value store used by other parts of the Hammer methodology to query for information.

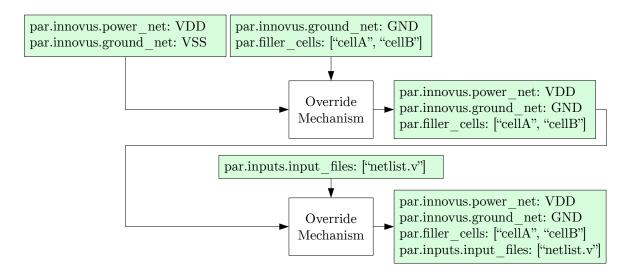

Figure 5: In the IR/Configuration library, IR snippets can override one another.

In order to facilitate re-use, IR snippets which occur later in the sequence of IR snippets will overwrite<sup>22</sup> key-value pairs if also defined in earlier snippets in the sequence. For example, a technology plugin can define parameters with defaults which can be overridden later on in a project IR snippet.

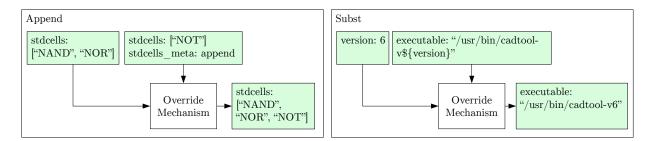

Figure 6: Two examples of meta directives in the IR/Configuration library. Meta directives allow IR snippets to use and modify information from previous snippets.

Meta directives allow IR snippets to use and modify information from previous snippets e.g. by appending to a pre-existing setting or using the value of another setting to create a new setting. When reading a setting, if the setting has an accompanying \_meta setting, it will be used when getting the setting. The \_meta setting's value can be either a string of one directive, or an array of multiple directives, processed in order.

The currently valid meta directives are:

$<sup>^{21}</sup>$ Via the mypy static type checker.

$<sup>^{22}</sup>$ While the implementation at the time of writing does not distinguish between intentional and unintentional overwriting

- append append the elements in the setting to the pre-existing setting.

- subst substitute any variable references (in the style of \${other\_setting\_key}) that appear in this setting with other variables. Note that referencing other settings that do not exist is an error.

- transclude replace the value of this setting with the content of the file at the path specified in this setting.

- json2list replace the value of this setting with a list parsed from a JSON representation stored in this setting.

- prependlocal prepend the local path of the config dict to this setting.

While user-defined meta directives are not currently supported by the IR/Configuration library as of the time of writing, they may be supported in a future release of Hammer.

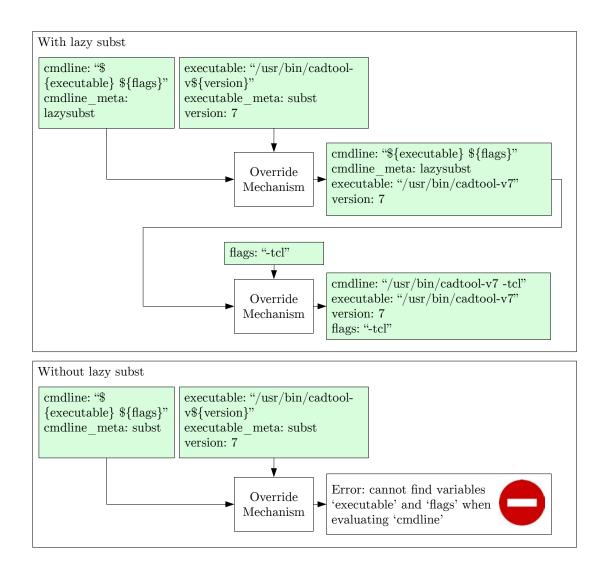

Lazy meta directives allow IR settings to forward-reference or re-use information in 'future' snippets, just as how meta directives allow IR settings to re-use information from previous snippets. Each 'regular' meta directive comes with a corresponding meta directive with the prefix lazy appended before its name. For example, subst has a corresponding lazy meta directive named lazysubst. When the IR/Configuration library processes a lazy meta directive, instead of executing the meta directive's action now, it will treat the setting and its meta setting as regular settings and then process them after all IR snippets in the sequence have been processed.

Lazy meta directives are especially useful when defining plugin defaults that are dependent on user settings which will only be available later in the substitution sequence. In particular, lazysubst is useful since the setting/template will not be substituted until all known configs have been bound.

Note that all lazy meta directives are single-stage - lazy meta directives cannot depend on other lazy meta directives.<sup>23</sup> For example, the following (YAML) IR snippet is not supported.

```

message: "${work} is fun"

message_meta: lazysubst

work: "taping out ${what}"

work_meta: lazysubst

what: "chips"

```

### 3.6 Tool Abstractions

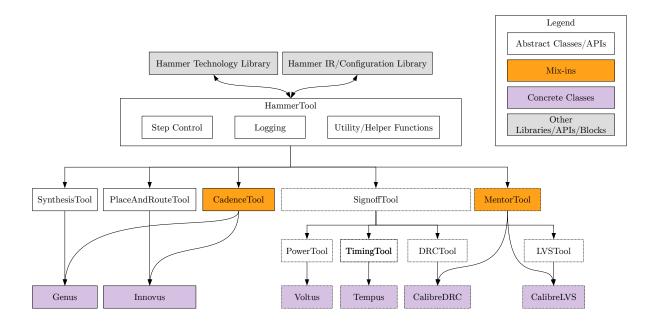

hammer-vlsi, the Hammer tool library, consists of a tree of abstract interfaces that provide APIs to perform various backend VLSI functions, including synthesis, place-and-route, DRC, LVS, voltage drop analysis, and timing analysis. hammer-vlsi uses the IR/Configuration library, as well as the Technology Abstraction library and is written in type-safe (via mypy) Python to be as lightweight as possible in order to enable users to write powerful plugins for Hammer in a modern programming language.

<sup>&</sup>lt;sup>23</sup>It may be supported in a future release of Hammer.

Figure 7: Lazy meta directives allow IR snippets to forward-reference or re-use information in 'future' snippets.

The core abstraction, HammerTool, provides a set of common infrastructural methods/APIs useful for writing CAD tool plugins. HammerTool contains functions for logging, querying the database of Hammer IR, stage control (see below), accessing the technology, and various helper functions including querying for PDK libraries, string manipulation, and shell functions.

HammerTool abstraction structures each CAD tool's flow as a series of steps. This makes it easier to have a fast iteration cycle by making it possible to selectively run steps in the tool without always having to run the entire step. In addition, in order to provide backwards compatibility with TCL, we developed a mechanism (referred to as TCL hooks in this document) to allow users to inject or override portions of the flow using higher-order functions operating on HammerTool in order to add, change, or suppress certain TCL generation behaviours in the program. For example, we include hooks to insert functions before or after a step (InsertPreStep/InsertPostStep), replace a step (ReplaceStep), resume before or after a

Figure 8: An overview of the Hammer tool abstraction (hammer-vlsi) in abstract APIs, mix-ins, concrete instances, and the relationships between them.

step (ResumePreStep/ResumePostStep) or pause the execution altogether.

After running, depending on the type of tool, each tool plugin populates a corresponding output snippet of Hammer IR containing the outputs from that run. For example, a synthesis run will populate outputs including the post-synthesis netlist and SDC constraints file.

```

@property

def steps(self) -> List[HammerToolStep]:

return [

self.init_design,

self.floorplan_design,

self.place_opt_design,

self.place_opt_design,

self.route_design,

self.opt_design,

self.write_design

]

```

CAD tool plugins are written as concrete classes which inherit from one or more of the abstract interfaces. Each plugin reads Hammer IR and emits the right TCL commands. Plugins can take full advantage of the the Hammer abstractions to minimize the effort required to write them. For example, Hammer comes with built-in functions for filtering from PDK libraries and processing them into the desired output format of the CAD tool (e.g. TCL or shell).

Finally, we can use Python's support for mixins<sup>[42]</sup> to "mix-in" common methods and functions for re-use between plugins. For example, many times CAD tools (say a synthesis

and a place-and-route tool) between the same vendor will share common startup/initialization commands (e.g. reading HDL, initializing libraries, etc). To help reduce code duplication and facilitate re-use between the two plugins, we can create a common class which contains helper functions for generating the common commands (e.g. MyVendorTool), and mix that into the actual tool classes (e.g. MySynthesisTool or MyPlaceAndRouteTool).

## 3.7 Technology Abstractions

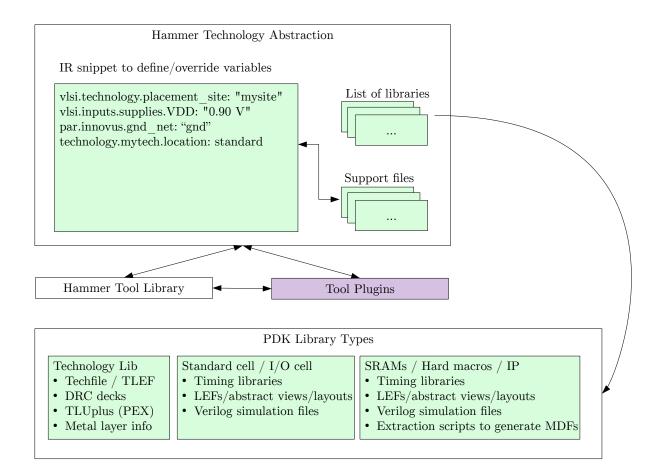

Figure 9: An overview of the three main components of the Hammer technology abstraction (hammer-tech).

A technology plugin in Hammer, implemented as a folder which the Hammer Technology library reads, consists of three main parts - 1) a defaults.yml or defaults.json snippet to define technology-specific IR settings, and to override any default tool or core (see Driver section) settings for this technology; 2) any support files necessary to support this technology properly - e.g. sometimes PDKs will have bugs or omissions which can be fixed with locally modified copies of files; 3) a list of libraries. The types of libraries supported include the technology itself (including technology LEFs, techfiles, DRC decks, etc) and standard cell/macro libraries, which include timing databases, Verilog simulation files, LEFs/Milkyway databases, and some scripts to extract data e.g to generate MDF files (see below) for use in other parts of the Hammer methodology.

At the moment, we have ported to the following technology nodes to the Hammer Technology abstraction:

- ST 28nm FDSOI

- TSMC 16nm FinFET

- SAED32

Having independent technology plugins is essential to making Hammer portable. Technology PDKs are highly sensitive and often cannot be easily shared across organizational boundaries. By decoupling technology concerns from the rest of the system, we can isolate this particular area of concern using an open-source API, allowing us to be more portable across technologies, projects, and organizational boundaries. By creating a technology abstraction, we aim to make it possible to encode solutions to physical design problems more abstractly with more potential for re-use.

We organized our technology plugin this way in noticing that certain technology nodes required overriding certain CAD tool behaviours in certain ways or supplying sets of data to the CAD tools. We encode our list of libraries as a JSON array. We read this array into our technology library, which parses the file into Python data structures. The technology plugin instance is then attached by hammer-vlsi (the Hammer Tool Abstraction) and made available to CAD tool plugins to query. For example, we provide functions to filter and process libraries in the technology to make it easy to look for information from the technology abstraction (e.g. all LEFs from standard cell/macro libraries) and emit it in the appropriate manner for the CAD tool.

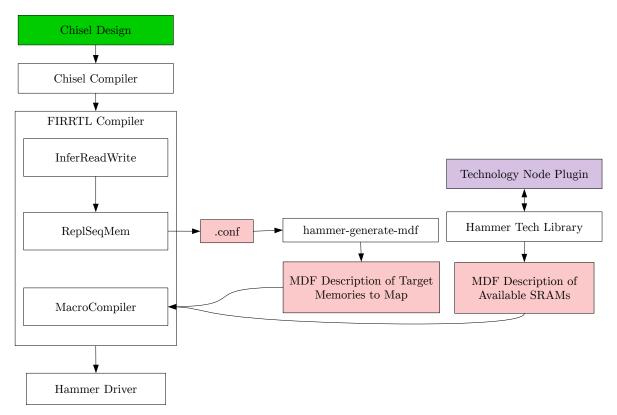

In addition to the above, the Hammer methodology features the macro description format (MDF), which is used to describe macros (type) and currently used most significantly for SRAMs (SRAM macros), though we plan to expand its use for other areas of backend VLSI (e.g. filler cells, I/O cells, etc). The description format is different for each type of macro - the most well-defined type of macro at the moment is the SRAM macro, which describes the width, depth, ports (names, read/write, masks, etc) of SRAMs. This format is currently used in the Hammer methodology by MacroCompiler, a pass which maps a generic Chisel/FIRRTL memory into a concrete implementation using a list of foundry SRAM macros. See the Agile RTL transformations and DSLs section for more about this.

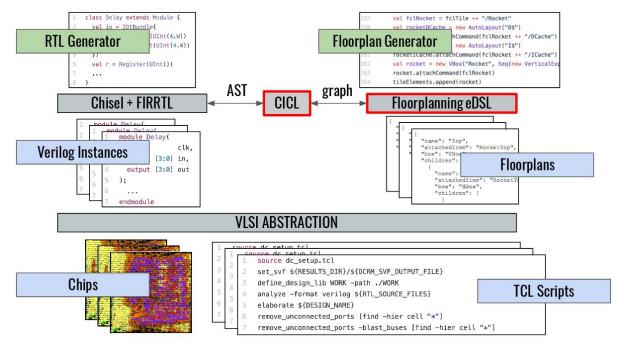

### 3.8 Agile RTL transformations and DSLs

As outlined in the overview, in order to be truly agile (fast, automated feedback loops), we would like to automatically generate physical design constraints using the FIRRTL circuit and any associated annotations. A related project at Berkeley, CICL (Circuit Introspection and Command Language) is an API/DSL embedded in Scala for manipulating RTL circuits represented in FIRRTL. It consists of a selection language, backed by a graph representation (as opposed to an AST). This enables us to develop agile transformations and DSLs by making it easier to query and manipulate the circuit while generating physical design information.

Figure 10: An example of using MDF to map abstract memories to technology-specific memories.

We want to tie the physical design constraint generation to the RTL generators due to powerful generators which can radically change RTL with parameter changes like rocket-chip, dsptools, etc.

For example, an operation that would be easily done in FIRRTL/CICL but tedious/nonreusable in TCL would be a transformation which takes half of an asynchronous FIFO and moves it to a different module with a different clock domain.

Should these transforms operate at the FIRRTL level? While there is theoretically nothing preventing you from writing Chisel code which generates Hammer IR, writing these transformations in FIRRTL allows you to address and manage circuit elements that didn't exist at the Chisel level yet, like memory macros generated by the MacroCompiler pass. In addition, not all designs are used in ASIC contexts, so having Chisel generators emit physical design constraints directly limits re-use.

MacroCompiler is a pass that takes FIRRTL with abstract memories. Using MDF information generated by Hammer from the technology plugin, it maps the abstract memory to an implementation using the foundry memories.

There are two main scenarios in terms of generating physical design information from Chisel/FIRRTL generators. The first is constraints that don't depend on technology/chip project information. In this case, we can encode these as FIRRTL annotations and use a simple FIRRTL pass to consume them and generate the appropriate Hammer IR. The second case involves constraints that depend on both the source RTL generator and technology/project

information. Examples of this include floorplanning (the same chip can be floorplanned in different ways to achieve different QoR), pad frame generation (depends on the technology as well as the pad/bump output), and clock/power gating constraints (requires insertion of power gating cells which depend on the technology).

As part of our efforts to explore the second scenario, we created an agile floorplan DSL to enable us to write floorplan generators corresponding to FIRRTL circuits which were portable and could emit physical design placement constraints in the Hammer IR.

Figure 11: Floorplan generation - an example of a scenario where generation of physical design constraints requires both upstream knowledge from the RTL generator but also downstream technology/project information.

The floorplan DSL is designed to enable users (hardware engineers) to write re-usable layout generators corresponding to RTL. The floorplan DSL consists of three major portions - a geometry API, connections to CICL and FIRRTL for interfacing with the RTL, and a numeric solver to concretize the design with numbers to enable tapeout.

We provide a variety of geometry constructs to enable the construction of layouts. These constructs can be nested within one another and are independent of any numerical co-ordinates to enable re-use of layouts across different technologies and chip projects.

These constructs, which facilitates relative placement, include:

- HBox tile the given elements horizontally.

- VBox tile the given elements vertically.

- AutoLayout do not specify any particular constraints to the backend tools for the module in this box.

- Expander create a space/separate the given modules as much as possible.

• HardMacro - represents a hard macro, which has a fixed size but can vary in position.

Each geometry element can be attached to a module at the RTL level via a CICL Path, a selector for exactly one hardware component (in this case, a module). Not every geometry element is required to have a CICL Path. For example, a VBox could be attached to a module and have two sub-elements to floorplan parts of that module and an expander in between. In this case, the expander would not need a RTL module attached to it.

Notably, the RTL hierarchy does not need to correspond to the physical hierarchy. For example, consider a design with a Rocket in-order core with a Hwacha vector processing unit. Hwacha could exist as a submodule of Rocket while in the physical hierarchy, Hwacha and Rocket could be two parallel modules.<sup>24</sup>

In the DSL, geometry elements are connected to CICL's hardware module selectors via the attachPath() function.

Finally, in order to tape out a chip, a floorplan needs to be resolved into concrete numbers (position and dimensions). Since the exact co-ordinates for a particular module or layout will differ widely between different process nodes, we want to enable layout generators to be re-used as much as possible. In order to enable this, numbers are specified separately in a second stage as opposed to being required when the layout is created.

In the DSL, geometric elements have numbers entered to them via setDimensions() and setCoordinates(). We can instruct the DSL to resolve all the co-ordinates in the system (e.g. for visualization or export to backend tools) via resolveAll().

## 4 Evaluation

#### 4.1 Sample Flows

git clone git@github.com:ucb-bar/hammer-examples.git

cd hammer-examples

git submodule update ---init ---recursive

# Edit sourceme.sh for the site setup

source sourceme.sh

Simple Adder Flow Given a simple 2-bit adder written in Verilog:

```

module adder (

input [1:0] a,

input [1:0] b,

output [1:0] c

);

assign c = a + b;

endmodule

```

<sup>&</sup>lt;sup>24</sup>Synthesis might shuffle or flatten the hierarchy around. Currently it is the responsibility of the CAD tool plugin to ensure that floorplanning paths are valid and exist after synthesis.

Running synthesis and place-and-route using Hammer is trivial:

hammer-vlsi syn-par -o output.json -v adder.v ---top adder

```

synthesis.inputs.input_files: ["SodorTile.v"]

synthesis.inputs.top_module: "SodorTile"

vlsi.inputs.clocks:

- name: "clock"

period: "50 ns"

uncertainty: "1 ns"

vlsi.inputs.placement_constraints:

- path: "SodorTile"

type: "toplevel"

x: 0

y: 0

width: 1500

height: 1500

margins:

left: 100

right: 100

top: 100

bottom: 100

- path: "SodorTile/core/d/csr"

type: "placement"

x: 600.0

y: 600.0

width: 30.0

height: 200.0

- path: "SodorTile/memory/async_data/bleh"

type: "hardmacro"

x: 30.0

y: 30.0

width: 100.0

height: 200.0

```

# Hierarchical example with manually specified placement constraints for each synthesis.inputs.input\_files: ["HierarchicalWriter.v"] synthesis.inputs.top\_module: "HierarchicalWriterTop" vlsi.inputs.hierarchical.config\_source: manual vlsi.inputs.hierarchical.manual\_modules:

```

- HierarchicalWriterTop:

- HierarchicalWriter2

HierarchicalWriter2:

- HierarchicalWriter1

vlsi.inputs.hierarchical.manual_placement_constraints:

- HierarchicalWriterTop:

- path: "HierarchicalWriterTop"

type: "toplevel"

\mathbf{x}: \mathbf{0}

y: 0

width: 2600

height: 1500

margins:

left: 50

right: 50

top: 50

bottom: 100

- path: "HierarchicalWriterTop/SRAM1RW512x32"

type: "hardmacro"

x: 1198

y: 1200

width: 204.684

height: 247.541

- path: "HierarchicalWriter2/HierarchicalWriter2"

type: "hardmacro"

x: 50

y: 100

width: 1200

height: 1000

- path: "HierarchicalWriter2/HierarchicalWriter2_1"

type: "hardmacro"

x: 1300

v: 100

width: 1200

height: 1000

- HierarchicalWriter2:

- path: "HierarchicalWriter2"

type: "toplevel"

\mathbf{x}: \mathbf{0}

y: 0

width: 1200

height: 1000

margins:

left: 50

```

```

right: 100

top: 100

bottom: 100

- path: "HierarchicalWriter2/SRAM1RW512x32"

type: "hardmacro"

x: 498

y: 650

width: 204.684

height: 247.541

- path: "HierarchicalWriter2/HierarchicalWriter1"

type: "hardmacro"

x: 50

y: 100

width: 500

height: 500

- path: "HierarchicalWriter2/HierarchicalWriter1_1"

type: "hardmacro"

x: 600

y: 100

width: 500

height: 500

- HierarchicalWriter1:

- path: "HierarchicalWriter1"

type: "toplevel"

\mathbf{x}: \mathbf{0}

y: 0

width: 500

height: 500

margins:

left: 50

right: 50

top: 50

bottom: 50

- path: "HierarchicalWriter1/SRAM1RW512x32"

type: "hardmacro"

x: 60

v: 60

width: 204.684

height: 247.541

vlsi.inputs.clocks:

- name: "clock"

period: "50 ns"

uncertainty: "1 ns"

```

Porting to a Different CAD Tool Vendor Given two snippets (use\_synopsys.json and use\_cadence.json):

```

use_cadence.json

{

"vlsi.core.synthesis_tool": "genus",

"vlsi.core.par_tool": "innovus",

. . .

}

use_synopsys.json

{

"vlsi.core.synthesis_tool": "dc",

"vlsi.core.par_tool": "icc",

. . .

}

Switching is as easy as going from:

hammer-vlsi syn-par -o output.json -v adder.v ---top adder \\

-e use_synopsys.json

To:

hammer-vlsi syn-par -o output.json -v adder.v ---top adder \\

-e use_cadence.json

```

**Porting to a Different Technology** Create a JSON/YAML IR snippet to reference the appropriate technology (YAML example below) and as before, use **-e** to point to the new technology.

use\_mytech.yml

vlsi.core.technology: my\_tech

vlsi.core.technology\_path: ["path\_to\_my\_tech"]

vlsi.core.technology\_path\_meta: append

```

hammer-vlsi syn-par -o output.json -v adder.v ---top adder -e use_mytech.yml

```

export HAMMER\_ENVIRONMENT\_CONFIGS="/path/to/file/with/local/settings.json"

## 4.2 EAGLE

EAGLE is an 8-core (Rocket in-order core+ Hwacha vector unit), 4-cluster SoC with 5 SerDes lanes in TSMC 16nm being taped out at the BWRC and ADEPT lab at UC Berkeley. Our

preliminary estimates for QoR include power consumption in the range of 6-7 watts, area of 5mm x 5mm, and a maximum clock rate of 980 MHz.

A successor to Hurricane- $2^{25}$  and CRAFT in terms of design methodology, EAGLE provided us with an opportunity to explore the benefits of the new Hammer methodology. We took the information encoded in previous 16nm CRAFT tapeouts and used it to write a new, re-usable 16nm technology plugin for Hammer. This plugin is in fact being used by multiple 16nm projects here at Berkeley, highlighting its re-usability.

EAGLE (eagle-vlsi) uses the CLIDriver abstraction to modify the default Hammer flow abstraction, since we weren't creating an entirely custom application/generator. Most of the customizations are via TCL hooks, which allowed us to incrementally use Hammer, increasing adoption and usability, especially while hooks were being added. For example, we used TCL hooks to implement a hierarchical flow while the Hammer hierarchical API was still being developed. Likewise, we currently use TCL hooks for extra VLSI/physical design features, like RDL routing, filler cells, tap cells, etc. This is consistent with our philosophy of incremental adoption. In fact, due to its open source nature, certain parts of Hammer used by EAGLE designers were found to be easier to use than competing commercial tools like flowtool.

Note that neither the hammer nor hammer-cad-plugins repo was forked during this tapeout, a first after many previous tapeouts involved wholesale forking/copying/modifying directly upstream flows and generators. For example, the Hurricane-2 tapeout repo was a fork of the rocket-chip generator with a heavily customized/mutated Synopsys RM copied/merged into it.

#### 4.3 EE194/290C

EE194/290C is a special topics class at UC Berkeley designed to teach advanced undergraduates who have never taped out before a hands-on experience in taping out a chip. Last iteration of the course, we used Synopsys tools and a traditional-style flow<sup>26</sup>. As in the flow for EAGLE, we never forked hammer or hammer-cad-plugins.

To give an idea of how much time we saved using re-usable libraries/frameworks/abstractions:

- Only 3 hours to initial GDS flow, ST28, first time using Cadence flows. Some debugging due to LEF files. No SRAMs yet.

- About 2 hours to investigate results and create power grid.

- About 5 hours (mostly editing paths in .tech.json files) to porting 10-layer 2.7 PDK to 8-layer 2.9 PDK (modulo the foundry dropping .lib files in some libraries)

- 3 hours porting new SRAMs and generating them with MacroCompiler.

<sup>&</sup>lt;sup>25</sup>Unfortunately no publication is available yet at the time of writing.

<sup>&</sup>lt;sup>26</sup>We attempted to use PLSI but it devolved into a traditional flow because it was difficult to customize the flow without effectively forking it into a separate repo.

• 5-6 hours to understand + implement I/O cells and implement usage in Innovus.

# 5 Related Work