# Scalable RF Receivers for Large Antenna Arrays

Konstantin Trotskovsky Elad Alon, Ed. Ali Niknejad, Ed. Ilan Adler, Ed.

## Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2020-188 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2020/EECS-2020-188.html

December 1, 2020

Copyright © 2020, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## Scalable RF Receivers for Large Antenna Arrays

by

Konstantin Trotskovsky

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Elad Alon, Chair Professor Ali M. Niknejad Professor Ilan Adler

Fall 2018

Scalable RF Receivers for Large Antenna Arrays

Copyright © 2018

by

Konstantin Trotskovsky

## Abstract

#### Scalable RF Receivers for Large Antenna Arrays

by

Konstantin Trotskovsky

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

## University of California, Berkeley

Professor Elad Alon, Chair

The ongoing exponential mobile traffic increase is continuing to push the requirements of wireless communication systems. Currently in dense urban areas the major limitation to the capacity of wireless links is interference between different users. Massive MIMO is a promising technology to address this challenge, where directional spatial beams are formed by an antenna array on a base station, each serving a different user. This concept is currently verified using commercial general-purpose analog hardware, with power consumption in the kW range for large arrays.

This thesis focuses on energy-efficient RF receiver design for Massive MIMO systems. In order to be energy-efficient, the system requirements for a large antenna array receiver are different from a conventional single-antenna receiver. We use the fact that the noise of each receiver is uncorrelated across the array, so we can save power by using receivers with larger noise, while still meeting the link budget requirements. However, receiver linearity cannot be relaxed due to the digital beamforming used in the system.

To address these challenges a novel RF receiver architecture is proposed, using a mixer-first approach with mixer switch resistance larger than  $50\Omega$ . Configurable mixer and baseband Gm sizes allow the receiver to trade noise figure for power consumption and use the same receiver for various array sizes and array-level noise specifications. Harmonic recombination is performed early in the signal path, enabling rejection of harmonic blockers up to -10dBm of power.

This architecture was implemented in a first chip prototype. Scalable element noise figure results in sub-2.5 dB array-level noise figure with 16 to 64 antennas and <368 mW total power consumption, for a frequency range of 0.25-1.7GHz.

In the second chip we perform an optimized design using the Berkeley Analog Generator (BAG). The proposed generator design methodology produces instances with optimum power consumption for a given noise figure specification. An instance of this generator is implemented in the chip, showing power consumption improvement of 50% and wider frequency range of 1-6GHz compared to the first chip.

# Contents

List of Figures

List of Tables

#### Acknowledgements

I am very grateful to many people in Berkeley that helped me through my PhD here. First I would like to thank my advisors, professors Elad Alon and Ali Niknejad. I feel very fortunate to work with them. The weekly meetings with Elad were something that I was expecting for the entire week. I was always impressed by Elad's ability to switch to a new solution and throw away the old one, no matter how much did we invest in it in the past. His levels of energy and optimism are something to aspire for me. I am very grateful to Ali for his offer to be co-advised by him. Ali provided a new insight and a different perspective to the problems that I was facing. I also had a great time GSI-ing 242A and 105 with him. Teaching was a hard experience for me in the beginning, and Ali was very helpful and supportive.

I would also like to thank professor Bora Nikolić for taking part in my quals committee and helping out during the project meetings that we had over the years. Thanks to professor Paul Wright for serving in my quals committee and providing feedback. Special thanks to professor Ilan Adler for being a member in my dissertation committee, even though I asked him so late.

The students in BWRC make this place very special. I feel that a large part of what I learned in the past 5 years was from interacting with them. In the first eWallpaper project we started as a team of inexperienced students, and this chip would not be possible to build without the effort of all of them. I feel lucky to work with Amy Whitcombe on this project and especially during the measurements and paper writing stage. I thought that I am a hard-working person that pays attention to details, but working with Amy had set a new bar for me. Her work ethics, willingness to help and positive attitude made our work a great experience. During the chip and board design I was fortunate to work with Pengpeng Lu. Pengpeng's patience and sense of humor made many hours that we spent together both funny and productive. Many thanks to Greg LaCaille who helped me with various circuit problems and had so many great ideas. Antonio Puglielli was a brilliant guy who made every problem look easy. Greg's and Antonio's help with top-level integration made this tapeout possible. Thanks to Nathan Narevsky, Eric Chang and Zhongkai Wang for their help and advice. Thanks to Greg Wright from Nokia who was very enthusiastic about the project and provided many helpful inputs.

In my second project I had to learn how to use BAG, and I would like to thank Eric Chang for being patient and helpful answering all my questions. In the early stages I had many questions and Eric was always patient and quick to respond. I am very happy that I got to know Marko Kosunen and worked with him on the chip flow and integration. His continuous efforts to make the chip work and meet the deadline made this chip possible. I learned a lot from Marko, both on the technical side and on the problem solving methodology. Thanks to Nathan, Zhongkai and Pengpeng for their help with the chip design.

I was lucky to be involved in two research groups of my two advisors and get to know many smart people. Thanks to Seobin Jung, Yida Duan, Jaeduk Han, Bonjern Yang, Nick Sutardja, Emily Naviasky, Ali Moin, Steven Callender, Andrew Townley, Nai-Chung Kuo, Lorenzo Iotti, Nima Baniasadi, Bo Zhao, Sashank Krishnamurthy, Yi-An Li, Luya Zhang, Ali Ameri and Matthew Anderson. Outside of my research groups, I would like to thank Luke Calderin, Sameet Ramakrishnan, Stevo Bailey, Mirjana Videnović-Mišić, Rachel Hochman, Amanda Pratt, Nandish Mehta, Sharon Xiao, Sidney Buchbinder, Filip Maksimovic, Krishna Settaluri and John Wright.

The staff members make BWRC a great place to work. Special thanks to Candy Corpus who was extremely friendly and helpful in solving any administrative problem. Candy's optimism and hard work make BWRC a great place to be in. Thanks a lot to Brian Richards who was very helpful and optimistic during the hard tapeout times. James Dunn was very quick to respond to any problem, and made sure that it is resolved no matter how busy he was. Fred Burghardt made the lab a great place to work and was always happy to help. Many thanks to Anita Flynn for her help with PCB design. Thanks to Ajith Amerasekera, Melissa Trevizo, Amber Sanchez, Olivia Nolan and Sarah Jordan for their help.

I would like to thank my family, my mother Elena and sister Maya. Being far away for a long time was a challenge for all of us, and I am very grateful to them for their support during all these years. My last and great thanks is to my fiancée Anna, who made my life far better since we met. I am looking forward to our future life together.

## Chapter 1

# Introduction

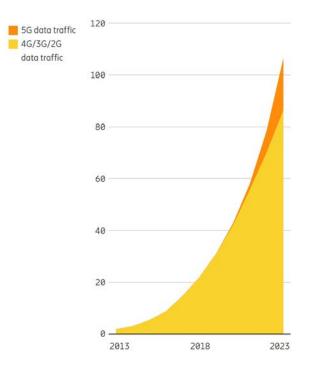

We are living in a time of exponential mobile traffic increase. In the past 5 years the yearly mobile traffic increased by 55-70% per year [?]. This trend is expected to continue at least in the next 5 years, projected in Figure ??. The total mobile traffic is expected to grow by a factor of 5 in this period.

Figure 1.1. Global mobile data traffic (exabytes per month). Exponential global traffic increase over time is projected.

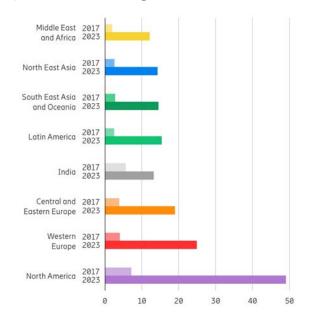

There are two contributors to the total mobile traffic increase. First, the number of mobile devices is growing. Second, and more importantly, the mobile traffic per device is growing as well. The projection is that from 2017 to 2023 the number of worldwide smartphones will increase by

8% per year, while the mobile traffic per smartphone will increase by 31% per year [?]. This trend happens all over the world, as illustrated in Figure ??.

Figure 1.2. Mobile data traffic per active smartphone (gigabytes per month). Data traffic increase per user is exponential all over the world.

To addess this increase in mobile traffic, the 3rd Generation Partnership Project (3GPP) created the specifications for Long-Term Evolution (LTE) in mobile communication. Approximately every year a new release is made enabling higher data rates and denser deployments. We now see a transition from a 4G LTE standard to 5G, when the current Release 15 is the first to have 5G specifications [?]. However, as shown in Figure ??, the transition between 4G and 5G will take many years, and in 2023 only about 20% of the data traffic will be through the 5G standard.

In the past decades many different techniques were used to address the exploding demand for data traffic. Two main challenges should be addressed: increasing the data rate per user, and supporting larger number of users simultaneously. We will briefly discuss them and see that continuing to improve them is becoming more and more difficult.

Ingoring other users, the main techniques to improve the data rate per user are increased bandwidth, improved channel coding and using higher constellations.

- Bandwidth is the most straightforward way to increase the possible data rate. However the frequency allocation in RF frequencies is very dense and extremely expensive in RF frequencies. One possible direction that is under consideration for 5G is starting to use mm-wave frequencies where more bandwidth is available. This creates new challenges that we will discuss later.

- Channel coding can enable the usage of smaller SNR for the same received data rate. Modern coding schemes are already very close to Shannon's limit, leaving very little room for improvement in the required SNR.

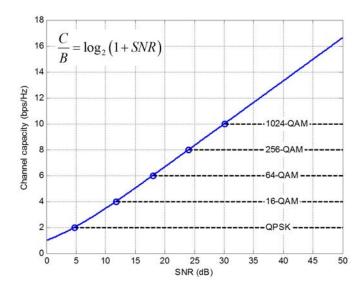

- **Higher constellation** enables larger channel capacity for the same bandwidth. However since the channel capacity is logarithmic with the SNR, there are diminishing returns in the chan-

nel capacity when improving SNR (Figure ??). In addition, the hardware implementation becomes extremely challenging for higher constellations.

Figure 1.3. Shannon's limit  $SNR = 2^{C/B} - 1$  makes it impractical to address exponential channel capacity growth by more complex constellation. For example, 3dB (2x) capacity from 8bps/Hz to 16bps/Hz requires 24dB (250x) higher SNR.

In less dense rural areas these are the main challenges. However, in dense urban areas large numbers of users need to be served simultaneosly. Here two main questions arise: how to share the wireless channel between different users, and how to prevent inter-user interference. Several techniques have been used to address these issues: Frequency-Division Multiple Access or FDMA (allocating different frequencies to different users), Time-Division Multiple Access or TDMA (allocating different time slots to different users), and Code-Division Multiple Access or CDMA (allocating different coding schemes to different users). The main limitation of these techniques is that they share the entire network capacity between the users, so adding more users will result in reduced user capacity.

To address these issues, spatial multiplexing is a promising direction. Multiple input-multipleoutput (MIMO) technology is already using multiple antennas on both receive and transmit sides, taking advantage of several multi-path propagations. Multi-user MIMO (MU-MIMO) offers even higher capacities due to simultaneous communication to different users.

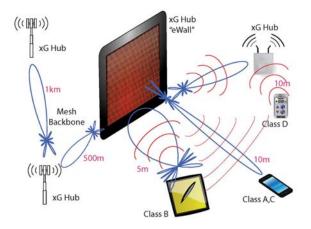

This approach is part of the Berkeley Wireless Research Center (BWRC) vision of a universal next-generation (xG) network [?], summarized in Figure ??. A large antenna array access point (xG Hub) provides connectivity to many devices using highly directional beams. The large array can support various communication standards, devices and ranges. Beamforming implements spatial selectivity and enables spectrum re-use and simultaneous communication to many users.

This vision has a lot in common with the recently popular Massive MIMO concept. The key idea of Massive MIMO is the use of a large number of base station antennas and much smaller number of users. Therefore, using beamforming, the large array can form a beam to every user, greatly improving the interference between the users and re-using the spectrum.

Several massive MIMO systems have been recently demonstrated in academia and industry.

Figure 1.4. Berkeley Wireless Research Center (BWRC) xG ( $x \ge 5$ ) vision for next generation wireless standard.

Their main goal was to explore the system performance rather than to implement an efficient hardware. For the RF transceivers off-the-shelf components were used. The Ngara system [?] operated at 806MHz for the uplink and 638MHz for the downlink and used discrete components. The Argos [?] and ArgosV2 [?] systems operated at the 2.4GHz ISM band and used Maxim 2829 WiFi transceiver, while ArgosV3 [?] used a wideband Lime Microsystems LMS7002M transceiver operating at 50MHz-3.8GHz. Lund University [?], National Instruments [?] and Samsung [?] have demonstrated systems using NI USRP RIO Software-Defined-Radio transceivers, operating at 3.7GHz, 50MHz-6GHz and 3.4-3.6GHz respectively.

These systems have 32-160 antennas and serve 10-16 users. The off-the-shelf RF transceivers used consume 100s of mW, making the array RF power consumption lie in the kW range. This power consumption is already huge, and will be even larger if more antennas are used to serve more users.

So far no custom-design RF IC receivers were demonstrated in Massive MIMO systems. The goal of this work is to implement an integrated energy-efficient RF receiver tailored for Massive MIMO applications. In Chapter ?? we discuss the RF receiver design considerations with an emphasis on the differences between a receiver for large antenna array and a more common single-antenna receiver. In Chapter ?? we describe the circuit architecture to address the array requirements and show a first version implementation of a chip for Massive MIMO applications. Chapter ?? describes the second chip implementation, fully designed using Berkeley Analog Generator (BAG) and optimized for energy-efficiency performance. Finally, Chapter ?? summarizes the thesis.

## Chapter 2

# System Design Considerations

In this chapter we will discuss the RF receiver design considerations for a large antenna array. Designing an RF receiver for a single-antenna system is a well-known procedure, but the fact that the receiver is intended to be used in a large array changes the specifications for the receiver. In other words, we will show what can we change in the RF receiver design in order to achieve the overall array performance in an energy-efficient manner.

The design considerations details of the entire Massive MIMO system can be found in [?] and [?]. Here we will focus on the implications on the RF receiver part of the system. A detailed description of the ADC design considerations is presented in [?].

## 2.1 Noise and energy-efficiency

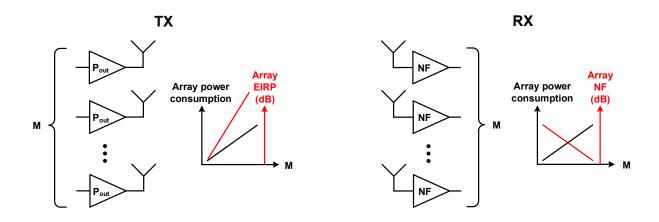

To understand the impact of the receiver noise performance on the overall array energy efficiency, we will compare the transmitter (TX) and the receiver (RX) behavior in large arrays. This is summarized in Figure ??.

We will assume that we have an array of M antennas, each has an output power of  $P_{out}$  for the TX side and a noise figure of NF for the RX side. Then both for TX and RX the total array power consumption is proportional to M:

$$P_{array} \propto M$$

(2.1)

On the TX side with beamforming the main beam points to the user direction, and we have spatial summation of the electromagnetic waves. So the electric fields are summed in the air, which is equivalent to voltage summation of the transmitter outputs. Thus when we have M transmitters with output power of  $P_{out}$ , the array equivalent isotropic radiated power (EIRP) is proportional to  $M^2P_{out}$ :

$$EIRP_{array} \propto M^2 P_{out} \tag{2.2}$$

It means that the ratio of the EIRP to the array power consumption is proportional to the

Figure 2.1. The impact of the array elements on the overall TX and RX array performance.

array size:

$$\frac{EIRP_{array}}{P_{array}} \propto M \tag{2.3}$$

The implication is that the overall TX energy efficiency can be improved when using the array. If we need a certain array EIRP to fulfill our link budget, we can reduce the overall array TX power consumption by using more array elements, each having lower output power. The array power consumption cannot be reduced indefinitely due to overhead power that does not scale with the array size, resulting in optimum array size for given array EIRP, transmitter efficiency and overhead power [?]. Generally speaking, for a large array we need efficient low output power transmitters with low overhead power.

However, on the RX side the analysis is different. The noise added by each receiver in the array is uncorrelated across the antenna elements. Thus while the output signal power is proportional to  $M^2$  (same as in the TX case), the output noise power is proportional to M. This is illustrated in Figure ?? for M = 4 elements.

Figure 2.2. Illustration of uncorrlated noise averaging for M = 4 array elements.

Consequently the array SNR is proportional to M, or equivalently:

$$NF_{array} = \frac{NF}{M} \tag{2.4}$$

We should note that this analysis is simplified as it ignores the uncorrelated noise from the environment. However, the result is unchanged, as shown in [?]. Hence for the array we have:

$$\frac{1}{P_{array}NF_{array}} = const. \tag{2.5}$$

The implication here is that the overall RX energy efficiency cannot be improved with the array. Even in an ideal case where the element power consumption is inversely proportional to its noise figure, when we add more elements to the array the overall power consumption stays constant. This is equivalent to a large receiver being split into M smaller receivers, each with smaller power consumption and higher noise figure, so the overall performance stays the same. Hence on the RX side we need to be able to build energy-efficient receivers that can have high noise. In other words, we would like to implement a receiver with power consumption inversely proportional to its noise figure across a wide range of noise figures.

From RX standpoint we should distinguish between two link-budget regimes:

- 1. Link-budget-limited regime, where a single RX element is not sufficient to meet the desired link budget. In order to meet the link budget, we need to use an antenna array to improve the SNR by the RX array gain. In this regime we should spend extra power consumption on the antenna elements to fulfill the system requirements.

- 2. Non-noise-limited regime, where a single RX element is sufficient to meet the desired link budget. An antenna array can be used in order to implement directional beamforming to different users rather than to meet the link budget requirements. Then, in order to avoid extra power consumption, we can use receivers with higher noise figure and lower power consumption, to keep the overall array power consumption constant.

We can see that in the two regimes we should have different implementations of the RF receiver. In the link-budget-limited regime, a low-noise receiver should be designed, and its noise is effectively further improved by the array gain. This is the case in many mm-wave systems, where lower output powers, higher noise figures and larger path losses may require an array to meet the link budget. In non-noise-limited regime, higher noise and lower power receivers should be designed in order to save the overall array power. This is the case in many sub-6GHz systems.

In our work we will focus on sub-6GHz receivers in non-noise-limited regime. To the best of our knowledge, this category of receivers has not been studied in the past and it is important for future Massive MIMO systems, especially when the array size is very large.

To summarize, in the non-noise-limited regime, if the link-budget requirement for the receiver array is  $NF_{array}$ , then from equation ?? the spec for the element noise figure is M times higher, or in dB:

$$NF[dB] = NF_{array}[dB] + 10\log_{10}M$$

(2.6)

## 2.2 Linearity

Several linearity metrics are used in RF receivers. RF chain compression by the desired signal (and specifically the 1dB compression point  $P_{-1dB}$ ) is used to characterize the SNR degradation

when the desired signals at the input of the receiver become large. The weak-nonlinearity intermodulations (and specifically second and third order intercept points IP2 and IP3) characterize the impact of nearby blockers with moderate input powers on the SNR of the desired signal. Finally, large nearby blockers cause the receiver gain of the desired signal to compress and the thermal noise floor to increase, both degrading the desired SNR.

When analyzing the impact of the array on the overall linearity performance, we observe that the inband linearity (the path of the signal) is unaffected by the fact that we are using an array. This is due to the fact that nonlinearity is a systematic feature of the array elements, so to first order each element has the same nonlinear characteristics. However, the blocker impact is very different. The main idea of Massive MIMO systems is to cancel the blockers and create directional beams that will enable larger signal-to-interferer ratios. Hence from the analog design standpoint, an important question is how exactly the blockers can be cancelled.

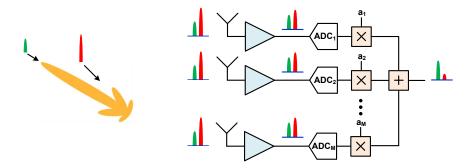

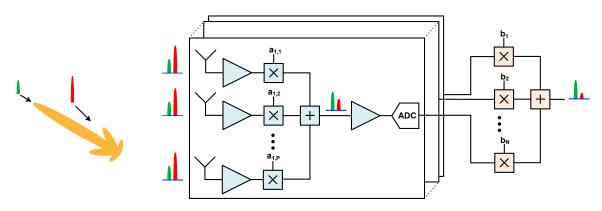

The first approach is digital beamforming, as shown in Figure ??. Each antenna element has an ADC and the digital signals are beamformed to cancel the blocker. Note that  $a_k$  are complex multipliers, acting on both I and Q outputs. This architecture is easy to build since we don't need to implement analog multiplications (phase shifters and VGAs). In addition, this picture shows a simple case of a single user, when only one beam is used. As the number of users grows we can keep the analog receivers unchanged, and add more columns of digital multipliers, which simplifies the overall system design. However, this architecture is challenging from linearity standpoint. Each analog receiver has to handle the full blocker strength, since the cancellation occurs only in the digital domain after the ADCs.

Figure 2.3. Digital beamforming, where the blockers are cancelled at the digital domain (pink) while the analog domain (light blue) must handle the full blocker power.

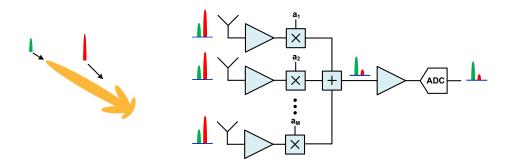

Another approach is analog beamforming, as shown in Figure ??. Here the analog signals are beamformed early in the RF chain before the ADC. The analog multiplication is implemented as a combination of phase shifters and VGAs, and can be performed in RF, LO, baseband or a combination of these. This approach relaxes the linearity requirements from the analog stages located after the beamforming since the blocker levels there are substantially lower. Hence from a linearity standpoint, it is advantageous to perform the beamforming earlier in the RF chain (for example, in RF/LO rather than in base-band). However, scaling this architecture to support many users results in duplicating the beamforming analog hardware, which makes the full system design much more complicated.

Finally, the last approach is hybrid beamforming, shown in Figure ??. Here we have both analog and digital blocker cancellation. The M antennas are split into groups of P antennas, each

Figure 2.4. Analog beamforming, where the blockers are cancelled at the analog domain (light blue) while the digital domain operates with reduced blocker levels.

group performing analog beamforming with a single ADC. The P digital signals are then digitally beamformed to create the final beam. The idea here is that each group formes a partial beam that cancels some portion of the blockers, relaxing the linearity requirements from the following analog stages.

Figure 2.5. Hybrid beamforming, where the blockers are cancelled in part in the analog domain (light blue) and in part in the digital (pink) domain.

The choice of the different beamforming architectures depends mainly on the speed of the digital data and its power consumption. In RF frequencies the channel bandwidth is relatively low (usually tens of MHz), so we can build a digital beamforming system with moderate digital power consumption. However in mm-wave systems the channel bandwidths are several GHz and the digital power consumption becomes very large, so some amount of analog beamforming is necessary. Hence mm-wave massive MIMO systems are typically using hybrid beamforming. Analog beamforming is too complicated for multi-user MIMO systems, and is mainly used in traditional phased array applications where a single beam is formed.

In our system we operate in the sub-6GHz frequency range with channel bandwidths of tens of MHz. Hence the digital power consumption is moderate, and we can use digital beamforming to simplify the overall system and enable easier support of many users. However, the implication is that the analog receiver part has to be very linear to support large blockers before being digitized by the ADCs.

## 2.3 Chip specifications

After a general discussion about the noise and linearity implications on a receiver design in a large array system, we will summarize the specifications for our first receiver prototype. We are not targeting any specific application, like WiFi or LTE, but rather want to build a system that can be used for various applications, as shown in the xG vision in Figure **??**. Hence we can briefly look at the current communication standards like WiFi and LTE, and try to derive the initial specifications for our system.

#### 2.3.1 Frequency range and bandwidth

The cellular LTE standard supports 1.4, 5, 10, 15, and 20 MHz channel bandwidths [?]. It also supports carrier aggregation, in which up to 5 bands can be used simultaneously to enhance bandwidth. Smaller bandwidths are supported for legacy compatibility with existing standards like GSM and CDMA, while larger bandwidths are used to support higher data rates for modern wireless systems. LTE operates over many of frequency bands, from 700MHz up to 3.8GHz.

The wireless local area network (WLAN) protocol or Wi-Fi is the most common protocol providing wireless internet access to laptops and smartphones. Since its introduction in 1997 as the IEEE 802.11 standard, many updates to the standard have been implemented to support higher data rates and more frequency bands to address the increasing demand. WiFi operates in industrial, scientific and medical (ISM) and Unlicensed National Information Infrastructure (U-NII) bands. Today most WiFi devices are operating in the 2.4GHz band of 2.412-2.484GHz (802.11b, 802.11g, and 802.11n) and the 5GHz band of 5.15-5.875GHz (802.11a, 802.11n, and 802.11ac) [?]. In addition, 802.11ad is using 60GHz bands. All 2.4GHz and 5GHz standards support 20MHz channel bandwiths, while 802.11n and 802.11ac also support 40MHz channels. The 802.11ac standard can also support 80 and 160 MHz bandwidths.

For our chip we will support a broad 700MHz to 6GHz range to cover all possible LTE and WiFi bands, as well as other possible bands in between. In terms of channel bandwidth we will use 20MHz channels (10MHz base-band bandwidth) for our chip. Supporting several channel bandwidths is possible, and was demonstrated in [?], [?] and [?], but the overhead required to do so is large and not required to illustrate our research goals.

#### 2.3.2 Blocker tolerance

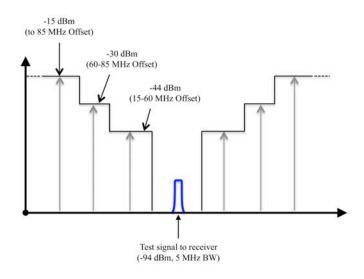

As we have seen in section ??, when we use digital beamforming, the RF receiver needs to be able to handle large blocker powers, since the blockers are only cancelled after the conversion by the ADCs. LTE standards have specifications of the adjacent channel interferers and out-of-band interferers resilience. An example of the power levels that an LTE receiver should tolerate is shown in Figure ??. This example has relatively relaxed blocker specs, only blockers further than 85MHz from the signal can be as high as -15dBm.

However, WiFi operates in unlicensed band and has to co-exist with other devices that use the ISM band, like Bluetooth devices, cordless phones and microwave ovens. The received power in the WiFi band can be estimated by the free-space path loss (FSPL) in the Friis transmission equation:

Figure 2.6. Visual representation of power levels and frequency offsets for out-of-band blocking characteristics, from [?].

$$FSPL = \left(\frac{4\pi d}{\lambda}\right)^2 \tag{2.7}$$

where d is the distance between the transmitter and the receiver and  $\lambda$  is the wavelength. At 2.4GHz and distance of 0.5m (a reasonable distance for an interferer) it results in losses of 34dB. So an example cordless phone with output power of 20dBm will result in blocker power of -14dBm. Bluetooth can be even a stronger interferer since mobile devices have both WiFi and Bluetooth support and their antennas can be much closer, or they can even share the same antenna. These Bluetooth blockers can be as high as -6dBm [?].

In academia, tolerance to large nearby blockers was explored. In recent years works showing resilience to 0dBm blockers tens of MHz away from the signal were demonstrated [?], [?], at a price of high power consumption.

For our prototype we will target -10dBm blocker power at 40MHz offset from the carrier frequency. This performance can provide resilience to the majority of possible scenarios, and enable the digital beamforming architecture that we are targeting. In addition, we should also tolerate harmonic blockers of -10dBm, since for the lower part of our band the harmonic blockers are still in-band. We will describe this problem in detail in section ??.

## 2.3.3 Specifications summary

The specifications for the chip prototype that we discussed in this section are summarized in Table ??. The element noise figure range of 12-24dB can support several system scenarios:

- Array noise figure of 6dB, with 4 64 array elements

- 16 array elements, with array noise figure of 0 12dB

| Frequency range        | 0.7 - 6 | GHz |

|------------------------|---------|-----|

| Element noise figure   | 12 - 24 | dB  |

| Baseband bandwidth     | 10      | MHz |

| Gain                   | 50      | dB  |

| Nearby blocker power   | -10     | dBm |

| Nearby blocker offset  | 40      | MHz |

| Harmonic blocker power | -10     | dBm |

Table 2.1. Specifications summary for the array element receiver prototype.

## Chapter 3

# A 0.25-1.7GHz, 3.9-13.7mW

# Power-Scalable, -10dBm Harmonic

# **Blocker-Tolerant Mixer-First**

# **RF-to-Digital Receiver**

## 3.1 Chip architecture

The chip specifications derived in the previous chapter are different from conventional RF receivers. We can generally categorize RF receivers into two main categories: high-performance and low-power. Their main specifications are summarized in Table ??.

|                   | High-performance            | Low-power              | Our goal           |

|-------------------|-----------------------------|------------------------|--------------------|

| Applications      | Cellular, WiFi, $SDR^{(1)}$ | Bluetooth, $IoT^{(2)}$ | Massive MIMO array |

| Power consumption | High                        | Low                    | Low                |

| Noise             | Low                         | High                   | High               |

| Linearity         | Good                        | Poor                   | Good               |

| RF frequency      | Narrowband/Wideband         | Narrowband             | Wideband           |

(1) Software-Defined Radio. (2) Internet of Things.

Table 3.1. Main specifications comparison for RF receiver categories. Our massive MIMO system doesn't fit into the two common receiver categories.

High-performance receivers [?], [?], [?], [?], [?], [?] are aiming for excellent noise and linearity, and consuming 10s to 100s of mW to achieve them. The noise and linearity performance

of a high-end single-antenna receiver are crucial to achieve the desired ranges and address intense interference scenarios. Thus these DC power budgets are acceptable. These high-performance receivers are not intended to be used in variable-size, low-power multi-user MIMO radio arrays. The work in [?] uses spatial filtering in a 4-element array to tolerate large in-band blockers and to relax the dynamic range of the analog-to-digital converter (ADC), but consumes >110 mW to support 4 receiver elements without integrated ADCs. In [?], a multi-antenna system with analog beamforming is shown, but does not include baseband circuitry and supports only a single user. Neither [?] nor [?] supports harmonic rejection, which is needed in wideband RF systems that can address multiple frequency bands and communication standards. The work in [?] shows a high-performance single receiver with resiliency to harmonic blockers, but consumes a large amount of power in noise-cancelling circuitry that is not needed in a massive MIMO array. RF receivers for software-defined radio (SDR) as in [?] provide only bandwidth and RF frequency tuning, but cannot be configured to trade power for NF in larger MIMO arrays.

Low-power receivers [?], [?], [?] are constrained by strict DC power budgets of a few mW. To meet the power budget, these receivers compromise on noise performance (which is acceptable since the data rates and ranges are smaller) and linearity (though nowadays interference is becoming more important when the number of IoT devices is sharply increasing). In addition, low-power receivers are narrowband which allows low-power LO generation and distribution schemes.

However, our system does not fit into these categories. We would like to have a receiver with good linearity (since we use digital beamforming) and low power (due to very large array size), but we can compromise on the noise since it is averaged across the array elements. We would like to design a programmable noise-power tradeoff as a common element of arrays with varying sizes; as the array size is increased, the relaxed per-element noise requirements are leveraged to reduce power consumption. In addition we would like to support a wideband RF (requiring harmonic rejection) and variable array size/noise specification (a scalable solution). Hence a new receiver architecture is needed.

#### 3.1.1 Mixer-first receivers

The first question to address is the RF frond-end. High-performance receivers target very low noise performance, and usually use a Low Noise Amplifier (LNA) as the first stage of the receiver. The LNA conributes low noise while providing large gain, so the noise contribution of the later stages is very small. To achieve a low noise performance, the power consumption of the LNA should be relatively large (typically 5-10mW). Moreover, the LNA experiences large blocker swings, and its power consumption should be large enough to sustain large blockers.

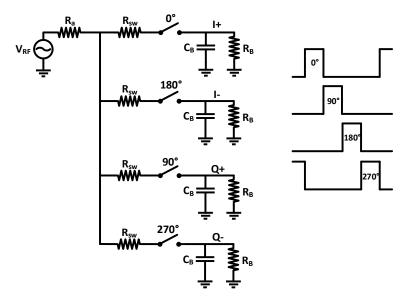

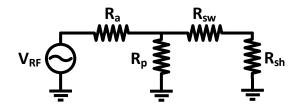

In recent years, a mixer-first topology was introduced [?], which enables noise figures of a few dB-s and excellent out-of-band linearity. The main idea is shown in Figure ??. A switching mixer is connected directly to the RF port, driven by non-overlapping LO phases. Each switch is shown as an ideal switch and a series resistor  $R_{sw}$  representing the switch series resistance. On the base-band side, each mixer is connected to a shunt capacitor  $C_B$ , and the equivalent resistance from the base-band side is represented by  $R_B$ . Charge-conservation analysis [?] shows that the input impedance for our linear time-varying (LTV) system can be accurately represented using a linear time-invariant (LTI) model as shown in Figure ??.  $\gamma$  represents the fundamental harmonic conversion gain:

$$\gamma = \frac{1}{N} \operatorname{sinc}^2 \left( \frac{1}{N} \right) \tag{3.1}$$

and  $R_{sh}$  represents the loss due to up-conversion of the baseband voltage via the LO harmonics:

$$R_{sh} = \frac{N\gamma}{1 - N\gamma} \left( R_a + R_{sw} \right) \tag{3.2}$$

where N is the number of the LO phases (N = 4 in Figure ??).

Figure 3.1. Mixer-first receiver conceptual diagram (left) and the corresponding LO waveforms (right).  $R_a$  is the antenna resistance,  $R_{sw}$  is the mixer switch resistance, and the switches are ideal.

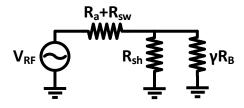

Figure 3.2. Mixer-first equivalent Linear Time-Invariant model. Impedance matching is achieved for  $R_{sw} + \gamma R_B ||R_{sh} = R_a$

The mixer-first architecture has two important properties:

• Impedance matching can be achieved by using small switch resistance  $R_{sw}$  and small equivalent baseband resistance  $R_B$  so that  $R_{sw} + \gamma R_B || R_{sh} = R_a = 50\Omega$ . For N = 4 we get  $\gamma = 0.2$ and  $R_{sh} = 4.3 (R_a + R_{sw})$ . Switch resistances of less than 10 $\Omega$  can easily be implemented using large mixer switch devices in modern processes. Low base-band resistance can be achieved by using Trans-Impedance Amplifiers (TIAs). • Band-pass filter -like input impedance is essentially achieved at RF frequecy due to upconversion of the base-band impedance. At RF frequencies close to the LO frequency (inband) we can achieve an impedance match, while at RF frequencies further away from the LO frequency (out-of-band) we see a low impedance (limited by the switch resistance). This impedance profile results in excellent out-of-band linearity of mixer-first receivers.

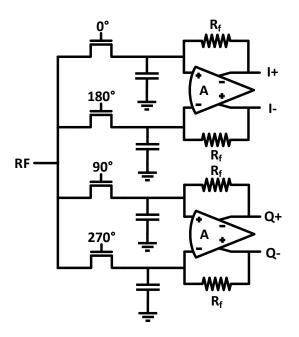

When the base-band  $R_B$  resistance is implemented using a TIA [?] (Figure ??) a feedback resistor  $R_f$  satisfying  $R_B = R_f/(A+1)$  can be used, where A is the TIA amplifier gain. Noise analysis of the LTI model in Figure ?? [?] shows that this topology can achieve noise figure of a few dB-s. Mixer-first topology with noise cancellation was introduced in [?], showing state-of-the-art sub-2dB noise figure, at a cost of increased complexity and power consumption.

Figure 3.3. Mixer-first with TIA as the first base-band stage. Low mixer switch resistance and TIA provide impedance matching and large voltage gain.

We will do a simple noise analysis of the model in Figure ?? here, taking into account only the mixer noise contribution ( $R_B$  is assumed to be noiseless). Then the output noise voltage is:

$$v_{n,out}^{2} = \left(\frac{R_{sh}||\gamma R_{B}}{R_{a}' + R_{sh}||\gamma R_{B}}\right)^{2} \left(v_{n,R_{a}}^{2} + v_{n,R_{sw}}^{2}\right) + \left(\frac{R_{a}'||\gamma R_{B}}{R_{sh} + R_{a}'||\gamma R_{B}}\right)^{2} v_{n,R_{sh}}^{2}$$

(3.3)

where  $R_a' = R_a + R_{sw}$ , and  $v_{n,R_a}$ ,  $v_{n,R_{sw}}$  and  $v_{n,R_{sh}}$  are the noise voltages of  $R_a$ ,  $R_{sw}$  and  $R_{sh}$  respectively.

Then the noise figure due to the mixer is given by:

$$F = \frac{1}{\operatorname{sinc}^2\left(\frac{1}{N}\right)} \left(1 + \frac{R_{sw}}{R_a}\right) \tag{3.4}$$

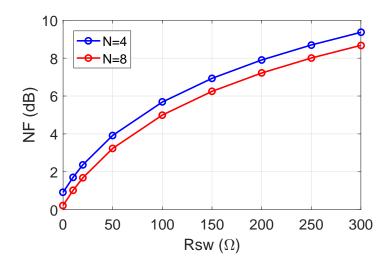

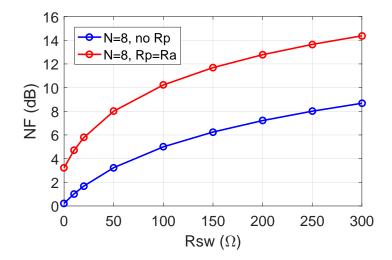

The plot of the noise figure is shown in Figure ?? for 4 phases and 8 phases. First we can see that increasing the number of phases from 4 to 8 improves the noise figure since there is less

re-radiation to higher harmonics (more on that in the next section). From equation ?? we can see that this improvement is  $\frac{\operatorname{sinc}^2(\frac{1}{8})}{\operatorname{sinc}^2(\frac{1}{4})} = 0.7dB$ , independent of the switch resistance. This is a substantial difference when targeting noise figures of a few dB, but less important for our spec. More importantly, even when the switch resistances are as large as several 100s of  $\Omega$ s (corresponding to minimum switch sizes in modern processes), the mixer noise contribution corresponds to noise figures of less than 10dB.

The power cost of the small switch resistance for high-performance mixer-first receivers is quite large, summarized in Table ??. Since the LO power is consumed by digital gates, the power consumption is proportional to the frequency  $P_{LO} = CV^2 f$ , where C is the total capacitance of the LO distribution, V is the LO supply voltage and f is the LO frequency. So it is convenient to consider the LO power per frequency (mW/GHz). We can see from the table that the LO power is a substantial part of the total (LO+BB) power. While the base-band power is constant, the LO power increases with the frequency. So at a few GHz of LO frequency the LO is the dominant part of the total power.

Since the LO power consumption is significant, and we don't need to use large switches for our noise specifications, we can use switches with large resistance and save substantial LO power. Moreover, since switches are easily scalable, we can build a bank of parallel switches and pick the size that we need for a desired spec. This architecture will enable us to achieve the noise tuning range that we need. However, we won't be able to achieve impedance matching using base-band TIAs, since the switch resitance will already be larger than  $50\Omega$ . We will address this issue in section ??.

Figure 3.4. Mixer-first noise figure, mixer noise contribution only. Note that even resistances of several 100s of  $\Omega$ s provide noise figures of less than 10dB.

| Ref. | Technology<br>(nm) | f (GHz)   | $\begin{array}{c} \mathbf{Rsw} \\ \mathbf{(} \Omega \mathbf{)} \end{array}$ | LO<br>phases | NF<br>(dB) | BB power<br>(mW) | LO power<br>(mW/GHz) |

|------|--------------------|-----------|-----------------------------------------------------------------------------|--------------|------------|------------------|----------------------|

| [?]  | 180                | 0.1-1.8   | NR                                                                          | 4            | 3.5        | 24               | 11                   |

| [?]  | 28                 | 0.4 - 3.5 | NR                                                                          | 8            | 2.6        | 36               | 16                   |

| [?]  | 65                 | 0.1 - 1.5 | 10                                                                          | 8            | 6.5        | 35               | 13                   |

| [?]  | 40                 | 0.1 - 2.7 | 20                                                                          | 8            | 1.6        | 32               | 17                   |

| [?]  | 65                 | 0.1-1.2   | 20                                                                          | 8            | 4.4        | 30               | 28                   |

| [?]  | 65                 | 0.2-1.2   | 5                                                                           | 8            | 3.5        | 36               | 33                   |

Table 3.2. LO power consumption of high-performance mixer-first receivers (NR - not reported). The LO power is a substantial part of the receiver, for low switch resistance  $(< 20\Omega)$  approximately 10-30mW/GHz are consumed by the LO.

### 3.1.2 Harmonic rejection

Since we are targeting a wideband frequency operating range of 1-6GHz, if we use a 4-phase mixer-first architecture, we will have a problem of harmonic blockers. Due to the fact that the LO is rectangular, RF signals around the odd harmonics of the LO will be also down-converted to base-band. The even harmonics can be suppressed by using a differential configuration. The 3rd and 5th harmonics are the most important, since for the lower part of the band (1-2GHz) these harmonics are still in-band (below 6GHz). Thus a mechanism of harmonic rejection is required to make sure that the receiver is robust against harmonic blockers.

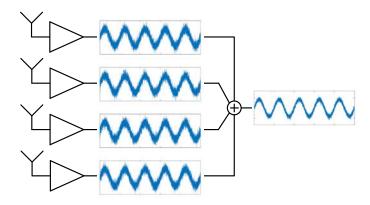

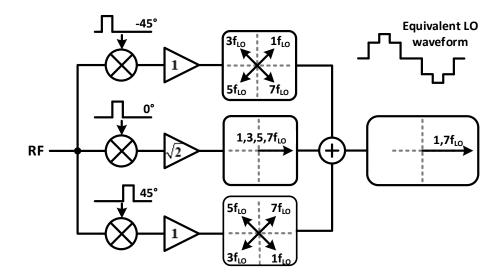

Harmonic rejection was under intense research in the past two decades. The most popular approach was introduced in [?], and its concept is shown in Figure ??. The main idea was to use 8 LO phases for the mixer switches, and recombine the outputs with the correct coefficients so a sine-like equivalent waveform is implemented. Generally speaking, the more LO phases are used, the more harmonics can be cancelled since the effective LO signal is closer to sinusoidal. For 6 phases [?] only the 3rd harmonic is cancelled, for 8 phases [?], [?], [?], [?], [?], [?], [?] the 3rd and 5th are cancelled, and for 16 phases [?] the odd harmonics up to 13th order can be cancelled. The design complexity and power consumption grows with the number of LO phases, so using more phases has a large cost.

Additional approaches to achieve harmonic rejection were introduced, all trying to emulate a sine-like LO using rectangular (digital) pulses. Multi-level LO DAC [?], LC tank at  $4f_{LO}$  [?], 2-stage recombination with 8 LO phases [?], using 3rd and 5th LO harmonics with feedforward cancellation [?] and using LO pulse-width modulation [?] are just a few examples. These approaches are targeting high-performance applications and all require large power for an extra hardware to implement the harmonic rejection.

Since low-power receivers are narrowband, they do not use harmonic rejection. So we need to come up with a low-power harmonic rejection scheme which will still be highly linear. Thus we would like to use a rectangular LO with a passive mixer for good linearity and come up with a low-power scheme.

Figure 3.5. Conceptual diagram of a harmonic-rejection mixer with 8 LO phases. Equivalent sine-like LO waveform is created when recombining the LO phases with the right coefficients.

reporting harmonic blocker powers of -25dBm to -37dBm. The work in [?] is dedicated to improve large signal harmonic rejection. Their architecture (called "harmonic rejection TIA") has extra circuitry for large harmonic blocker resiliency with large power consumption of 40-70mW. Rather than quoting the harmonic rejection, this paper shows the NF degradation with large harmonics. We will compare our harmonic rejection linearity to this state-of-the-art paper.

| Ref. | Harmonics<br>power (dBm) | LO<br>phases | Harmonics       | Rejection<br>(dB)     | Method                 |

|------|--------------------------|--------------|-----------------|-----------------------|------------------------|

| [?]  | -30                      | 8            | $3,\!5$         | 60,64                 | RF+BB Gm (2 stages)    |

| [?]  | -37                      | 8            | $3,\!5$         | $56,\!56$             | RF Gm                  |

| [?]  | -25                      | 8            | $3,\!5$         | $75,\!45$             | BB Gm                  |

| [?]  | -30                      | $4^{(1)}$    | $3,\!5,\!7,\!9$ | >70                   | Digital MMSE equalizer |

| [?]  | -10                      | 8            | $3,\!5$         | not reported $^{(2)}$ | Harmonic rejection TIA |

(1) Two paths are used. (2) Gain and NF degradation due to large harmonic blockers is reported.

Table 3.3. Published harmonic rejection linearity results. Only one work dedicated to large signal harmonic rejection is able to cancel -10dBm harmonics.

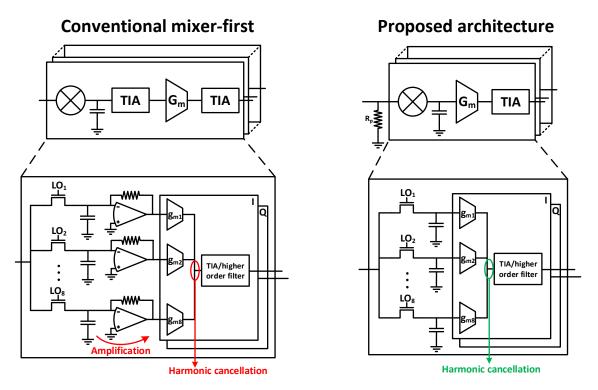

### 3.1.3 Proposed architecture

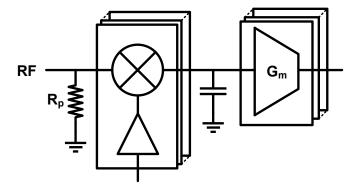

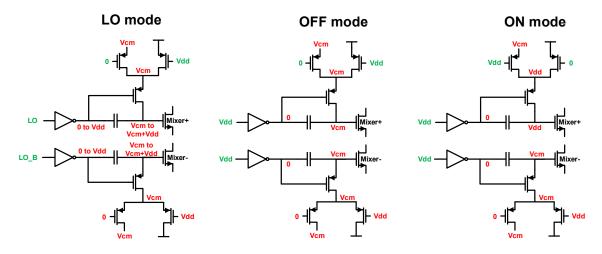

Our proposed architecture is shown in Figure ??. To achieve low power harmonic rejection, we can use small mixer switches with large resistance (as we described in section ??) and use 8 phases to cancel the 3rd and 5th harmonics. As mentioned in section ??, we won't be able to achieve impedance matching using base-band TIAs, since the switch resistance will already be larger than  $50\Omega$ . Hence we eliminate the base-band TIAs and use the harmonic recombination  $G_m$  stage directly at the base-band input.

To achieve impedance matching we use a shunt resistor  $R_p$  at the RF input. This matching

strategy is a simple passive solution with no linearity and power consumption downside. Active negative impedance matching can be further explored, analyzing its noise, linearity and power consumption consequences.

Figure 3.6. Conventional mixer-first [?] and the proposed architecture. Harmonic recombination earlier in the receiver chain enables better linearity of the harmonic cancellation. Impedance matching is achieved by a shunt  $R_p$  resistor.

This architecture has a substantial advantage in the **harmonic rejection linearity**. In the conventional architecture the harmonic blocker is amplified by the TIAs before getting cancelled by the  $G_m$  stage recombination. In the proposed architecture, the harmonic blocker is cancelled right at the base-band input before any amplification. Hence this architecture is more linear in terms of harmonic rejection - it is capable of cancelling larger blockers without affecting the fundamental path.

In order to calculate the required shunt resistor  $R_p$  for impedance matching, we can look at the mixer-first input impedance without the base-band TIAs. In this case the low-frequency base-band impedance is infinite, and the effective base-band impedance is only  $R_{sh}$  (see Figure ??). From equations ?? and ?? for N = 8 we get  $\gamma = 0.12$  and  $R_{sh} = 19.8 (R_a + R_{sw})$ . Hence the input impedance is:

$$R_{in} = R_{sw} + R_{sh} = R_{sw} + 19.8 \left( R_a + R_{sw} \right) \tag{3.5}$$

From equation ?? the input impedance is in the k $\Omega$  range, so we need  $R_p \cong R_a$  for matching. To analyze the noise impact of this parallel matching we can use a simple LTI model in Figure ??. Since  $R_{sh} >> R_{sw}$  we can ignore  $R_{sh}$  for a simpler analysis (which has only 0.2dB of error in the noise figure). For  $R_p = R_a$  the noise figure is:

$$F = 2 + \frac{4R_{sw}}{R_a} \tag{3.6}$$

The factor of 2 is due to the noise of  $R_p = R_a$ , and the factor of 4 is due to the fact that  $R_{sw}$  is not in series with  $R_a$ , so the noise of  $R_a$  is attenuated by  $R_p$  before propagating to the base-band output.

We can compare the mixer-only noise figure of the original mixer-first architecture from equation ?? to the proposed architecture. The result is shown in Figure ??. The noise figure degradation is between 3dB for small switch resistances and 6dB for large switch resistances. Based on our desired noise figure range of about 12-24dB, the mixer noise contribution of this architecture looks reasonable.

Figure 3.7. Mixer-first with shunt  $R_p$  matching equivalent Linear Time-Invariant model (wihout the base-band noise contribution).

Figure 3.8. Mixer-first noise figure (mixer noise contribution only), shunt  $R_p$  noise impact. Degradation of 3-6dB due to  $R_p$  is still reasonable for our low-power high-noise application.

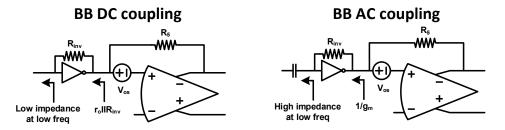

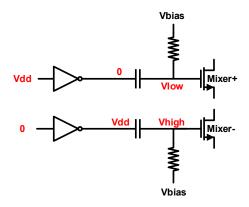

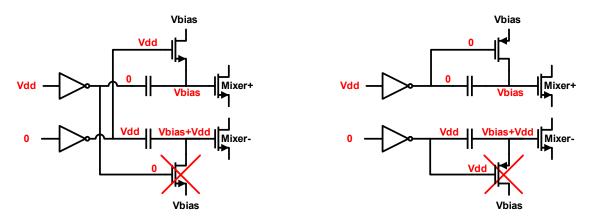

#### 3.1.4 AC-coupling

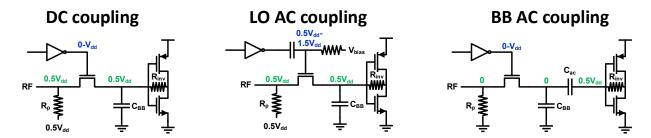

In the proposed architecture in Figure ??, we need to address the issue of different commonmode voltages of the base-band input and the RF. The base-band input is a  $G_m$  stage where optimum implementation in terms of noise efficiency is a complimentary inverter structure. Thus the optimum base-band input common-mode voltage is around mid-rail (0.5 $V_{dd}$ ). The three possible options for AC/DC coupling of the mixer are shown in Figure ??. DC coupling is the simplest solution, but its main drawback is a large mixer switch resistance, since the device  $V_{gs}$  is only  $0.5V_{dd}$ . LO AC coupling improves the mixer switch resistance (though it is not optimal due to losses to the mixer bottom-plate cap) at a cost of larger power consumption and area. BB AC coupling has the best switch resistance, but the cost is loss in signal path (due to bottom-plate capacitance), area and extra noise from the inverter feedback resistor  $R_{inv}$ .

Figure 3.9. Different options for mixer AC/DC coupling. The LO swing is shown in blue, and the common-mode votlages are shown in green. High-performance receivers usually use LO AC-coupling, but for our low-power receiver BB AC-coupling has a better overall performance.

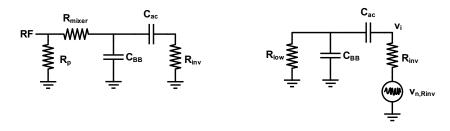

To analyze the noise impact of the inverter feedback resistor  $R_{inv}$  in the case of BB AC coupling, we observe that this resistor is connected to a low-impedance node (TIA input) at the Gm drain. In Figure ?? we show a simplified LTI schematic of the impedances that impact the noise propagation of the  $R_{inv}$  noise to the Gm input.

Figure 3.10. Noise impact of the inverter feedback resistor  $R_{inv}$  in the case of BB AC coupling. A simplified LTI schematic (left) and  $R_{inv}$  noise source (right).

Since we need the high-pass corner frequency to be much lower than the signal pole, we can treat  $R_{low}$  and  $C_{BB}$  as shorts, so the  $R_{inv}$  noise transfer function is a low-pass with a corner frequency at the AC-coupling high-pass corner frequency:

$$v_i = \frac{v_{n,Rinv}}{1 + sR_{inv}C_{ac}} \tag{3.7}$$

This behavior is similar to kT/C noise in sample-and-hold circuit. To reduce the resistor noise impact we need to increase the capacitor  $C_{ac}$  as much as possible.

In most high-performance mixer-first receivers, LO AC coupling is used [?], [?], [?]. When high performance is targeted, the mixer size is large, so we only lose the LO swing due to the AC-coupling cap bottom-plate. The extra DC power is also tolerated in these applications.

In our case we are using small mixer sizes (down to minimum size devices). Then the ACcoupling cap should be small, and its bottom plate portion becomes larger. So we have large losses and extra power consumption to drive this bottom-plate cap. Thus we choose to use BB AC-coupling, so we won't spend extra power on the LO distribution, and pay the extra area and performance loss of the bottom-plate and noise in the signal path.

#### 3.1.5 DC-offset

The base-band AC coupling has an important impact on the DC offset of the receiver. A comparison between the opamp DC offset contribution of DC-coupling the base-band and AC-coupling the base-band is shown in Figure ??. The opamp offset gain is a non-inverting amplifier gain:

$$\frac{V_{os,out}}{V_{os}} = 1 + \frac{R_5}{R_{out,G_m}} \tag{3.8}$$

where  $V_{os}$  is the opamp offset,  $V_{os,out}$  is the output offset due to the opamp and  $R_{out,G_m}$  is the impedance looking into the  $G_m$  output.

Figure 3.11. Opamp DC-offset impact in DC and AC coupling of the base-band. AC coupling creates low impedance looking into the  $G_m$  output and large gain of the opamp DC offset to the receiver output.

When the base-band is DC-coupled, the impedance seen into the mixer from the  $G_m$  is low, so the impedance looking into the  $G_m$  output is  $r_o || R_{inv}$ , which is high. Thus the offset gain is small, and the opamp offset contribution is relatively low.

However, when the base-band is AC-coupled, the impedance seen into the mixer from the  $G_m$  is infinite at low frequency, so looking into the  $G_m$  output we see a low  $1/g_m$  impedance. Thus the offset gain is large, and the opamp offset becomes the major contribution to the overall receiver DC offset. Thus a mechanism to cancel this DC offset is needed, which we will describe in section ??.

## 3.2 Design Implementation

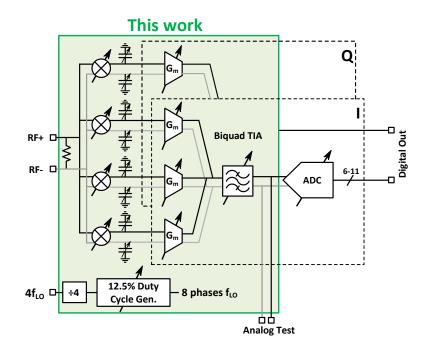

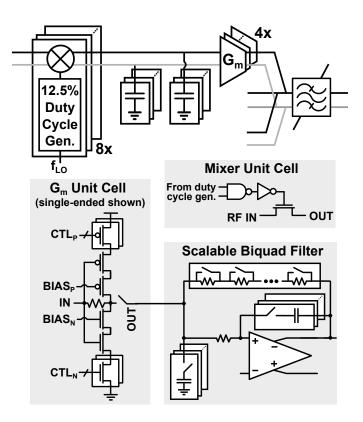

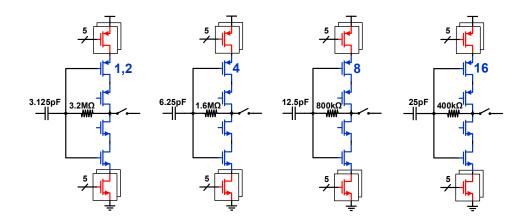

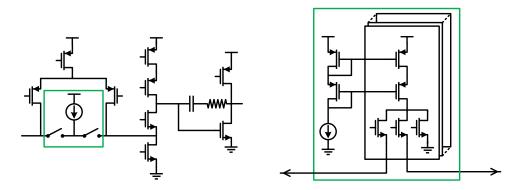

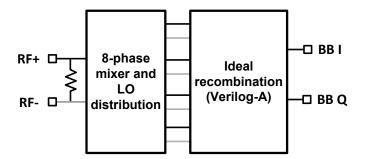

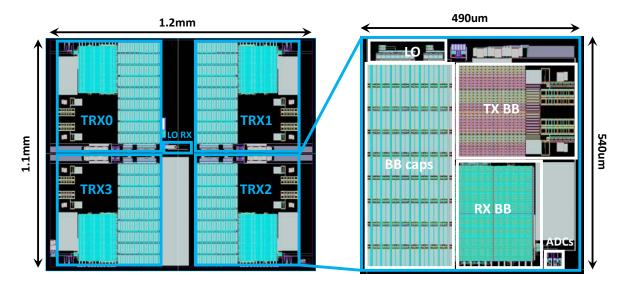

The implemented receiver architecture is shown in Figure ??. We will describe the details of the analog components here, while the details of the ADC implementation can be found in [?].

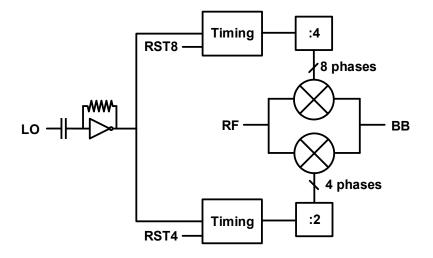

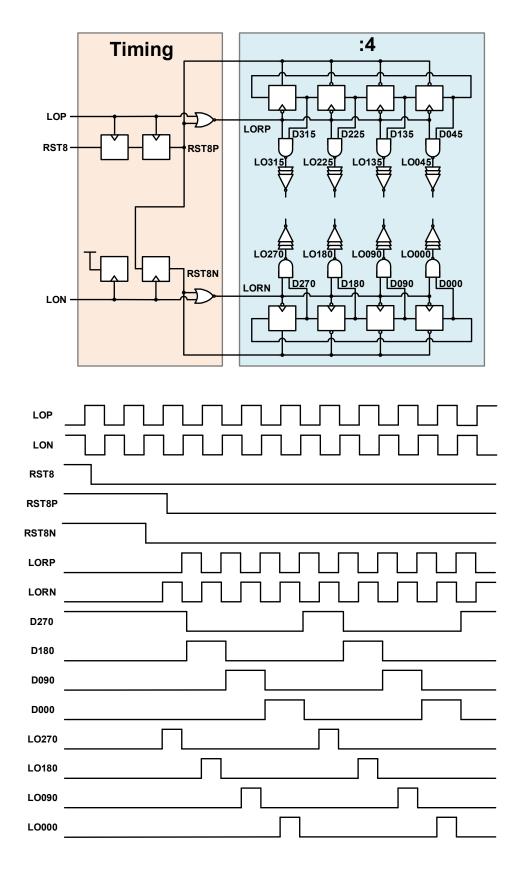

The LO contains a divide-by-4 circuit, and a size-programmable LO distribution circuit that creates 8 non-overlapping phases and drives the mixer switches. The LO distrubution is partitioned into 8 unit cells (Figure ??), each with a series resistance of roughly  $240\Omega$ . The baseband capacitors

Figure 3.12. Scalable RF-to-digital receiver architecture [?].

are programmable with 7 bits of resolution to keep the low-pass corner constant for the mixer tuning range and for process variations.

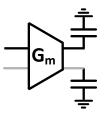

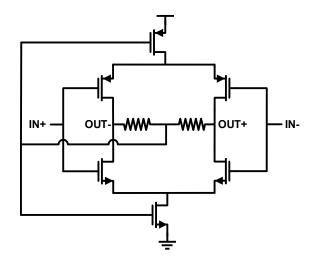

The parallel  $G_m$  unit cells are shown in Figure ?? and in more detail in Figure ??. The  $G_m$  cells were built as cascode transconductors to increase the output impedance and avoid degrading the subsequent filter response. The cascode devices gate voltage is also used to turn the cells off. Each  $G_m$  unit cell has a transconductance of 0.9 mS. Tunable resistive degeneration (with 5 bits of resolution) of the  $G_m$  unit cells allows fine-tuning of the harmonic recombination weights. This tuning method is not in the signal path, so it does not affect the fundamental transfer function. The AC-coupling caps are shared between different phases of the  $G_m$  elements, and there are no series switches for the AC coupling caps (to prevent additional noise).

Several aspects of the  $G_m$  stage limit the scalability range of the receiver. First, the maximum size is limited by the series capacitor area. The minimum size is limited by the resistor area. In addition, series switches at the output of the  $G_m$  cells were added to reduce the parasitic cap of the  $G_m$  when tuned to a low  $G_m$  setting. These parasitic caps prevent the biquad filter from keeping a constant transfer function at low capacitor settings.

A Rauch biquad TIA [?], [?] converts the total current obtained after harmonic recombination into a voltage, providing third order filtering together with the pole after the mixer switches. The Rauch topology was chosen for good linearity, low power, and input capacitance that can embed the parasitics of the  $G_m$  output. The passive components of the filter are tunable with 7 bits of resolution to maintain a constant gain and filtering profile across the different  $G_m$  sizes. For small  $G_m$  size, large feedback resistor for the filter is used (to keep a constant gain), and the filter caps are tuned to maintain the second-order biquad transfer function. A two-stage Miller-compensated opamp was used in the filter. The prototype of this receiver supports a single baseband bandwidth

Figure 3.13. Scalable RF front-end schematic diagram.

Figure 3.14.  $G_m$  stage schematic diagram. All inputs and outputs are shorted.

of 10 MHz, but the architecture can be changed to support various bandwidths for massive MIMO applications by using higher resolution on the filter capacitors and a higher bandwidth op-amp.

The DC-offset cancellation DAC is shown in Figure ??. The current is injected into the first stage (folded cascode) of the opamp. The DAC has 9 bits of resolution with an LSB of 40nA to provide an ouptut voltage resolution of 10mV. Due to the low LSB current, the device size is small (w=600nm, l= $2.4\mu$ m). The current is steered to the positive side, negative side or ground to prevent the bias point to change if the branch is off. On-chip automatic calibration for zero input was implemented, by scanning the DAC codes and selecting the code with minimum output offset.

Figure 3.15. DC-offset cancellation DAC location in the opamp (left) and DAC structure (right).

### **3.3** Measurement Results

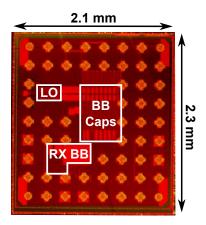

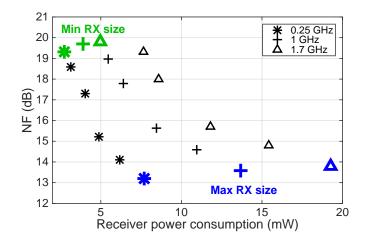

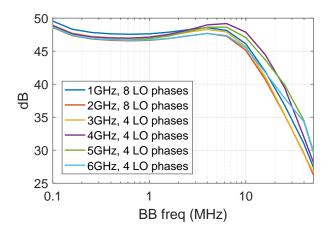

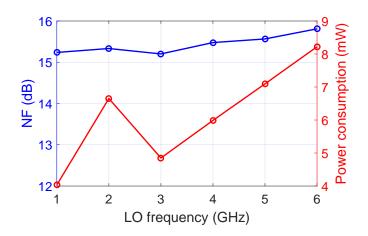

The RF-to-digital receiver was implemented in 65 nm CMOS process (Figure ??). Figure ?? shows the NF and power scaling range of the receiver (RX) at three different LO frequencies, implemented by tuning the sizes of the mixer switches and the  $G_m$  stages. For the min RX size, a single mixer unit cell and  $G_m$  cell were used, while for the max RX size, 8 parallel mixer unit cells and 4 parallel  $G_m$  cells were used.

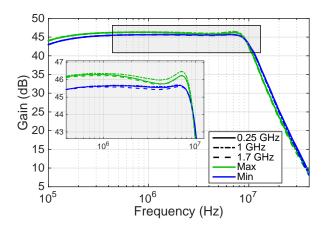

The passives are tuned to maintain constant gain and third order filtering profile, as shown in Figure ??. The receiver power scales by 4x from the maximum to minimum size, saving power in larger arrays. In this prototype, the maximum LO frequency was limited to 1.7 GHz by the LO frequency divider (which receives an externally generated 4x clock) rather than the LO distribution architecture. Harmonic recombination may not be required for higher bands in the sub-6 GHz range, so a simpler factor of 2 divider can be used with the same input clock.

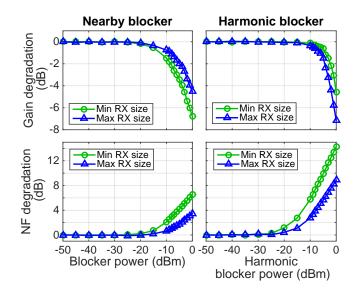

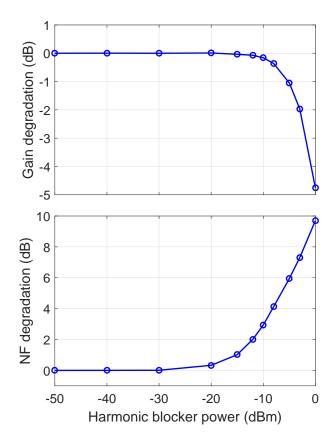

The linearity performance of the receiver is shown in Figure ?? with LO frequency of 800 MHz, signal at 801 MHz, and large harmonic blocker at 2400.7 MHz. The early harmonic recombination enables a large harmonic blocker P1dB of >-6.2 dBm and NF degradation of <10 dB for input harmonic powers up to -5 dBm. In addition, resilience to large nearby blockers at offset of 40 MHz was measured. The low-pass filtering after the mixer downconversion and additional biquad filtering enable gain and NF degradation of less than 2 dB for input blocker powers up to -10 dBm. The results in Figs. ??, ??, and ?? were measured at the analog test output before the ADC input.

The input matching measurements for LO frequency of 1GHz are shown in Figure ??. The

Figure 3.16. Die micrograph.

Figure 3.17. Receiver scalability.

Figure 3.18. Receiver gain for min and max RX size.

Figure 3.19. Receiver tolerance to 40 MHz offset blocker (left) and in-band 3rd harmonic blocker (right). Measured using an LO frequency of 800 MHz and signal at 801 MHz

impedance seen from the RF port is the intentional  $50\Omega$  resistor in parallel with the impedance seen into the mixer. When the mixer size increases as we approach the min RX size, the out-of-band impedance seen into the mixer becomes larger, so the out-of-band impedance seen from the RF port becomes closer to  $50\Omega$ . The center frequency is lower than 1GHz due to the parasitic capacitance of the pad and the switches on the RF port. Since the input impedance to the mixer has a band-pass response, it can be seen as a parallel RLC circuit. Thus adding a parasitic capactance on the RF port decreases the central frequency. Changing the mixer size affects the Q of the band-pass, so the same parasitic capacitance results in different frequency shift. This frequency shift can be eliminated using complex feedback between the base-band I and Q paths [?], [?].

Figure 3.20. Measured input matching of the receiver at 1 GHz.

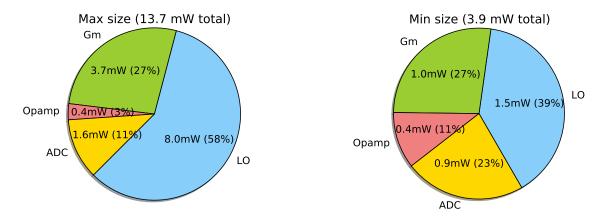

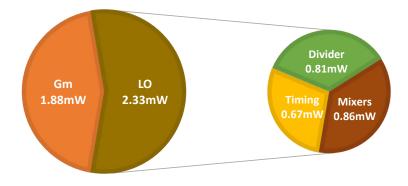

The power consumption breakdown of the receiver and the ADC is shown in Figure ??. The

opamp is the only non-scalable part in the current design since its power consumption is relatively low. The LO power is the major contributor since we are limited by min size devices when implementing the min size RX settings.

Figure 3.21. Measured power consumption breakdown of the receiver and the ADC at 1 GHz.

#### 3.4 Conclusion

When used in an array, this receiver can be configured with higher NF and lower power as the number of array elements grows to maintain constant array-level NF and power consumption while improving spatial selectivity. In this work, the single-element NF range is  $\sim$ 13-19 dB. For an array-level NF of 1.5 dB, 16 elements are required for the max RX size and 64 elements are required for the min RX size. To support >64 elements without linear increase in array power, a smaller (lower power) RX unit cell is required. Similarly, to maintain an array-level NF of 1.5 dB for <16 elements, more unit cells are required in each receiver to lower the per-element NF.

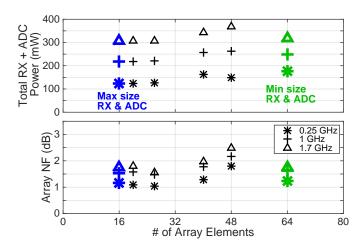

Figure ?? shows the calculated equivalent array-level NF (bottom) and power consumption (top) for three different LO frequencies. With the proposed scalable architecture, this design can maintain sub-2.5 dB array-level noise figure with up to 64 antennas and <368 mW total receiver+ADC power consumption, much lower than any prior art shown in Table ?? when referenced to a 64-element array.

While [?] has relatively low power, it does not include baseband circuitry and uses analog beamforming that supports only a single user. The harmonic blocker resilience of this scalable low-power design is comparable to the state-of-the-art [?], allowing multiple users to be supported through digital beamforming. Overall, this scalable design can support an array size increase of up to 4x while maintaining excellent linearity and nearly constant array-level NF and power consumption.

Figure 3.22. Calculated array-level NF and total receiver + ADC power consumption.

|                                 | [?]               | [?]     | [?]       | [?]     | Th                                                                            | is work                            |         |

|---------------------------------|-------------------|---------|-----------|---------|-------------------------------------------------------------------------------|------------------------------------|---------|

|                                 | [• ]              | [•]     | [• ]      | [•]     | Single<br>element                                                             | Calculated<br>array<br>performance |         |

| RF Freq. (GHz)                  | 0.1 - 3.1         | 1.0-2.5 | 0.1-3.3   | 0.4-3   | 0.25-1.7                                                                      |                                    |         |

| BW (MHz)                        | NR                | NR      | NR        | 0.5-50  | 10                                                                            |                                    |         |

| Array elements                  | 4                 | 4       | 1         | 1       | 1                                                                             | 8                                  | 32      |

| NF $(dB)^{(1)}$                 | $3.4 - 5.8^{(2)}$ | 6       | 1.7       | 1.8-2.4 | $\frac{13.2 \text{-} 13.8^{(3)}}{18.6 \text{-} 19.3^{(4)}}$                   | 4.2-4.8                            | 3.5-4.2 |

| Gain (dB)                       | 41                | 12      | NR        | 70      |                                                                               | 46                                 |         |

| 3rd harm. blocker<br>P1dB (dBm) | N/A               | N/A     | -6.5      | N/A     | $-4.3^{(3)}$<br>$-6.2^{(4)}$                                                  | -4.3                               | -6.2    |

| Harm. blocker NF<br>@-5dBm (dB) | N/A               | N/A     | 9         | N/A     | $22.9^{(3)} \\ 24.6^{(4)}$                                                    | 13.8                               | 9.6     |

| Out-of-band<br>IIP3 (dBm)       | $-5/12^{(5)}$     | 5       | 11.5      | 8       | $     \begin{array}{r}       14.6^{(3)} \\       18.8^{(4)}     \end{array} $ | 14.6                               | 18.8    |

| Supply (V)                      | 1.2               | 1.0     | 1.0       | 0.9     | 1.2 Analog, 1.0 Digital                                                       |                                    |         |

| CMOS technology                 | 65  nm            | 65  nm  | 28  nm    | 28  nm  | 65  nm                                                                        |                                    |         |

| Total power (mW)                | 116-147           | 26-36   | 36.8-62.4 | <40     | $7.6-19^{(3)} \\ 3.1-7.6^{(4)}$                                               | 61-152                             | 99-243  |

| Total area (mm <sup>2</sup> )   | 0.8               | 0.2     | 5.2       | 0.6     | 0.7                                                                           | 5.6                                | 22.4    |

NR: Not reported. N/A: Not applicable.

(1) For multi-element arrays, equivalent array-level noise figure calculated as

single-element NF - 10  $\log_{10}(\text{num. of array elements})$ . (2) With spatial filtering enabled (without: 1.7-4.5 dB). (3) Max size configuration. (4) Min size configuration. (5) Depends on receiving angle.

Table 3.4. Summary and comparison with state-of-the-art.

## Chapter 4

# BAG-Generated RF Receiver for Large Antenna Arrays

#### 4.1 Motivation

The receiver design that we described in the previous chapter has a fews issues that can be improved.

First, optimization of the power consumption was not rigorously performed. We came up with the architecture that enables scalable noise-power consumption tradeoff, but did not design it to have optimum power consumption for each noise setting.

Second, the design was performed for a particular technology (65nm). Design decisions (like LO/BB AC coupling, LO chain fanout,  $G_m$  stage structure and so on) were made for this particular technology. If we'd like to design the next version of this receiver in a different technology node, we should repeat the same manual process of creating schematics, drawing layouts, running simulations, updating schematic and layout parameters all over again. The optimum design point will obviously depend on the technology, so we need to have a very long design cycle to get the final optimized design.

This problem is of course nothing new, analog designers faced it for many decades. Recently a Berkeley Analog Generator version 2 (BAG2) framework was introduced [?]. This framework enables design automation by creating process-portable circuit "generators". The generators are capturing the design methodoogy, the schematic and layout creation and running testbenches. Using this framework we can write a single circuit generator for the entire system, and produce different implementations ("instances") for different specs and different technologies.

In section ?? we will give a short introduction of the BAG framework. Then in section ?? we will introduce a design methodology procedure within BAG that will provide us with the optimum receiver given the specs and the technology. In section ?? we will give a detailed description of the

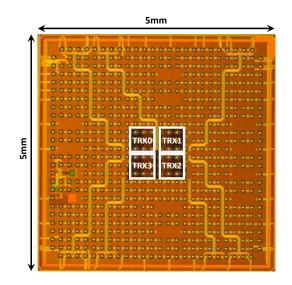

chip that implements this design methodology in a 16nm FinFET process, and in section ?? we will show the measurement results.

#### 4.2 Berkeley Analog Generator

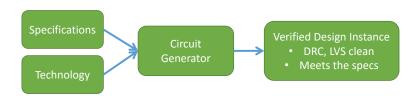

The Berkeley Analog Generator (BAG) was first introduced in [?]. The main idea of this framework was that instead of designing a circuit for a specific spec and technology, the designer should capture the design methodology into a circuit "generator". The generator gets inputs of specs and technology and consists of methods to produce schematics layouts and testbenches

Figure 4.1. The general idea of a generator: a single procedure (circuit generator) produces verified design instance for given specifications and technology.

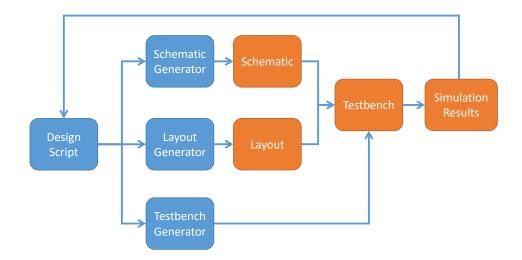

A simplified flowchart of a circuit generator design is shown in Figure ??. The blocks shown in blue are implemented in the generator framework (Python) and the blocks shown in brown are generated into the circuit design and simulation software (Cadence Virtuoso). We can summarize the steps as follows:

- The design script gets the specifications and the technology as its inputs, and provides the parameters (device sizes, threshold flavors, number of stages etc.) for the schematic, layout and testbench generators.

- The schematic, layout and testbench generators create an instance according to the parameters specified by the design script. The generated layout is DRC clean, and passes LVS with the generated schematic.

- The generated testbench is executed for the generated circuit (after post-layout extraction).

- The simulated results are fed back into the design script and compared with the desired specifications. If some of the specs are not met and a change of parameters is required, new schematic, layout and testbench instances are generated and the procedure is repeated. Also if the specs are met but a more optimized result is required, the procedure can be repeated.

From Figure ?? we can see that four scripts should be written: the three generators (schematic, layout and testbench) and the design script. The design script incorporates the design methodology

Figure 4.2. BAG generator design flowchart. The blocks shown in blue are implemented in the generator framework (Python) and the blocks shown in orange are generated into the circuit design and simulation software (Cadence Virtuoso)<sup>2</sup>.

of the circuit. Based on the specs it can select the desired architecture, run preliminary device-level simulations (or get them from a previously generated database), run circuit-level simulations for sub-circuits and extract their important parameters in the desired design space and technology, run optimization algorithms on these parameters (without running additional simulations) and so on.

The flow in Figure ?? is a simplified one, in practice every generator has a different version of this flow. Our goal is to create a flow that will minimize the execution time until the specs are met, so the overall design time is minimized. Thus we should come up with a design methodology that will minimize the number of generation and simulation cycles.

Another important feature of a BAG generator that it can actually provide us instances with better performance than manual designs. If many design iterations are needed, automation saves considerable amount of time, since the designer doesn't need to repeat manual steps of changing the schematic and the layout and re-running simulations. So with an automated BAG generator, better optimization result can be achieved in shorter overall design time for new specifications and/or technology.

In addition, generators enable easy design re-use for different projects. Many building blocks are used for different applications, with different specs or technologies. Once a generator is built, it can be used for different projects or for different blocks in the same system, without manually re-designing it for each particular application.

$<sup>^{2}</sup>$ In addition to the generated schematic, layout and testbench, a behavioral model and various other files (lef/lib/verilog/spice/...) need to be generated to enable integration into a larger SoC.

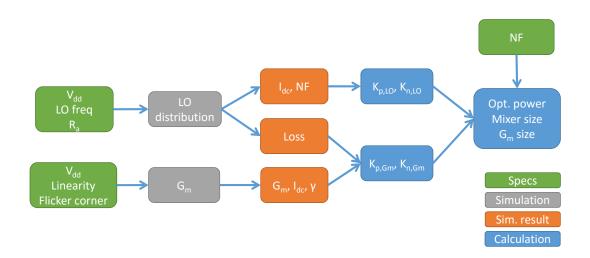

#### 4.3 Receiver Design Methodology

#### 4.3.1 DC power optimization

The first question to address is how should we find the optimum DC power consumption for a given noise figure spec. The main contributors to the noise of the receiver are the front-end components: the  $R_p$  matching resistor, the mixer switches and the baseband  $G_m$ . They are shown in the schematic in Figure ??.  $R_p$  is fixed to be equal to the antenna resistance for impedance matching. The mixer size (and consequently the LO distribution driving it) and the  $G_m$  size are unknown for now.

Figure 4.3. The front-end components that contribute to the noise figure of the receiver. While  $R_p$  is fixed, many combinations of the mixer and the  $G_m$  size result in the same noise figure.

We can intuitively see the optimization process in the following way. Larger LO size will result in lower noise figure and larger power consumption. Similarly, larger  $G_m$  size will also result in lower noise figure and larger power consumption. So we could achieve the desired noise figure by using large LO and small  $G_m$ , or by using small LO and large  $G_m$ . Actually there are many combinations of the mixer and the  $G_m$  size that result in the same overall noise figure. From these combinations we would like to pick the mixer size and the  $G_m$  size that will minimize the overall power consumption.

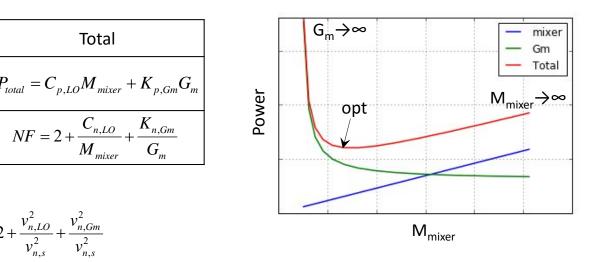

To formulate the optimization process we will write the power consumption and the noise contribution of the mixer and the  $G_m$  as functions of their size. The LO power consumption is proportional to the mixer size  $M_{mixer}$  (number of fingers for given finger width and length):

$$P_{LO} = K_{p,LO} M_{mixer} \tag{4.1}$$

where  $K_{p,LO}$  is a constant. Similarly the  $G_m$  stage power consumption is proportional to its transconductance  $G_m$ :

$$P_{Gm} = K_{p,Gm}G_m \tag{4.2}$$

where  $K_{p,Gm}$  is a constant. Thus the total power consumption is:

$$P_{total} = K_{p,LO}M_{mixer} + K_{p,Gm}G_m \tag{4.3}$$

The noise voltage generated by the LO is:

$$v_{n,LO}^2 = \frac{K_{n,LO}}{M_{mixer}} v_{n,s}^2 \tag{4.4}$$

where  $v_{n,s}$  is the source (antenna) noise voltage and  $K_{n,LO}$  is a constant. Similarly the noise voltage generated by the  $G_m$  is:

$$v_{n,Gm}^2 = \frac{K_{n,Gm}}{G_m} v_{n,s}^2$$

(4.5)

where  $K_{n,Gm}$  is a constant. The noise voltages in equations ?? and ?? can be referred to any point in the circuit (input/output/other). It is just important that all three of  $v_{n,LO}$ ,  $v_{n,Gm}$  and  $v_{n,s}$  will be referred to the same point in the circuit. Then the receiver noise figure is:

$$NF = \frac{v_{n,s}^2 + v_{n,R_p}^2 + v_{n,LO}^2 + v_{n,Gm}^2}{v_{n,s}^2} = 2 + \frac{v_{n,LO}^2}{v_{n,s}^2} + \frac{v_{n,Gm}^2}{v_{n,s}^2}$$

(4.6)

where  $v_{n,R_p}$  is the  $R_p$  resistor noise voltage which is equal to  $v_{n,s}$  since  $R_p$  is equal to the antenna resistance. Substituting the expressions from equations ?? and ?? we get:

$$NF = 2 + \frac{K_{n,LO}}{M_{mixer}} + \frac{K_{n,Gm}}{G_m}$$

$$\tag{4.7}$$

From equation ?? we can write the required  $G_m$  for a given noise figure and mixer size:

$$G_m(M_{mixer}) = \frac{K_{n,Gm}}{NF - 2 - \frac{K_{n,LO}}{M_{mixer}}}$$

(4.8)

And from equations ?? and ?? we can derive the expression for the total power consumption as a function of the noise figure and the mixer size:

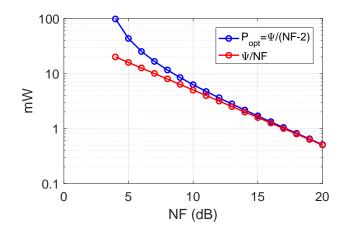

$$P_{total}\left(M_{mixer}\right) = K_{p,LO}M_{mixer} + K_{p,Gm}G_m\left(M_{mixer}\right) = K_{p,LO}M_{mixer} + \frac{K_{p,Gm}K_{n,Gm}}{NF - 2 - \frac{K_{n,LO}}{M_{mixer}}} \quad (4.9)$$