### Configurable Data Converters for Digitally Adaptive Radio

*Amy Whitcombe Borivoje Nikolic, Ed.*

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2019-156 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2019/EECS-2019-156.html

December 1, 2019

Copyright © 2019, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### Configurable Data Converters for Digitally Adaptive Radio

by

Amy Whitcombe

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Elad Alon Professor Aaron Parsons

Fall 2018

Configurable Data Converters for Digitally Adaptive Radio

Copyright © 2018 by Amy Whitcombe

#### Abstract

#### Configurable Data Converters for Digitally Adaptive Radio

by

Amy Whitcombe

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley Professor Borivoje Nikolić, Chair

In the past few decades, wireless connectivity has grown from an expensive luxury to an integral component of everyday life, creating a need for wireless systems that can satisfy exponentially growing demand for data in an energy- and cost-efficient manner. New techniques such as digital beamforming can utilize spatial diversity to support multiple users with arrays of radio elements, but the required performance of these elements varies with array size. Additionally, while conventional single-element radios are typically designed to meet stringent performance requirements outlined in wireless standards, peak performance is rarely required. Adaptive wireless receivers that configure performance to suit a system's needs may therefore serve as building blocks for energy-efficient wireless platforms, and enhanced digital processing capabilities afforded by CMOS technology scaling can help realize fully integrated smart wireless systems. However, while computation improvements due to process scaling have driven the adoption of smart devices, complex design rules and lower supply voltages often make it difficult to construct high-performance analog circuits such as wireless receivers in advanced process nodes. To that end, this dissertation discusses the design and implementation of analog-to-digital interface circuits for receivers that are both configurable and well-suited to implementation in scaled nodes optimized for digital performance. It first explores circuit-level techniques for constructing resolution-configurable receivers from scalable elements, and then discusses an alternative receiver design that can integrate scalability at the architecture level.

To explore how circuit-level design techniques can enable configurability, this dissertation first discusses the design of a resolution-scalable successive approximation (SAR) analogto-digital converter (ADC) for wireless receiver applications. The converter is built with a scalable capacitive digital-to-analog converter (DAC), comparator, and tunable switching algorithm to trade power for resolution. The 80 MS/s prototype converter implemented in a general purpose 65nm CMOS process consumes 0.4-0.8 mW and provides 7.0-9.1 effective bits of resolution in a 10 MHz signal bandwidth. It is integrated with a power-scalable receiver to demonstrate its suitability for wireless systems. By trading noise for power consumption, this receiver can serve as a building block for energy efficient digital beamforming arrays.

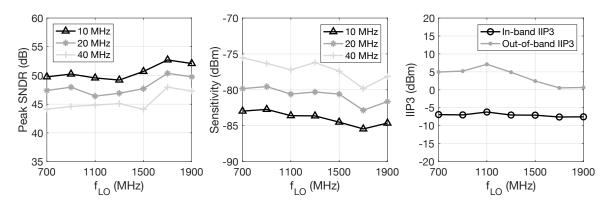

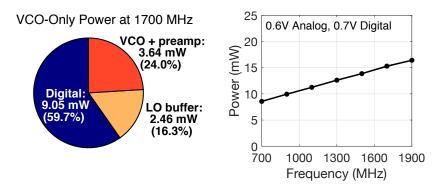

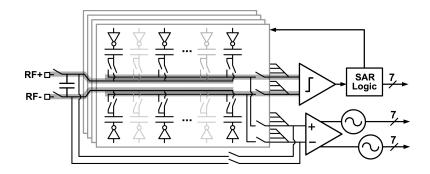

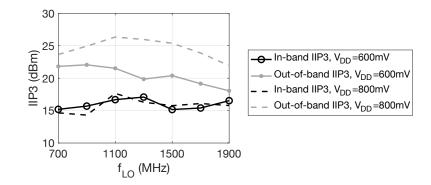

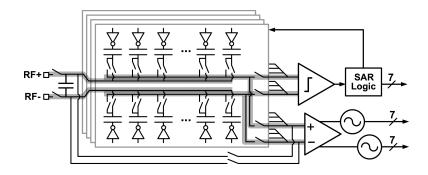

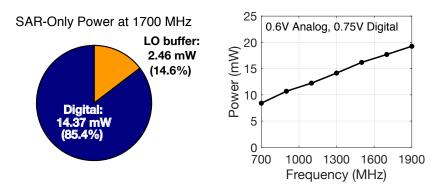

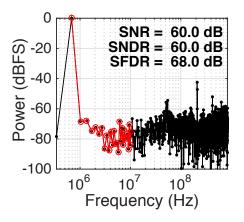

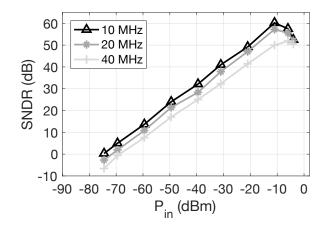

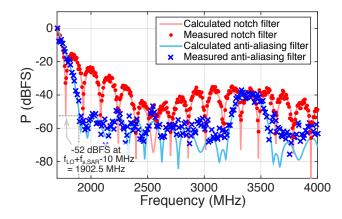

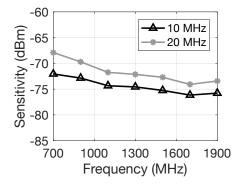

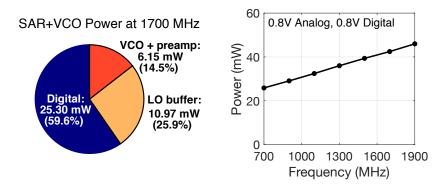

Finally, this thesis demonstrates architectural techniques for affording configurability by discussing the design and implementation of a reconfigurable, digital-intensive RF-todigital converter. The proposed receiver uses a SAR ADC with integrated discrete-time filtering to provide high linearity and a voltage-controlled oscillator (VCO) based ADC to improve sensitivity. By replacing the high-performance active amplifiers and filters used in conventional receivers with an ADC constructed from digital building blocks, the 16nm CMOS FinFET prototype can leverage the benefits of technology scaling. In low-power mode, the 0.7-1.9 GHz receiver is configured as a VCO-based design drawing 9-16 mW and providing -82 dBm sensitivity in a 10 MHz bandwidth. In blocker-tolerant mode, the SAR ADC can be enabled to obtain 60 dB SNDR and an in-band IIP3 of +16 dBm. The prototype achieves performance comparable to state-of-the-art RF-to-digital converters using an easily configurable digital-intensive design. Overall, both configurability techniques discussed in this dissertation are promising means of leveraging the advantages of CMOS scaling to enable future digitally adaptive wireless systems.

# Contents

| Li | st of       | f Figures                                     | iii     |

|----|-------------|-----------------------------------------------|---------|

| 1  | Intr        | roduction                                     | 1       |

|    | 1.1         | Research scope                                | 1       |

|    |             | 1.1.1 CMOS scaling and analog design          | 1       |

|    |             | 1.1.2 Motivation for reconfigurable receivers | 3       |

|    |             | 1.1.3 Research focus                          | 4       |

|    | 1.2         | Related work                                  | 5       |

|    |             | 1.2.1 Configurable receivers                  | 5       |

|    |             | 1.2.2 Process scalable receivers              | 6       |

|    |             | 1.2.3 Contribution of this work               | 7       |

|    | 1.3         | Thesis organization                           | 7       |

| 2  | Det         | to Communication for Windows Applications     | 8       |

| 4  | 2.1         | ta Conversion for Wireless Applications       | 8       |

|    | $\angle .1$ | Performance requirements of wireless systems  | 0<br>9  |

|    |             | 2.1.1    Applications                         | 9<br>10 |

|    |             |                                               | 10      |

|    | 2.2         |                                               | 11      |

|    | 2.2         | Receiver & ADC specifications                 | 11      |

|    |             | 2.2.1 Receiver design                         |         |

|    | 0.0         | 2.2.2 ADC design                              | 14      |

|    | 2.3         | Alternative receiver architectures            | 17      |

|    |             | 2.3.1 MIMO radio arrays                       | 17      |

|    |             | 2.3.2 Software-defined radio                  | 21      |

| 3  | A r         | resolution-configurable ADC                   | 23      |

|    | 3.1         | Prior scalable ADC designs                    | 24      |

|    |             | 3.1.1 Pipelined ADCs                          | 24      |

|    |             | 3.1.2 Oversampled ADCs                        | 25      |

|    |             | 3.1.3 Successive approximation ADCs           | 26      |

|    | 3.2         | SAR ADC design considerations                 | 27      |

|    |             | 3.2.1 General topology                        | 27      |

|    |             | 3.2.2 Capacitive DAC and Sampling             | 29      |

|    |             | 3.2.3 Logic                                   | 35      |

|    |             | 3.2.4 Comparator                              | 37      |

|          |     | 3.2.5 Considerations for scalable SAR design                                                                                                                       |

|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 3.3 | Prototype implementation                                                                                                                                           |

|          |     | 3.3.1 Comparator bias tuning and DAC switching                                                                                                                     |

|          |     | 3.3.2 Capacitive DAC                                                                                                                                               |

|          |     | 3.3.3 Logic                                                                                                                                                        |

|          |     | 3.3.4 Comparator                                                                                                                                                   |

|          |     | $3.3.5$ Top-level design $\ldots \ldots 58$               |

|          | 3.4 | Measurement results                                                                                                                                                |

|          |     | 3.4.1 Measurement setup                                                                                                                                            |

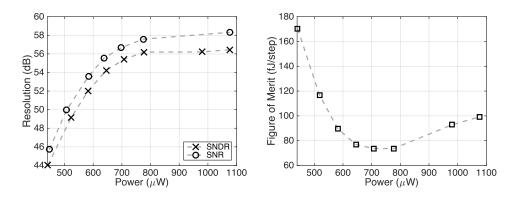

|          |     | $3.4.2$ Overall scalability $\ldots \ldots \ldots$ |

|          |     | 3.4.3 Performance across configuration schemes                                                                                                                     |

|          |     | 3.4.4 Comparison to prior work                                                                                                                                     |

|          |     | 3.4.5 Analysis of scalability limitations                                                                                                                          |

|          | 3.5 | Conclusion                                                                                                                                                         |

|          |     |                                                                                                                                                                    |

| 4        |     | hitecture-configurable RF-to-digital receiver 77                                                                                                                   |

|          | 4.1 | Prior software-defined radio work                                                                                                                                  |

|          |     | 4.1.1 Direct RF-to-digital receiver design                                                                                                                         |

|          |     | 4.1.2 Mixer-first receiver design $\dots \dots \dots$              |

|          |     | 4.1.3 Filtering SAR ADC                                                                                                                                            |

|          | 4.0 | 4.1.4 Limitations of prior work                                                                                                                                    |

|          | 4.2 | Design considerations                                                                                                                                              |

|          |     | 4.2.1 Filtering SAR ADC design                                                                                                                                     |

|          | 4.9 | 4.2.2 VCO-based ADC design                                                                                                                                         |

|          | 4.3 | Prototype implementation 95   4.3.1 Overview   96                                                                                                                  |

|          |     |                                                                                                                                                                    |

|          |     | 4.3.2 Input sampling $\dots \dots \dots$                           |

|          |     | $4.3.3  \text{SAR} + \text{FIR filter} \qquad 101$                                                                                                                 |

|          |     | 4.3.4 VCO-based ADC                                                                                                                                                |

|          |     | 4.3.5 Signal recombination $\dots \dots \dots$                     |

|          | 4 4 | $4.3.6  \text{Top-level design} \dots \dots$                 |

|          | 4.4 | Measurement results                                                                                                                                                |

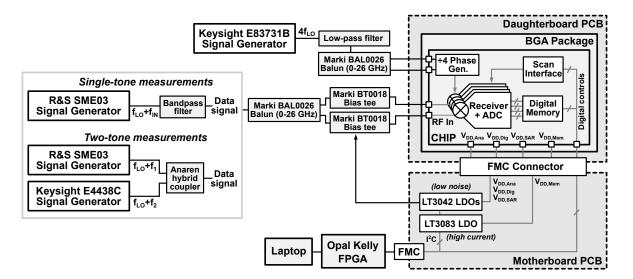

|          |     | 4.4.1 Measurement setup $\dots \dots \dots$                        |

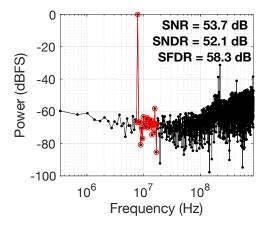

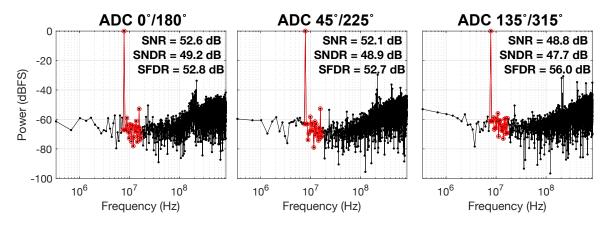

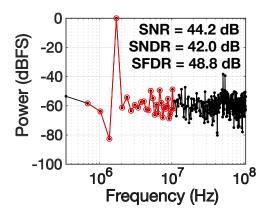

|          |     | 4.4.2 VCO mode                                                                                                                                                     |

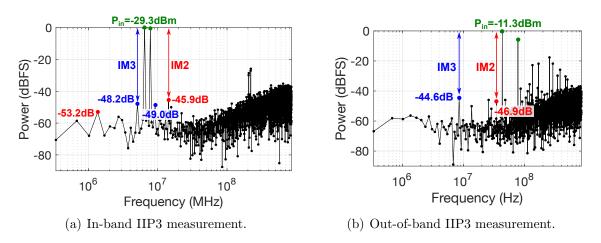

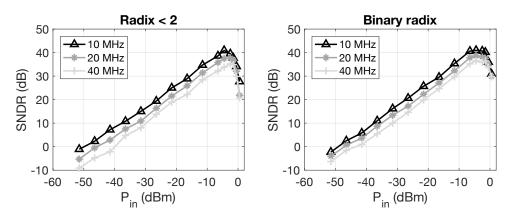

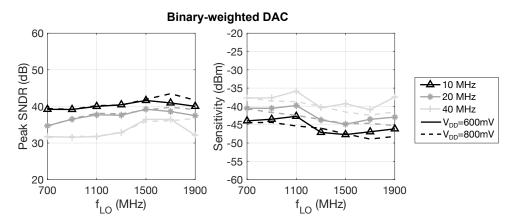

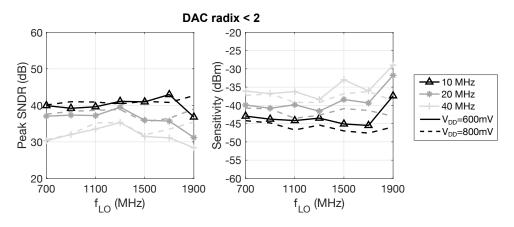

|          |     | $4.4.3  \text{SAR mode} \dots \dots$                         |

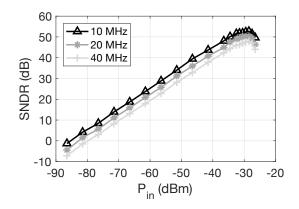

|          |     | $4.4.4  \text{SAR+VCO mode}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                                      |

|          | 4 5 | 4.4.5 Architecture comparison                                                                                                                                      |

|          | 4.5 | Conclusions                                                                                                                                                        |

| <b>5</b> | Con | clusion 135                                                                                                                                                        |

|          | 5.1 | Main contributions                                                                                                                                                 |

|          | 5.2 | Future work                                                                                                                                                        |

|          |     |                                                                                                                                                                    |

# List of Figures

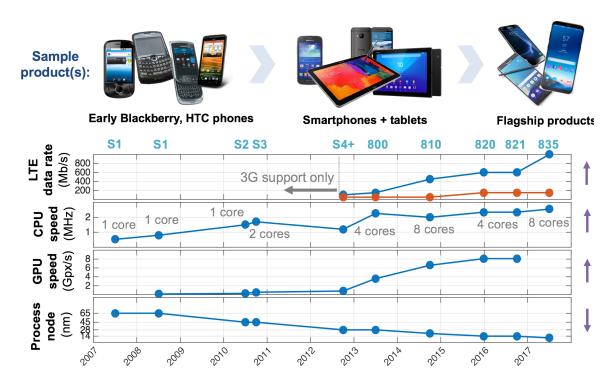

| 1.1          | Capabilities of Qualcomm Snapdragon SoCs over time                                                           |

|--------------|--------------------------------------------------------------------------------------------------------------|

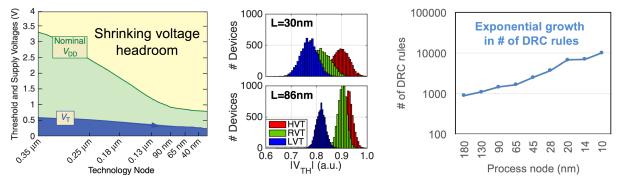

| 1.2          | CMOS technology scaling challenges                                                                           |

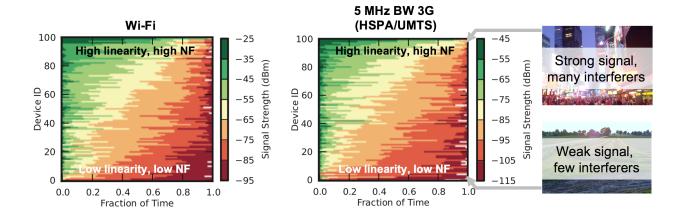

| 1.3          | Measured wireless signal strength in a variety of handheld devices                                           |

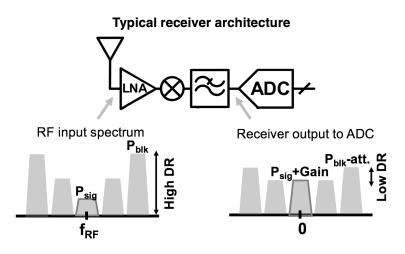

| 1.4          | Generic receiver topology and spectrum before and after receiver                                             |

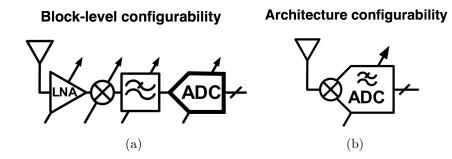

| 1.5          | Comparison between approaches to designing configurable receivers 5                                          |

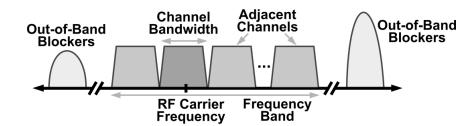

| 2.1          | Generic wireless spectrum                                                                                    |

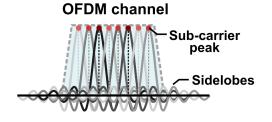

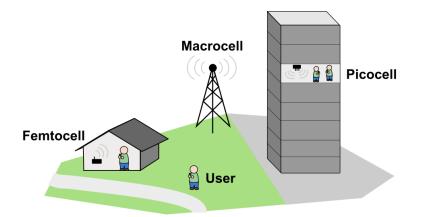

| $2.2 \\ 2.3$ | Sample channel using orthogonal frequency division multiplexing (OFDM). Examples of various wireless devices |

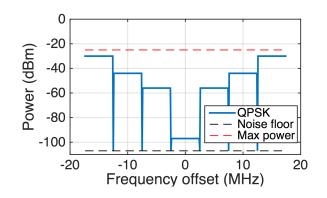

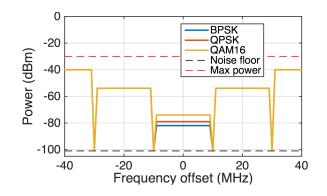

| 2.0<br>2.4   | Adjacent channel selectivity requirement of 5 MHz LTE                                                        |

| 2.5          | Adjacent channel selectivity requirement of 20 MHz Wi-Fi                                                     |

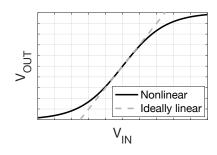

| 2.6          | Ideally linear (dashed) vs. nonlinear (solid) voltage transfer curve                                         |

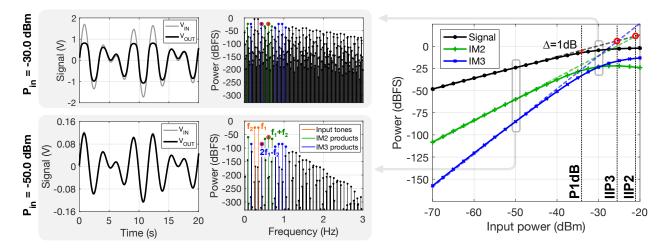

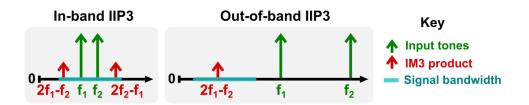

| 2.7          | Linearity characterization metrics                                                                           |

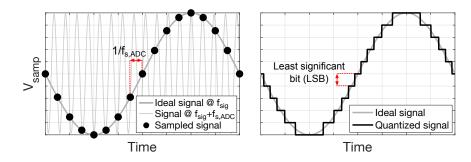

| 2.8          | ADC performance limitations                                                                                  |

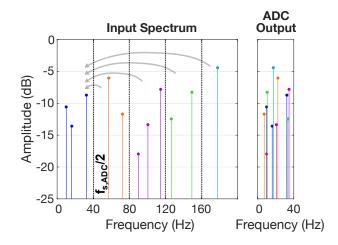

| 2.9          | Aliasing effects in the frequency domain                                                                     |

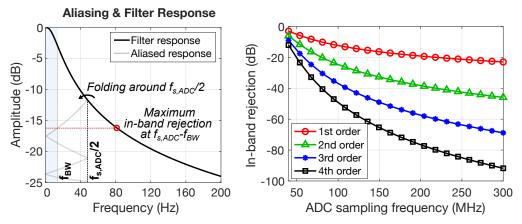

| 2.10         | Impact of ADC sampling rate on anti-alias filtering                                                          |

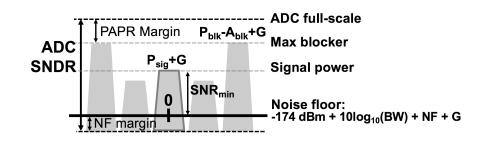

|              | Receiver design parameters + ADC design requirements                                                         |

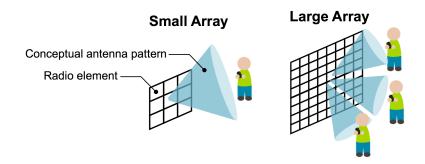

|              | Concept of spatial multiplexing via beamforming                                                              |

|              | Example of 4-element array averaging                                                                         |

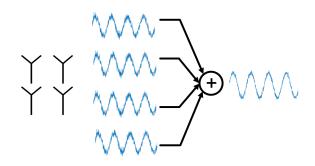

|              | ADC-limited array SNR vs. array size                                                                         |

| 2.15         | Receiver and array design parameters + ADC design requirements 19                                            |

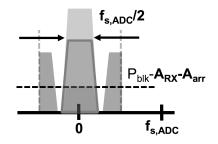

| 2.16         | Aliased blockers with power $P_{blk}$ are attenuated by spatial filtering from re-                           |

|              | ceiver $(A_{arr})$ in addition to filtering from the receiver $(A_{RX})$                                     |

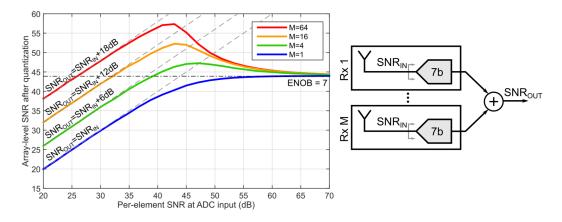

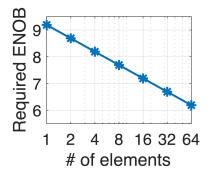

| 2.17         | Required ADC resolution vs. array size                                                                       |

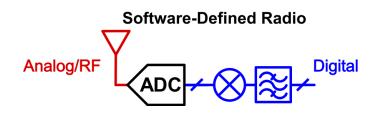

| 2.18         | Software-defined radio concept                                                                               |

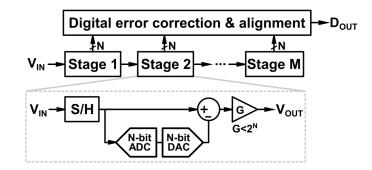

| 3.1          | Pipelined converter block diagram                                                                            |

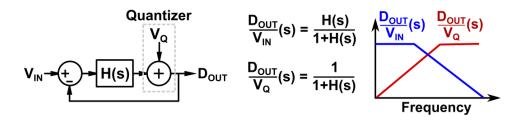

| 3.2          | $\Delta\Sigma$ converter block diagram                                                                       |

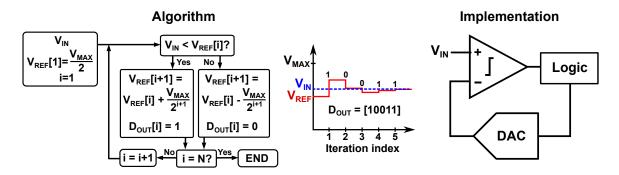

| 3.3          | Successive approximation algorithm                                                                           |

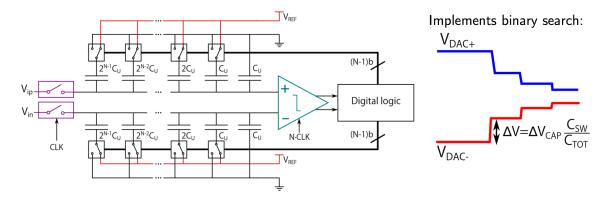

| 3.4          | Diagram of differential capacitive DAC-based SAR ADC                                                         |

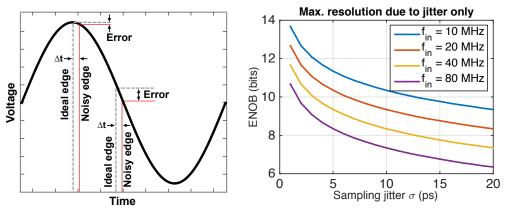

| 3.5          | Sampling jitter effects                                                                                      |

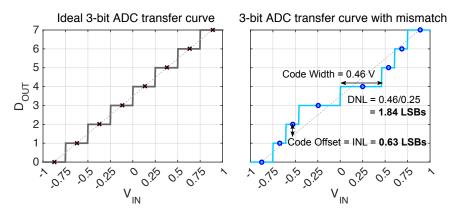

| 3.6          | INL and DNL example                                                                                          |

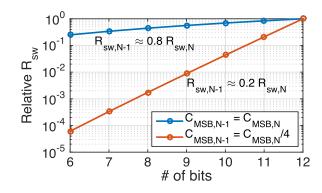

| 3.7          | DAC switch resistance scalability                                                                            |

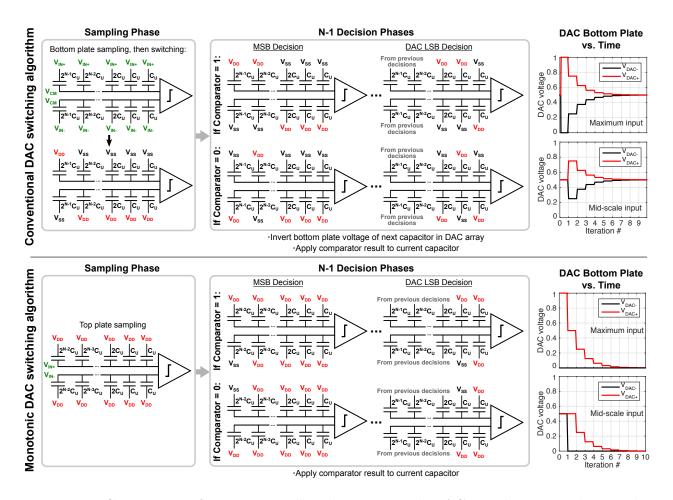

| 3.8          | Conventional vs. monotonic DAC switching procedures                                                          |

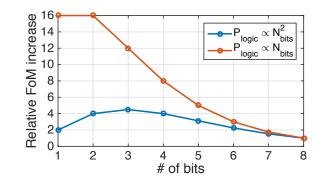

| 3.9          | Impact of logic scalability on ADC FoM                                                                       |

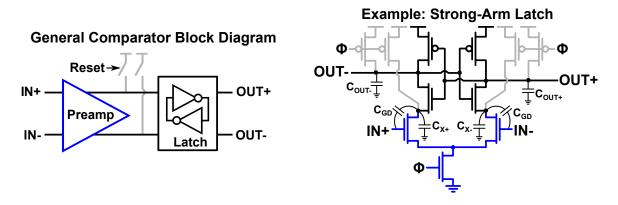

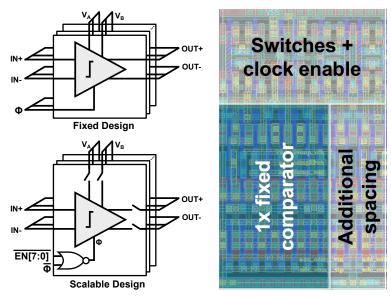

| 3.10 | Scalable comparator diagram                                             |

|------|-------------------------------------------------------------------------|

| 3.11 | Diagram of prototype receiver $+$ ADC, as presented in [1]. $\ldots$ 43 |

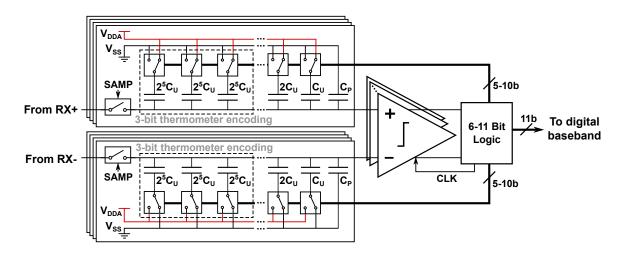

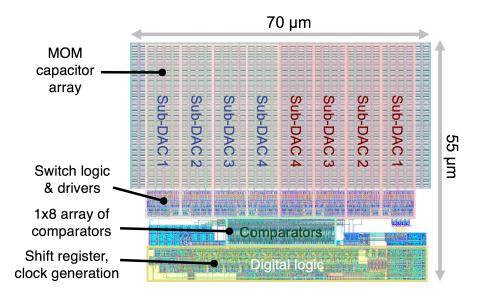

|      | Scalable ADC design topology                                            |

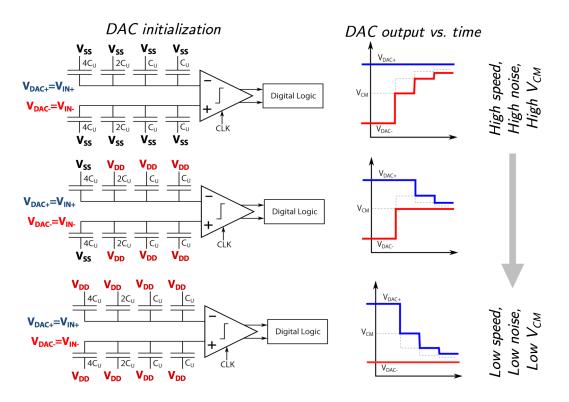

| 3.13 | $V_{CM}$ -programmable DAC switching procedure                          |

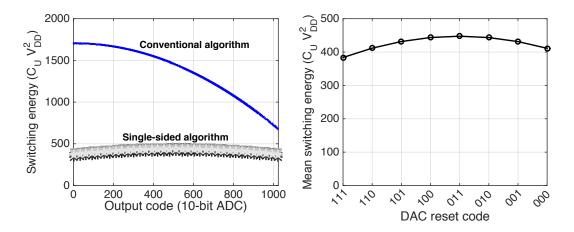

| 3.14 | Simulated DAC switching energy for programmable switching procedure 45  |

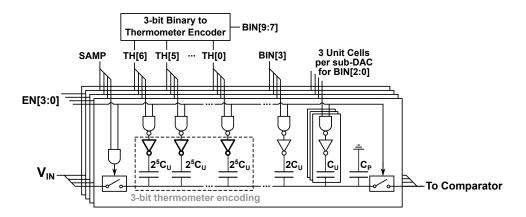

| 3.15 | Schematic of DAC diagram                                                |

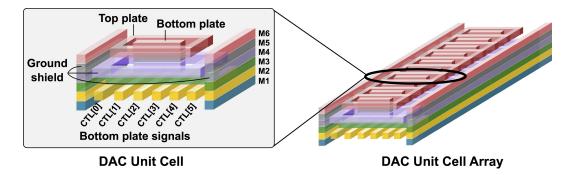

|      | Diagram of DAC unit cell layout                                         |

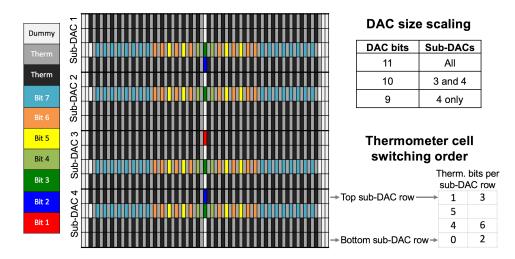

|      | Diagram of common centroid DAC unit cell layout                         |

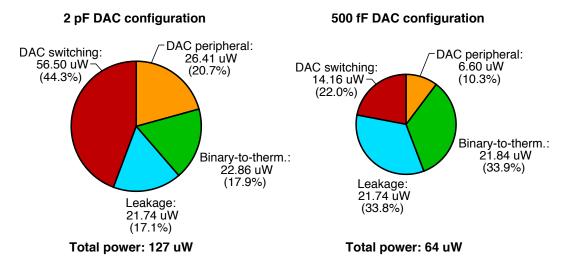

| 3.18 | DAC power consumption breakdown                                         |

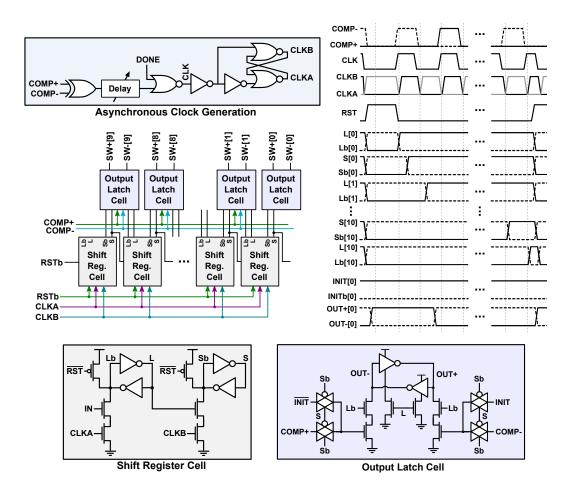

| 3.19 | Resolution-scalable ADC logic implementation                            |

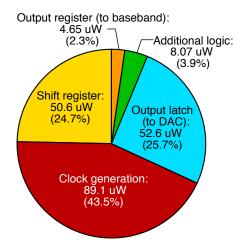

|      | Logic power breakdown                                                   |

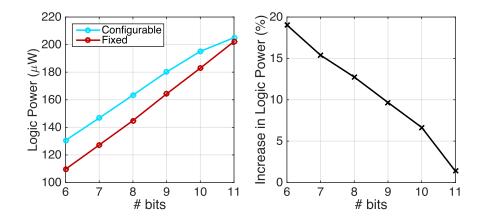

|      | Configurable vs. fixed logic power                                      |

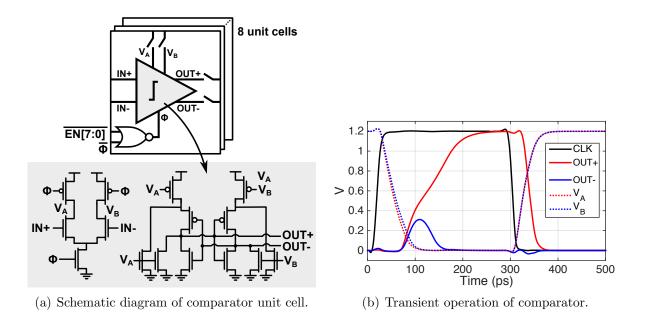

|      | Operation of scalable double-tail comparator cell                       |

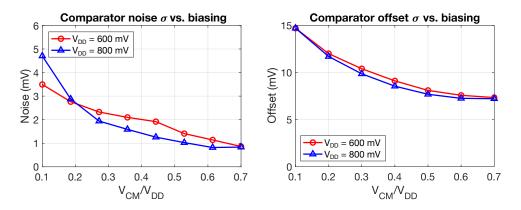

|      | Scalable comparator performance                                         |

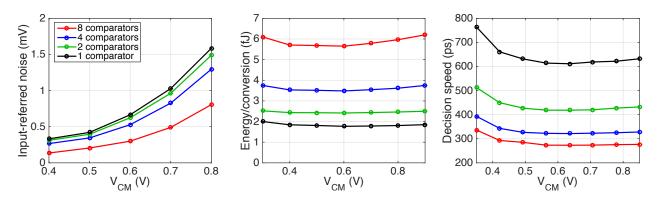

| 3.24 | Scalable comparator offset vs. $V_{CM}$                                 |

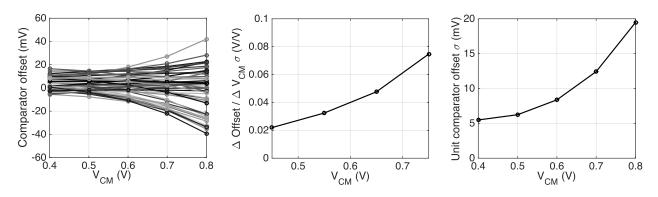

|      | Comparator offset calibration example                                   |

|      | Fixed vs. configurable comparator implementation                        |

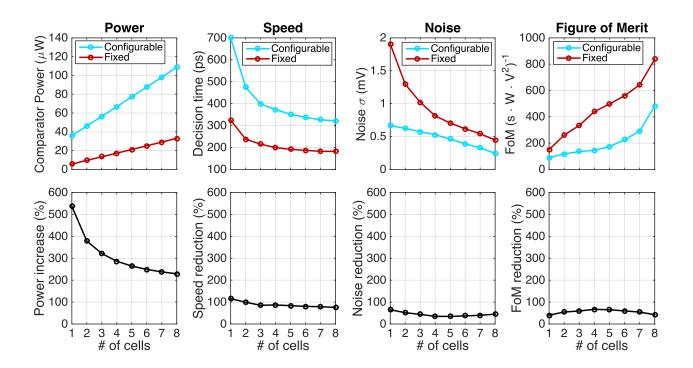

|      | Scalable vs. fixed comparator performance                               |

|      | Scalable ADC layout                                                     |

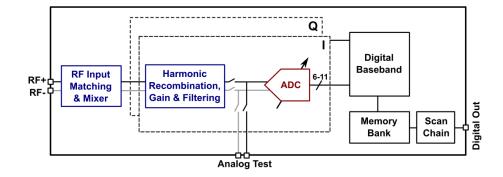

|      | Block diagram of blocks interacting with scalable ADC                   |

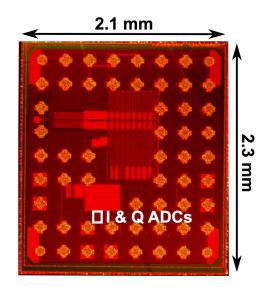

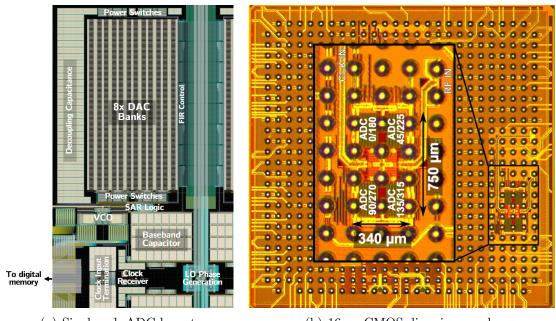

|      | 65nm CMOS Die micrograph                                                |

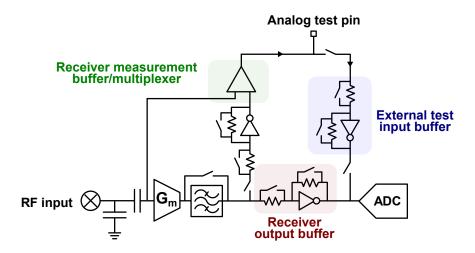

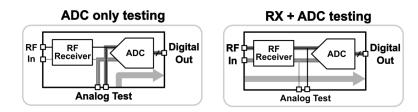

|      | Interface between receiver, ADC, and test pin                           |

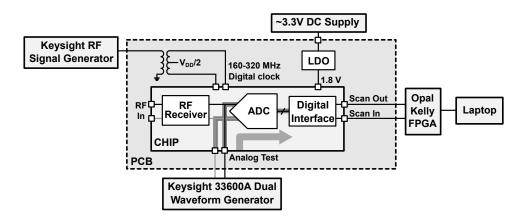

|      | ADC test configuration                                                  |

|      | Nyquist-rate ADC performance summary                                    |

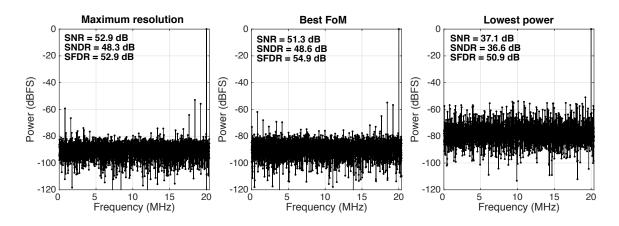

| 3.34 | Nyquist-rate ADC FFT comparison                                         |

| 3.35 | Oversampling ADC performance summary                                    |

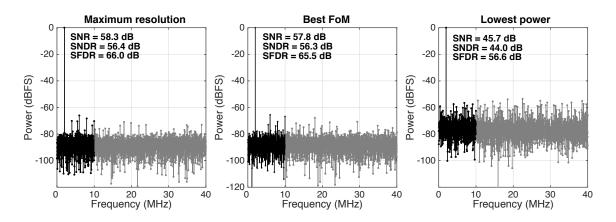

|      | Oversampling ADC FFT comparison                                         |

| 3.37 | Stand-alone ADC vs. receiver+ADC test configuration                     |

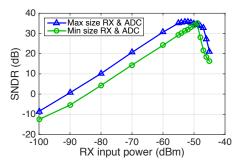

|      | ADC SNDR vs. receiver input power                                       |

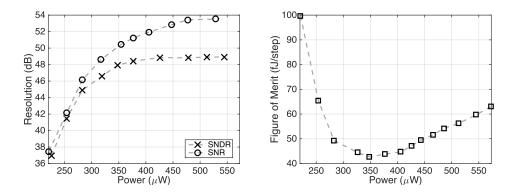

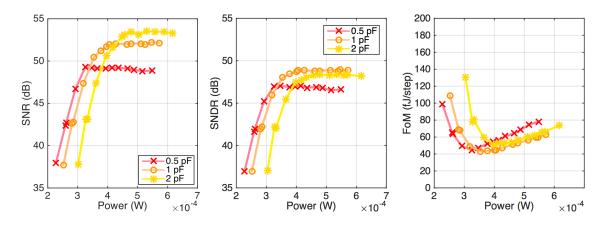

| 3.39 | SNR, SNDR, and FoM as a function of DAC size                            |

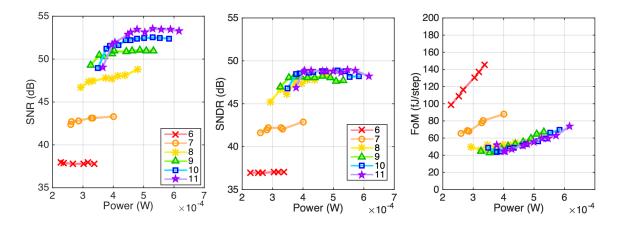

| 3.40 | SNR, SNDR, and FoM as a function of number of bits                      |

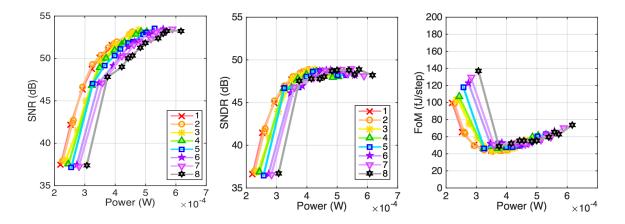

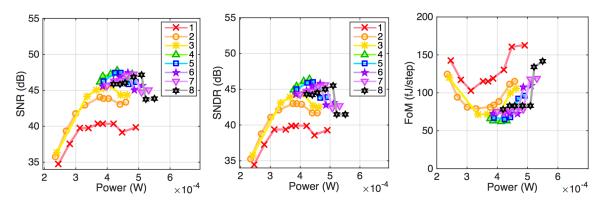

| 3.41 | SNR, SNDR, and FoM as a function of number of comparators               |

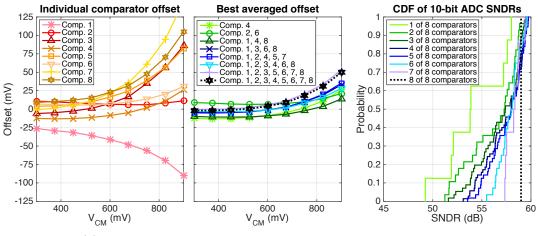

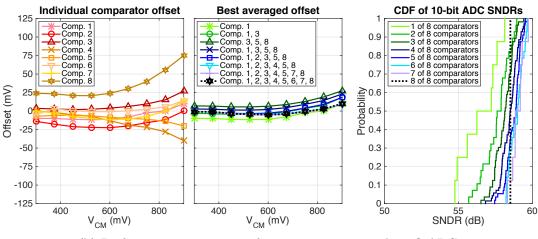

| 3.42 | Comparator offset distribution measurements                             |

| 3.43 | SNR, SNDR, and FoM vs. number of comparators with high $V_{CM}$         |

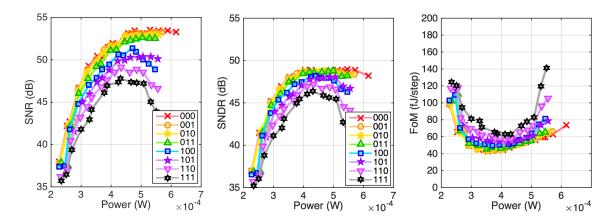

| 3.44 | SNR, SNDR, and FoM for vs. switching scheme                             |

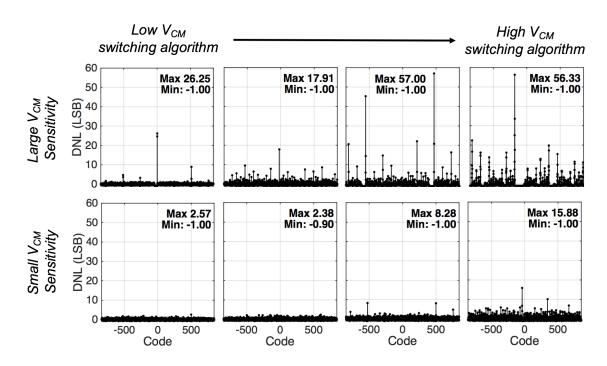

| 3.45 | Measured DNL vs. switching procedure                                    |

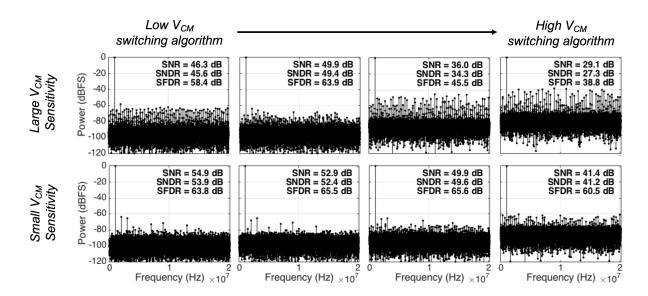

| 3.46 | Measured FFT vs. switching procedure                                    |

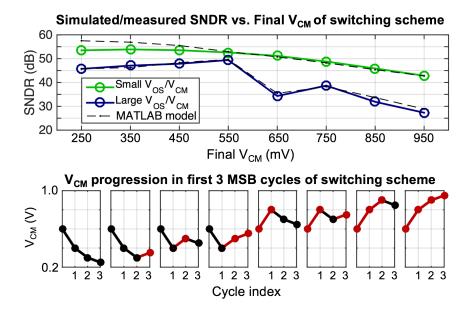

| 3.47 | Measured vs. simulated SNDR vs. switching procedure                     |

| 3.48 | Figure of merit comparison to prior ADCs                                |

| 3.49 | Comparison table                                                        |

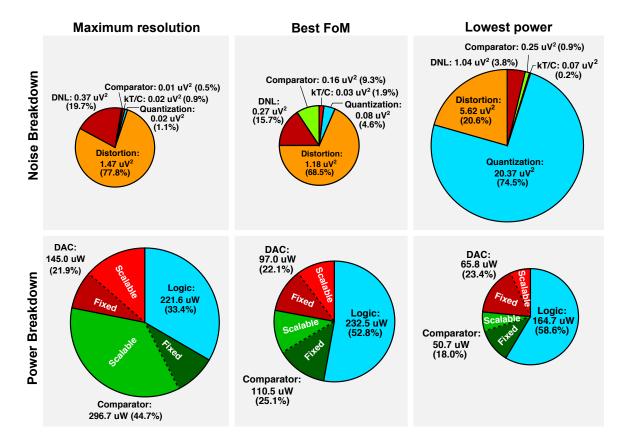

| 3.50 | Breakdown of ADC noise and power consumption vs. configuration 74       |

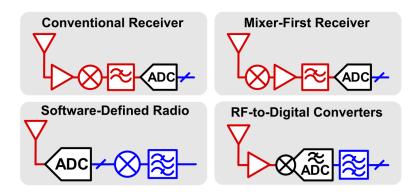

| 4.1  | Comparison of receiver architectures                                    |

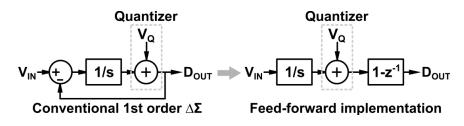

| 4.2  | Feedback vs. feed-forward first order $\Delta\Sigma$ block diagram      |

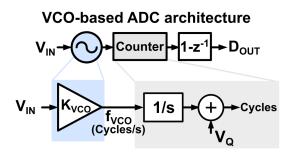

| 4.3  | VCO-based ADC concept                                                   |

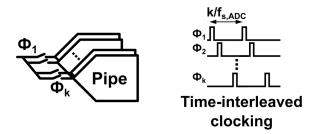

| 4.4  | Time interleaved pipelined ADC structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

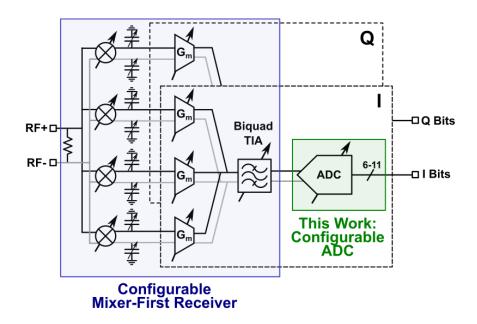

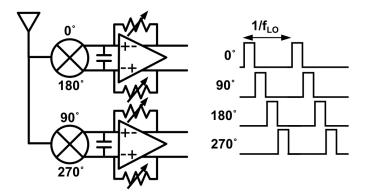

| 4.5  | Sample 4-phase mixer-first receiver architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

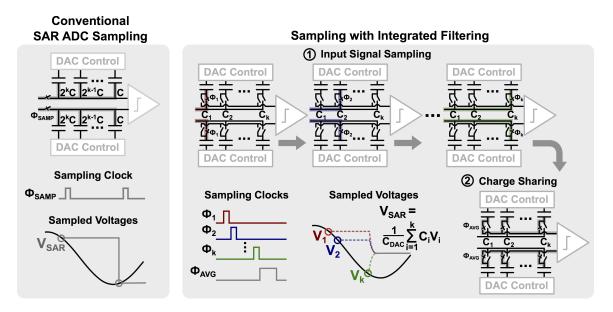

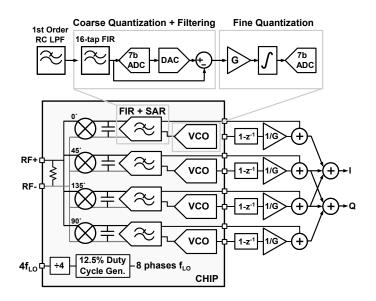

| 4.6  | FIR/SAR filtering example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.7  | Diagram of implemented RF-to-digital receiver topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

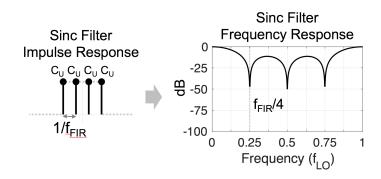

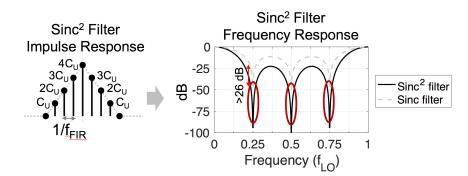

| 4.8  | Example 4-tap sinc filter impulse response (left) and frequency response (right). 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.9  | Example 4-tap $\operatorname{sinc}^2$ filter impulse response (left) and frequency response (right). 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

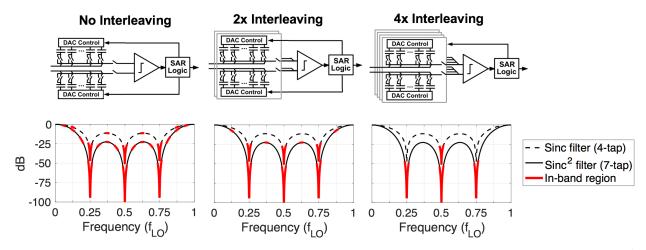

| 4.10 | Effect of DAC interleaving on frequencies that alias in-band for sinc and $\operatorname{sinc}^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | filter configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

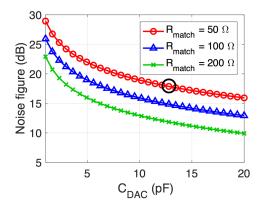

| 4.11 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

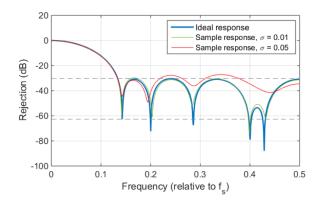

|      | Sample effect of mismatch on 11-tap FIR filter frequency response with weights                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      | $[1\ 2\ 3\ 4\ 5\ 5\ 5\ 4\ 3\ 2\ 1]. \qquad 90$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

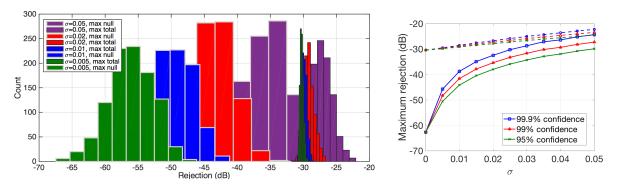

| 4.13 | Summary of mismatch effects on FIR filter rejection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

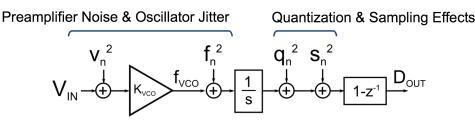

|      | Block diagram of the VCO-based ADC, including noise sources 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

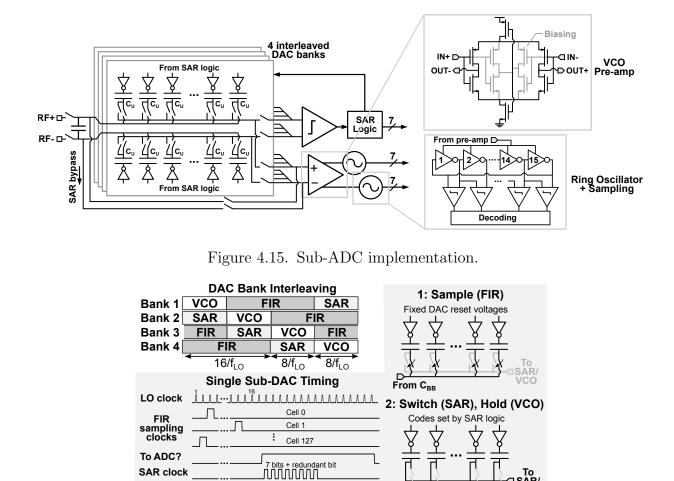

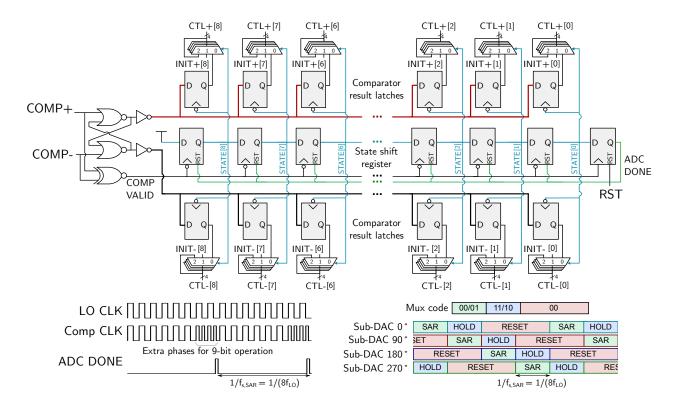

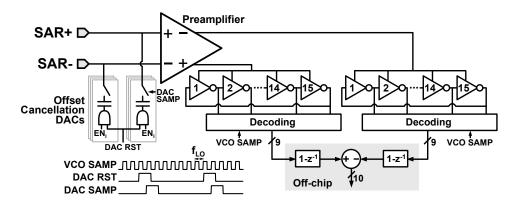

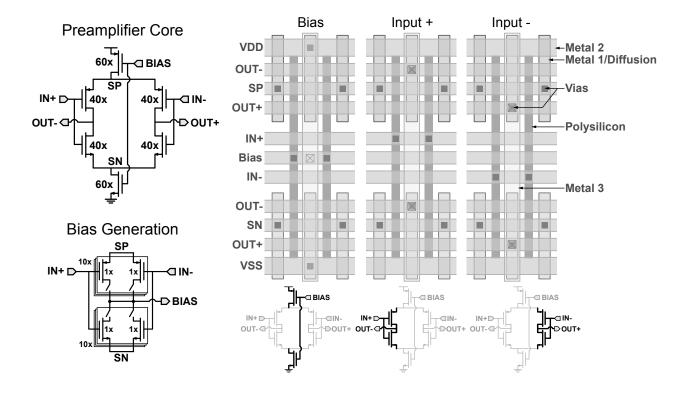

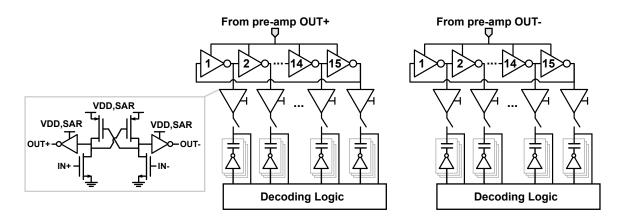

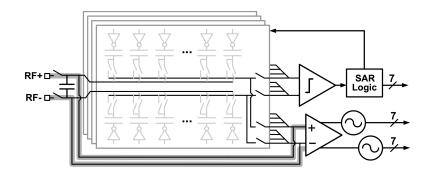

| 4.15 | Sub-ADC implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.16 | Sub-ADC timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | Input sampling network for single sub-ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

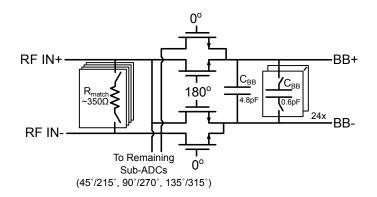

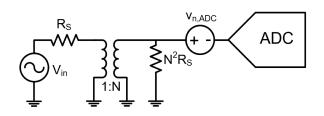

| 4.18 | Single-ended impedance transformation example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

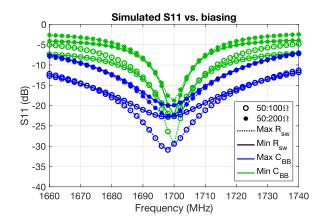

|      | Simulated S11 of input sampling network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

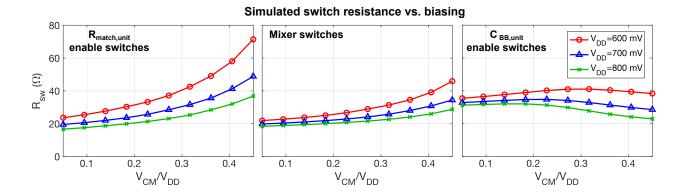

| 4.20 | Simulated input network switch resistances vs. bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

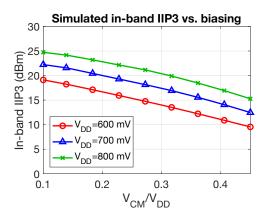

| 4.21 | Simulated IIP3 of mixer vs. bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

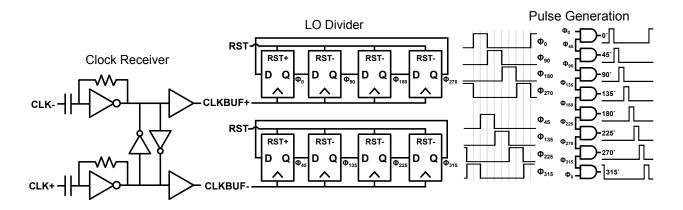

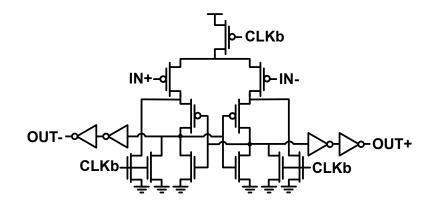

| 4.22 | Clock receiver and LO divider schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

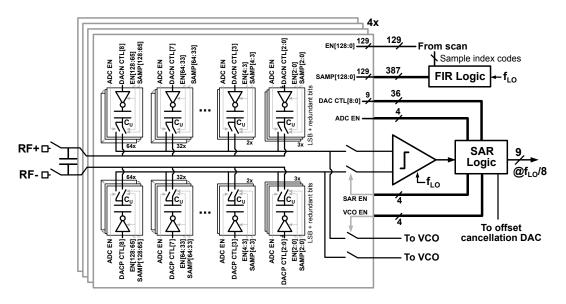

| 4.23 | Detailed schematic implementation of FIR filter / SAR ADC 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

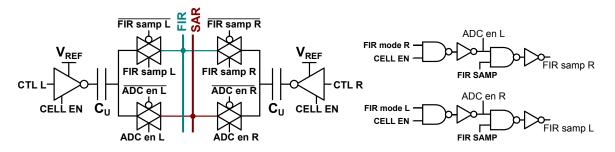

| 4.24 | DAC unit cell implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

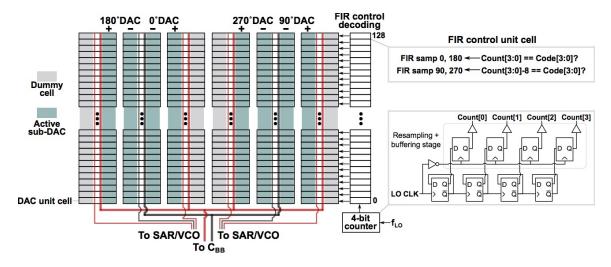

| 4.25 | Overall DAC and FIR sampling cell implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

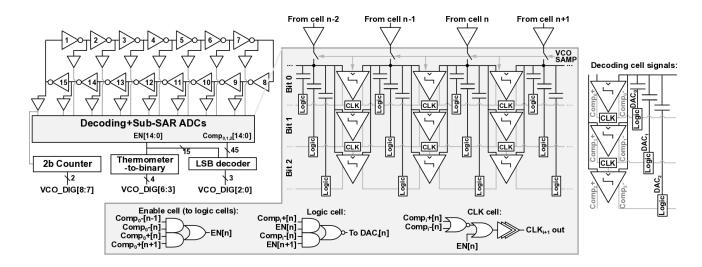

| 4.26 | SAR ADC logic implementation and clocking scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

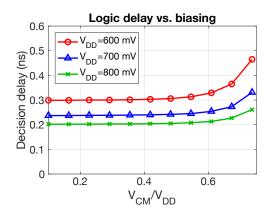

| 4.27 | Logic delay vs. biasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

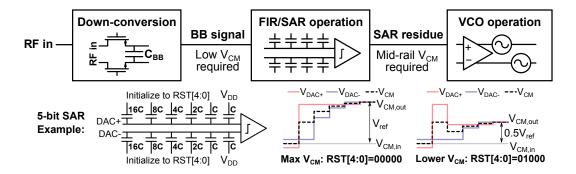

| 4.28 | $V_{CM}$ -programmable SAR switching procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

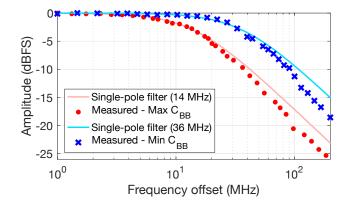

| 4.29 | See See Frank Fr |

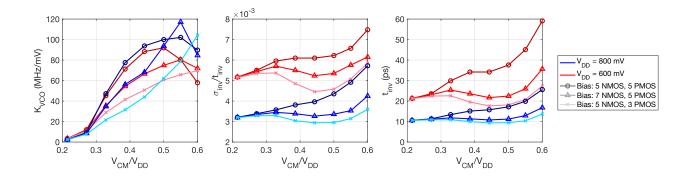

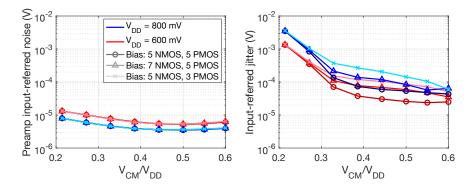

| 4.30 | Strong arm latch characterization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

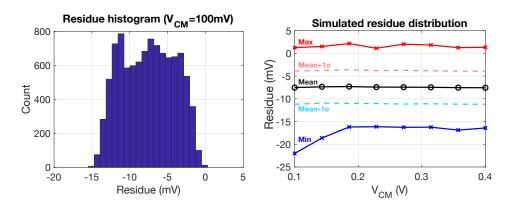

|      | Expected SAR residue distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |