# Energy-Efficient System Design Through Adaptive Voltage Scaling

Ben Keller Borivoje Nikolic, Ed. Krste Asanović, Ed. Duncan Callaway, Ed.

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2019-146 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2019/EECS-2019-146.html

December 1, 2019

Copyright © 2019, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Energy-Efficient System Design Through Adaptive Voltage Scaling

by

Benjamin Andrew Keller

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Borivoje Nikolić, Co-chair Professor Krste Asanović, Co-chair Associate Professor Duncan Callaway

Fall 2017

#### Energy-Efficient System Design Through Adaptive Voltage Scaling

$\begin{array}{c} \text{Copyright 2017} \\ \text{by} \\ \text{Benjamin Andrew Keller} \end{array}$

#### Abstract

Energy-Efficient System Design Through Adaptive Voltage Scaling

by

Benjamin Andrew Keller

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Co-chair

Professor Krste Asanović, Co-chair

Improving the energy efficiency of processor systems-on-chip (SoCs) is key to improving the performance and utility of thermally-limited servers, battery-constrained mobile devices, and energy-harvesting Internet-of-Things nodes. Adaptive voltage scaling adjusts voltage levels at runtime in response to changes in workload, reducing voltage when additional performance is not required. The granularity of this voltage scaling greatly impacts its effectiveness. Fine-grained adaptive voltage scaling (FG-AVS) in time reduces wasted energy by tracking microsecond-scale changes in workload; FG-AVS in space independently adjusts voltage levels in many different portions of an SoC, saving additional energy. FG-AVS has the potential to save considerable energy, but it has not yet seen adoption in commercial systems due to several challenges that complicate its implementation. Integrated voltage regulators are required to supply the many voltages required and switch quickly between modes, but efficient implementations impose high area overhead. Clocking, synchronization, and power management have their own requirements and difficulties.

This work presents key components of fully-featured SoCs that enable demonstration of FG-AVS. Integrated simultaneous-switching switched capacitor voltage regulators are presented that achieve high conversion efficiency when coupled with an adaptive clock generator. Power management is accomplished with programs run on a dedicated power management unit (PMU), and a pausible bisynchronous FIFO circuit that can achieve low-latency communication between asynchronous voltage domains is described. These components are integrated into systems that demonstrate the potential energy savings of FG-AVS. The Raven-3 testchip demonstrates efficient voltage regulation supplying a complicated digital load; the system achieves 26.2 GFLOPS/W while operating its processor under the generated supply voltage and adaptive clock. The Raven-4 testchip includes integrated power management circuits that allow fully integrated feedback for FG-AVS. The programmable PMU can run a wide variety of power management algorithms, including an AVS algorithm that saves 39.6% energy in a synthetic microbenchmark with minimal performance penalty. The Hurricane-1 testchip implements multiple independent voltage domains and hardware counters that can

be used for power management. The Hurricane-2 testchip features finer spatial partitioning and more effective instrumentation for power management; simulation results show up to 13.3% energy savings for an algorithm exercising FG-AVS in time and 46.0% energy savings for an algorithm using FG-AVS in space. Together, these testchip implementations show the potential of FG-AVS to save energy in production SoCs.

To Helen.

# Contents

| $\mathbf{C}$ | Contents |        |                                                     |              |

|--------------|----------|--------|-----------------------------------------------------|--------------|

| Li           | st of    | Figure | es                                                  | $\mathbf{v}$ |

| Li           | st of    | Tables | 5                                                   | xii          |

| 1            | Intr     | oducti | ion                                                 | 1            |

|              | 1.1      | Motiva | ation                                               | 1            |

|              |          | 1.1.1  | Energy Efficiency in Datacenters                    | 2            |

|              |          | 1.1.2  | Energy Efficiency in Mobile Devices                 | 4            |

|              |          | 1.1.3  | Energy Efficiency in IoT Devices                    | 5            |

|              | 1.2      | Funda  | mentals of Fine-Grained Adaptive Voltage Scaling    | 5            |

|              |          | 1.2.1  | Voltage Scaling Granularity                         | 6            |

|              |          | 1.2.2  | Globally Asynchronous, Locally Synchronous Design   | 7            |

|              |          | 1.2.3  | Challenges of Fine-Grained Adaptive Voltage Scaling | 8            |

|              | 1.3      | Techno | ology Trends                                        | 9            |

|              |          | 1.3.1  | Process Variation                                   | 9            |

|              |          | 1.3.2  | Workloads                                           | 9            |

|              |          | 1.3.3  | SoC Design                                          | 10           |

|              | 1.4      | Disser | tation Outline                                      | 10           |

| 2            | Cha      | llenge | s of Adaptive Voltage Scaling                       | 12           |

|              | 2.1      | Voltag | ge Regulation                                       | 12           |

|              |          | 2.1.1  | Integrated Regulation                               | 13           |

|              |          | 2.1.2  | Multi-rail Switching                                | 16           |

|              |          | 2.1.3  | Voltage Dithering                                   | 17           |

|              | 2.2      | Clock  | Generation                                          | 20           |

|              | 2.3      | Clock  | Domain Crossings                                    | 21           |

|              | 2.4      | Area ( | Overhead                                            | 23           |

|              |          | 2.4.1  | Integrated Voltage Regulation                       | 24           |

|              |          | 2.4.2  | Clock Generation                                    | 24           |

|              |          | 2.4.3  | Clock Domain Crossings                              | 24           |

|   | 2.5  | 2.4.5           | Power Grid                             | 24<br>25<br>25 |

|---|------|-----------------|----------------------------------------|----------------|

| 3 | Inte | egrated         | Voltage Regulation 2                   | 27             |

|   | 3.1  |                 |                                        | 27             |

|   |      |                 | 1 0                                    | 27             |

|   |      |                 |                                        | 20             |

|   | 2.0  |                 |                                        | 30             |

|   | 3.2  | _               |                                        | 33             |

|   | 3.3  | -               | 1                                      | 35<br>35       |

|   |      |                 |                                        | 36             |

|   |      |                 | V                                      | 37             |

|   |      |                 | 1 0 0                                  | 36             |

|   |      | 0.0.1           |                                        | ,.             |

| 4 | Inte | $_{ m egrated}$ | Power Management 4                     | 12             |

|   | 4.1  | Estimat         | sing Workload                          | 12             |

|   |      |                 | e e e e e e e e e e e e e e e e e e e  | 43             |

|   |      |                 |                                        | 15             |

|   | 4.2  |                 |                                        | 17             |

|   |      |                 | 0                                      | 17             |

|   |      |                 |                                        | 49             |

|   | 4.3  |                 | 9 9                                    | 49             |

|   |      |                 | · · · · · · · · · · · · · · · · · · ·  | 52             |

|   |      |                 | O .                                    | 54             |

|   |      | 4.3.3           | Activity Predictors                    | 55             |

| 5 | Fast | t Asvnc         | hronous Interfaces 5                   | 66             |

|   | 5.1  | v               |                                        | 56             |

|   | 5.2  | Alterna         | tive Clock Domain Crossing Circuits    | 56             |

|   |      |                 |                                        | 56             |

|   |      | 5.2.2           | The Even-Odd Synchronizer              | 30             |

|   |      | 5.2.3           | Pausible Clocks                        | 31             |

|   | 5.3  | Pausible        | e Bisynchronous FIFO                   | 33             |

|   |      | 5.3.1           | Circuit Design and Operation           | 36             |

|   |      |                 |                                        | 37             |

|   |      | 5.3.3           | Implementation and Measurement Results | 73             |

| 6 | Enc  | rov-Eff         | cient SoC Design 7                     | 76             |

| • | 6.1  |                 | _                                      | 76             |

|   | 0.1  |                 |                                        | 76             |

| $\mathbf{Bib}$ | Bibliography 1 |         |                                    |     |

|----------------|----------------|---------|------------------------------------|-----|

| ,              | 7.2            | Future  | e Work                             | 125 |

| ,              | 7.1            | Summ    | ary of Contributions               | 124 |

| 7              | Con            | clusion | n                                  | 124 |

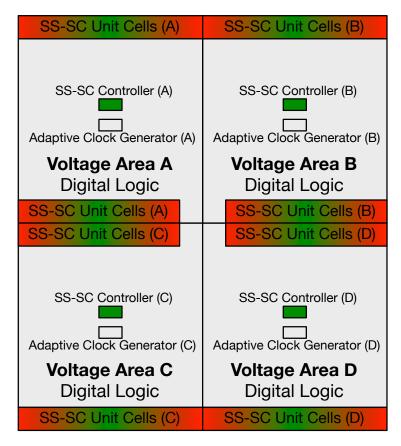

|                |                | 6.4.2   | Simulating Fine-Grained AVS        | 116 |

|                |                | 6.4.1   | System Design and Implementation   |     |

| (              | 6.4            | Hurric  | cane-2: Realizing Fine-Grained AVS |     |

|                |                | 6.3.2   | Measurement Results                | 105 |

|                |                | 6.3.1   | System Design and Implementation   |     |

| (              | 6.3            | Hurric  | cane-1: AVS At Scale               | 101 |

|                |                | 6.2.2   | Measurement Results                | 90  |

|                |                | 6.2.1   | System Design and Implementation   |     |

| (              | 6.2            | Raven-  | -4: Integrated Power Management    | 87  |

|                |                | 6.1.2   | Measurement Results                | 81  |

|                |                |         |                                    |     |

# List of Figures

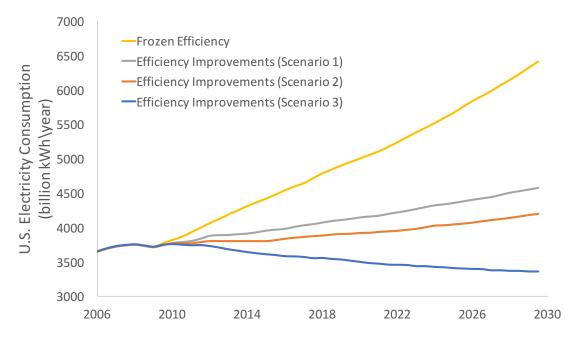

| 1.1 | Results of a model estimating total U.S. electricity consumption by 2030 [1]. The   |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | frozen efficiency curve assumes no efficiency improvements past 2010, causing       |    |

|     | electricity consumption to grow with the economy. Scenario 1 shows the effect       |    |

|     | of implementing existing policies to improve energy efficiency. Scenario 2 shows    |    |

|     | the further reductions possible by the full deployment of existing technological    |    |

|     | efficiency advances. Scenario 3 shows the more aggressive reductions possible       |    |

|     | when all possible semiconductor-enabled efficiency improvements are included        | 2  |

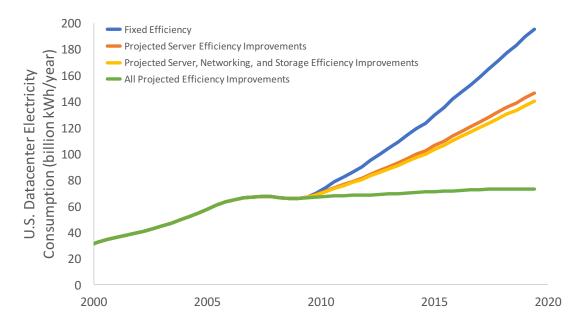

| 1.2 | Estimated energy savings from current trends in US datacenter efficiency im-        |    |

|     | provements [2]. Energy efficiency improvements are predicted to save a total of     |    |

|     | 620 billion kW h over a decade.                                                     | 3  |

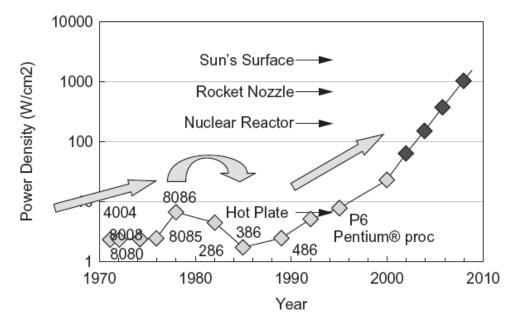

| 1.3 | Predictions of silicon power density in 2001 as first summarized by Shekhar Borkar  |    |

|     | of Intel [3] (© 2001 IEEE). As explained by Pat Gelsinger, then CTO of Intel,       |    |

|     | "If scaling continues at present pace, by 2005, high-speed processors would have    |    |

|     | power density of nuclear reactor, by 2010, a rocket nozzle, and by 2015, the        |    |

|     | surface of the sun."                                                                | 4  |

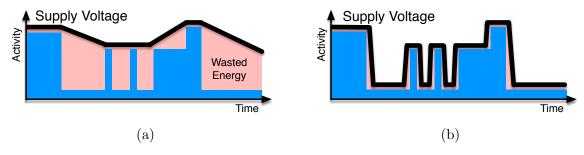

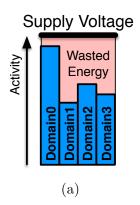

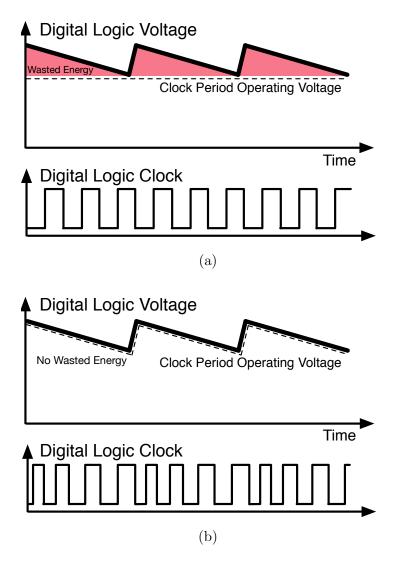

| 1.4 | An example showing the additional energy savings of fine-grained AVS in time        |    |

|     | (b) compared to the coarse-grained AVS baseline (a)                                 | 7  |

| 1.5 | An example showing the additional energy savings of fine-grained AVS in space.      |    |

|     | (a) shows the wasted energy resulting from a coarse-grained AVS implementation,     |    |

|     | while (b) shows how energy can be saved with a fine-grained approach                | 8  |

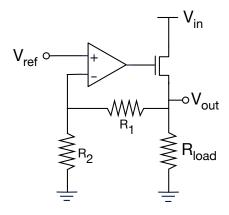

| 2.1 | A simple LDO circuit.                                                               | 14 |

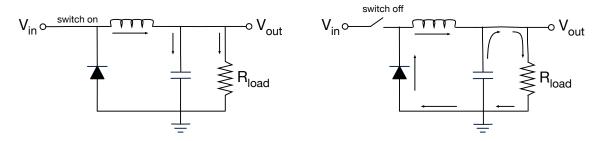

| 2.2 | The two operating phases of a buck converter circuit [31]. The arrows denote the    |    |

|     | direction of current flow                                                           | 15 |

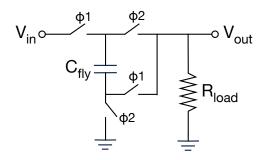

| 2.3 | A switched-capacitor voltage regulator                                              | 16 |

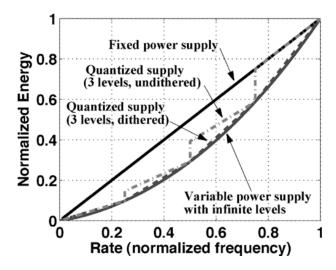

| 2.4 | The energy cost of voltage dithering. Dithering at various duty cycles results in a |    |

|     | linear interpolation between two points on the energy-frequency curve, resulting    |    |

|     | in marginally higher energy consumption than a regulator with arbitrary output      |    |

|     | voltage levels [48] (© 2006 IEEE)                                                   | 18 |

|     |                                                                                     |    |

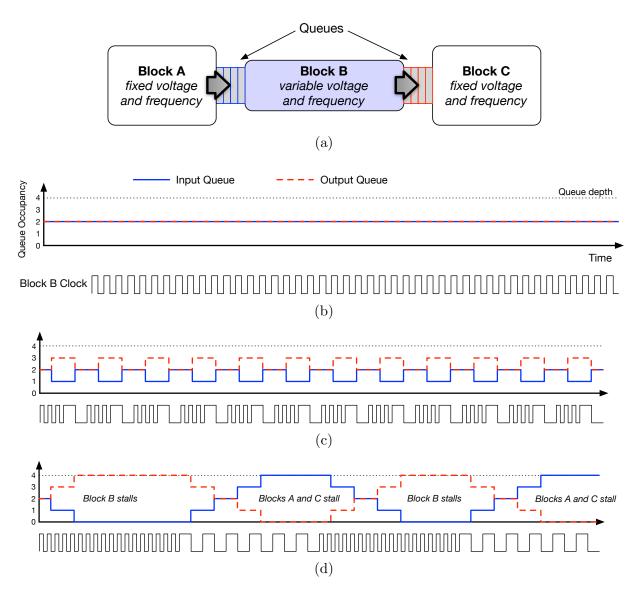

| 2.5 | An example showing a drawback of dithering cause by rate imbalance. Consider<br>the system shown in (a), in which a variable-voltage Block B communicates with                                                                                                                                                                            |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | two fixed-voltage Blocks A and C. If Block B is able to operate at the same                                                                                                                                                                                                                                                               |    |

|     | frequency as its neighbors as shown in (b), then data flows through the system without issue. In some cases, this operating condition may not be available or                                                                                                                                                                             |    |

|     | efficient, requiring dithering between two adjacent voltage/frequency pairs. If                                                                                                                                                                                                                                                           |    |

|     | the dithering takes place rapidly as in (c), then the input and output queues do                                                                                                                                                                                                                                                          |    |

|     | not fill, and Block B correctly simulates a virtual operating mode that matches rates with its source and sink. However, if dithering is slower as in (d), then                                                                                                                                                                           |    |

|     | the pipeline stalls as the queues fill and empty during the rate mismatch. Note<br>that these examples do not account for the latency penalty of the asynchronous                                                                                                                                                                         |    |

|     | crossings between the blocks, which would further exacerbate rate-balancing issues.                                                                                                                                                                                                                                                       | 19 |

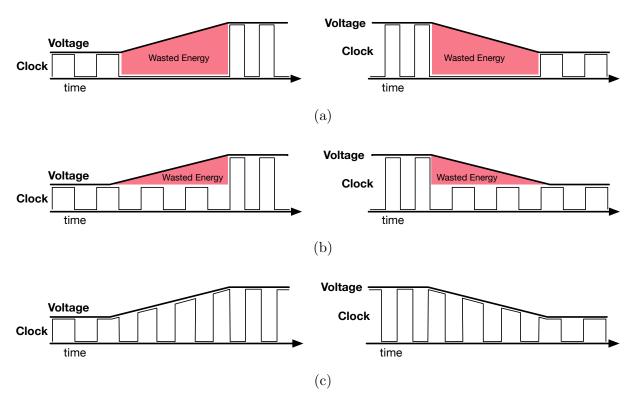

| 2.6 | Waveforms demonstrating the energy cost of different clocking schemes during rising and falling voltage transitions. In (a), the clock is halted during a voltage                                                                                                                                                                         |    |

|     | transition, wasting considerable energy. In (b), the clock operates at the lower frequency during the transition. In (c), an adaptive clocking scheme continuously                                                                                                                                                                        |    |

|     | adjusts the clock period during the voltage transition                                                                                                                                                                                                                                                                                    | 21 |

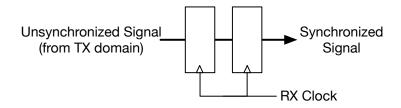

| 2.7 | Synchronization via series flip-flops                                                                                                                                                                                                                                                                                                     | 23 |

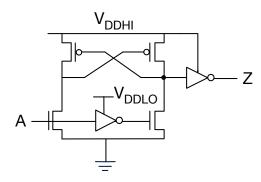

| 2.8 | A level-shifter circuit that converts signal $A$ in voltage domain $V_{DDLO}$ to buffered signal $Z$ in voltage domain $V_{DDHI}$                                                                                                                                                                                                         | 25 |

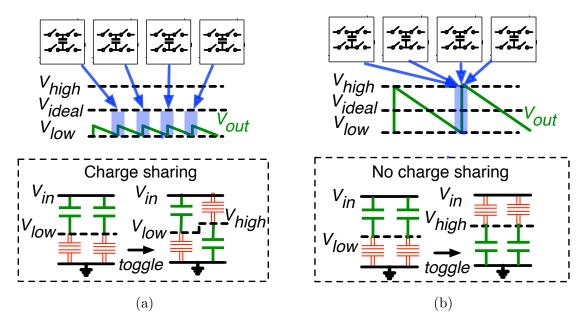

| 3.1 | Interleaved and simultaneous-switching switched-capacitor DC-DC converters [10]. In the four-phase interleaved converter shown in (a), each unit cell switches out of phase with the others, resulting in a relatively flat output voltage but incurring charge-sharing losses. In the simultaneous-switching converter shown in (b), all |    |

|     | unit cells switch at once, eliminating charge-sharing losses but resulting in a large                                                                                                                                                                                                                                                     | 20 |

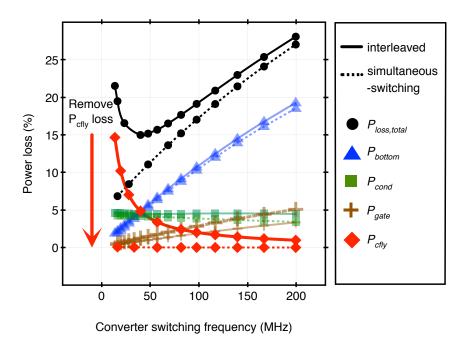

| 3.2 | output voltage ripple                                                                                                                                                                                                                                                                                                                     | 28 |

| 5.2 | switched-capacitor voltage regulator [10] (© 2016 IEEE)                                                                                                                                                                                                                                                                                   | 29 |

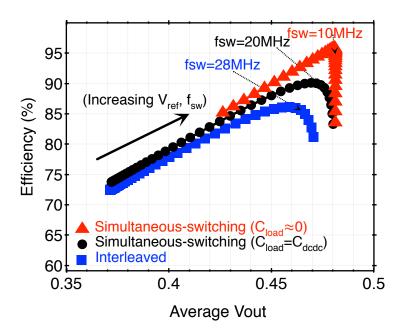

| 3.3 | Simulation results showing the impact of load capacitance on converter efficiency                                                                                                                                                                                                                                                         |    |

| 0.4 | and switching frequency [10] (© 2016 IEEE)                                                                                                                                                                                                                                                                                                | 30 |

| 3.4 | Sample voltage and clock waveforms of SS-SC systems. In (a), the clock does not adapt to the voltage ripple, so it must be margined for the lowest supply voltage,                                                                                                                                                                        |    |

|     | resulting in wasted energy at higher voltages. In (b), the clock adapts to the                                                                                                                                                                                                                                                            |    |

|     | voltage ripple, allowing the circuit to speed up when the voltage is higher than                                                                                                                                                                                                                                                          |    |

|     | the minimum.                                                                                                                                                                                                                                                                                                                              | 31 |

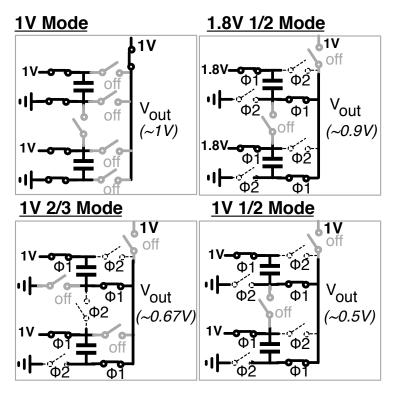

| 3.5 | The four topologies of the reconfigurable SS-SC converter [10] (© 2016 IEEE).                                                                                                                                                                                                                                                             | 32 |

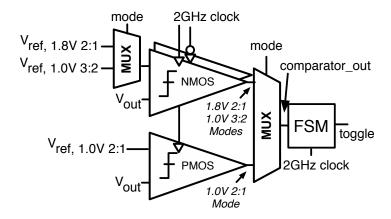

| 3.6 | A diagram of the comparators used in the SS-SC controller [10] (© 2016 IEEE). Different comparators are needed to accommodate the voltage ranges of the ref-                                                                                                                                                                              |    |

|     | erences for the three different switching modes                                                                                                                                                                                                                                                                                           | 33 |

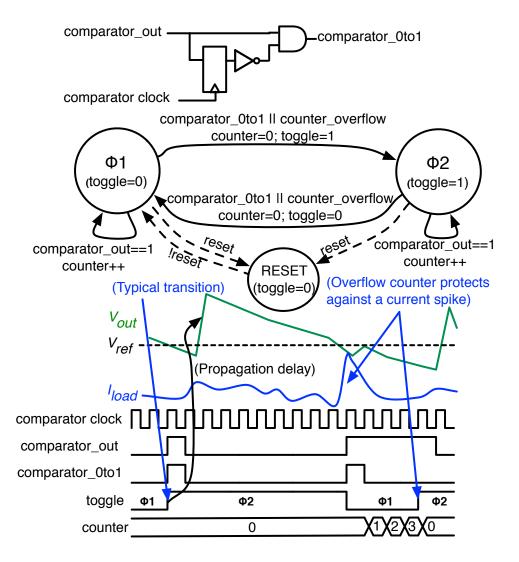

| 3.7  | The state machine used in the SS-SC controller and example waveforms of its operation [10] (© 2016 IEEE). If the current demand increases as the converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | is toggling, the voltage may not rise about $V_{ref}$ , so an additional counter triggers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | further switching until the voltage increases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34 |

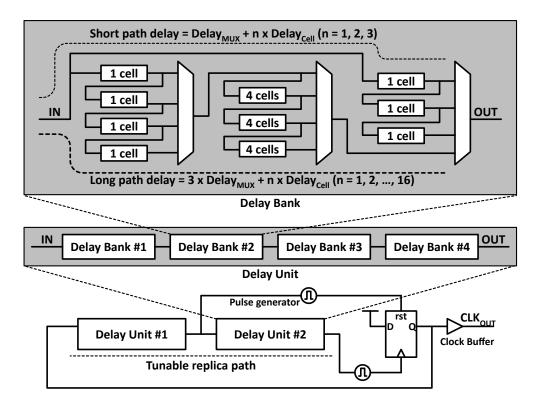

| 3.8  | A block diagram of the adaptive clock generator [68] (© 2017 IEEE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35 |

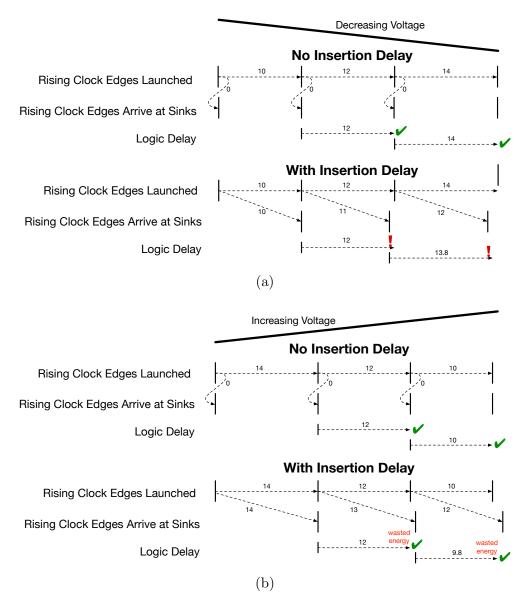

| 3.9  | Timing diagrams demonstrating the effects of clock insertion delay under a changing supply voltage and adaptive clock. In this example, the adaptive clock generator is assumed to perfectly track the voltage-delay characteristics of the digital logic. The numbers are arbitrary, representative delays. In each case, in the absence of insertion delay results in logic arrival times that match the arrival of the next clock edge, while the presence of insertion delay causes a mismatch. In (a), the voltage is decreasing, so insertion delay causes setup time violations because the clock edges propagate through the clock tree more quickly than the slowed logic propagation times. These violations require additional clock margin |    |

|      | to eliminate, increasing energy cost. In (b), the voltage is increasing, so insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | delay causes the logic propagation to complete early, meeting timing but resulting in wasted energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38 |

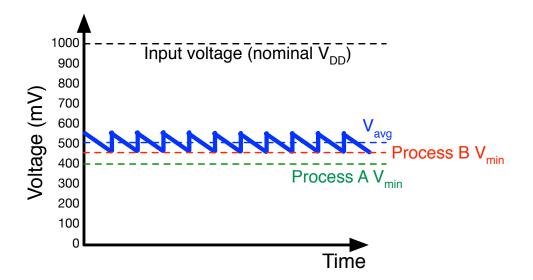

| 3.10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | regulator operates in a 2:1 step-down mode from the fixed 1 V supply; it has a $100 \mathrm{mV}$ ripple around the average voltage $V_{avg}$ of $500 \mathrm{mV}$ . In Process A, $V_{min} = 400 \mathrm{mV}$ , but the SS-SC cannot achieve this output voltage because it is limited to simple ratios of the input for high-efficiency conversion. In Process B, $V_{min} = 450 \mathrm{mV}$ . The SS-SC regulator is operating at the lowest possible voltage without violating $V_{min}$ , but its average voltage remains $50 \mathrm{mV}$ higher than a non-rippling regulating technique                                                                                                                                                        | 39 |

| 3.11 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40 |

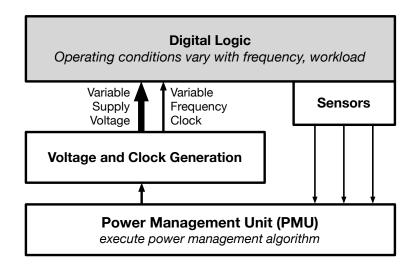

| 4.1  | A typical feedback loop for SoC power management. Only a single varying voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | domain is shown for simplicity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43 |

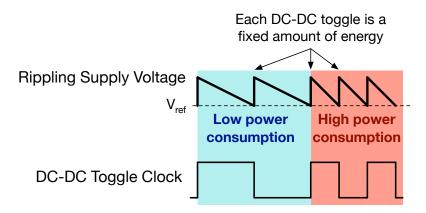

| 4.2  | The basis for measuring power consumption in a system with SS-SC converters and a rippling supply voltage [68] (© 2017 IEEE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44 |

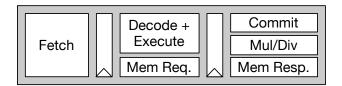

| 4.3  | The Z-scale processor pipeline [68] (© 2017 IEEE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 48 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

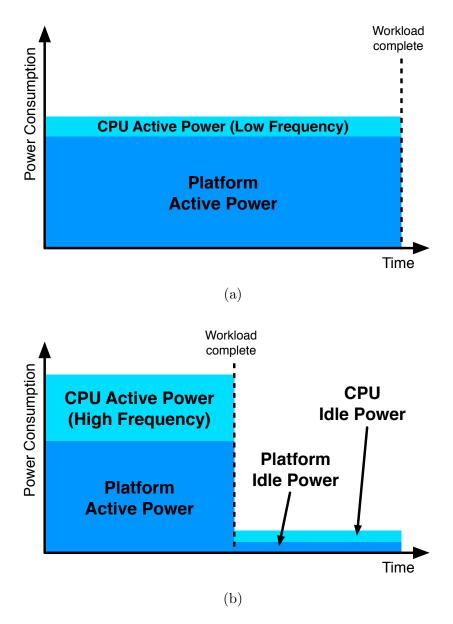

| 4.4  | Sample power consumption plots showing the benefit of race-to-halt power management. In (a), the CPU voltage and frequency is reduced so the computation completes more slowly. This reduces the total energy used by the CPU, but the platform consumes a large amount of energy because it remains active for the duration of the computation. In (b), the CPU operates in a faster, less energy-efficient mode, allowing the platform and CPU to be put in a lower-power idle |      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4 5  | state more quickly and reducing overall energy consumption                                                                                                                                                                                                                                                                                                                                                                                                                       | 51   |

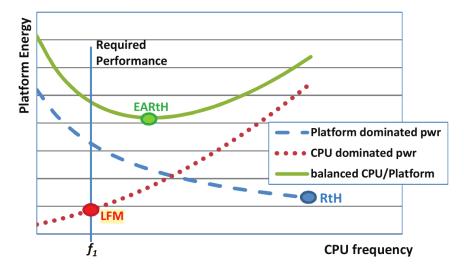

| 4.5  | A plot showing the minimum-energy point achieved when accounting for both platform power and CPU power [98] (© 2014 IEEE)                                                                                                                                                                                                                                                                                                                                                        | 52   |

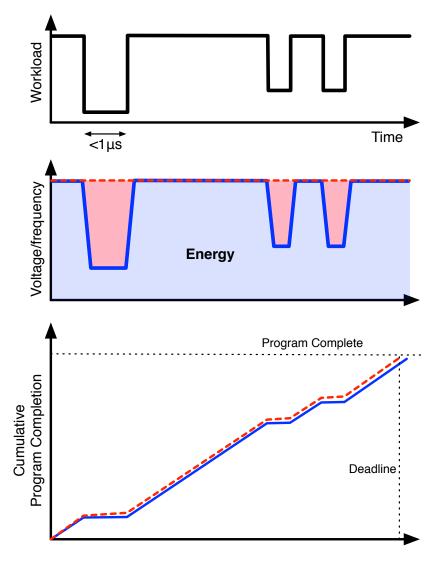

| 4.6  | Applying fine-grained AVS to save energy. The coarse-grained AVS system (in red) has reduced the voltage and frequency as much as possible while still meeting the fixed deadline, but it cannot track rapid changes in workload. The fine-grained AVS system (in blue) can reduce voltage and frequency during periods of low activity, saving significant energy (shaded red) with minimal impact on execution time.                                                           | 53   |

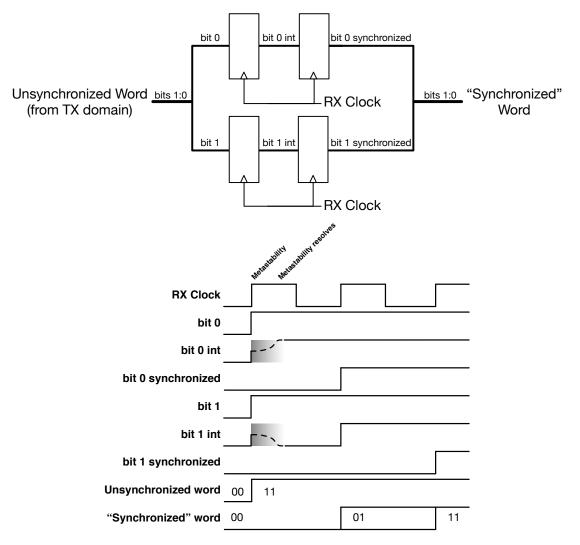

| 5.1  | A waveform illustrating the danger of naive synchronization of data words via                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 0.1  | series flip-flops. In this example, the data word transitions from 00 to 11 near the RX clock edge, resulting in metastability. Each bit of the word resolves in the opposite direction, resulting in a cycle for which the output word is neither                                                                                                                                                                                                                               |      |

|      | 00 nor 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57   |

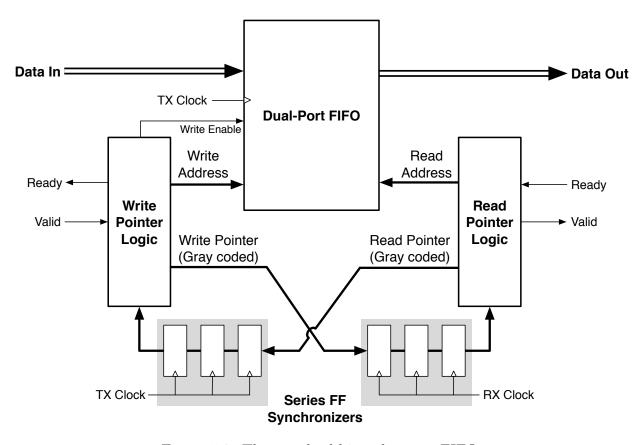

| 5.2  | The standard bisynchronous FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58   |

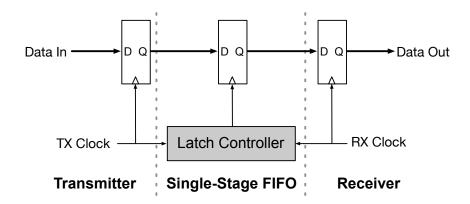

| 5.3  | A single-stage synchronizing FIFO based on a carefully timed flip-flop [116]                                                                                                                                                                                                                                                                                                                                                                                                     | 60   |

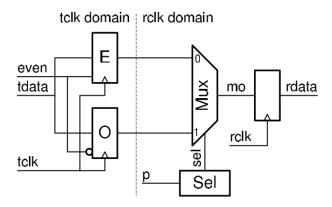

| 5.4  | The even-odd synchronizer [117] (© 2010 IEEE)                                                                                                                                                                                                                                                                                                                                                                                                                                    | 61   |

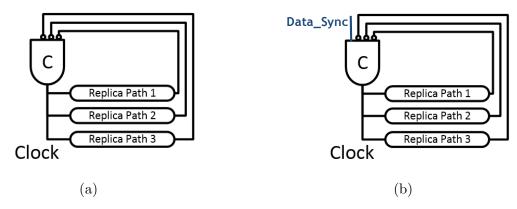

| 5.5  | Local clock generators. The standard circuit (a) can be modified with an addi-                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|      | tional input (b) to enable pausible clocking.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62   |

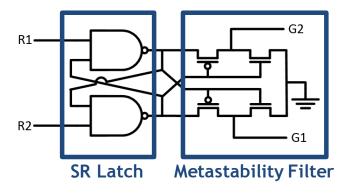

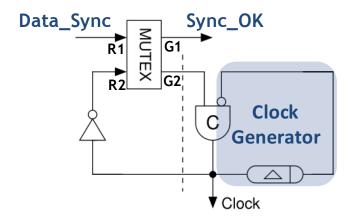

| 5.6  | A mutual exclusion (mutex) circuit. Any metastability in the SR latch is blocked from the output by the metastability filter                                                                                                                                                                                                                                                                                                                                                     | 63   |

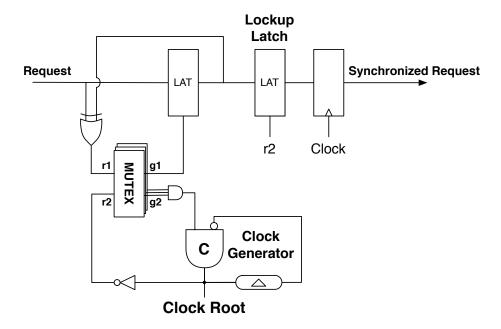

| 5.7  | A mutex used to enable safe asynchronous boundary crossing via pausible clocks [120]                                                                                                                                                                                                                                                                                                                                                                                             |      |

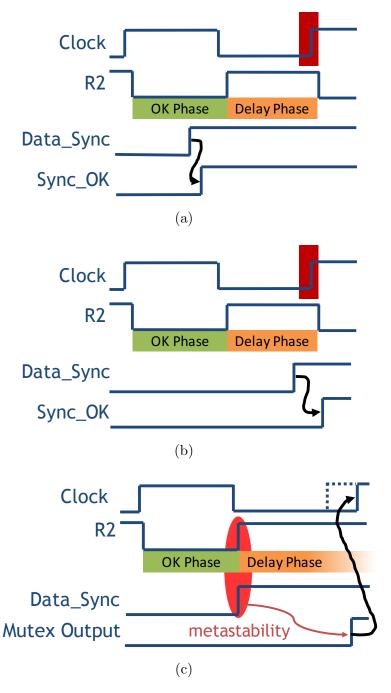

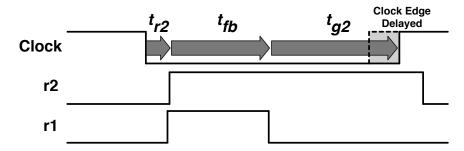

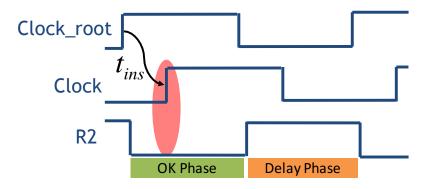

| 5.8  | Waveforms showing the response of the pausible clock circuit to three different                                                                                                                                                                                                                                                                                                                                                                                                  | . 00 |

|      | data arrival times. The red region near the clock edge represents the period                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|      | during which it would be dangerous for the output Sync_OK signal to transition.                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|      | If data arrives during the "OK" phase when r2 is low, then it is passed through                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|      | (a). If data arrives during the "delay" phase, then it is delayed until after the                                                                                                                                                                                                                                                                                                                                                                                                |      |

|      | next clock edge (b). If the data arrives at the boundary between these two phases,                                                                                                                                                                                                                                                                                                                                                                                               |      |

|      | the mutex circuit can go metastable, potentially delaying the next clock edge (c).                                                                                                                                                                                                                                                                                                                                                                                               | 64   |

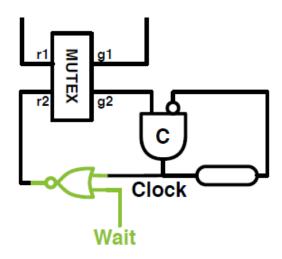

| 5.9  | A pausible clock circuit with an additional gating input                                                                                                                                                                                                                                                                                                                                                                                                                         | 65   |

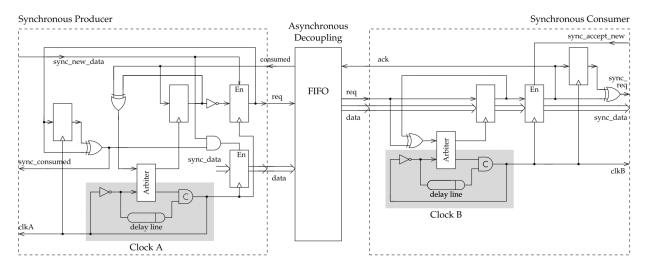

| 5.10 | A pausible asynchronous FIFO [121] (© 2002 IEEE). A fully asynchronous queue                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|      | buffers data in the FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65   |

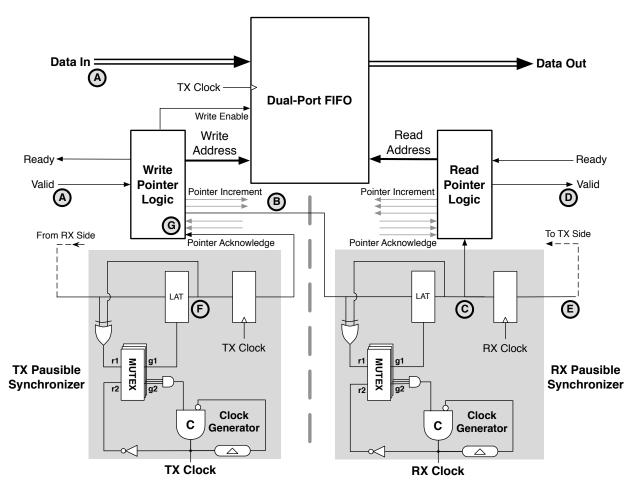

| 5.11 | A pausible bisynchronous FIFO [120] (© 2015 IEEE). The lettered circles show                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|      | the sequence of operations to move data through the FIFO                                                                                                                                                                                                                                                                                                                                                                                                                         | 67   |

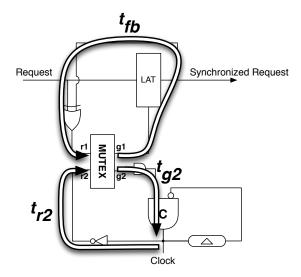

| 5.12 | The key delays in the pausible clock circuit [120] (© 2015 IEEE)                                                                                                                                                                                                                                                                                                                                                                                                                 | 68   |

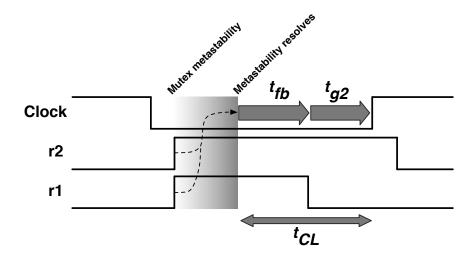

| 5.13                     | Waveforms showing the clock period constraint in the pausible clock circuit [120] (© 2015 IEEE). If this constraint is violated, the next clock edge will be frequently                                                                                                    |                |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                          | · ·                                                                                                                                                                                                                                                                        | 69             |

| 5.14                     | Waveforms illustrating the worst-case setup time for the combinational logic in                                                                                                                                                                                            |                |

|                          |                                                                                                                                                                                                                                                                            | 66             |

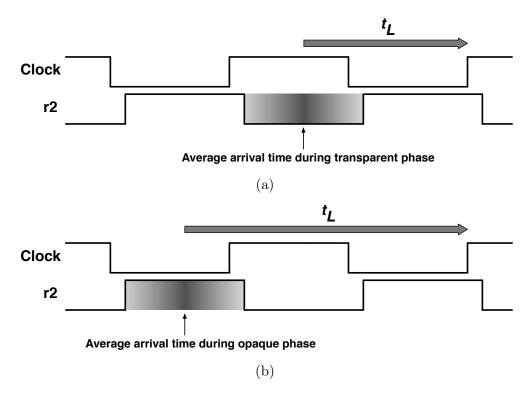

| 5.15                     | Waveforms showing the average latency through the pausible interface, as determined by taking the mean of the average latency during the transparent phase (a) and the average latency during the opaque phase (b) [120] (© 2015 IEEE).                                    | 70             |

| 5.16                     | Waveforms illustrating the effect of insertion delay on the pausible clock circuit [120]. Insertion delay can misalign the phases of the circuit, resulting in unsafe transmission of data                                                                                 | 71             |

| 5.17                     | The pausible synchronizer with an additional latch to guard against the effects of insertion delay [120] (© 2015 IEEE)                                                                                                                                                     | 71             |

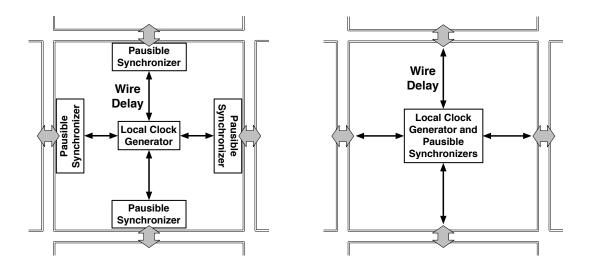

| 5.18                     | Two layout options for the local clock generator and synchronizer logic [120] (© 2015 IEEE)                                                                                                                                                                                | 72             |

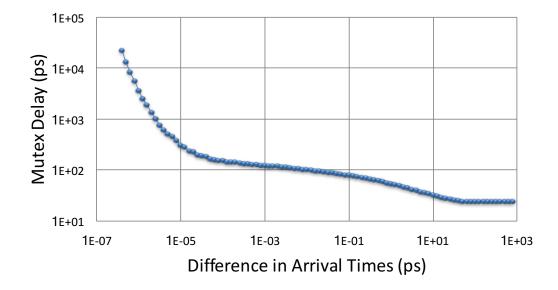

| 5.19                     | Simulated mutex delay for different input arrival times [120]                                                                                                                                                                                                              | 73             |

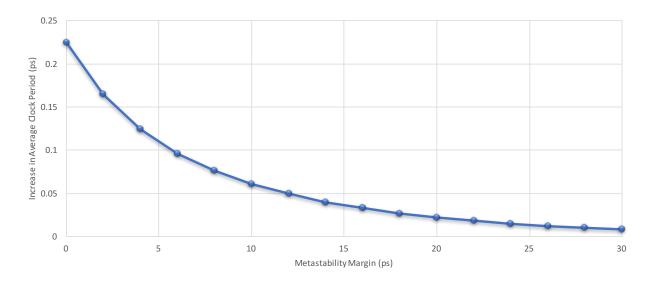

| 5.20                     | The effect of added $t_m$ on average clock period perturbation                                                                                                                                                                                                             | 74             |

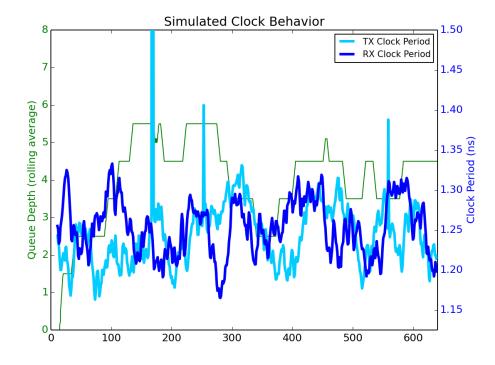

| 5.21                     | Sample simulation result. TX and RX clock period are randomly varied over time. The spikes in TX clock period are clock pauses triggered by simulated metastability                                                                                                        | 74             |

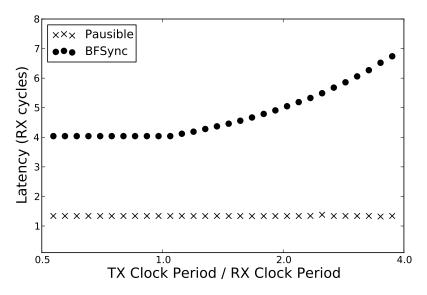

| 5.22                     | Simulated latency through the pausible FIFO with varying TX and RX clock periods [120] (© 2015 IEEE). BFSync is the standard bisynchronous FIFO                                                                                                                            | 75             |

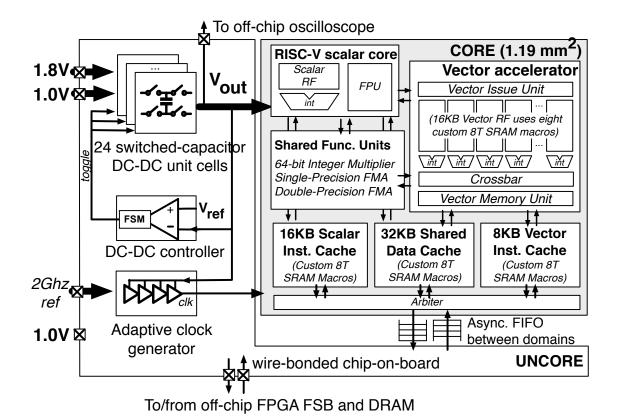

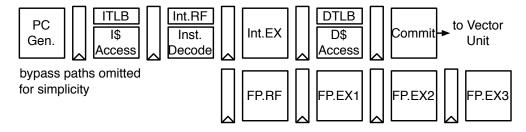

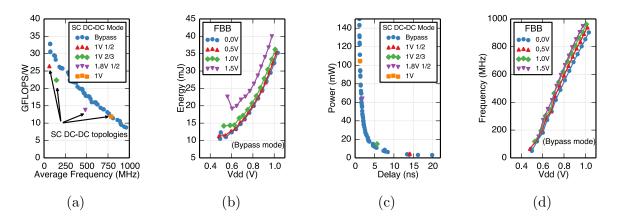

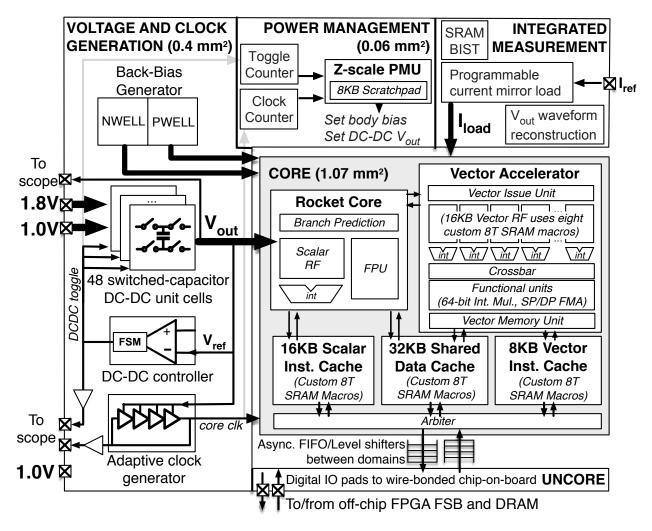

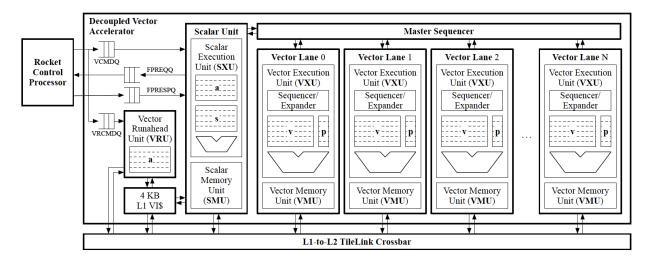

| 6.1<br>6.2<br>6.3<br>6.4 | A block diagram of the Raven-3 testchip [10] (© 2016 IEEE) A simplified pipeline diagram of the Rocket processor [10] (© 2016 IEEE) A block diagram of the Hwacha vector accelerator [10] (© 2016 IEEE)                                                                    | 77<br>77<br>78 |

|                          | main [68] (© 2017 IEEE)                                                                                                                                                                                                                                                    | 79             |

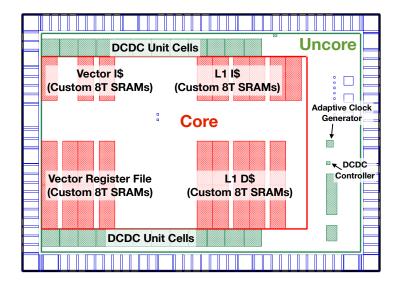

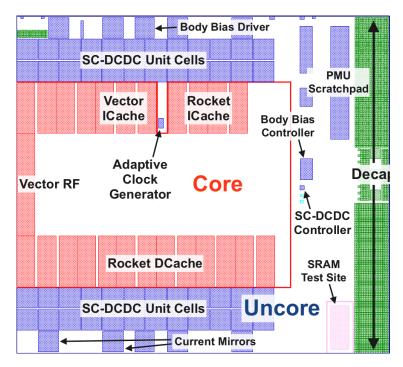

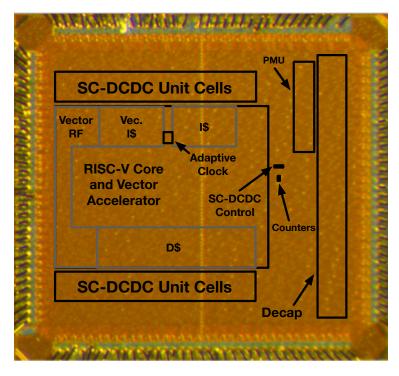

| 6.5                      | Annotated floorplan of the Raven-3 testchip [10] (© 2016 IEEE)                                                                                                                                                                                                             | 80             |

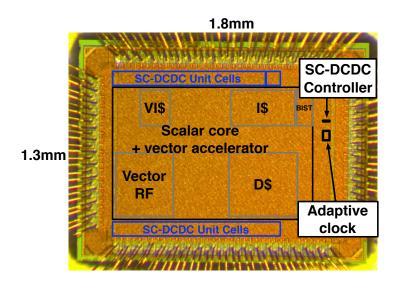

| 6.6                      | Annotated die micrograph of the Raven-3 testchip [10] (© 2016 IEEE)                                                                                                                                                                                                        | 81             |

| 6.7                      | · ·                                                                                                                                                                                                                                                                        | 82             |

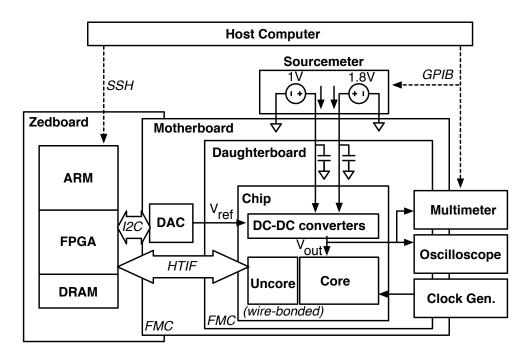

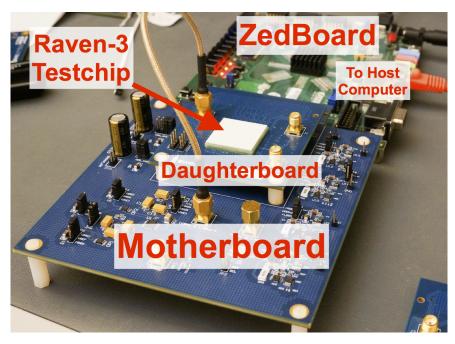

| 6.8                      | The Raven-3 testchip and associated infrastructure. The chip itself is obscured by the white protective covering.                                                                                                                                                          | 82             |

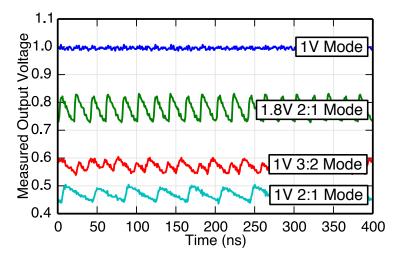

| 6.9                      | Oscilloscope traces of the voltages generated in the four SS-SC operating modes [10] (© 2016 IEEE)                                                                                                                                                                         | 83             |

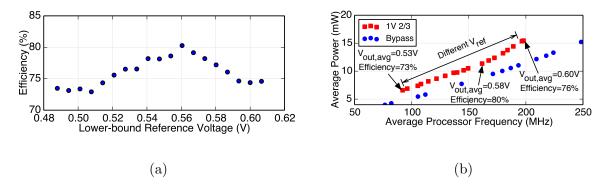

| 6.10                     | Figures showing the effect of different lower-bound reference voltages on system operation [10] (© 2016 IEEE). (a) shows the system conversion efficiency as the voltage is swept, and (b) shows the effect of different $V_{ref}$ on average output voltage and frequency | 83             |

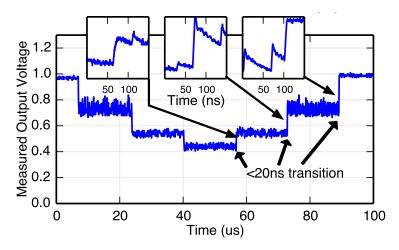

| 6.11                     | An oscilloscope trace showing the generated core voltage as the SS-SC converter rapidly cycles through each of the four operating modes [10] (© 2016 IEEE)                                                                                                                 | 84             |

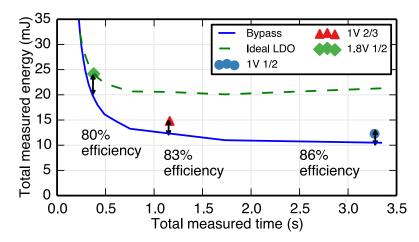

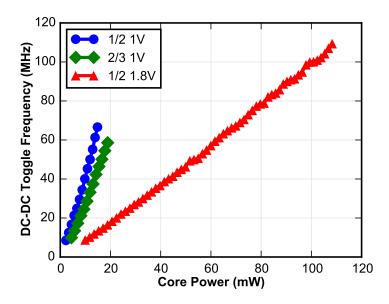

| 6.12 | ing modes [10] (© 2016 IEEE)                                                         | 85 |

|------|--------------------------------------------------------------------------------------|----|

| 6 13 | Measurements of the adaptive clock generator frequency over different voltages       | 00 |

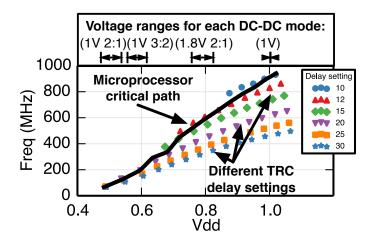

| 0.10 | and replica path delay settings [10] (© 2016 IEEE)                                   | 86 |

| 6.14 | Plots showing the measured energy, power, and frequency of the processor core        |    |

|      | in bypass mode and with the switching regulators enabled [10] (© 2016 IEEE).         | 86 |

| 6.15 | A block diagram of the Raven-4 testchip [68] (© 2017 IEEE)                           | 88 |

|      | Annotated floorplan of the Raven-4 testchip [68] (© 2017 IEEE)                       | 89 |

|      | Annotated die micrograph of the Raven-4 testchip [135] (© 2016 IEEE)                 | 90 |

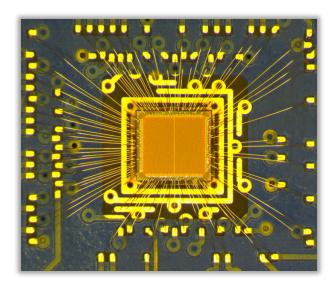

|      | The Raven-4 die wirebonded to the daughterboard                                      | 9  |

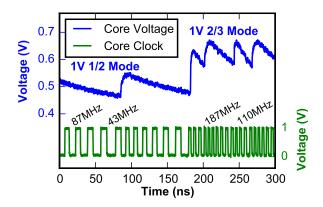

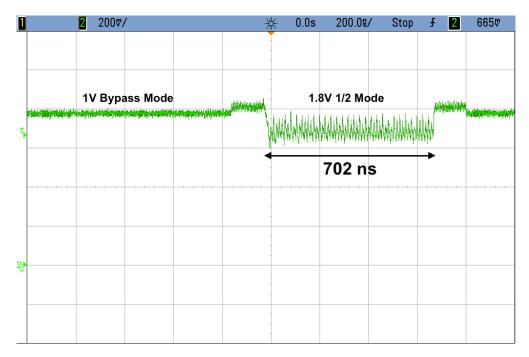

| 6.19 | Oscilloscope traces of the core voltage and clock during an SS-SC mode transi-       |    |

|      | tion [68] (© 2017 IEEE)                                                              | 9  |

| 6.20 | A shmoo chart showing processor performance while executing a matrix-multiply        |    |

|      | benchmark under a wide range of operating modes [68] (© 2017 IEEE). The              |    |

|      | number in each box represents the energy efficiency of the application core as       |    |

|      | measured in double-precision GFLOPS/W                                                | 9  |

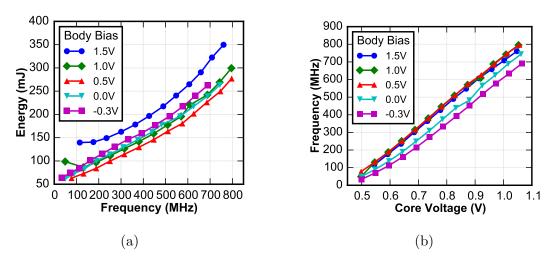

| 6.21 | Plots showing the effects of FBB on core frequency and energy [68] (© 2017 IEEE).    | 9  |

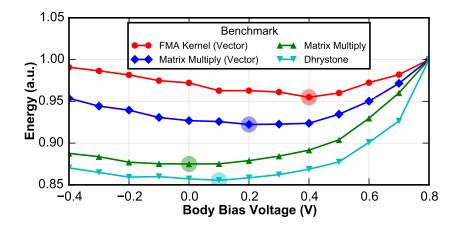

| 6.22 | The effect of FBB on different benchmarks with a supply voltage of 0.6V (bypass      |    |

|      | mode) [135] (© 2016 IEEE). The total energy consumed by each benchmark               |    |

|      | has been normalized so the relative effects of body bias can be compared. The        |    |

|      | minimum-energy point is highlighted for each benchmark                               | 9  |

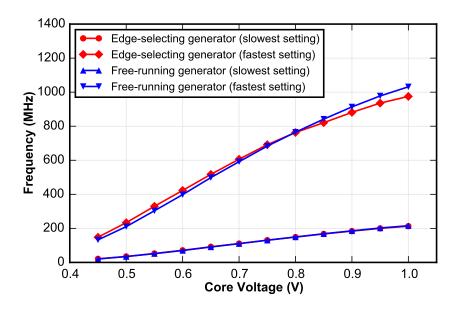

| 6.23 | Measured comparison of the two clock generators implemented in the Raven-4           |    |

|      | testchip [68] (© 2017 IEEE)                                                          | 9  |

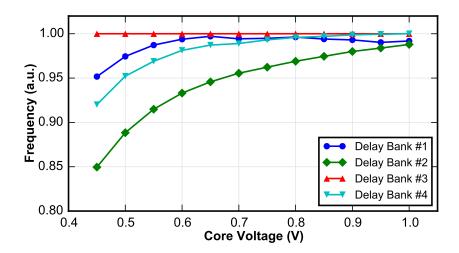

| 6.24 | Measurement results showing the relative difference in voltage-dependent fre-        |    |

|      | quency behavior of the four delay banks in the adaptive clock generator [68] (©      |    |

|      | 2017 IEEE)                                                                           | 9. |

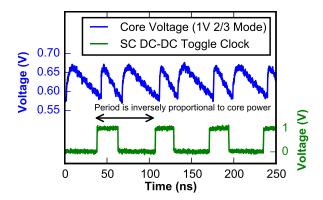

| 6.25 | Oscilloscope traces showing the rippling core supply voltage and the SS-SC toggle    |    |

|      | clock [68] (© 2017 IEEE)                                                             | 9. |

| 6.26 | Measurement results showing the correlation between SS-SC toggle frequency and       |    |

|      | measured core power [68] (© 2017 IEEE)                                               | 9  |

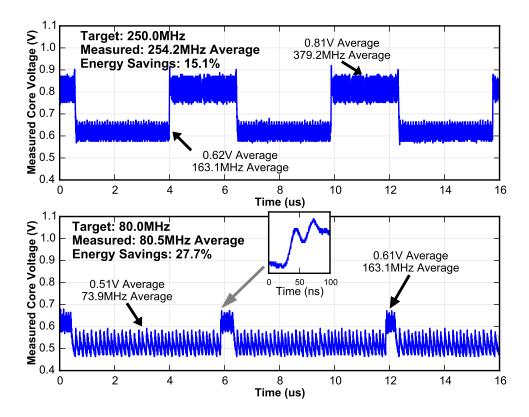

| 6.27 | Oscilloscope traces showing the core voltage as the frequency hopping algorithm      |    |

|      | is applied with two different frequency targets [68] (© 2017 IEEE)                   | 9  |

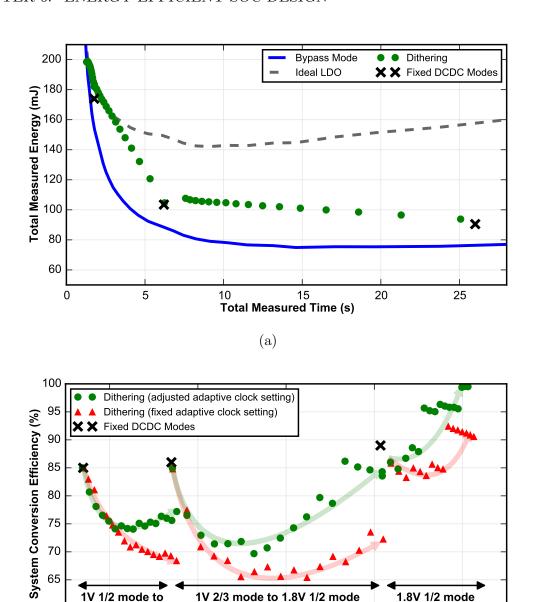

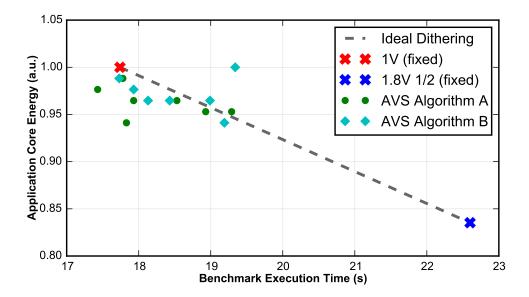

| 6.28 | Plots showing the effect of voltage dithering on system conversion efficiency [68]   |    |

|      | (© 2017 IEEE). (a) compares the energy cost of dithering to the bypass mode          |    |

|      | baseline (in blue), which represents 100% efficient regulation. The dithering op-    |    |

|      | erating points linearly interpolate completion time and energy between the fixed     |    |

|      | SS-SC modes. (b) shows the measured system conversion efficiencies under volt-       |    |

|      | age dithering. The results in green show the benefit of re-tuning the replica timing | _  |

|      | circuit in the adaptive clock generator after each SS-SC mode transition             | 98 |

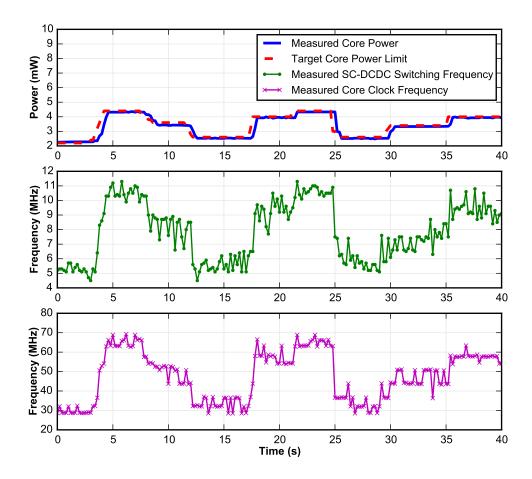

| 6.29 | Measurement results showing a power envelope tracking program executing on                 |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | the PMU [68] (© 2017 IEEE). The frequency of the core is adjusted in response              |     |

|      | to measured changes in core power so that the core operates as quickly as possible         | 100 |

|      |                                                                                            | 100 |

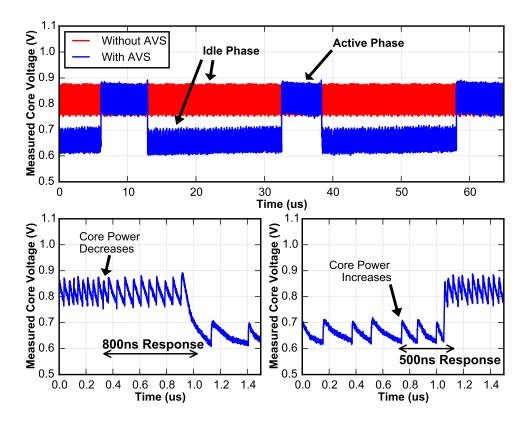

| 6.30 | Oscilloscope traces showing an FG-AVS algorithm running on the PMU [68] (©                 |     |

|      | 2017 IEEE)                                                                                 | 101 |

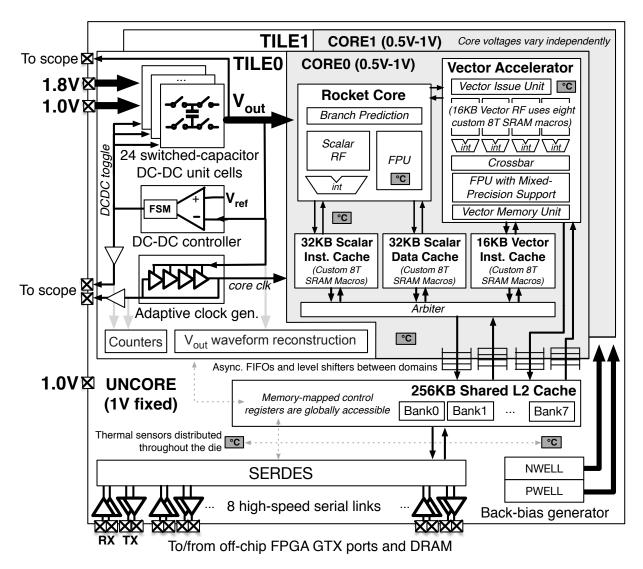

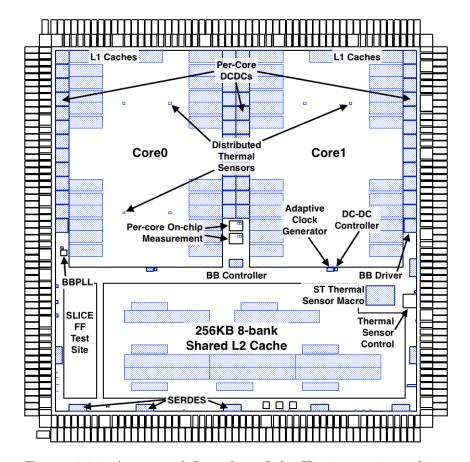

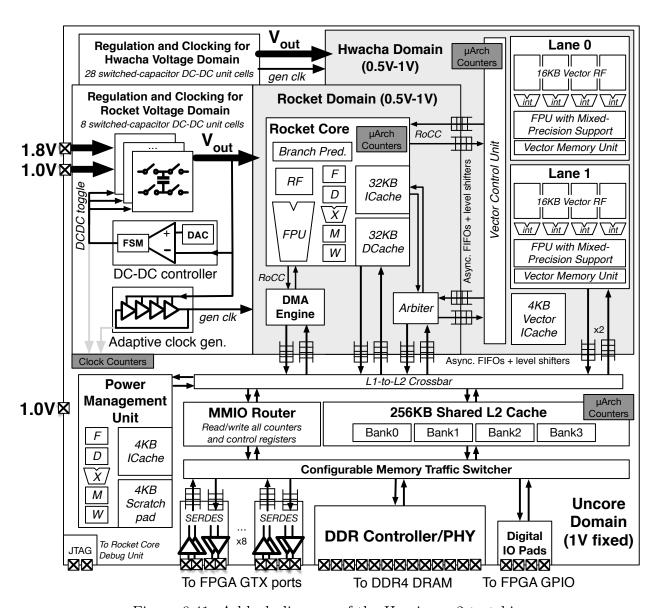

|      | A block diagram of the Hurricane-1 testchip                                                | 102 |

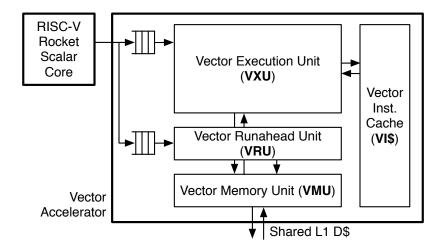

|      | A block diagram of the reimplemented Hwacha microarchitecture [137]                        | 103 |

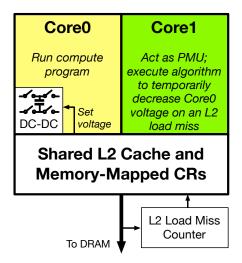

| 6.33 | A feedback diagram showing how FG-AVS algorithms can be implemented on the                 |     |

|      | Hurricane-1 testchip                                                                       | 104 |

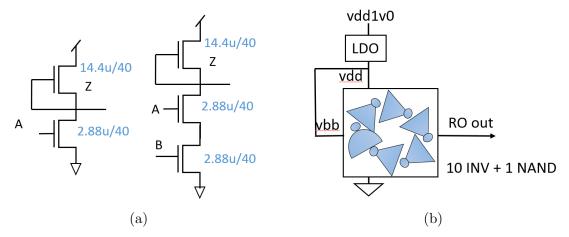

| 6.34 | The distributed thermal sensor circuit. (a) shows the nMOS-only standard cells             |     |

|      | that make up the ring oscillator shown in (b)                                              | 105 |

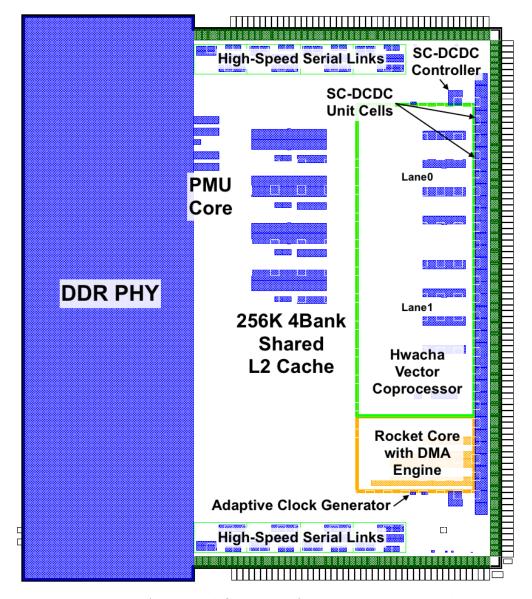

| 6.35 | Annotated floorplan of the Hurricane-1 testchip                                            | 106 |

| 6.36 | Annotated die micrograph of the Hurricane-1 testchip                                       | 107 |

| 6.37 | Pseudocode for two power-management algorithms run on Hurricane-1. The                     |     |

|      | $n_{cycles}$ variable, which specifies different interval durations in each algorithm, was |     |

|      | swept to find the greatest energy savings for each algorithm                               | 108 |

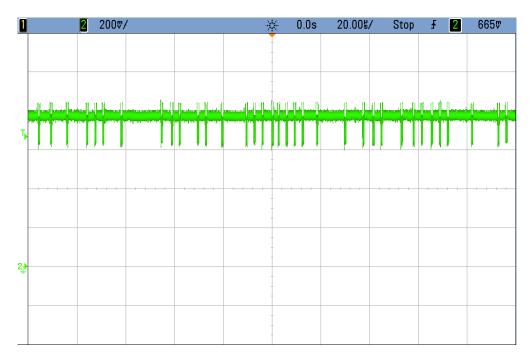

| 6.38 | Measurement of the Core0 voltage during AVS algorithm execution                            | 108 |

| 6.39 | Measurement of the Core0 voltage after an L2 cache miss triggers voltage scaling.          | 109 |

| 6.40 | Measurement of a Core 0 voltage after an L2 cache miss triggers voltage scaling.           |     |

|      | Energy measurements are normalized to the fixed-1V operating mode                          | 110 |

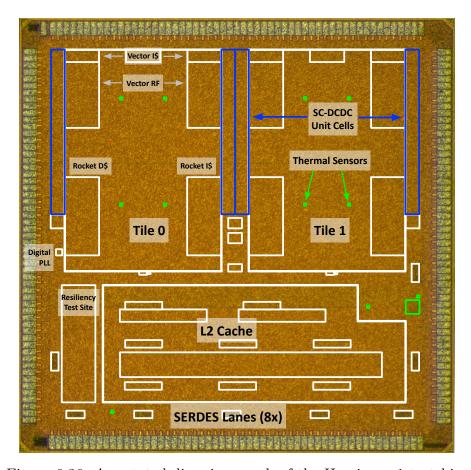

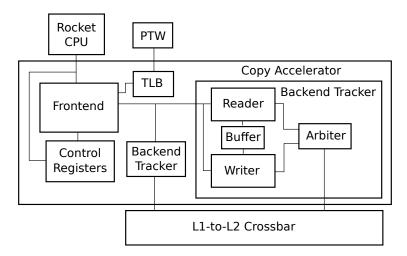

| 6.41 | A block diagram of the Hurricane-2 testchip                                                | 112 |

| 6.42 | A block diagram of the memory copy accelerator in Hurricane-2                              | 113 |

| 6.43 | Annotated floorplan of the Hurricane-2 testchip                                            | 115 |

|      | Pseudocode for a PMU program to demonstrate FG-AVS in time on Hurricane-2.                 | 117 |

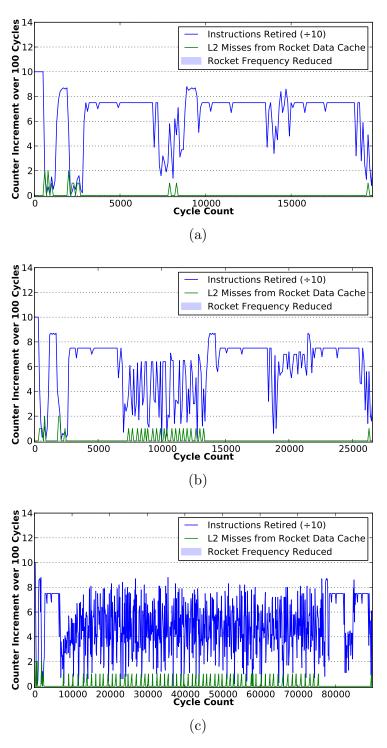

| 6.45 | Execution traces with counter values for median (a), vector-vector add (b), and            |     |

|      | sparse matrix-vector multiplication (c) benchmarks executing on the application            |     |

|      | core while running the AVS algorithm on the PMU core. The cycle count is                   |     |

|      |                                                                                            | 118 |

| 6.46 | Pseudocode for two power-management algorithms that take advantage of mul-                 |     |

|      | tiple AVS levels.                                                                          | 120 |

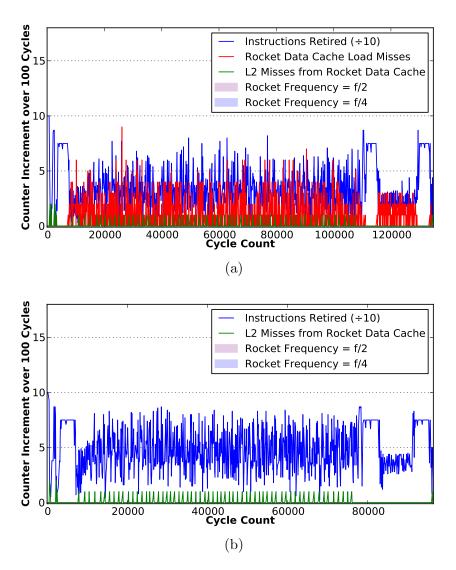

| 6.47 | Execution traces with counter values for the two multi-level PMU algorithms.               |     |

|      | The first algorithm is actuated by L1 data cache load misses (a), and the second           |     |

|      | by counting multiple L2 cache misses (b)                                                   | 121 |

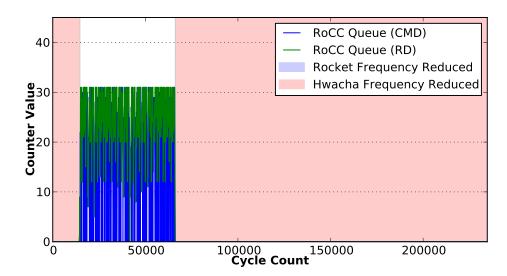

| 6.48 | Pseudocode for a PMU program to demonstrate FG-AVS in space on Hurricane-2.                |     |

|      | An execution trace showing the RoCC queue counters used for feedback in the                |     |

|      | AVS algorithm                                                                              | 123 |

|      | $\smile$                                                                                   |     |

## List of Tables

| 5.1  | Pausible bisynchronous FIFO synthesis results and comparison [120]                                                                                               | 75  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1  | A summary of key results and details from the Raven-3 testchip [10]                                                                                              | 84  |

| 6.2  | Comparison of the two Raven-4 processors [68]                                                                                                                    | 89  |

| 6.3  | A summary of key results and details from the Raven-4 testchip [68]                                                                                              | 91  |

| 6.4  | Measured system conversion efficiencies achieved by the Raven-4 system [68]                                                                                      | 92  |

| 6.5  | The effects of AVS Algorithm A on runtime and energy, as well as the proportion of runtime spent in the lower-voltage $1.8V\ 1/2$ mode. Data from the fixed $1V$ |     |

|      | and 1.8V 1/2 modes are included for comparison                                                                                                                   | 110 |

| 6.6  | The effects of AVS Algorithm B on runtime and energy, as well as the proportion                                                                                  |     |

|      | of runtime spent in the lower-voltage 1.8V 1/2 mode                                                                                                              | 111 |

| 6.7  | Parameters used in the energy model from [141] to calculate simulated energy                                                                                     |     |

|      | savings                                                                                                                                                          | 119 |

| 6.8  | Energy savings for the Rocket voltage domain resulting from the implementation                                                                                   |     |

|      | of FG-AVS                                                                                                                                                        | 119 |

| 6.9  | Energy savings for the Rocket voltage domain resulting from the implementation                                                                                   |     |

|      | of FG-AVS with multiple simulated voltage levels                                                                                                                 | 120 |

| 6.10 | Energy savings for each voltage algorithm resulting from FG-AVS as the appli-                                                                                    |     |

|      | cation core executes a matrix-multiply benchmark                                                                                                                 | 123 |

#### Acknowledgments

I owe a tremendous debt of gratitude to those who made this dissertation possible. While all research stands on prior work, I think it's fair to say that to an extraordinary extent, my research would not have been feasible without all of those who contributed to the big ideas and massive projects that made this work happen.

I would be remiss if I did not begin by thanking my advisors, Bora Nikolić and Krste Asanović. The first aspects of this project began well before I arrived at Berkeley, and it is their research vision and tireless persistence that allowed my research to progress. Bora has never been afraid to think big, in terms of our research goals, our potential achievements, and the extent of our broad project collaborations. Without his leadership, this project would have surely foundered. Krste oversaw the development of an entire new architecture research infrastructure over just a few years, all while taking pains to convince every computer architect in earshot that tapeouts matter. The unique confluence of these two visions was the foundation for my work. Thanks for all of this, and for the million things I haven't space to mention.

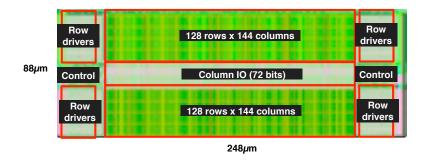

Mixed-signal tapeouts are fantastically challenging; I am extremely fortunate to have worked with such a talented group of colleagues throughout my graduate career. Most importantly for my own work, Alberto Puggelli, Ruzica Jevtic, and Hanh-Phuc Le invented and implemented the voltage regulation that was the lynchpin of our chips and an absolute requirement for my own research. I cannot overstate the extent to which my own experimentation relies on their outstanding work. Jaehwa Kwak designed the clock generators that were critical to the high efficiency of our systems; his layout prowess remains unmatched. Brian Zimmer designed the custom memories that allowed our chips to operate at low voltages. He also served as a tapeout guru, circuit expert, and indefatigable mentor throughout his time at Berkeley. Yunsup Lee was responsible for many of the digital blocks that made up our tapeouts, including the vector processors and the first power management unit, but his most important contribution was his unhesitating commitment to dreaming big and achieving that vision. Martin Cochet designed the power monitoring hardware and temperature sensors, and Milovan Blagojević designed the integrated body bias generator; these two visiting students also provided invaluable tapeout help in understanding the STMicroelectronics process and working with our French collaborators. Pi-Feng Chiu and Stevo Bailey were my partners in crime through every tapeout. System integration is a thankless task, but their tapeout expertise remains invaluable, and I am in their debt for the many, many hours they devoted to this project. John Wright designed the serial links in the Hurricane tapeouts and integrated them into the memory system. Jarno Salonaa made improvements to the integrated voltage regulators in Hurricane-2. To these students, as well as Alon Amid, Keertana Settaluri, Jessica Iwamoto, and everyone else who made it possible to teach sand to think, thank you.

In addition to circuits, our tapeouts relied heavily on RISC-V, Chisel, and the Rocket Chip Generator, all technologies for which I have Krste Asanović's research group to thank. Andrew Waterman and Yunsup Lee, along with Krste and Dave Patterson, invented and

promoted the RISC-V ISA, and contributed a tremendous amount of software infrastructure that has proved invaluable to our efforts. The Chisel hardware description language made it possible to achieve the design productivity that we did, and I'm grateful to Jonathan Bachrach for conceiving and promoting the effort. The Rocket Chip Generator made it possible for us to tape out real processors; thanks to Yunsup, Andrew, and Henry Cook for remaining committed to open-source hardware generators. Palmer Dabbelt is a systems wizard; he made many an impossible problem disappear without breaking a sweat. Colin Schmidt made building and programming vector machines possible. Howie Mao has written countless hardware blocks that just happened to do exactly what we needed. Stephen Twigg spent many hours helping me understand the capabilities of Chisel. And my other architecture groupmates, Eric Love, Martin Maas, David Biancolin, Jack Koenig, Adam Israelevitz, Albert Magyar, Scott Beamer, Donggyu Kim, Albert Ou, Sagar Karandikar, and Rimas Avizienis, have contributed in numerous ways to our research ecosystem, as well as everyone who has contributed to the open-source RISC-V, Rocket, and Chisel ecosystems.

In addition to those with whom I worked directly, many students at the Berkeley Wireless Research Center have made my research possible. My ignorance of analog design runs deep, and so I'm indebted to Sameet Ramakrishnan, Nathan Narevsky, Lucas Calderin, and Greg Lacaille for their patient explanations and for showing me around the lab. Thanks to all of the students in Bora's research group, including Angie Wang, Rachel Hochman, Antonio Puglielli, Paul Rigge, Amy Whitcombe, Nick Sutardja, Mira Videnović-Mišić, Katerina Papadopoulou, Milos Jorgovanovic, Sharon Xiao, Matt Weiner, Amanda Pratt, and Charles Wu, who provided useful research feedback and copious grad school advice while generally keeping things sane. Undergraduate students Gary Choi and Vighnesh Iyer respectively contributed a power virus and FPGA expertise to the project. The BWRC is a great place to work and learn, and it's my colleagues that make it so.

Faculty and staff have greatly contributed to my Berkeley experience. Thanks to Vladimir Stojanovic and Duncan Callaway for serving on my qualifying exam committee and providing crucial feedback on my research. In addition to overseeing the initial work on voltage regulation, Elad Alon has never hesitated to answer questions and provide much-needed guidance and perspective. Brian Richards has the unglamorous role of negotiating myriad CAD tools, foundries, license agreements, and everything in between; his tireless work makes it possible for us to do our research. James Dunn contributed many of the board designs so we could test our chips. Many thanks to Ubirata Coelho and Kostadin Ilov for keeping the servers running, and to Fred Burghardt for maintaining the lab. Thanks also to the front-office staff at BWRC and the ASPIRE Lab. Olivia Nolan, Candy Corpus, Leslie Nishiyama, Erin Hancock, Yessica Bravo, Roxana Infante, and Tami Chouteau kept the lights on and handled so much behind the scenes so that we could do our work.

Many people outside of Berkeley also contributed to this research. I'm particularly indebted to Brucek Khailany and Matt Fojtlik, who served as my mentors at NVIDIA Research. Their support and direction provided the foundation for Chapter 5 of this dissertation. Thanks also to Bill Dally, Yan Zhang, John Poulton, Tezaswi Raja, Stephen Tell,

and John Edmonson for their invaluable discussions and feedback at NVIDIA. I would also like to thank Alon Naveh and Mark Reynolds of Intel, Tom Burd of AMD, Luke Shin and Frankie Liu of Oracle, and Dave Ditzel of Esperanto for taking an early interest in my work and providing valuable feedback as I continued it. My experiences and conversations with industry members yielded valuable guidance and grounding for the project.

My research was funded by the National Science Foundation Graduate Research Fellowship Program, the NVIDIA Graduate Fellowship, Intel Research, and GRC under Grant SRC/TxACE 1836.136. Aspects of the project were also funded by DARPA PERFECT Award Number HR0011-12-2-0016, AMD, and the Marie Curie FP7. Fabrication of all four testchips was donated by STMicroelectronics; I'm particularly grateful to Andreia Cathelin and Phillippe Flatresse at ST, whose tireless advocacy of our projects and our collaboration made our chip development possible. Thanks to all of these organizations, as well as all of the sponsors of BWRC and the ASPIRE Lab.

Finally, I would like to thank my family, without whom I certainly would not be where I am today. My parents, to whom I am eternally grateful, supported my decision to pursue twenty-four straight years of schooling without batting an eye. My brother has stuck with me through it all, a dependable, insightful sounding board for all of my frustrations and triumphs. And my wife Helen, who made it through problem sets, prelims, evening meetings, paper deadlines, tapeouts, qualifying exams, all-nighters, conference travel, and the inevitable existential uncertainty, somehow still wanted to marry me afterwards. Thank you.

### Chapter 1

### Introduction

Fine-grained adaptive voltage scaling (FG-AVS) is a powerful energy-saving technique that can be used to improve the efficiency of a wide range of system-on-chip (SoC) designs. By adjusting the operating voltage and frequency of each part of an SoC to track workload requirements, energy consumption can be greatly reduced during periods of low activity. The implementation of FG-AVS requires extensive changes in design methodology, presenting many challenges to successful adoption. However, key technology trends in deeply scaled process technologies make the use of FG-AVS increasingly important. This dissertation presents innovation in voltage regulation, clock generation, synchronization, power management, and system integration that enable these challenges to be overcome, paving the way for the widespread use of FG-AVS in modern digital design.