# Variability Analysis and Yield Optimization in Deep-Submicron Mixed-Signal Circuits

Katerina Papadopoulou

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2019-10 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2019/EECS-2019-10.html

May 1, 2019

Copyright © 2019, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Variability Analysis and Yield Optimization in Deep-Submicron Mixed-Signal Circuits

by

Aikaterini Papadopoulou

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Electrical Engineering and Computer Sciences

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Tsu-Jae King Liu Professor Jasmina Vujić

Spring 2017

|       | The dissertation of Aikaterini Papadopoulou is approved. |      |

|-------|----------------------------------------------------------|------|

|       |                                                          |      |

|       |                                                          |      |

|       |                                                          |      |

| Chair |                                                          | Date |

|       |                                                          |      |

|       |                                                          |      |

|       |                                                          | Date |

|       |                                                          |      |

|       |                                                          |      |

|       |                                                          | Data |

|       |                                                          | Date |

University of California, Berkeley Spring 2017

#### Abstract

Variability Analysis and Yield Optimization in Deep-Submicron Mixed-Signal Circuits

by

Aikaterini Papadopoulou

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley Professor Borivoje Nikolić, Chair

Scaling of CMOS technology into the deep-submicron regime has made superior device performance and high density possible. However, achieving extreme performance is often limited by an increase in variability due to the aggressive shrinking of dimensions. As variability continues to rise, statistical modeling methods like Monte-Carlo and corner simulation that have been extensively used to predict circuit yield in the past, now become insufficient. It is now evident that models can no longer be developed solely by device variation measurements, but they need to exhibit flexibility and tunability to a specific design.

In this work, we address the problem of rising variability and insufficient variability modeling in two ways. Firstly, by characterizing variability in a deeply-scaled technology node, and secondly by developing a methodology for simple, fast model tuning for design-specific yield optimization.

Technology characterization is achieved by designing a set of dedicated test structures in a 28nm FDSOI technology. Test structures include both device characterization as well as high-speed comparator characterization, and focus on design-dependent, layout-dependent and topology-dependent sources of variation. Worst-case measured within-die device variation goes up to 11 % while a 46% of current variation is measured across different dies. Layout-dependent systematic effects do appear to be significant in this technology. Several comparator topologies are also measured, showing a direct link between comparator sensitivity and measured offset.

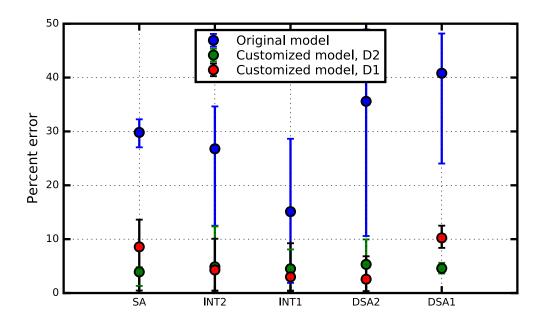

Yield optimization is achieved by model customization to a specific design. A methodology that uses backward propagation of variance and sparse regression techniques is developed in order to achieve this. The methodology is shown to have the ability to tune models to variability structure measurements, decreasing the estimated prediction error from 30% to <4%.

Σαν έξαφνα, ώρα μεσάνυχτ΄, ακουσθεί αόρατος θίασος να περνά με μουσικές εξαίσιες, με φωνές την τύχη σου που ενδίδει πια, τα έργα σου που βγήκαν όλα πλάνες, μη ανωφέλετα θρηνήσεις. Σαν έτοιμος από καιρό, σα θαρραλέος, αποχαιρέτα την, την Αλεξάνδρεια που φεύγει. Προ πάντων να μη γελασθείς, μην πεις πως ήταν ένα όνειρο, πως απατήθηκεν η ακοή σου μάταιες ελπίδες τέτοιες μην καταδεχθείς. Σαν έτοιμος από καιρό, σα θαρραλέος, σαν που ταιριάζει σε που αξιώθηκες μια τέτοια πόλι, πλησίασε σταθερά προς το παράθυρο, κι άχουσε με συγκίνησιν, αλλ΄ όχι με των δειλών τα παρακάλια και παράπονα, ως τελευταία απόλαυσι τους ήχους, τα εξαίσια όργανα του θιάσου, κι αποχαιρέτα την, την Αλεξάνδρεια που χάνεις.

[Κ. Π. Καβάφης]

# Contents

| C  | onter            | nts      |                                                         | ii |

|----|------------------|----------|---------------------------------------------------------|----|

| Li | st of            | Figur    | es                                                      | v  |

| Li | $\mathbf{st}$ of | Table    | ${f s}$                                                 | ix |

| A  | ckno             | wledge   | ements                                                  | Х  |

| 1  | Intr             | oducti   | ion                                                     | 1  |

|    | 1.1              | Motiv    | ation                                                   | 1  |

|    | 1.2              | Resear   | rch goal                                                | 3  |

|    | 1.3              | Thesis   | s organisation                                          | 4  |

| 2  | Var              | iability | y and statistical modeling                              | 5  |

|    | 2.1              | Varial   | pility sources and effects                              | 5  |

|    | 2.2              | Tradit   | cional statistical modeling techniques                  | 7  |

|    | 2.3              | Advar    | nces in statistical modeling                            | 9  |

|    |                  | 2.3.1    | Yield optimization through circuit performance modeling | 10 |

|    |                  | 2.3.2    | Yield optimization through device performance modeling  | 12 |

|    | 2.4              | Summ     | nary                                                    | 13 |

| 3  | Cus              | stomize  | ed model generation                                     | 14 |

|    | 3.1              | Custo    | mized models                                            | 14 |

|    |                  | 3.1.1    | Base models                                             | 14 |

|    |                  | 3.1.2    | Base model tuning                                       | 16 |

|    |                  | 3.1.3    | Parameter screening and system constraints              | 18 |

|   | 3.2 | Applie  | cation examples                                              | 25 |

|---|-----|---------|--------------------------------------------------------------|----|

|   |     | 3.2.1   | Customized models for device characterization                | 23 |

|   |     | 3.2.2   | Customized models for comparator characterization            | 28 |

|   | 3.3 | Summ    | ary                                                          | 34 |

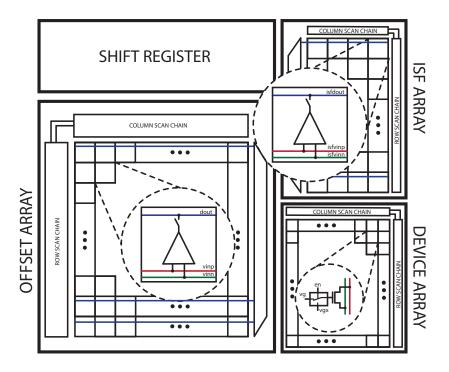

| 4 | Tes | t struc | ture design for data extraction                              | 42 |

|   | 4.1 | Overv   | iew of test structures and goals                             | 42 |

|   | 4.2 | Test s  | tructure design                                              | 43 |

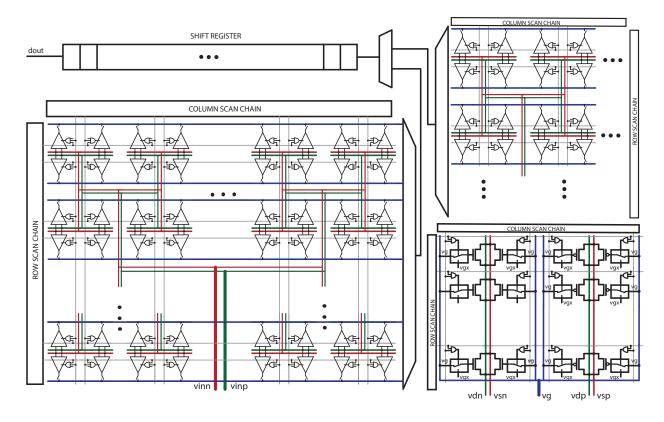

|   |     | 4.2.1   | Offset characterization array                                | 45 |

|   |     | 4.2.2   | Impulse sensitivity function characterization array          | 46 |

|   |     | 4.2.3   | Device characterization structures                           | 48 |

|   | 4.3 | Chara   | cterization and comparison of comparator topologies          | 49 |

|   | 4.4 |         | cterization of random and systematic ility                   | 51 |

|   |     | 4.4.1   | Random variability test structures                           | 52 |

|   |     | 4.4.2   | Systematic variability test structures                       | 54 |

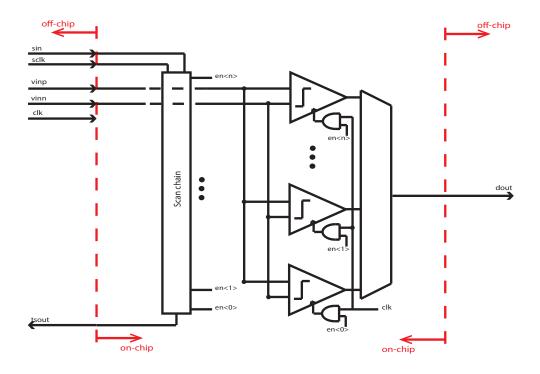

|   | 4.5 | Chip o  | overview and testing                                         | 55 |

|   | 4.6 | Summ    | ary                                                          | 57 |

| 5 | Exp | erime   | ntal evaluation of customized models                         | 58 |

|   | 5.1 | Chara   | cterization of device variability in 28nm FDSOI              | 58 |

|   |     | 5.1.1   | Matching performance                                         | 59 |

|   |     | 5.1.2   | Within-die variability                                       | 60 |

|   |     | 5.1.3   | Die-to-die variability                                       | 62 |

|   | 5.2 | Chara   | cterization of comparator variability in 28nm FDSOI          | 64 |

|   |     | 5.2.1   | Layout-related effects of variability                        | 67 |

|   | 5.3 | Varial  | pility-aware comparator design in deeply-scaled technologies | 69 |

|   |     | 5.3.1   | Variation-driven comparator topology selection               | 69 |

|   |     | 5.3.2   | Variation-driven comparator clocking scheme selection        | 73 |

|   | 5.4 | Design  | n-specific model customization                               | 74 |

|   |     | 5.4.1   | Base model performance                                       | 74 |

|   |     | 5.4.2   | Model customization overview                                 | 75 |

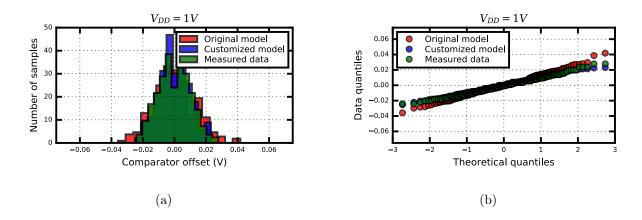

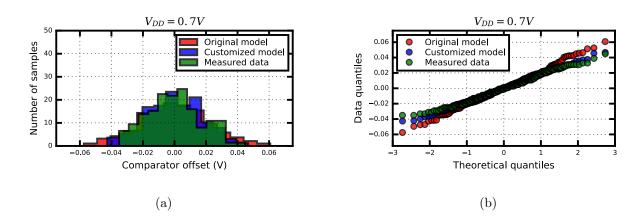

|   |     | 5.4.3   | Customized model performance                                 | 77 |

| 6                         | Con    | aclusions         | 83 |

|---------------------------|--------|-------------------|----|

|                           | 6.1    | Key contributions | 83 |

|                           | 6.2    | Future work       | 84 |

|                           | 6.3    | Conclusions       | 85 |

| $\mathbf{B}_{\mathbf{i}}$ | ibliog | graphy            | 86 |

# List of Figures

| 1.1 | Effects of scaling in digital circuit design                                                                                                                                                                      | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Effects of scaling in mixed-signal circuit design                                                                                                                                                                 | 4  |

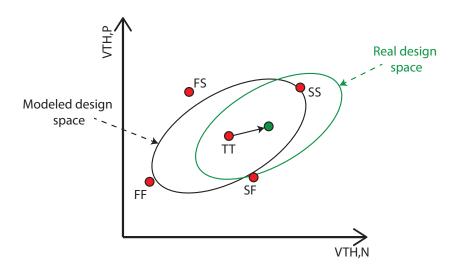

| 2.1 | Corners and Monte-Carlo scatter plot of NMOS and PMOS $V_{TH}$ (normalized).                                                                                                                                      | 8  |

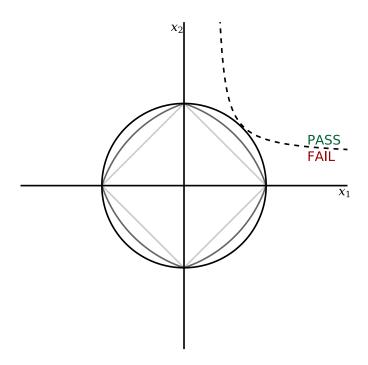

| 2.2 | Illustration of design centering                                                                                                                                                                                  | 9  |

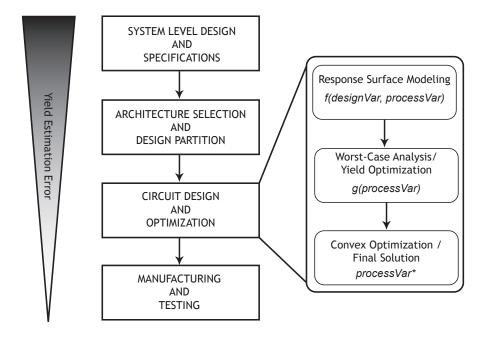

| 2.3 | Block diagram of circuit design process and yield optimization through parameteric performance modeling.                                                                                                          | 11 |

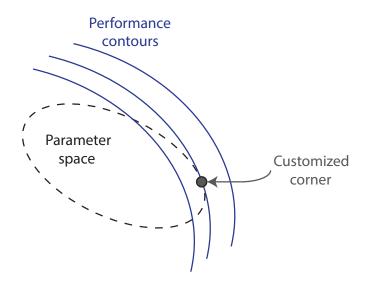

| 2.4 | Simplified illustration of a customized corner                                                                                                                                                                    | 12 |

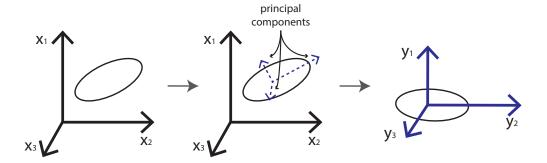

| 3.1 | Illustration of principal component analysis using a 3-dimensional space as an example                                                                                                                            | 15 |

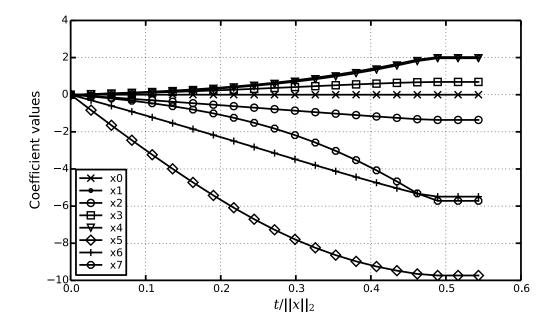

| 3.2 | Ridge regression, produced with artificially generated data. Coefficients are kept small and converge to their final values                                                                                       | 20 |

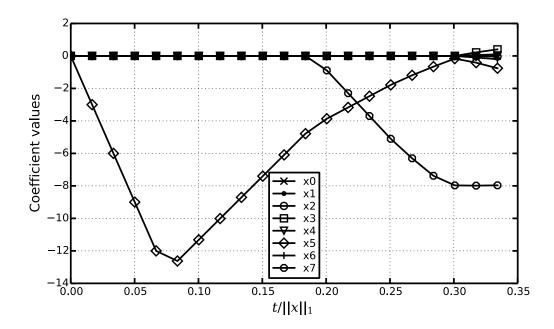

| 3.3 | LASSO solution, produced with artificially generated data. For decreasing $t$ , more and more coefficients are forced to zero                                                                                     | 21 |

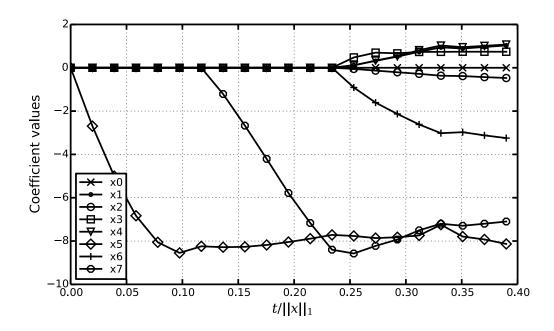

| 3.4 | Elastic net solution with $\rho = 0.5$ , produced with artificially generated data. The solution combines the properties of ridge regression and LASSO, depending upon the value of $\rho$                        | 22 |

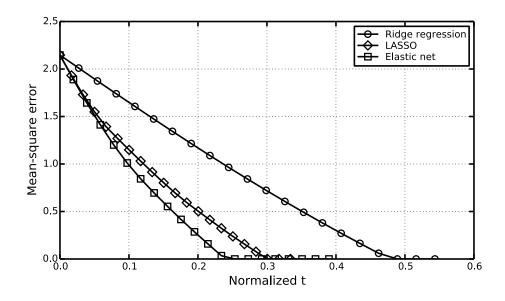

| 3.5 | Root mean square error for ridge, LASSO and elastic net regression                                                                                                                                                | 22 |

| 3.6 | Two-dimensional contour plots of the ridge (black), LASSO(light grey) and elastic net (dark grey) penalty terms for a hypothetical 2-parameter system. The dotted line indicates the valid solution space         | 23 |

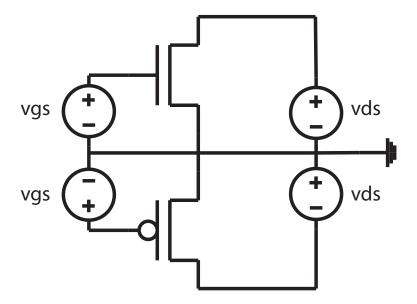

| 3.7 | Simulation circuit for IV curve extraction of NMOS and PMOS                                                                                                                                                       | 24 |

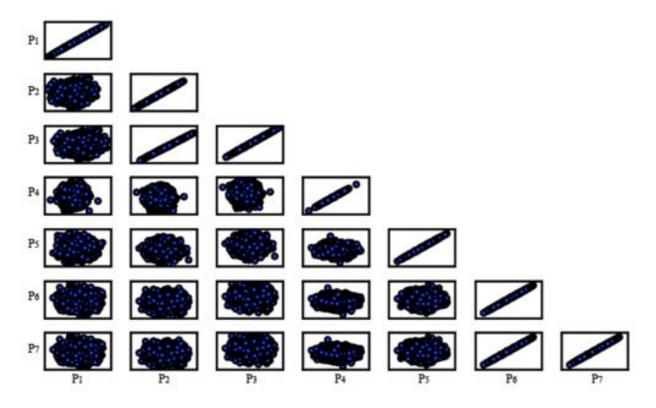

| 3.8 | Scatter plots of a subset of the parameters used                                                                                                                                                                  | 25 |

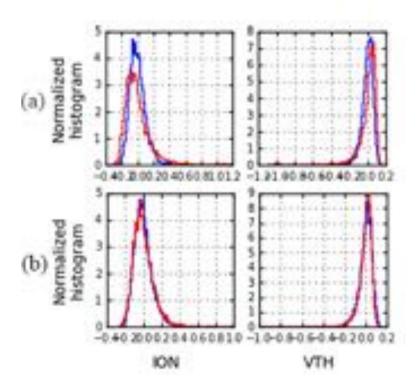

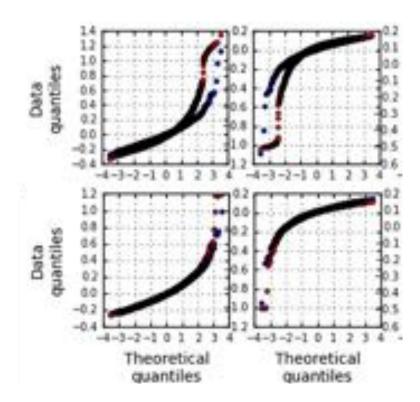

| 3.9 | Comparison of extracted histograms (a) without adding physical constraints and (b) with physical constraints. In both cases blue denotes the original model and red the customized model. All data are normalized | 26 |

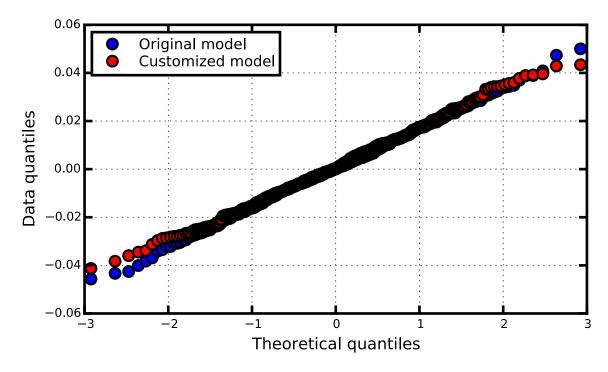

| 3.10 | and (b) with physical constraints. In both cases blue denotes the original model and red the customized model. All data are normalized                                      | 27 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

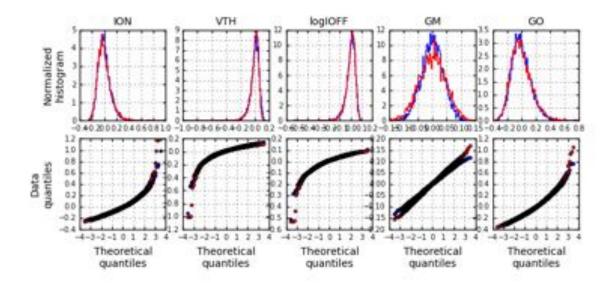

| 3.11 | Output histograms (top) and quantile-quantile plot (bottom) comparison. In both cases blue denotes the original model and red the customized model. All data are normalized | 28 |

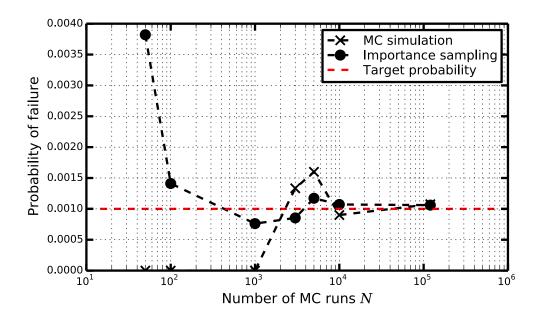

| 3.12 | Simulated probability of failure using Monte-Carlo and importance sampling.                                                                                                 | 29 |

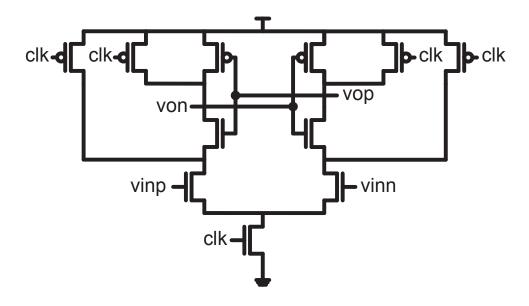

| 3.13 | Circuit of a StrongARM latch including pre-charge devices                                                                                                                   | 29 |

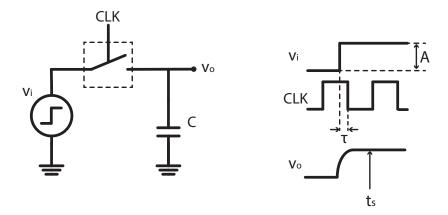

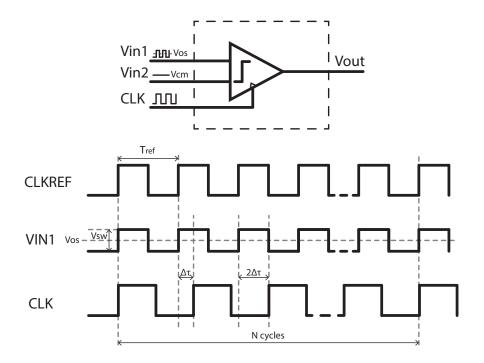

| 3.14 | Simulation setup for ISF extraction of a sampler                                                                                                                            | 31 |

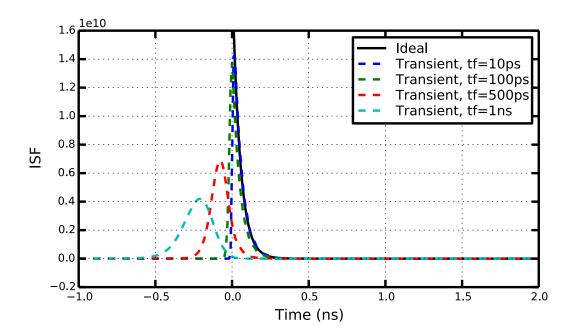

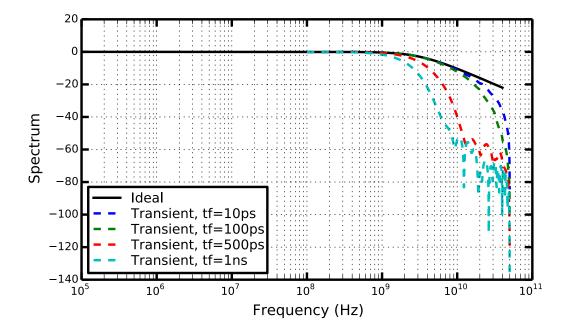

| 3.15 | Impulse response of the sampler for various clock fall times, compared to an ideal response. Larger clock fall times increase the aperture width                            | 37 |

| 3.16 | Extracted spectrum for various clock fall times, compared to an ideal response. Increased aperture width limits the bandwidth of the sampler                                | 37 |

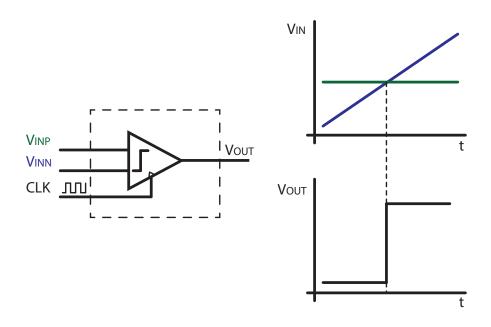

| 3.17 | Simulation setup for offset measurement of a comparator                                                                                                                     | 38 |

| 3.18 | Simulation setup for impulse sensitivity function measurement of a comparator.                                                                                              | 38 |

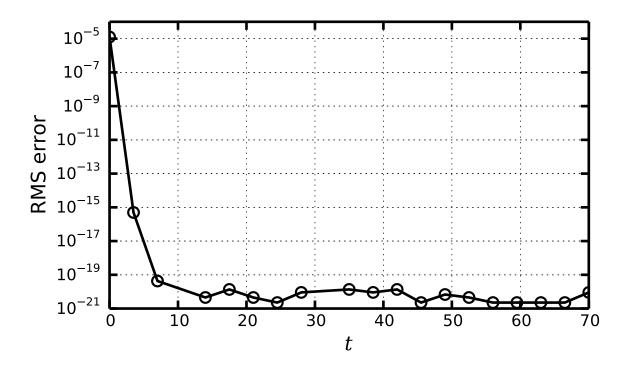

| 3.19 | Root-mean square error of elastic net regression for comparator offset                                                                                                      | 40 |

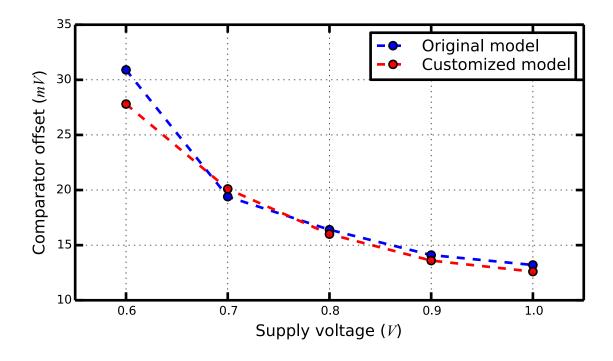

| 3.20 | $\label{thm:comparison} \mbox{Comparison of offset prediction between original model and customized model.}$                                                                | 40 |

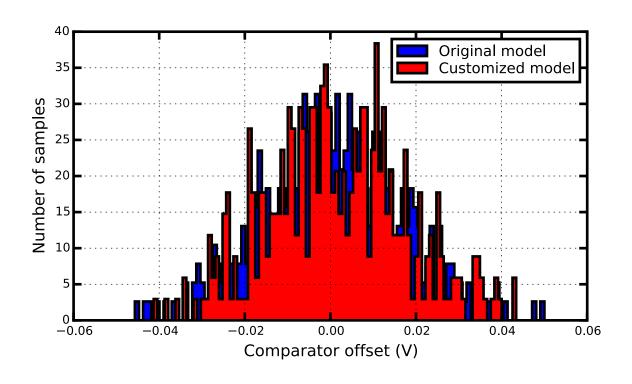

| 3.21 | Comparison of the distributions and QQ plots between original model and customized model                                                                                    | 41 |

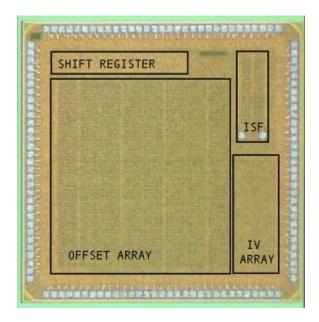

| 4.1  | High-level chip block diagram, featuring the offset, ISF and comparator arrays and the on-chip memory                                                                       | 43 |

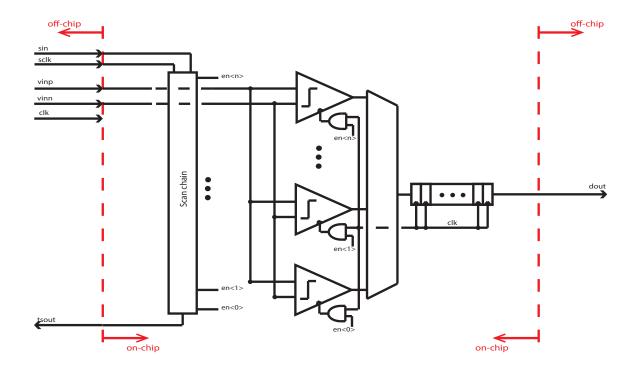

| 4.2  | Simplified schematic of the complete chip                                                                                                                                   | 44 |

| 4.3  | One column of the offset measurement array                                                                                                                                  | 45 |

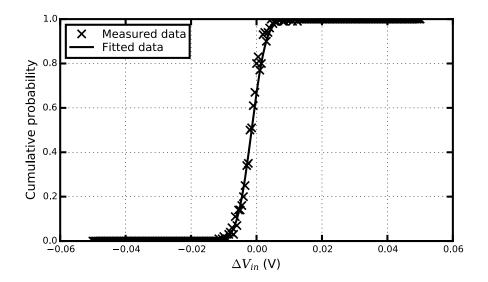

| 4.4  | Example of a cumulative probability function of a single comparator, after noise averaging                                                                                  | 46 |

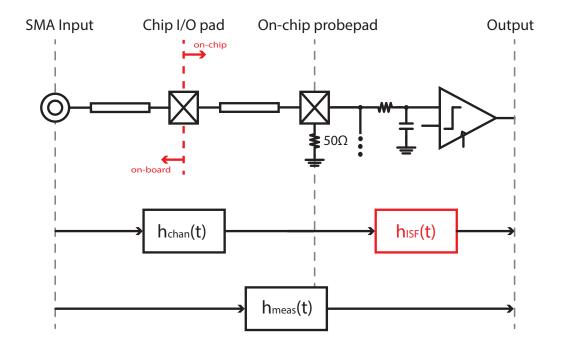

| 4.5  | One column of the ISF measurement array                                                                                                                                     | 48 |

| 4.6  | Input signal path consisting of SMA input, PCB trace, bondwire, chip input pad, probepad, wires and the comparator                                                          | 49 |

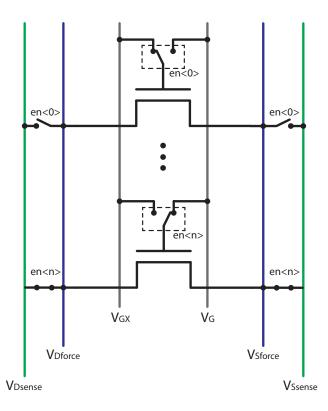

| 4.7  | Schematic design of the transistor array for Kelvin-sensing measurement of a large number of DUTs                                                                           | 50 |

| 4.8  | Monte-Carlo simulation showing the effect of reverse gate bias for leakage reduction                                                                                        | 51 |

| 4.9  | Part of the device characterization array layout                                                                                                                            | 54 |

| 4.10 | Layout picture of the complete chip                                                                                                                                         | 56 |

| 4.11 | Test board setup, including motherboard, daughterboard and Opal Kelly Shuttle LX1 board                                                                                                                                     | 57 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.1  | Die photo of the chip, showing the various blocks described in Section 4.2                                                                                                                                                  | 59 |

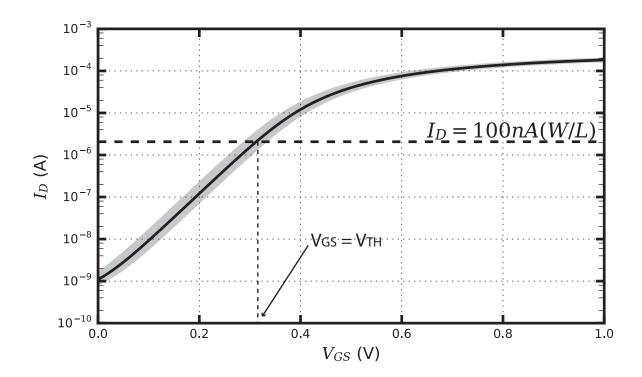

| 5.2  | The constant-current voltage threshold extraction method                                                                                                                                                                    | 60 |

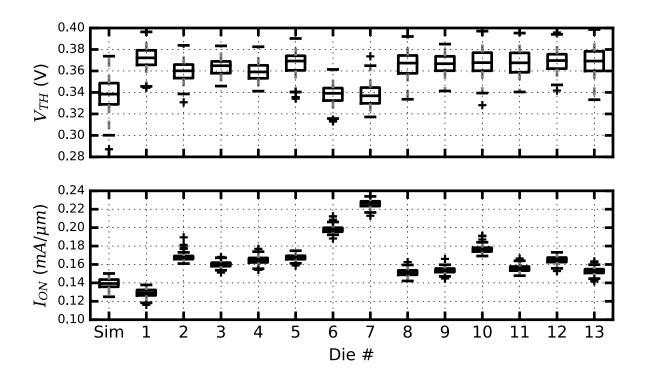

| 5.3  | Distributions of measured $V_{TH}$ and $I_{ON}$ for a 310nm/30nm device across different dies, compared to the simulated distributions                                                                                      | 61 |

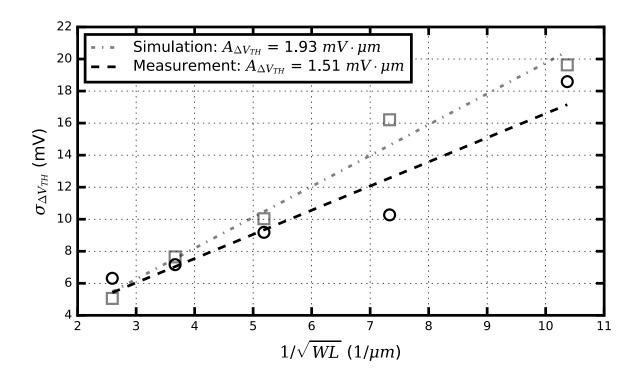

| 5.4  | Pelgrom plot using simulated and measured data                                                                                                                                                                              | 62 |

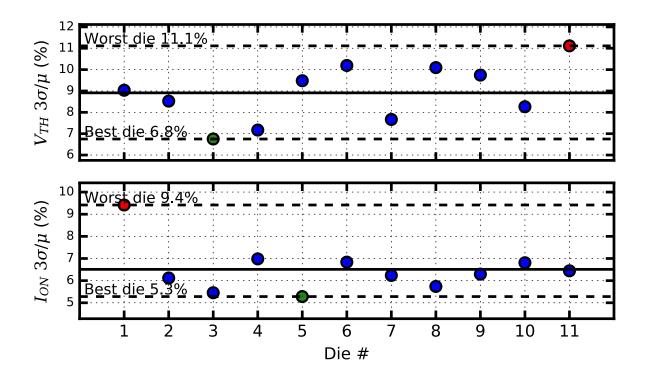

| 5.5  | Measured WID $3\sigma/\mu$ variation for a $310 \text{nm}/30 \text{nm}$ device across different dies. The solid line shows the average WID variation, while the dashed lines mark the best and worst WID variation measured | 63 |

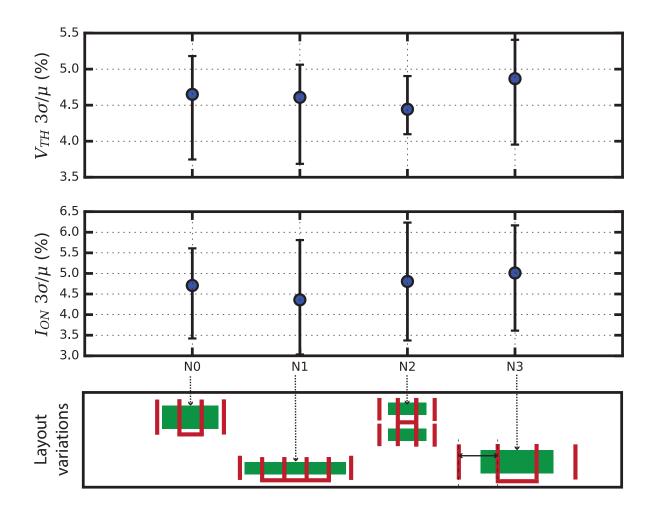

| 5.6  | Measured WID $3\sigma/\mu$ variation from all dies across different layouts. The blue dots correspond to the mean value                                                                                                     | 64 |

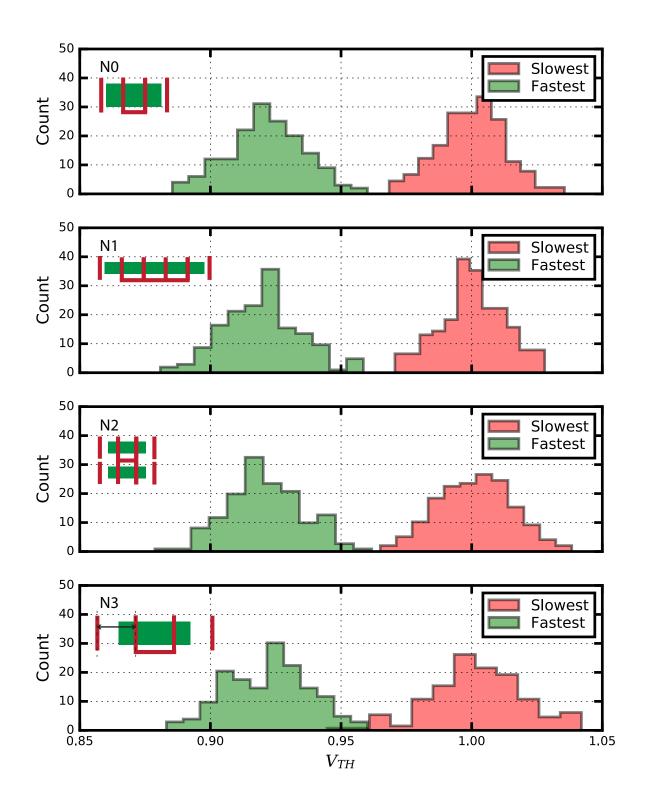

| 5.7  | Comparison of measured $V_{TH}$ distributions of fasted and slowest die for different layouts. Data are normalized to the mean $V_{TH}$ value of the reference device N0 in the slowest die                                 | 65 |

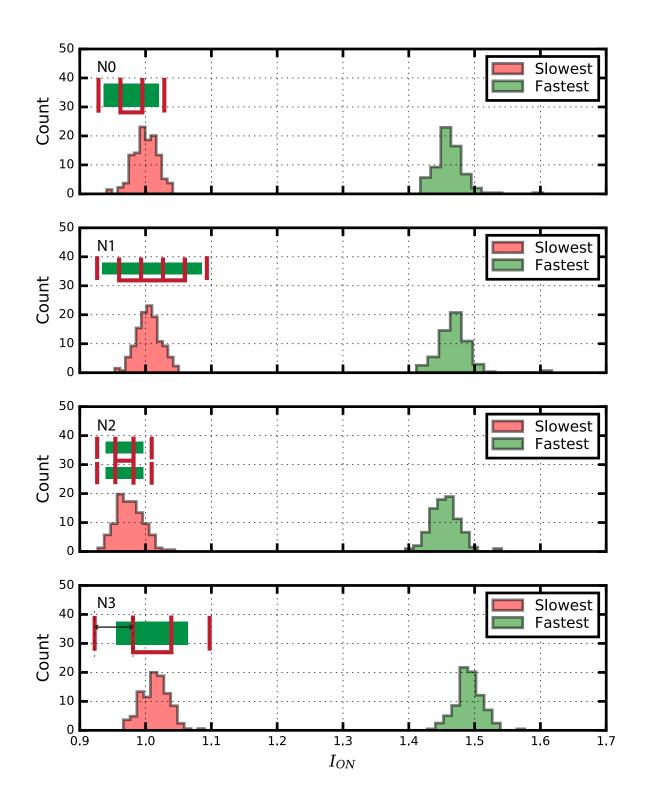

| 5.8  | Comparison of measured $I_{ON}$ distributions of fasted and slowest die for different layouts. Data are normalized to the mean $I_{ON}$ value of the reference device N0 in the slowest die                                 | 66 |

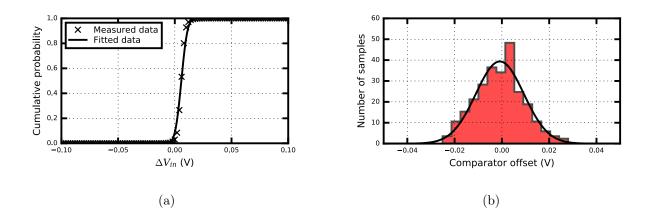

| 5.9  | (a) Noise cumulative distribution function of a single SA comparator instance and (b) offset distribution of SA comparator within a die                                                                                     | 67 |

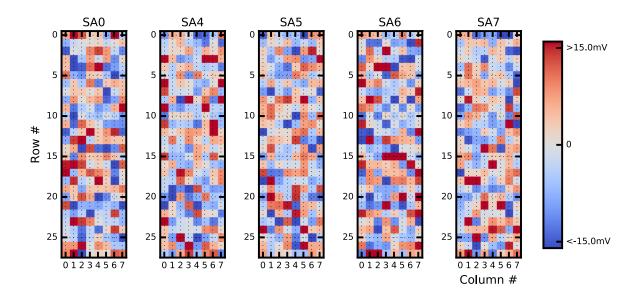

| 5.10 | Colormaps of measured WID comparator offsets for different comparator layouts.                                                                                                                                              | 68 |

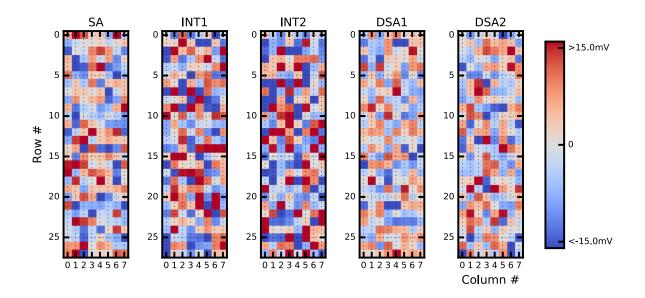

| 5.11 | Colormaps of measured comparator offsets for different comparator topologies within a die.                                                                                                                                  | 70 |

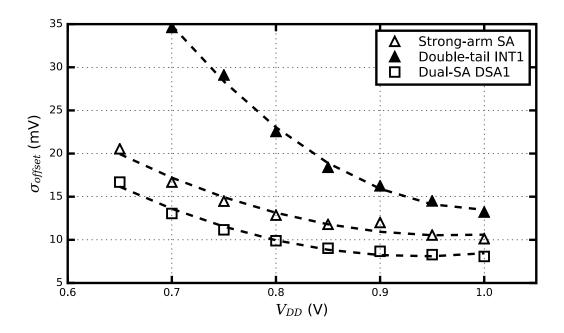

| 5.12 | Comparison of all single clock-phase topologies                                                                                                                                                                             | 70 |

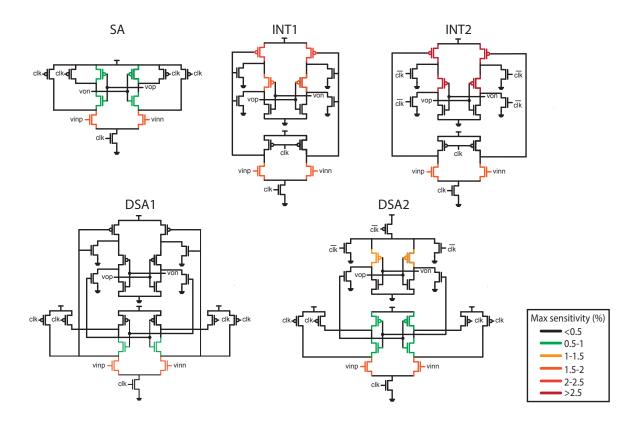

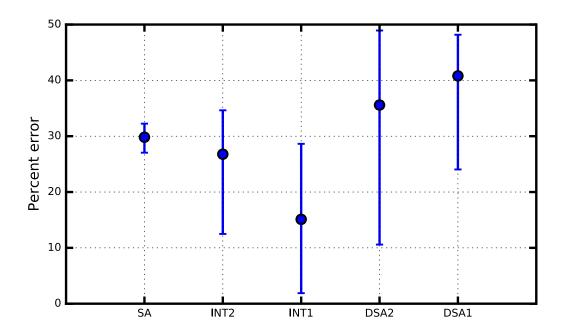

| 5.13 | Illustration of sensitivities for each device of each comparator type. Colors correspond to the maximum sensitivity of the device                                                                                           | 71 |

| 5.14 | Scatter plots of simulated $I_{ON}$ and $V_{TH}$ with respect to model parameters. Data are normalized to zero mean and unit variance. Each plot title shows the corresponding Pearson correlation coefficient              | 72 |

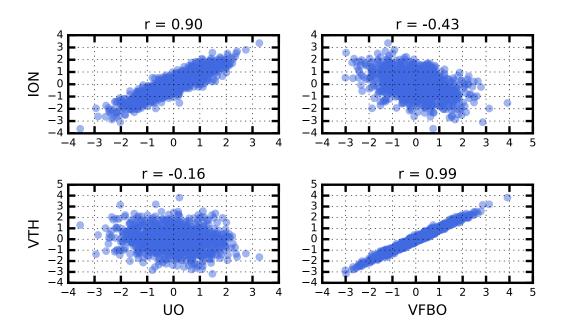

| 5.15 | Comparison of comparator offset in all two-stage topologies                                                                                                                                                                 | 73 |

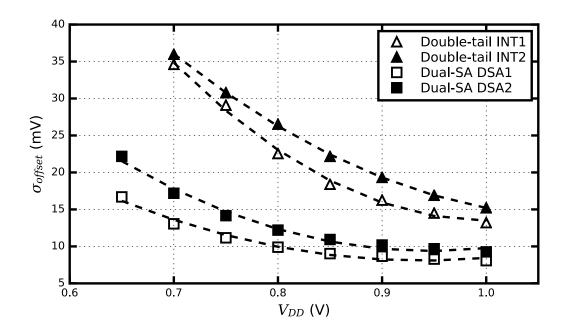

| 5.16 | Mean absolute percent prediction error across different supply voltages for all topologies                                                                                                                                  | 75 |

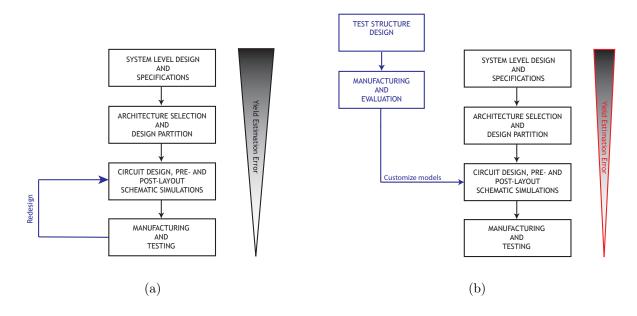

| 5.17 | (a) Conventional design process steps and (b) proposed design process steps.                                                                                                                                                | 76 |

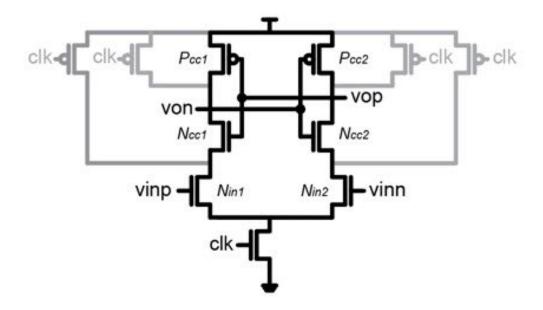

| 5.18 | Strong-arm latch used for design centering. The greyed-out devices were not assigned statistical parameters.                                                                                                                | 77 |

| 5.19 | Comparison of (a) offset distribution and (b) corresponding quantile-quantile plot for the strong-arm comparator at nominal supply voltage                   | 78 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.20 | Comparison of (a) offset distribution and (b) corresponding quantile-quantile plot for the strong-arm comparator at scaled supply voltage.                   | 79 |

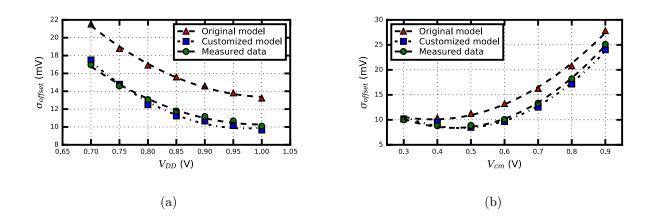

| 5.21 | Comparison of offset standard deviation across (a) supply voltage and (b) input common-mode, when the customized model is calibrated at each voltage step    | 79 |

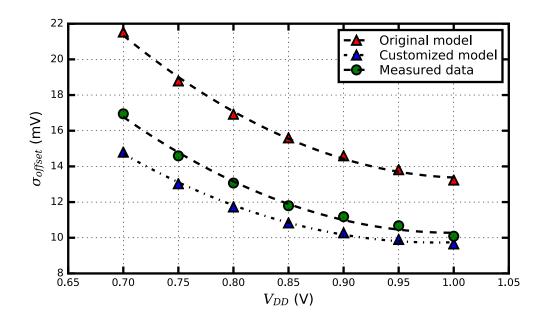

| 5.22 | Comparison of offset standard deviation across supply voltage, when the customized model is calibrated only at nominal supply                                | 80 |

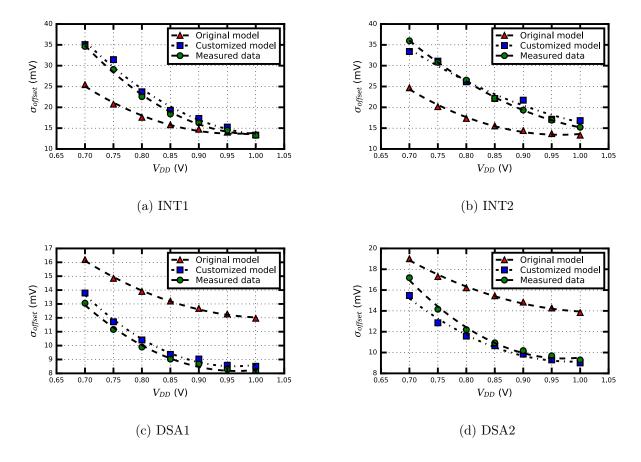

| 5.23 | Comparison of offset standard deviation across supply voltage when the customized model is calibrated at each voltage step for various comparator topologies | 81 |

| 5.24 | Comparison of mean absolute percent prediction error across different supply voltages for all topologies                                                     | 82 |

# List of Tables

| 3.1 | First step of parameter selection                                                                                                  | 19 |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | FDSOI 28nm PSP model statistical parameters for Monte-Carlo (MC) and Fixed-Corner (FC) simulation                                  | 35 |

| 3.3 | Percent sensitivities to parameters                                                                                                | 36 |

| 3.4 | Parameter standard deviations in original model (OM) and customized model (CM)                                                     | 36 |

| 3.5 | Proposed search algorithm                                                                                                          | 36 |

| 3.6 | Comparator offset sensitivity to statistical parameters for input devices and cross-coupled pair devices at nominal supply voltage | 39 |

| 4.1 | Time step $\Delta \tau$ for various combinations of $f_{ref}$ and $N$ for ISF characterization.                                    | 47 |

| 4.2 | Comparator topologies included in the test-chip                                                                                    | 52 |

| 4.3 | Layouts and geometries of devices under test                                                                                       | 53 |

| 5.1 | Comprator layout configurations                                                                                                    | 68 |

| 5.2 | Percent offset shifts of comparators with respect to SA0                                                                           | 69 |

| 5.3 | Comparison of simulated and measured variation for a $310\mathrm{nm}/30\mathrm{nm}$ device .                                       | 74 |

| 5.4 | Comparator percent offset sensitivity to statistical parameters                                                                    | 78 |

| 5.5 | Mean absolute prediction error comparison at nominal supply voltage                                                                | 81 |

#### Acknowledgements

I wish to acknowledge the contributions of the students, faculty and sponsors of the Berkeley Wireless Research Center, wafer fabrication donation of STMicroelectronics, and the support of the Center for Circuit and System Solutions (C2S2) Focus Center, funded under the Focus Center Research Program, a Semiconductor Research Corporation (SRC) program.

More specifically, I would like to acknowledge Brian Zimmer, Amy Whitecombe and Vladimir Milovanović for their contributions to this work through discussions and assistance in circuit and board design. I would like to thank James Dunn for doing the layout of our boards, as wells as Brian Richards and Ubirata Chavez Coelho for all technical support. Last but not least I would like to thank my advisor Borivoje Nikolić for his patience and support throughout my time in grad school.

On a personal level, I would like to thank Evi Kitsou and Dimitra Bavelou, as well as the "good" ones, Ioannis Protonotarios, Iris Safaka, Marina Kordoni and Antonis Moros for their endless love and support. Infinitely many thanks to Mike Lorek because his heart is made of gold, and also to Georgia Gkioxari for being a friend and a sister.

# Chapter 1

## Introduction

Scaling of CMOS technology into the deep-submicron regime has brought on significant changes in all aspects of circuit design, from modeling and simulation to manufacturing. Along with scaling, the introduction of new technologies like ultra-thin body devices and FinFETS has introduced new challenges as well.

Over the past few years research focus has shifted towards optimizing these technologies at deeply-scaled nodes, in order to enable high yield design. This thesis attempts to characterize and quantify device and circuit variability with a focus on ultra-thin body silicon-on-insulator (SOI) technology, as well as present a modeling optimization methodology for mixed-signal circuits. This is achieved through the design, measurement and analysis of a 28nm fully-depleted SOI testchip. In this introductory chapter, the motivation and research goals will be discussed and an overview of the thesis will be given.

### 1.1 Motivation

In the recent years, rapid technology developments in the metal-oxide-semiconductor industry have lead to dimensional and functional scaling of CMOS processes down to the sub-20nm regime. Transistor gates are projected to scale down to less than 12nm by 2020 [1], resulting in significant changes in all stages of circuit design process, from device manufacturing up to product design.

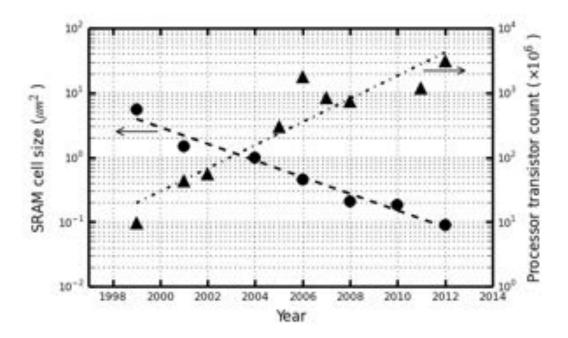

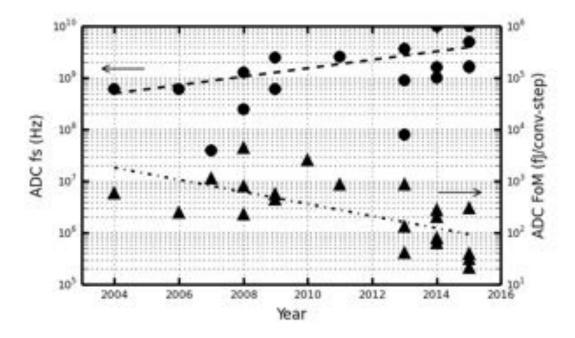

As a result of aggressive technology scaling, the spectrum of applications has now broadened and improved. Superior device performance and high density have given new perspective to circuit design, ranging from digital processors and memory to high-speed analog front-ends. Figure 1.1 shows the effects of scaling for digital processors and memory, based on data published by Intel [2], illustrating how digital circuit design has been smoothly following Moore's Law over the past years. Figure 1.2 shows the effects of scaling in mixed-

signal design, using recently published time-interleaved successive approximation register (TI-SAR) analog-to-digital converters as a representative circuit [3]. Although analog and mixed-signal circuits do not scale as well as digital, the benefits are obvious as the integrated circuit community has been consistently pushing the boundaries of performance, demonstrating multi-GS/s designs over the past few years.

While achieving extreme performance is now possible, it is often limited by an increase in variability due to shrinking of dimensions into the deep submicron regime. Both within-die and die-to-die variations are shown to increase when scaling from 90nm to 45nm [4] and are expected to increase even more as devices scale to sub-10nm. Traditional sources of variation, like random dopant fluctuation (RDF), line-edge roughness (LER) and gate work-function variation (WFV) [5] become more pronounced as variances fail to track scaling of the mean, which makes any slight deviation from the nominal value to have an amplified effect on transistor electrical performance. Additionally, with the introduction of new technologies and materials, new sources of variation arise like silicon thickness  $(T_{si})$  variation, which is present in thin-body devices, or fin width variation which affects FinFET performance. Device variability is increasingly becoming a bottleneck in achieving high-performing and high-yielding circuits, and therefore it is now a necessity to address it in all stages of circuit design, from manufacturing to device modeling to final design.

Traditionally, device models introduced a large set of model parameters, used to predict typical device performance. As variability started to rise, statistical modeling methods were developed to help designers improve yield and, therefore, decrease cost.

Monte-Carlo simulation is one of the most common ways to account for variability in device models, and it involves extracting variation data from devices, and assigning distributions to the model parameters such that the simulated device performance tracks the measured one. Another commonly used method for yield prediction is corner modeling. Similarly, variation data are extracted from a set of devices. Instead of distributions, the model parameters are assigned deterministic shifts to their nominal value, such that the device performance is pushed n standard deviations away from its mean value. Different combinations of those shifts push the device into different points in the design space, known as corners. As variability rises, more corners become available in new models, including corners for analog design, based on device I-V curves, and corners for digital design, typically based on delay-chain measurements.

Although corner modeling and MC simulation have been extensively used to predict circuit yield at the design stage in the past, extreme device scaling makes the nature of variability much more complex now, and renders these two techniques insufficient. As relating device-level variation to the circuit-level variation in an efficient and accurate manner becomes more challenging, research increasingly focuses on improving statistical modeling techniques [6, 7]. It is now evident that a vertical approach must be taken in dealing with variability; models can no longer be developed solely by device variation measurements, but they need to exhibit flexibility and tunability to a specific design. Accurate, design-specific, high-yielding statistical modeling is still an open problem.

Overall, device scaling delivers both the promise for exceptional circuit performance and

Figure 1.1: Effects of scaling in digital circuit design.

the threat of lower yield and increased cost. As the device manufacturing technology is facing new challenges, research in CMOS device variability as well as in modeling of its effects has the potential to determine the future steps of circuit design.

#### 1.2 Research goal

As devices are scaling in the deep-submicron regime variability rises and becomes more complex, making traditional statistical modeling insufficient. Circuit designers need to account for design-specific effects of variability in order to accurately optimize for yield, which normally requires some statistical modeling expertise. The goal of this work is twofold:

- 1. To investigate variability in mixed-signal circuit design by characterizing designdependent, layout-dependent and topology-dependent sources of variation.

- 2. To present a methodology for simple, fast model tuning for design-specific yield optimization, that is accessible to the circuit designer. The methodology utilizes backpropagation of variance and convex optimization techniques to customize existing statistical model cards to a given design.

Achieving those two goals can shorten the design manufacturing process by providing

Figure 1.2: Effects of scaling in mixed-signal circuit design.

guidelines for robust mixed-signal circuit design and improving the yield prediction of models at an early design stage.

## 1.3 Thesis organisation

The present dissertation is organized as follows. In Chapter 2 we present a more in-depth look into the device variability by summarizing its different types and their characteristics. Additionally, we discuss in more depth the traditional statistical modeling techniques and classify more advanced methods of yield optimization to two categories; those that utilize circuit performance modeling and those that utilize device performance modeling techniques. Chapter 3 presents a methodology for customized, design-specific model generation that targets at improving existing models. We present both the mathematical background as well as simulation examples of the proposed methodology. Chapter 4 discusses the necessary test structures for data extraction that will enable the use of custom models. Finally, measurement data and corresponding customized models are presented in Chapter 5.

# Chapter 2

## Variability and statistical modeling

As outlined in Chapter 1, increasing variability is becoming a bottleneck for both digital and analog circuit design. In order to understand it better, it is necessary to take an analytical approach and understand the different types of variability as well as the existent solutions. This is the goal of the current chapter. In Section 2.1, variability is defined and categorized based on its sources and general characteristics. In Sections 2.2 and 2.3, traditional and state-of-the-art statistical modeling techniques are presented and categorized based on their modeling approach, before the chapter concludes with a brief summary in Section 2.4.

### 2.1 Variability sources and effects

In order to fully understand the need for yield optimization in deeply-scaled device modeling, it is crucial to know some basic information about variability and its effects on circuit design, performance and cost. Variability describes any deviation of device performance from its designed or typical value, which may be caused by known or unknown reasons. Such reasons may be environmental, such as supply and temperature variation, or physical, such as process variation or atomic-scale effects [8, 9].

Physical variations can be further classified in many different ways, depending on their nature, their sources or their spatial and temporal characteristics. In [10] two main categories are used; intrinsic and extrinsic. Intrinsic variations are those that originate from atomic-scale effects, like quantum-mechanical effects and statistical variation in dopant profiles and particles. Extrinsic variations are mainly attributed to any shift in the process conditions, which causes parameter fluctuation usually with some spatial correlation.

With respect to spatial characteristics, process variations can be further classified to:

- 1. Lot-to-lot

- 2. Wafer-to-wafer, within a lot

- 3. Die-to-die, within a wafer

- 4. Within-die

Within-die variations are defined by parameters that vary significantly over distances smaller than the dimension of a die. Parameters that vary gradually across a wafer cause die-to-die variations. Wafer-to-wafer variations cause different wafers to have different properties. In a typical design methodology, designs are made to satisfy the worst case corners which consist of the total within-die and die-to-die variations.

Finally, another useful classification divides variations to random and systematic. Random variations are a result of stochastic natural processes that are unpredictable and affect each device in an arbitrary way. Systematic variations are deterministic shifts in device parameters that are better understood and usually more easily modeled.

Systematic variations have their sources largely in the manufacturing process and its different steps [11]. The implant and annealing process cause a different number of dopants to be positioned in different parts of the wafer. Oxide thickness variations are caused by non uniformity in the process of oxide growth. Non-uniform annealing temperature can cause further variation in the threshold voltage, while strain and stress can affect carrier mobility in a systematic fashion. Finally, lithography and etching effects induce variation in critical device sizes, like channel length and width, which are much narrower than the light wavelength used to print them.

Random variation sources lie in atomic-level effects like random dopant fluctuation (RDF) and line-edge roughness (LER). These variations get significantly worse with scaling, as intrinsic parameter fluctuations introduced by the discreteness of charge start to dominate. As channel length scales, less dopants are deposited in the channel for a fixed doping density. With less averaging into play, these discrete dopants start causing potential fluctuations due to their random distribution. The effect is called RDF and manifests itself primarily as threshold voltage variability. At the same time, scaling of dimensions closer and closer to the size of an atom causes previously smooth, continuous and distinct interfaces to become granular and pebbled. Granularity that affects the channel length is called LER. The introduction of thin body devices like FDSOI devices and FinFETS has brought additional sources of variation; granularity that affects the channel thickness in thin body devices is called silicon thickness variation and granularity in the width of the fins in FinFETs is called fin width variation. Other random variability sources that affect all devices are gate work-function variation as well as random strain and stress effects.

Both systematic and random variation are of great interest since they strongly affect circuit performance, yield and cost. More specifically, variability affects the yield of integrated circuits, which is defined as the probability that a circuit will meet the required specifications for a given product. In turn, yield affects the cost in an inversely proportional manner; high circuit yield enables mass production and lowers production cost. It is evident that

properly defining the maximum performance margins for a circuit and a certain yield can help optimize performance and cost, while and overestimation or underestimation of those margins can increase design complexity or compromise yield, respectively. Therefore, variability characterization and accurate yield modeling can enable lowering cost and making new technologies more accessible.

As mentioned in Chapter 1, in response to the increase in variability, statistical modeling methods have been developed to help designers improve circuit yield. Such methods include well-established techniques, such as generating worst-case corners for the model, introducing parameter variations through Monte-Carlo simulation or, in the case of digital design, modeling variations in gate delay and using statistical timing analysis (STA) to monitor how delay propagates through a circuit, as well as more sophisticated modeling techniques which generally seek to improve accuracy of corner modeling and Monte-Carlo simulation. Each method comes with advantages and disadvantages. An overview of the most well-established statistical modeling methods will be given in the following section.

## 2.2 Traditional statistical modeling techniques

A device model is basically the mapping of a set of input parameters to a set of output variables. For example, for a MOSFET device input parameters may be process parameters, like doping profile, carrier mobility and flatband voltage, and outputs include device threshold voltage and current, under certain operating conditions. In deeply scaled technologies models are typically a combination of equations that are derived through device physics and empirical equations; therefore, parameters can be physical as well as empirical. Adding variability to those parameters translates as device variability, and statistical modeling tackles the problem of determining what variability needs to be added and how, in order to properly represent the device.

Monte-Carlo simulation was introduced in the 1970s to integrated circuits for tolerance analysis [12]. To achieve that, random perturbations are added to model parameters, and the output variables are evaluated. By adding a distribution at the input and observing the output distribution, circuit yield can be calculated. Determining the right variance to add to each parameter is accomplished by measuring process variation data using a large set of devices. Since model parameters are generally correlated and large in quantity, principal component analysis (PCA) is typically used to reduce them to a smaller and more manageable set [13], while in newer models some parameter correlations may be preserved in order to improve accuracy. The disadvantages of Monte-Carlo simulation lay in the complexity and computational inefficiency. More specifically, since the nature of variability is very complex, accurately representing all different types of variability in a model quickly becomes an impossible task. Die-to-die and within-die are generally lumped together, and types of variation that are not well-modeled, like strain and time-dependent effects, are treated as random, which results to overly conservative design margins. Additionally, a large number of simula-

tions is required which makes the task of yield optimization very slow and computationally intense.

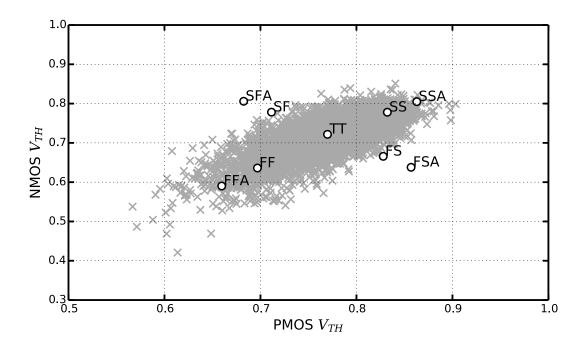

A faster and simpler way of accounting for systematic variability in models is corner modeling. The main idea here is to add deterministic shifts to process parameters, such that the output variables are evaluated not only for the typical case but also for cases where variation is present [14, 15]. By pushing the parameters n deviations away from their mean, the design performance can be evaluated at its worst-case corners. As variability rises, more corners become available in new models, including corners for analog design, based on device I-V curves, and corners for digital design, typically based on delay-chain measurements. Some of the corners for a 28nm technology are shown in Figure 2.1. Although corner modeling is fast and computationally efficient, in newer technologies it can result in overly optimistic or pessimistic results, as devices scale and variability becomes harder to track. Figure 2.1 compares the process corners to the results of a Monte-Carlo simulation; it is evident that a circuit that is designed to meet specification in the all corners spans a different design space than a circuit designed using Monte-Carlo, and therefore yields unreliable results. Additionally, precise yield prediction is hard to get, since yield represents individual device characteristics and therefore topology specific and layout-induced effects are ignored.

In order to tackle the insufficiencies of Monte-Carlo and corner modeling, design-specific or performance-aware modeling approaches have gained more popularity in the recent years. The main concept is illustrated in Figure 2.2 and involves identifying the actual design space

Figure 2.1: Corners and Monte-Carlo scatter plot of NMOS and PMOS  $V_{TH}$  (normalized).

and moving the design in order to increase the margin from failure. Some of these modeling techniques will be discussed in the following section.

### 2.3 Advances in statistical modeling

In the digital domain, variations play an important role since they are directly linked to timing and memory failures. However, digital CAD tools are fairly well developed and digital tool flows are automated, allowing for better design optimization and faster redesign. Along with corner modeling and Monte-Carlo, process variations have been traditionally modeled using static timing analysis (STA), which makes use of calibrated lookup tables for standard cells at multiple technology dependent corners. Traditional STA techniques are much faster than Monte-Carlo simulation, but due to the complex and interacting nature of various sources of variation they have become insufficient for highly scaled technology nodes, which led to the introduction of statistical static timing analysis (SSTA). SSTA computes an upper bound on the distribution of the exact circuit delay, accounting for die-to-die and within-die process variations and their spatial correlations [16–18]. Although more accurate, it has an exponential run time complexity. Methods and algorithms have been proposed in order to reduce runtime, however there remain large obstacles to the widespread use of SSTA in the industry [18, 19].

In analog and mixed signal integrated circuits, the design cycle remains long and errorprone [20]. As a result, although analog circuits are typically only a small fraction of a modern system-on-chip (SoC), their design and yield verification can often be the bottleneck for the

Figure 2.2: Illustration of design centering.

whole system. Recent advances in modeling try to address this problem by introducing yield optimization algorithms applied on circuit performance models or targeting at improving existing device models themselves. We classify these approaches into two broad categories:

- 1. Approaches that focus on circuit performance modeling

- 2. Approaches that focus on device performance modeling

These two types of modeling approaches are discussed in detail in the following paragraphs.

#### 2.3.1 Yield optimization through circuit performance modeling

In the area of yield optimization through performance modeling, the main effort is to try to create an accurate parametric model of the circuit and then apply an efficient yield optimization algorithm in order to center the design. The general design procedure is illustrated in Figure 2.3. The first step of the optimization is to generate a parametric response surface model for the circuit that is a function of the design variables and the process variables, using some form of regression technique. This process is also called symbolic modeling. Then a yield optimization algorithm is applied that typically formulates the problem as an optimization problem with respect to the design variables, given the model process variation. Finally the optimization problem is solved by means of convex optimization or geometrical programming. Such performance models are used to speed up circuit sizing: in every iteration of the synthesis procedure, calls to the transistor-level simulator are replaced by evaluations of a suitably constructed parametric model. The model building process is a one-time up-front investment that has to be done only once for each circuit in each technology.

The simplest type of model that can be used in order to estimate yield is a linear approximation of circuit performance [21, 22]. A stochastic approximation algorithm is then applied to the linear model to determine the design parameters that optimize yield. Whereas a simple linear approximation may work well for some circuits, it is not adequate to describe analog or mixed-signal circuits that present non-linearities, especially in deeply scaled technologies. Therefore more efforts have been made over the year to create polynomial and posynomial models. In [23], quadratic-style posynomial performance models for analog circuits are created by fitting a preassumed posynomial equation template to simulation data created according to a design of experiments scheme. The problem with using higher order models is that they are more complex and therefore more challenging to solve for all the necessary fitting coefficients. In order to mitigate that, the authors in [24], who also use quadratic polynomial/posynomial models, suggest a methodology called RObust Analog Design (ROAD). The methodology applies a projection operator with the goal of obtaining an optimal low-rank model by minimizing the approximation error, therefore achieving to simplify the problem and reduce modeling cost.

Another class of regression techniques borrows ideas from data mining, which focuses on extracting meaningful patterns to large amounts of high-dimensional data [25, 26]. The idea here is to exploit the large amount of simulation points one can get from the simulator in

Figure 2.3: Block diagram of circuit design process and yield optimization through parameteric performance modeling.

order to train a predictive model. Models including neural networks, boosted neural networks or support vector machines have been used for this purpose. As the aim of symbolic modeling is to use simulation data to generate interpretable mathematical expressions that relate the circuit performances to the design variables, these models generally fail to provide circuit insight.

All the aforemenentioned symbolic modeling techniques generally use some template for modeling, which means that model selection is restricted to a certain form, like a linear or quadratic form, for example. Another approach is presented in [27, 28]. The method is called Canonical Functional Form Expressions in Evolution (CAFFEINE) and it presents the first template-free model generation approach, i.e. the designer does not have to specify a priori a model template, but the model itself evolves as part of the optimization process.

Figure 2.4: Simplified illustration of a customized corner.

#### 2.3.2 Yield optimization through device performance modeling

All the techniques discussed in the previous section target at improving yield prediction by using existing simulation data. The accuracy of those techniques depends strongly on the accuracy of the variation data added to the device models. However, realistic worst case corners and variation data cannot be accurately predicted by IC foundries. The large number of different types of variability makes it impossible to capture, isolate and model all of them. Typically, different types of variation are lumped together in the models, sacrificing accuracy. Along with that, variation data is captured using individual device arrays, therefore ignoring topology-dependent and performance-dependent effects of more complex circuits. For this reason, it is beneficial to discover ways to improve the original device models to accurately represent variability for circuits of interest.

In [29, 30] the authors propose a hierarchical model for process variability. The model addresses both systematic and random variations at wafer, field, die, and device level, and spatial correlation artifacts are captured implicitly. Finally, layout dependent effects are incorporated as an additive component. In [31] the authors incorporate spatial correlation of model parameters into their models to further improve them. In both cases, models become significantly more complex.

Another approach is to create customized or performance aware corners for a given design. A customized corner is defined as the tangential point between performance function contours of the design and the parameter variability ellipsoid, as show in Figure 2.4 [32]. In [33, 34] the authors apply backpropagation of variance in order to evaluate model parameter variances based on measurements. By using the methodology with measurements from specific circuits, it is possible to create performance-driven device models for the circuits of interest. Though a generally efficient model for simple systems, it is dependent on

handpicking parameters and has increased numerical complexity for large systems. In [35] the authors propose a methodology to generate performance-aware corner models. Although promising, the methodology assumes prior knowledge of the variation of some of the physical parameters and is based on simplified model equations.

#### 2.4 Summary

In this chapter, different types of classification of variations were presented; among them, variations were categorized to random and systematic, based on whether they are a result of unpredictable natural processes, or better-understood design conditions. This is one of the most important variation classifications, and it will be used throughout this thesis. Additionally, traditional and advanced modeling techniques were presented, and their advantages and disadvantages were discussed. It was shown that performance-aware device models, also described as custom corners, are possible.

Because of the curse of dimensionality, custom corners are very hard to analytically find and incorporate into the models. Technology scaling however imposes new restrictions to manufacturing resulting in more design rules - for example, gate orientation becomes fixed, poly and metal densities are carefully controlled, gate pitch gets confined to predefined values, transistor dimensions scale by fixed steps. Consequently, the number of practical circuit and layout topologies reduces, making design-specific modeling an increasingly attractive option. Containing the problem to a smaller set of designs and parameters, it is possible to create customized model cards to better predict design yield. In the following chapter, a methodology for creating customized models will be discussed.

# Chapter 3

# Customized model generation

In this chapter, a methodology for optimizing statistical models customized to a given class of designs is presented. The methodology builds on the existing body of modeling, employs the backpropagation of variance technique to improve the variation assigned to each model variable and is adapted to include existing model parameter correlations. We then formulate the problem as a constrained convex optimization problem, including parameter selection as well as the addition of physical, model-derived constraints by the designer. This enables the creation of customized model cards for robust design of high-performance circuit blocks.

Section 3.1 presents the theoretical background for base models and customized model creation, followed by a set of simulation examples for preliminary model validation, shown in Section 3.2. The chapter concludes with a brief summary of the main points in Section 3.3.

### 3.1 Customized models

#### 3.1.1 Base models

The first step to model customization is understanding basic concepts of modeling and, especially, of how models treat variations. In general, models describe the device behavior to the circuit simulation program, and so they need to describe a variety of physical effects. For modern devices, a completely theoretical model based on the fundamentals of physics becomes practically intractable. On the other hand, use of a completely empirical model results in a loss of predictive capabilities. A compromise is usually made in developing models for circuit simulation. A combination of physics-based and empirical equations is used. The

Figure 3.1: Illustration of principal component analysis using a 3-dimensional space as an example.

primary model parameters are closely linked to theory providing an engineering understanding of device physics and serving as a process control aid. The secondary model parameters are partly empirical and help keep the model equations simple. The extraction of optimum model parameter values is necessary to ensure that the device model equations represent the device characteristics closely. Although most models are based on physical theory, there are always some parameters which do not have physically well-defined values, and others for which the physical values do not give the best fit to actual device characteristics. Thus it is generally necessary to extract model parameters from transistor data, obtained from device characterization [36].

In order to include variations in a model, sets of device characterization test structures are designed, typically consisting of a large number of devices under test. Assuming there are M devices under test and N model parameters for each device, then the total number of parameters is a vector of length  $d = M \times N$ :

$$\mathbf{x} = \begin{bmatrix} x_1 & x_1 & \dots & x_d \end{bmatrix}^T \tag{3.1}$$

Now if the parameter vector is treated as a vector of random variables (RVs)  $\mathbf{X}$  and  $\mathbf{X_0} = E[\mathbf{X}]$  is the vector with the nominal values of the parameters, then  $\Delta \mathbf{X} = \mathbf{X} - \mathbf{X_0}$  contains the variations from the nominal values with a zero-mean distribution.  $\Delta \mathbf{X}$  is typically modeled as a set of zero-mean jointly normal RVs that are generally correlated. Let  $\Sigma$  be the covariance matrix of  $\Delta \mathbf{X}$  and  $\mathbf{T}$  an orthogonal matrix such that:

$$\mathbf{T}'\mathbf{\Sigma}\mathbf{T} = \mathbf{\Lambda} = diag(\lambda_1, \lambda_2, ..., \lambda_d)$$

(3.2)

where  $\lambda_1 \geq \lambda_2 \geq ... \geq \lambda_d$  are the eigenvalues of  $\Sigma$ . Let  $\Delta \mathbf{Y} = \mathbf{T}' \Delta \mathbf{X}$ , then it can be shown that the  $\Delta Y_j$  are uncorrelated and  $Var[\Delta Y_j] = \lambda_j$ . Then  $\Delta Y_j$  is called the *j*th principal component of  $\Delta \mathbf{X}$  and the process is called principal component analysis (PCA). Intuitively,

starting from a complex set of variables, illustrated as a coordinate system in Figure 3.1, PCA finds a new set of variables orthogonal to each other and then rotates the coordinate system. It can also be shown that it is possible to reduce the dimension of  $\Delta X$  with small loss of information by essentially dropping the components that matter least. A more rigorous mathematical analysis of PCA and dimensionality reduction can be found in [37].

Principal component analysis is widely used in statistical models for two reasons. Firstly, it enables transforming a correlated set of normally distributed parameters to a set of mutually independent parameters. Secondly, it enables reducing the set of parameters to a smaller, more manageable set without significant loss of accuracy. From now on, when referring to base model parameters, we will refer to this reduced set of mutually independent parameters.

#### 3.1.2 Base model tuning

A circuit simulator requires three types of information to specify a transistor model completely: fundamental constants, operating conditions and model parameters. We denote the fundamental physical constants as a vector  $\mathbf{c}$ , containing constants such as electronic charge. Those are defined inside the circuit simulation program. The operating conditions define the circumstances under which the model equations are to be evaluated, and we will denote them as a vector  $\mathbf{x}$ . The operating conditions are normally the transistor's bias voltages, temperature etc. Finally, the third set of information required is the set of model parameters for each device in the circuit, denoted here as  $\mathbf{p}$ . The model output vector  $\mathbf{y}$  is a function of  $\mathbf{x}$ ,  $\mathbf{p}$  and  $\mathbf{c}$ .

$$\boldsymbol{x} = f(\boldsymbol{x}, \mathbf{p}, \mathbf{c}) \tag{3.3}$$

For a given design biased around a bias point  $\mathbf{x} = \mathbf{x}^*$ , Equation 3.3 can be re-written as  $\mathbf{y} = f(\mathbf{x}^*, \mathbf{p}, \mathbf{c}) = f(\mathbf{p})$ , where  $\mathbf{y} = [y_1, ..., y_m]^T$  is the output vector of the circuit and  $\mathbf{p} = [p_1, ..., p_n]^T$  is the parameter vector of the given base model. In order to incorporate variability to the models, each of the parameters in  $\mathbf{p}$  is treated as an independent random variable (RV)  $P_i$  and assigned a normal distribution with mean  $\mu_i$  and standard deviation  $\sigma_i$ , i = 1, ..., n. Let  $\mathbf{p_0}$  denote the vector of mean values and  $\mathbf{P} = \mathbf{p_0} + \Delta \mathbf{P}$ , we have:

$$\mathbf{Y} = f(\mathbf{P}) : \Re^n \to \Re^m \tag{3.4}$$

The Taylor expansion of (3.4) around the nominal point  $\mathbf{p_0}$  is:

$$\mathbf{Y} = f(\mathbf{p_0}) + \mathbf{J}(\mathbf{P} - \mathbf{p_0}) + \frac{1}{2!}\mathbf{G}(\mathbf{P} - \mathbf{p_0}) \otimes (\mathbf{P} - \mathbf{p_0}) + h.o.t.$$

(3.5)

where  $\mathbf{J} \in \Re^{m \times n}$  is the partial derivatives (Jacobian) matrix, defined in Equation 3.6,  $\mathbf{G} \in \Re^{m \times n \times n}$  is the second-order partial derivatives matrix, defined in Equation 3.7, and  $\otimes$  symbolizes the Kronecker product.

$$\mathbf{J} = \begin{bmatrix} \frac{\partial f_1}{\partial x_1} & \frac{\partial f_1}{\partial x_2} & \cdots & \frac{\partial f_1}{\partial x_n} \\ \frac{\partial f_2}{\partial x_1} & \ddots & & \vdots \\ \vdots & & \ddots & \vdots \\ \frac{\partial f_m}{\partial x_1} & \cdots & \frac{\partial f_m}{\partial x_{n-1}} & \frac{\partial f_m}{\partial x_n} \end{bmatrix}$$

(3.6)

$$\mathbf{G} = \begin{bmatrix} \frac{\partial \mathbf{J}}{\partial x_1} & \frac{\partial \mathbf{J}}{\partial x_2} & \cdots & \frac{\partial \mathbf{J}}{\partial x_n} \end{bmatrix} \text{ where } \frac{\partial \mathbf{J}}{\partial x_p} = \begin{bmatrix} \frac{\partial^2 f_1}{\partial x_p \partial x_1} & \frac{\partial^2 f_1}{\partial x_p \partial x_2} & \cdots & \frac{\partial^2 f_1}{\partial x_p \partial x_n} \\ \frac{\partial^2 f_2}{\partial x_p \partial x_1} & \ddots & & \vdots \\ \vdots & & \ddots & & \vdots \\ \frac{\partial^2 f_m}{\partial x_p \partial x_1} & \cdots & \frac{\partial^2 f_m}{\partial x_p \partial x_{n-1}} & \frac{\partial^2 f_m}{\partial x_p \partial x_n} \end{bmatrix}$$

(3.7)

Assuming small perturbations we can remove the high-order terms from Equation 3.5 and get:

$$\mathbf{Y} = f(\mathbf{p_0}) + \mathbf{J}(\mathbf{P} - \mathbf{p_0}) = f(\mathbf{P_0}) + \mathbf{J} \cdot \Delta \mathbf{P} \Rightarrow$$

$$\mathbf{Y} - f(\mathbf{P_0}) = \mathbf{J} \cdot \Delta \mathbf{P} \Rightarrow$$

$$\Delta \mathbf{Y} = \mathbf{J} \cdot \Delta \mathbf{P}$$

(3.8)

Next, we transform Equation 3.8 as follows:

$$\Delta \mathbf{Y} \cdot \Delta \mathbf{Y}^{T} = \mathbf{J} \cdot \Delta \mathbf{P} \cdot \Delta \mathbf{P}^{T} \cdot \mathbf{J}^{T} \Rightarrow$$

$$E[\Delta \mathbf{Y} \cdot \Delta \mathbf{Y}^{T}] = E[\mathbf{J} \cdot \Delta \mathbf{P} \cdot \Delta \mathbf{P}^{T} \cdot \mathbf{J}^{T}] \Rightarrow$$

$$\mathbf{R}_{\Delta \mathbf{Y}} = \mathbf{J} \cdot \mathbf{R}_{\Delta \mathbf{P}} \cdot \mathbf{J}^{T}$$

(3.9)

where  $\mathbf{R}_{\Delta \mathbf{Y}}$ ,  $\mathbf{R}_{\Delta \mathbf{P}}$  the autocorrelation matrices of  $\Delta \mathbf{Y}$  and  $\Delta \mathbf{P}$ , respectively. Since  $P_i$  are independent, the matrix  $\mathbf{R}_{\Delta \mathbf{P}}$  is diagonal, and all the diagonal elements represent variances of the parameters, which are the unknowns. Similarly, in matrix  $\mathbf{R}_{\Delta \mathbf{Y}}$ , the diagonal elements are the variances of the outputs.

Denoting the  $k^{th}$  unit vector  $\mathbf{u}_k$  as a vector with all zeros except a one on the  $k^{th}$  row, we can derive an expression for the  $k^{th}$  diagonal element of  $\mathbf{R}_{\Delta \mathbf{Y}}$  by using Equation 3.9:

$$\sigma_{\Delta Y_k}^2 = \mathbf{u}_k^T \cdot \mathbf{R}_{\Delta \mathbf{Y}} \cdot \mathbf{u}_k = \mathbf{u}_k^T \cdot \mathbf{J} \cdot \mathbf{R}_{\Delta \mathbf{P}} \cdot \mathbf{J}^T \cdot \mathbf{u}_k$$

(3.10)

Let  $\mathbf{v}_k^T = \mathbf{u}_k^T \cdot \mathbf{J}$ , where k = 1, ..., m. It is evident that  $\mathbf{v}_k^T$  is the  $k^{th}$  row of the Jacobian matrix  $\mathbf{J}$ . From the above, we can now transform the problem to a linear optimization problem of the form  $\mathbf{b} = \mathbf{A} \cdot \mathbf{x}$ , relating the variances of the outputs on the left-hand side to the squares of the sensitivities and the input variances on the right-hand side.

$$\underbrace{\begin{pmatrix} \sigma_{\Delta y_1}^2 \\ \sigma_{\Delta y_2}^2 \\ \vdots \\ \sigma_{\Delta y_m}^2 \end{pmatrix}}_{\mathbf{b}} = \underbrace{\begin{pmatrix} J_{11}^2 & J_{12}^2 & \cdots & J_{1n}^2 \\ J_{21}^2 & J_{22}^2 & \cdots & J_{2n}^2 \\ \vdots & \vdots & \ddots & \vdots \\ J_{m1}^2 & J_{m2}^2 & \cdots & J_{mn}^2 \end{pmatrix}}_{\mathbf{A}} \cdot \underbrace{\begin{pmatrix} \sigma_{\Delta p_1}^2 \\ \sigma_{\Delta p_2}^2 \\ \vdots \\ \sigma_{\Delta p_n}^2 \end{pmatrix}}_{\mathbf{x}} \tag{3.11}$$

Although typically PCA is used in order to get an independent model parameter set, in some cases parameter correlations may be preserved by the models, for example correlations between the NMOS and PMOS parameters. As long as the covariance of the correlated parameters can be calculated using the given model, the above function can be altered to incorporate correlations. If, for example, two parameters with indices u and v are correlated, a term  $2 \cdot J_{ku} \cdot J_{kv} \cdot cov(\Delta p_u, \Delta p_v)$  is added to the right-hand side of the equation for the  $k^{th}$  output variance. From here, given a set of observations of the output vector extracted by test structures, we can calculate the variances of the parameters by solving Equation 3.11.

#### 3.1.3 Parameter screening and system constraints

The resulting  $m \times n$  system of equations has, in the general case, more inputs than outputs (m < n). Linear systems of equations are normally solved by minimizing the residual sum of squares as shown in (3.12).

$$\underset{x}{\text{minimize }} \|\mathbf{b} - \mathbf{A} \cdot \mathbf{x}\|_{2}^{2} \tag{3.12}$$

In the case of overdetermined systems (n < m), the least-squares approach is guaranteed to find a unique closed-form solution. In underdetermined systems however, there is an infinite number of solutions, if any. In this case, it is common to formulate the problem as shown in (3.13) and select the minimum norm solution.

minimize

$$\|\mathbf{x}\|_2^2$$

subject to  $\mathbf{b} = \mathbf{A} \cdot \mathbf{x}$  (3.13)

However, in this case the minimum norm solution will not generally be an applicable one. The reason for that is that there are constraints imposed by the models and the nature of the problem. For example, a solution that contains negative values is not acceptable, since the unknowns represent variances and are therefore always non-negative. In order to guarantee a physically acceptable solution, we perform parameter screening and then add physical explicit constraints to the problem.

Table 3.1: First step of parameter selection

| Given $\mathbf{A}_{m \times n}$ , $\mathbf{x}_{n \times 1}$ |                                              |  |

|-------------------------------------------------------------|----------------------------------------------|--|

| 1:                                                          | for $j = 1, 2,, n$                           |  |

| 2:                                                          | if $  \mathbf{A}_{\bullet j}   \leq \lambda$ |  |

| 3:                                                          | eliminate $\mathbf{A}_{ullet j}$             |  |

| 4:                                                          | eliminate $x_j$                              |  |

| 5:                                                          | return $\mathbf{A}$ , $\mathbf{x}$           |  |

Parameter screening in the system of Equation 3.11 enables the reduction of the length of  $\mathbf{x}$  and is done in two steps. First, we observe that matrix  $\mathbf{A}$  will, in the general case, have some level of sparsity. This observation is motivated by the fact that only a certain number of all model parameters will play an important role for the chosen output in a given system. In other words, a given output may be insensitive to certain parameters. This observation allows the designer to eliminate columns of the sensitivity matrix using a simple algorithm shown in Table 3.1, where  $\mathbf{A}_{\bullet j}$  denotes the  $j^{th}$  column of the matrix  $\mathbf{A}$ . Parameter  $\lambda$  provides a tradeoff between complexity (i.e. number of parameters) of the final system and accuracy, and should be selected by the designer to accommodate the given design. At this first step  $\lambda$  is kept very small, so that only column that have zero-norms or norms that are multiple orders of magnitude lower get eliminated. This conservative selection may be enough for some cases, depending on the given design and the given models. If it is not enough, we proceed with more sophisticated parameter selections methods, discussed below.

If after the first step of parameter selection, the system is still underdetermined, we introduce some form of regression in order to produce a final solution. For this, we use a combination of ridge regression [38] and the least absolute shrinkage and selection operator (LASSO) [39, 40]. Both are forms of regularization used in statistics and machine learning in order to find a solution to ill-formed problems by adding an additional constraint to the system. Ridge regression constraints the  $l_2$ -norm of the solution, as shown in (3.14), which helps shrink large coefficients to reduce overfitting, as illustrated in Figure 3.2 using example data.

minimize

$$\|\mathbf{b} - \mathbf{A} \cdot \mathbf{x}\|_2^2$$

subject to  $\|\mathbf{x}\|_2 < t$  (3.14)

The LASSO, shown in (3.15), constraints the  $l_1$ -norm of the solution. This not only helps shrink large coefficients, like ridge regression, but also forces some coefficients to zero, therefore achieving parameter selection. In Figures 3.3 and 3.5, it is shown that as t increases, more and more coefficients get non-zero values and prediction error is reduced, and therefore t provides a trade-off between complexity and accuracy. LASSO has been previously used as

Figure 3.2: Ridge regression, produced with artificially generated data. Coefficients are kept small and converge to their final values.

an improvement of response surface modeling for large-scale performance modeling problems, demonstrating dimensionality reduction without overfitting [41].

minimize

$$\|\mathbf{b} - \mathbf{A} \cdot \mathbf{x}\|_2^2$$

subject to  $\|\mathbf{x}\|_1 < t$  (3.15)

Stable convergence, shrinkage and parameter selection can be achieved by combining the two regularization methods to an elastic net formulation, shown in (3.16) [42]. Figure 3.6 shows an illustration of the penalty terms for each of the aforementioned regularization techniques, for a 2-parameter system. The elastic net penalty term is a convex combination of ridge regression, for  $\rho = 1$ , and the LASSO, for  $\rho = 0$ . Figure 3.4 shows the effect on the coefficients when applying his method to the same example data as before.

minimize

$$\|\mathbf{b} - \mathbf{A} \cdot \mathbf{x}\|_2^2$$

subject to  $(1 - \rho)\|\mathbf{x}\|_1 + \rho\|\mathbf{x}\|_2 < t$  (3.16)

So far we have exploited several statistical concepts in order to reduce the parameter space and produce a system solution while avoiding overfitting. However, in device modeling there is only a limited set of solutions that are physically acceptable, and the solution produced

Figure 3.3: LASSO solution, produced with artificially generated data. For decreasing t, more and more coefficients are forced to zero.

from (3.16) may not be one of them. In order to limit the solution space into that physically acceptable set, we introduce a number of constraints based on knowledge of the system and models. Such constraints are derived directly by the nature of the solution, for example  $\mathbf{x} \geq 0$  since  $\mathbf{x}$  consists of variances, and from the given model documentation. Therefore, we formulate the problem as a constrained convex optimization problem.

minimize

$$\|\mathbf{b} - \mathbf{A} \cdot \mathbf{x}\|_{2}^{2}$$

subject to

$$\begin{cases} (1 - \rho) \|\mathbf{x}\|_{1} + \rho \|\mathbf{x}\|_{2} < t \\ 1 \le \mathbf{x} \le \mathbf{u} \end{cases}$$

(3.17)

In Equation 3.17,  $\mathbf{l}$  and  $\mathbf{u}$  indicate the lower and upper boundaries of  $\mathbf{x}$ , respectively. Note that not all parameters need to be constrained, in which case the corresponding elements of vectors  $\mathbf{l}$  and  $\mathbf{u}$  can be set to 0 and a very large value, respectively.

The final solution,  $\mathbf{x}^*$ , contains the variances of each parameter, which are then added back into the model, therefore generating a customized model card, tied to the specific design.

Figure 3.4: Elastic net solution with  $\rho = 0.5$ , produced with artificially generated data. The solution combines the properties of ridge regression and LASSO, depending upon the value of  $\rho$ .

Figure 3.5: Root mean square error for ridge, LASSO and elastic net regression.

Figure 3.6: Two-dimensional contour plots of the ridge (black), LASSO(light grey) and elastic net (dark grey) penalty terms for a hypothetical 2-parameter system. The dotted line indicates the valid solution space.

# 3.2 Application examples

### 3.2.1 Customized models for device characterization

For a first-order validation of this methodology through simulation, we extract voltagecurrent characteristics of NMOS and PMOS devices in a 28nm FDSOI technology, given a PSP technology model. The circuit used for extraction is shown in Figure 3.7. The selection of this test structure allows us to compare the customized model cards directly to the original cards.

## Methodology

In order to set up the system of Equations 3.11, we begin with identifying the complete statistical parameter set used in the given models. Figure 3.8 shows scatter plots of some of the parameters extracted from MC simulation revealing full correlation in two pairs of parameters that are physically linked, which are incorporated into Equation 3.11. Only a

Figure 3.7: Simulation circuit for IV curve extraction of NMOS and PMOS.

subset of the parameters used is shown in order to simplify plots. The full set of statistical parameters in this particular model is shown in Table 3.2. The fourth column of the Table shows the model used for certain parameter correlations in the model.

The next step is the selection of the outputs of interest for the specific design. Here, we select a set of 5 outputs that are of interest for digital and/or analog design:

$$\mathbf{y} = [I_{on}, V_{th}, logI_{off}, g_m, g_o]$$

Next, we use finite differences to extract the Jacobian matrix from the given simulation model. The top part of Table 3.3 shows the extracted percent sensitivities of each output with respect to the parameter subset and therefore corresponds to matrix  $\mathbf{J}$ , and the bottom part shows the calculated norms of each column of matrix  $\mathbf{A}$ . This format shows the tradeoff between choosing a smaller or larger  $\lambda$  for parameter selection. Zero columns are automatically removed from the system, and the choice of  $\lambda$  in the order of  $1e^{-8}$  further reduces the size of the final system to 8 parameters without significant error.

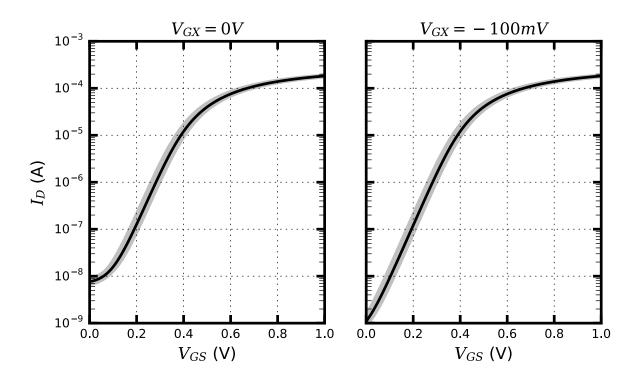

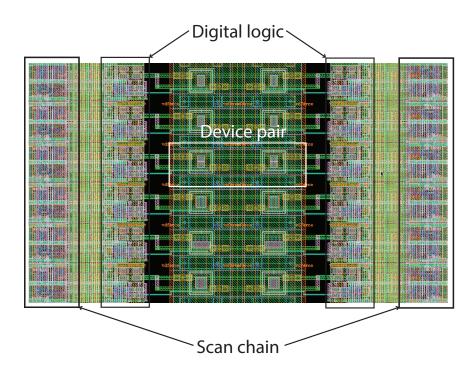

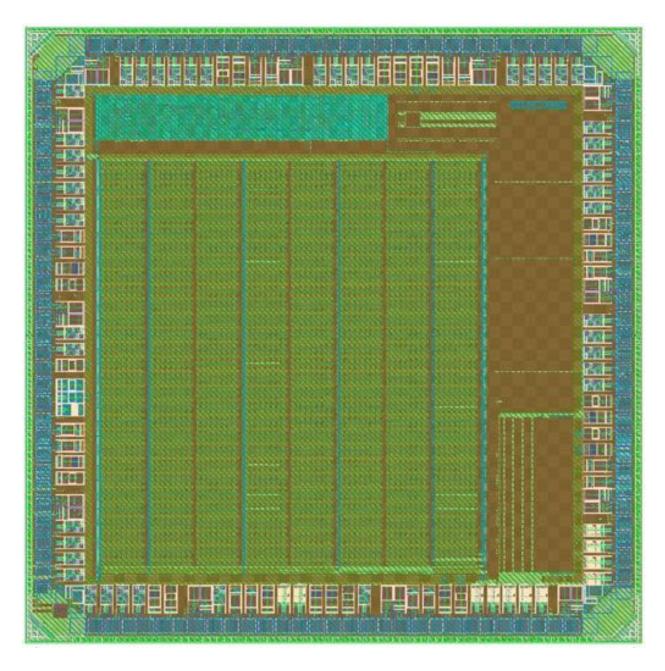

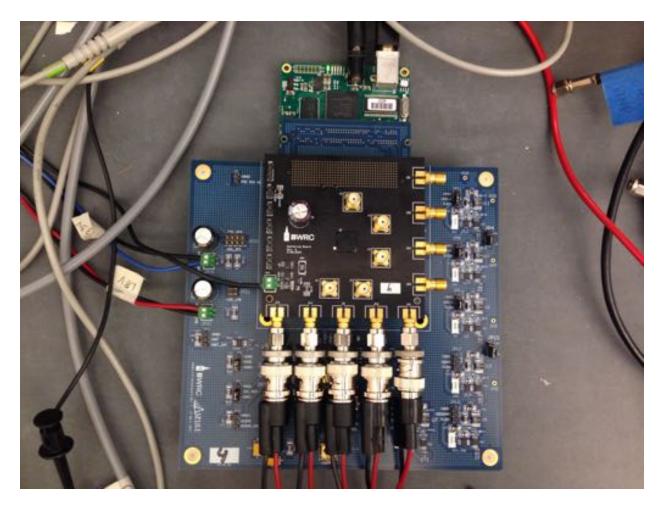

After parameter selection, physical constraints are added in order to limit the solution space. The first and most obvious constraint that needs to be added to the system is  $\mathbf{x} \geq 0$ , since  $\mathbf{x}$  is a vector of variances. From there, minimum and maximum values for some parameters are derived from the model documentation, whereas other parameters remain unconstrained. The resulting optimization problem is then solved using a commercially available convex programming package, like CVX [43, 44].