## Variability-Aware Compact Modeling of Nano-scale Technologies with Customized Test Structure Designs

Ying Qiao Costas J. Spanos, Ed. Borivoje Nikolic, Ed.

Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2018-148 http://www2.eecs.berkeley.edu/Pubs/TechRpts/2018/EECS-2018-148.html

December 1, 2018

Copyright © 2018, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# Variability-Aware Compact Modeling of Nano-scale Technologies with Customized Test Structure Designs

by

Ying Qiao

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering – Electrical Engineering and Computer Sciences

in the

**Graduate Division**

of the

University of California, Berkeley

Committee in charge:

Professor Costas J. Spanos, Chair

Professor Borivoje Nikolić

Professor Haiyan Huang

Spring 2017

# Variability-Aware Compact Modeling of Nano-scale Technologies with Customized Test Structure Designs

Copyright © 2017

by

Ying Qiao

#### Abstract

Variability-Aware Compact Modeling of Nano-scale Technologies with Customized Test Structure Designs

by Ying Qiao

Doctor of Philosophy in Electrical Engineering and Computer Sciences

University of California, Berkeley Professor Costas J. Spanos, Chair

It is widely recognized that in nano-scale CMOS technology variation in the manufacturing process has emerged as a fundamental challenge to IC design. While foundries are working hard to mitigate process variability, the design houses are asking for accurate and appropriate models to handle statistical circuit performance evaluation. To accurately represent the process and device variability, it is essential to incorporate the variability during the extraction and calibration phase of compact transistor models. In addition, these compact transistor models require customized test structure designs as well as proper statistical characterization procedures. Conventional statistical compact model characterization methodologies require special single transistor, direct-access test arrays, or virtual measurements from physical simulation data; moreover, these models do not include rigorous statistical model parameter selection criteria.

Our proposed variability-aware compact transistor models can enable statistically optimized designs by capturing device variations in a concise, yet physically accurate way, and they are relatively easy to integrate with existing CAD tool flow. In this work, we have electrical measurements from carefully designed SRAM array test structures with bit transistor access, fabricated using a collaborating foundry's 28nm FDSOI technology. Stepwise parameter selection is combined with sequential extractions of statistical compact model parameters upon foundry-provided nominal compact model cards. These nominal models are trusted as they have been tested extensively and used during the test structure design.

Our characterization methodology selects an optimal statistical model parameter set that can be reliability extracted with the given measurement data. With further data from imaging ROIC test array, we are able to explore the linear spatial propagation of variance method to extract the variability in the compact model parameters with hierarchical models.

We have also built a customized Monte Carlo (MC) simulation platform to utilize these compact transistor models in the statistical IC design flow. Different statistical model parameters can be specified prior to the MC simulation within the scripted wrapper of standard SPICE-based simulators. We further exploit the statistical structure of the extracted parameters in order to capture the nonlinear correlations and the non-Gaussian distributions through mixture of Gaussian distributions. The goal is to demonstrate that significant non-normality in the measured data can be captured by our simplified model. Such non-normality is often evident at the tails of the performance distributions, and capturing that is necessary for the statistical modeling of inherently high-yielding IC designs.

To my mom and dad

# **Contents**

| List of Figu | res and Tables                                 | V   |

|--------------|------------------------------------------------|-----|

| Chapter 1    | Introduction                                   | 1   |

| 1.1 M        | otivation: Process Variation                   | 1   |

| 1.2 Ba       | nckground                                      | 3   |

| 1.2.1        | Advanced Transistor Structures                 | 3   |

| 1.2.2        | Sources of Variation                           | 6   |

| 1.2.3        | Test Structures for Variation Characterization | 8   |

| 1.3 Th       | nesis Organization                             | 9   |

| Chapter 2    | Variability Characterization Test Structures   | 14  |

| 2.1 In       | troduction                                     | 14  |

| 2.2 Tr       | ansistor Characterization Array Design         | 15  |

| 2.2.1        | Random Variability Test Structures             | 17  |

| 2.2.2        | Systematic Variability Test Structures         | 18  |

| 2.2.         | 2.1 Shallow Trench Isolation (STI) Effect      | 18  |

| 2.2.         | 2.2 Length of Diffusion Effect                 | 19  |

| 2.2.         | 2.3 Well Proximity Effect                      | 21  |

| 2.2.         | 2.4 Segmented Channel Transistors              | 22  |

| 2.3 Tr       | ansistor Array Test Setup and Measurement      | 23  |

| 2.3.1        | Test Circuitry                                 | 23  |

| 2.3.2        | Measurement Setup                              | 28  |

| 2.3.3        | Variability Observation                        | 32  |

| 2.4 Su       | ımmary                                         | 36  |

| Chapter 3    | •                                              |     |

|              | rification                                     |     |

|              | troduction                                     |     |

|              | atistical Compact Model Characterization       |     |

| 3.2.1        | MOSFET Device Models and Extraction            | 40  |

| 322          | Statistical Device Characterization            | 42. |

|     | 3.2.2.     | 1 Stepwise Compact Model Parameter Selection Algorithm                 | <b>m</b> 43 |

|-----|------------|------------------------------------------------------------------------|-------------|

|     | 3.2.2.     | 2 Linear Spatial Backward Propagation of Variance                      | 48          |

| 3.3 | Stat       | istical Circuit Verification                                           | 52          |

| 3.3 | <b>3.1</b> | Statistical Parametric Yield Estimation                                | 52          |

|     | 3.3.1.     | 1 Customized Monte Carlo Simulation                                    | 52          |

| 3.3 | 3.2        | Statistical Circuit Modeling                                           | 54          |

|     | 3.3.2.     | 1 Enhanced Method with Gaussian Mixture Model                          | 56          |

| 3.4 | Sun        | ımary                                                                  | 58          |

| _   |            | Variability-Aware Compact Modeling and Statistical Cin SRAM Test Array |             |

| 4.1 | Intr       | oduction                                                               | 61          |

| 4.2 | SRA        | AM Test Array Design and Measurement                                   | 62          |

| 4.2 | 2.1        | 6T SRAM Macro                                                          | 62          |

| 4.2 | 2.2        | Test Circuitry                                                         | 64          |

| 4.2 | 2.3        | Measurement Setup                                                      | 65          |

| 4.3 | SRA        | AM Transistor PSP Model Statistical Characterization                   | 67          |

| 4.3 | <b>3.1</b> | Review of PSP Model Parameters                                         | 67          |

| 4.3 | 3.2        | Statistical Model Characterization Results                             | 69          |

| 4.4 | Stat       | istical Circuit Simulation Results on SRAM writability                 | 72          |

| 4.5 | Sun        | ımary                                                                  | 75          |

| _   |            | Statistical Device Characterization and Circuit Modeling IC Data       |             |

| 5.1 | Intr       | oduction                                                               | 78          |

| 5.2 | Ima        | ging ROIC Design and Measurement                                       | 79          |

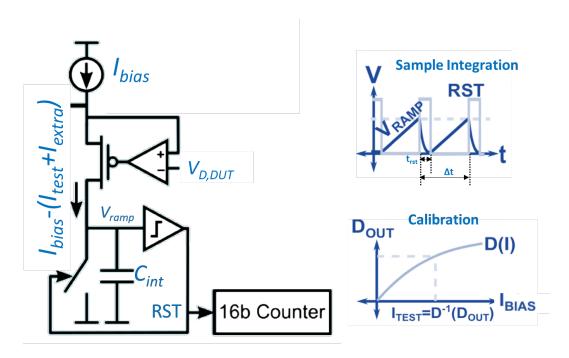

| 5.2 | 2.1        | DUT and Measurement Cell                                               | 80          |

| 5.2 | 2.2        | Test Chip Architecture                                                 | 82          |

| 5.2 | 2.3        | Measurement Procedure and Calibration                                  | 83          |

| 5.3 | Tra        | nsistor Model Statistical Characterization                             | 84          |

| 5.3 | 3.1        | Dataset Description and PSP Model Parameter Review                     | 84          |

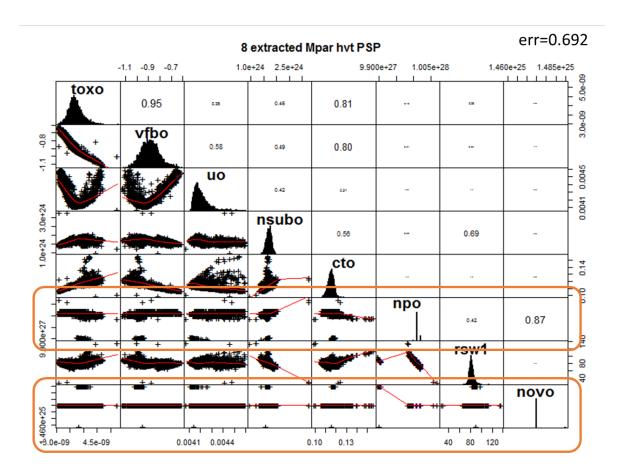

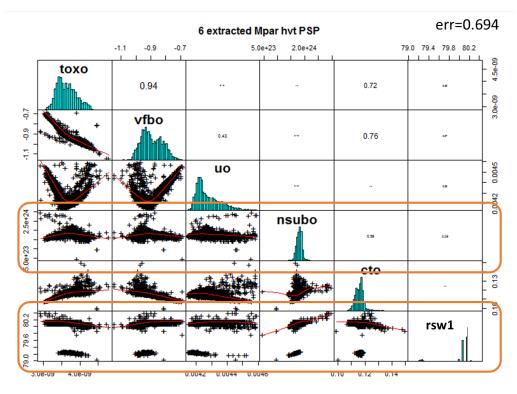

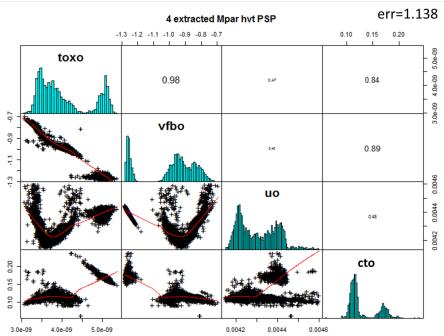

| 5.3 | 3.2        | <b>Stepwise Compact Model Parameter Selection Results</b>              | 86          |

| 5.3 | 3.3        | Linear SBPV Device Characterization Results                            | 90          |

|           | ratistical Circuit Modeling and Verification Results on Crit |      |

|-----------|--------------------------------------------------------------|------|

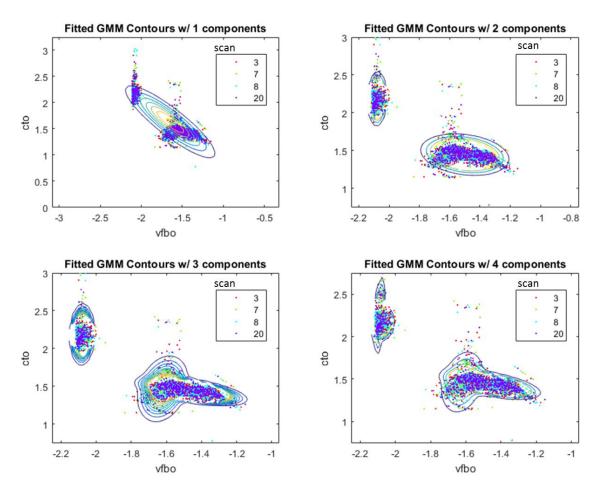

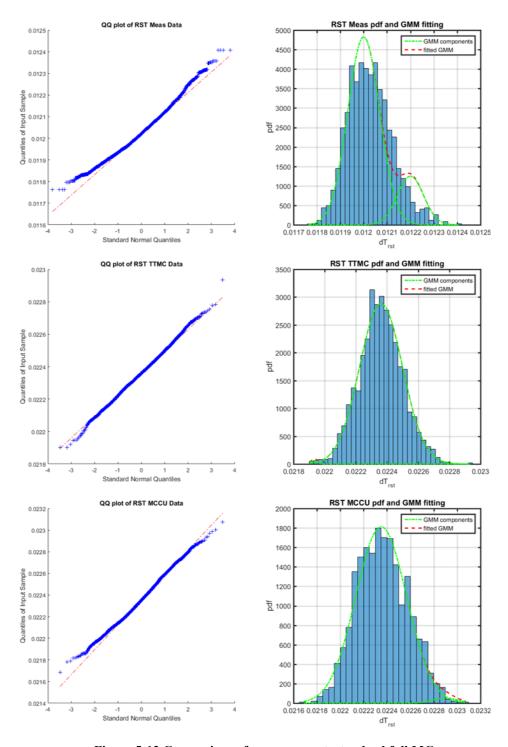

| 5.4.1     | Circuit Performance GMM Results                              | . 92 |

| 5.4.2     | Customized MC Simulation Results                             | . 94 |

| 5.5 St    | ımmary                                                       | . 99 |

| Chapter 6 | Conclusion                                                   | 102  |

| 6.1 St    | ımmary and Thesis contribution                               | 102  |

| 6.2 St    | iggestions for Future Work                                   | 103  |

| 6.2.1     | Process Variation Ahead                                      | 103  |

| 6.2.2     | Variation Prediction within a Process Development Cycle      | 104  |

# **List of Figures and Tables**

| Figure 1-1 Increase of process variability in conventional scaled MOS technology [1-2]                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2 TEM cross-sections of MOSFETs at various technology nodes, with approximately the same scale [1-7]4                                                                                                           |

| Figure 1-3 (a) 3D view of a planar FD-SOI transistor [1-12]; (b) A TEM cross-section of N-channel FD-SOI transistors [1-13]5                                                                                             |

| Figure 1-4 (a) 3D view of a vertical FinFET transistor; (b) TEM image of an array of FinFET transistors showing the fin and gate features [1-14]5                                                                        |

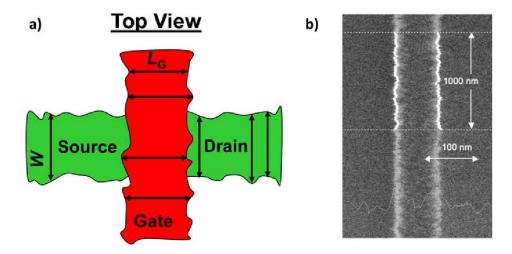

| Figure 1-5 (a) Top view showing how LER can affect the gate length and channel width of a transistor; (b) SEM image of a photoresist line with LER [1-19]                                                                |

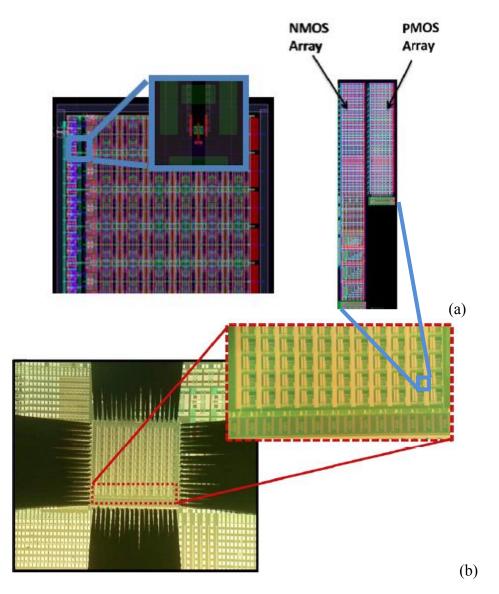

| Figure 2-1 (a) Layout of transistors characterization block and DUT (b) Photo of a die under test with probe tips landed on top; zoomed-in photo of the die showing the macro on the bottom row                          |

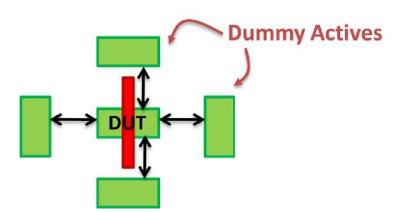

| Figure 2-2 Layout showing DUT surrounded by dummy active regions with equal distance to eliminate any layout-dependent proximity effects                                                                                 |

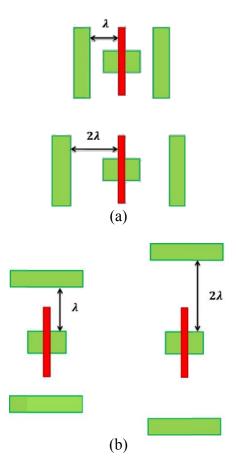

| Figure 2-3 (a) Test structures to monitor the effect of STI-induced stress along the channel direction (lateral) (b) Test structures to monitor the effect of STI-induced stress across the channel direction (vertical) |

| Figure 2-4 (a) Test structures used to study the impact of length of diffusion on transistor performance (b) Test structures with asymmetric source/drain diffusion lengths                                              |

| Figure 2-5 (a) Test structures used to study the impact of proximity to the bottom N-well (b) Test structures to study the impact of proximity to the side                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N-well, away from bottom N-well                                                                                                                                                                                                   |

| Figure 2-6 Test structures comparing continuous vs. segmented channel designs                                                                                                                                                     |

| Figure 2-7 Floor plan for the transistor characterization array consisting of selection circuitry and DUTs                                                                                                                        |

| Figure 2-8 Top-level schematic showing selection circuitry and analog signals25                                                                                                                                                   |

| Figure 2-9 Circuit schematic showing access transistors for row selection and Kelvin Force/Sense configuration                                                                                                                    |

| Figure 2-10 Row selection circuit with $V_{GX}$ biasing for minimizing off-state leakage for an NMOS array                                                                                                                        |

| Figure 2-11 (a) Packaged test chip mounted on the custom-made PCB; coaxial and tri-axial cables are used for delivering analog signals to the chip; (b) Digital signals outputted from DB25 port used to control the scan-chain29 |

| Figure 2-12 (a) Leakage calibration: leakage floor subtracted out from the raw data (b) Higher $I_{on}$ current is observed with Kelvin measurement 31                                                                            |

| Figure 2-13 Boxplot of V <sub>T SAT</sub> of the minimum-sized ( <i>Lg</i> =30 <i>nm</i> ) transistors across various measured FDSOI dies                                                                                         |

| Figure 2-14 Distributions of $V_{TSAT}$ [@ $V_{DS}$ =1 $V$ ]. RVT have nearly Gaussian distributions, but LVT and HVT do not follow a strict normal distribution.                                                                 |

| Figure 2-15 Strong positive correlation shows between $V_{T LIN}$ and $V_{T SAT}$ ; weak correlation between $V_{TSAT}$ and DIBL, negative correlation between $V_{T LIN}$ and DIBL                                               |

| Figure 3-1 Compact Modeling for Statistical Circuit Design Scheme [3-7] 42                                                                                                                                                        |

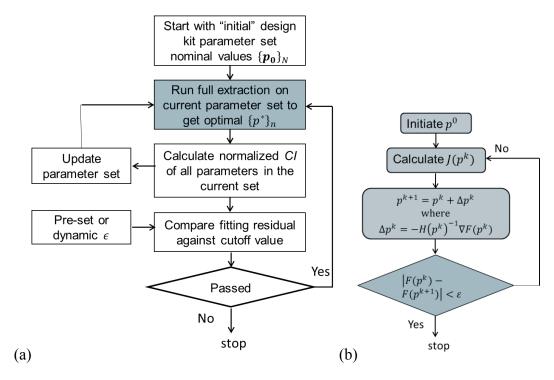

| Figure 3-2 (a) Stepwise compact model parameter selection algorithm (b) Compact model parameter extraction with Newton's method                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

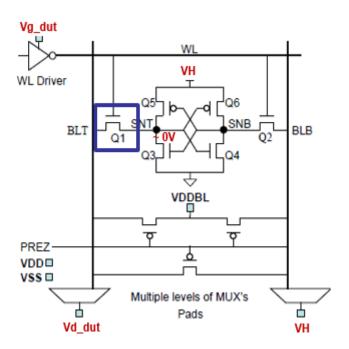

| Figure 4-1 Direct bit transistor access cell pass-gate transistor I-V measurement scheme. [4-7]                                                                                                                                                               |

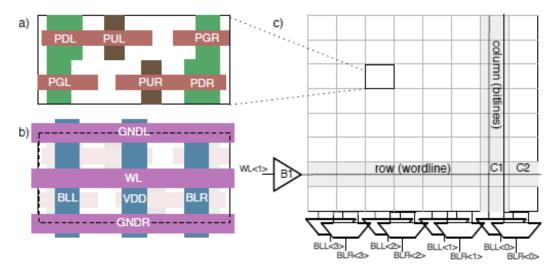

| Figure 4-2 (a) Layout of transistors in a 6T SRAM cell; (b) Layout of metal layers for a 6T SRAM cell (c) Generic overview of SRAM array design [4-10]                                                                                                        |

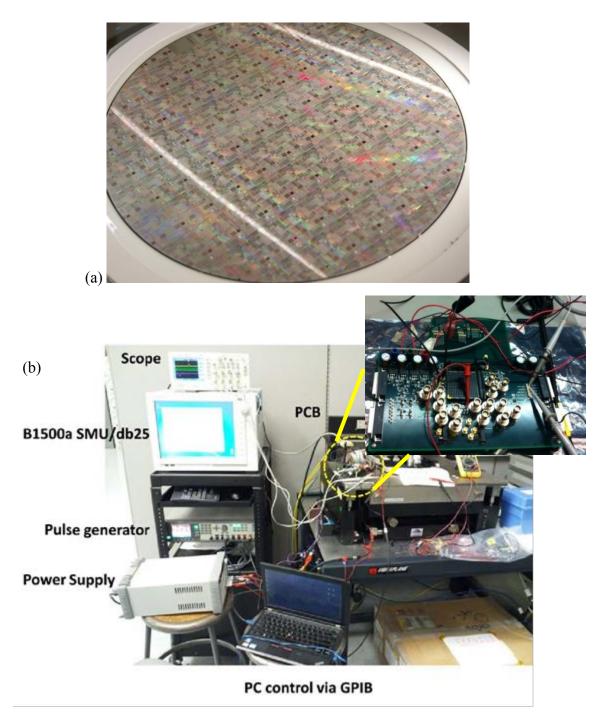

| Figure 4-3 (a) Wafer photo containing multiple dies; (b) Overall test setup consisting of semiconductor parametric analyzer (Agilent B1500A), arbitrary waveform generator, DC power supply, and a laptop computer; enlarged photo of test PCB and die socket |

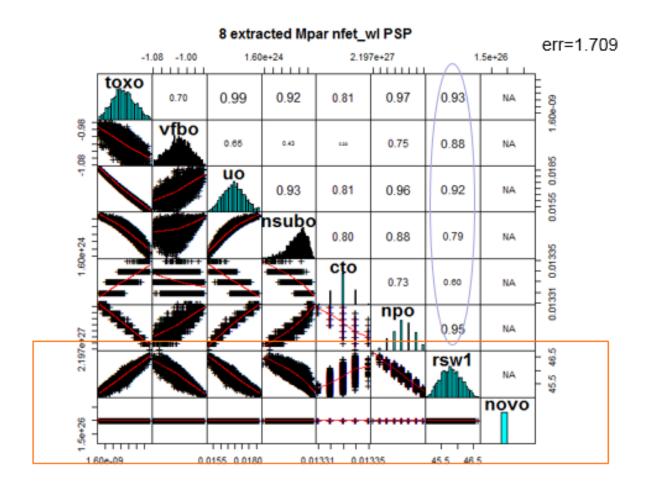

| Figure 4-4 Stepwise parameter selection results with pass-gate I-V data from chip1 on PSP model71                                                                                                                                                             |

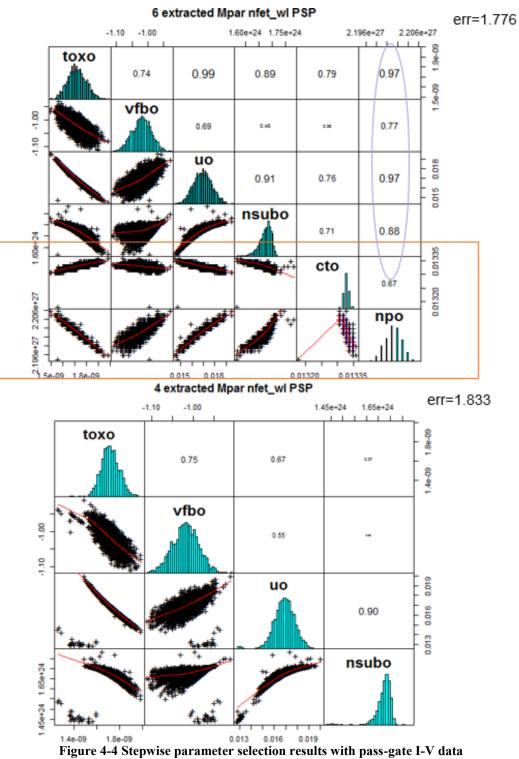

| Figure 4-5 SRAM DC write noise margin BWTV metric Comparison of measurements vs. full standard Monte Carlo simulations vs. customized Monte Carlo simulations using differ reduced set of extracted mode parameters                                           |

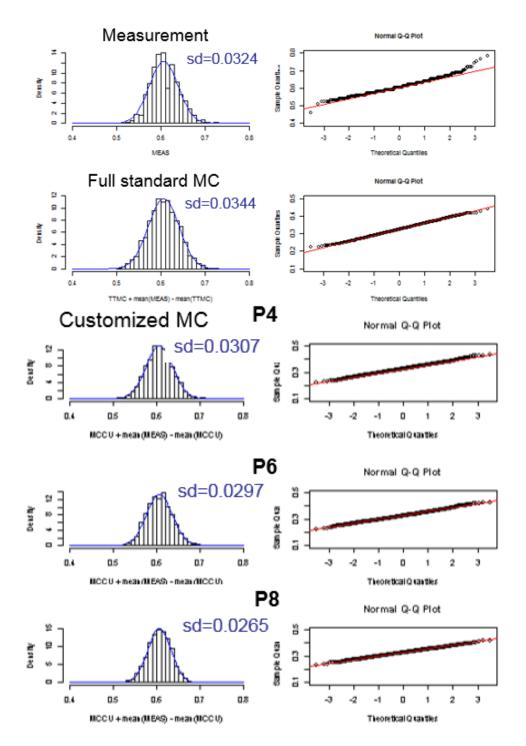

| Figure 4-6 Statistical model parameter extraction results from chip2 data (55 rows and 512 columns) on PSP model, extracted parameter set of {vfbo, uo toxo, nsubo} shows multimodal distribution as well as outliers in the data se                          |

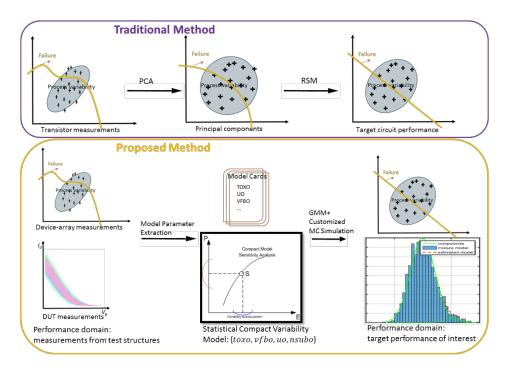

| Figure 5-1 Conceptual illustration of our proposed method79                                                                                                                                                                                                   |

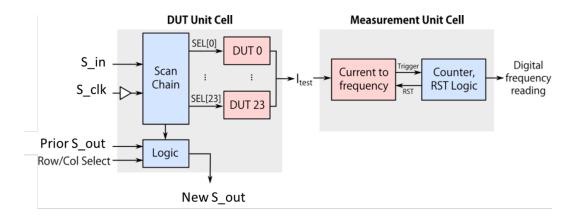

| Figure 5-2 General structure of unit cell pair, containing one device under test (DUT) unit cell (left) and one measurement unit cell (right) [5-6] 81                                                                                                        |

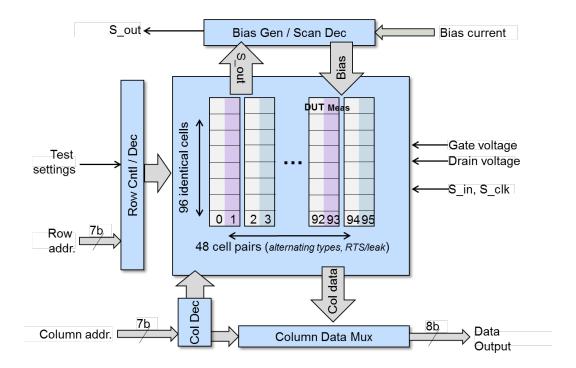

| Figure 5-3 Characterization chip system architecture [5-6] 81                                                                                                                                                                                                 |

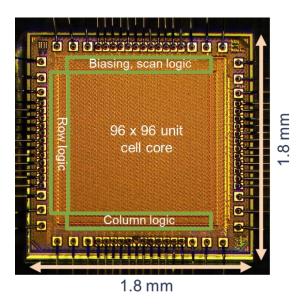

| Figure 5-4 Die photo of the fabricated chip in 28nm bulk process [5-6] 82                                                                                                                                                                                     |

| Figure 5-5 Example of calibration and measurement [5-6]                                                                                                                                                                                                       |

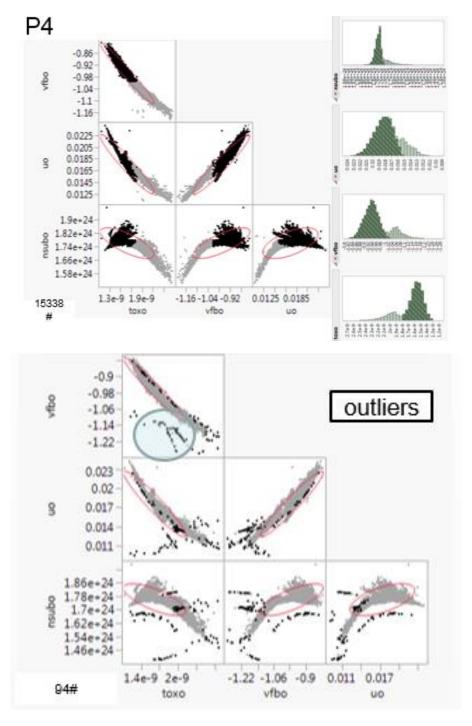

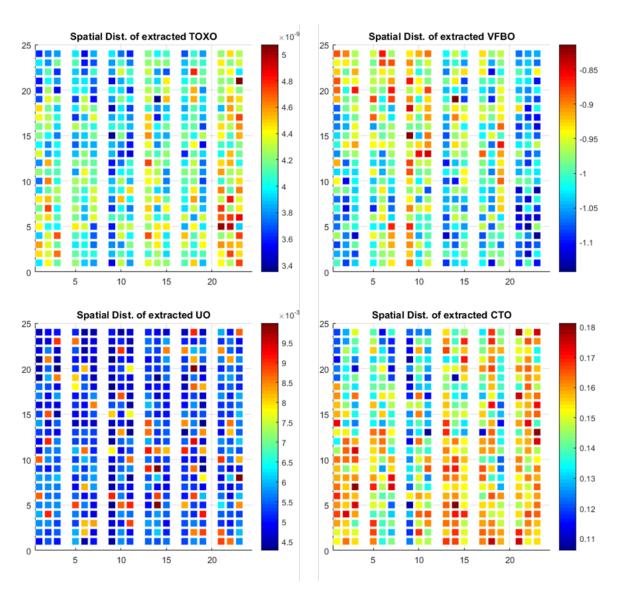

| Figure 5-6 Stepwise parameter selection results with HVT PMOS I-V data from chip3 on PSP model                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5-7 Chip maps of extracted compact model parameters {toxo, vfbo, uo cto};                                                                                                             |

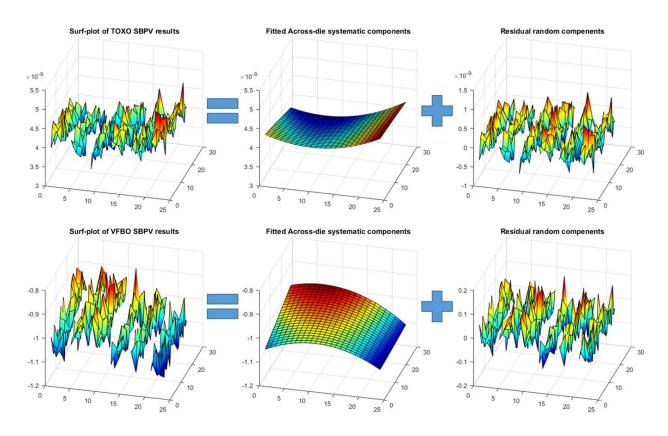

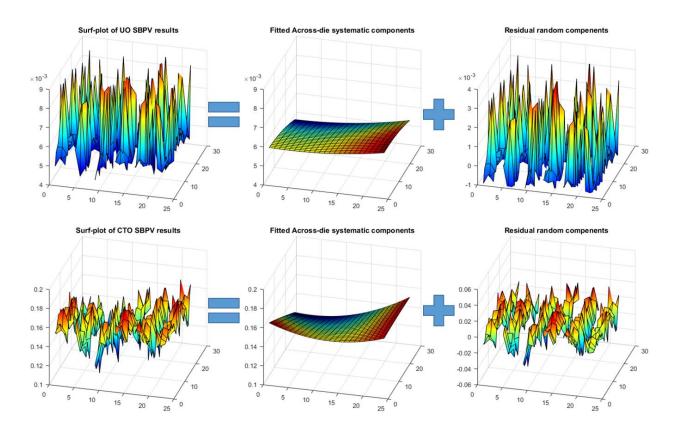

| Figure 5-8 Chip level variation decomposition for <i>{uo, cto}</i> calculated from SBPV method;                                                                                              |

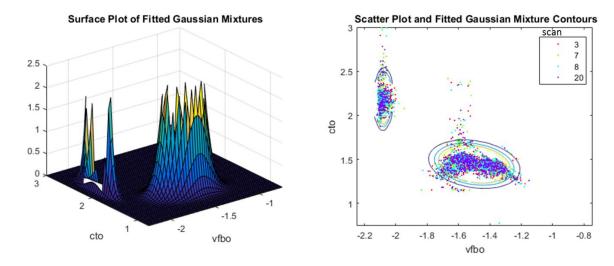

| Figure 5-9 Fitting GMM contours with different number of mixture components on extracted model parameter pair {vfbo, cto} for visualization                                                  |

| Figure 5-10 Surface plot, scatter plot and fitted GMM contours with 2 mixture components on extracted model parameter pair {vfbo, cto} for visualization;                                    |

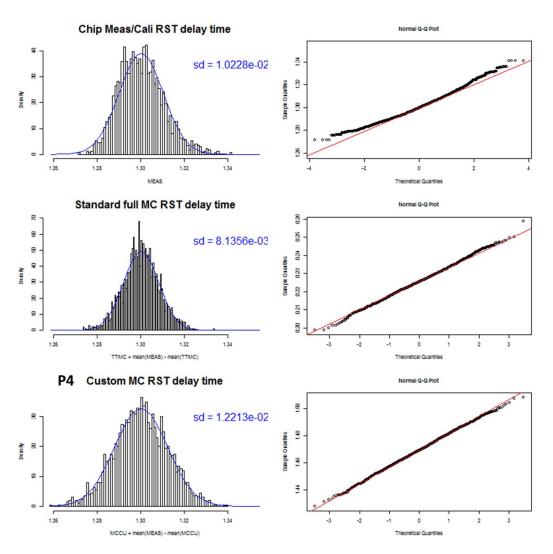

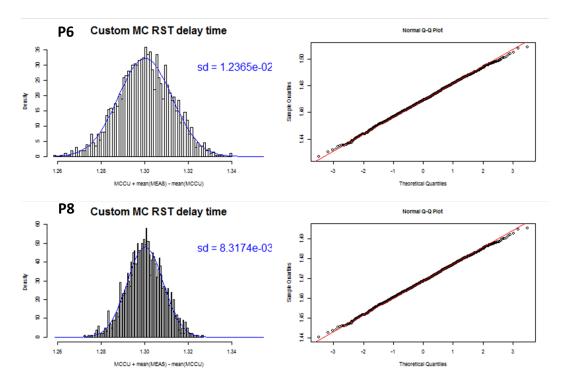

| Figure 5-11 RST critical path delay metric Comparison of measurements vs full standard MC simulations vs. customized MC simulations using differenced uced set of extracted model parameters |

| Figure 5-12 Comparison of measurement, standard full MC and customized MC with GMM models                                                                                                    |

| Table 3-1 EM algorithm to solve GMM maximum likelihood estimation 57                                                                                                                         |

| Table 4-1 Candidates of PSP model parameters for extraction [4-15] 68                                                                                                                        |

| Table 5-1 Summary of DUT types included in the measurement dataset; 85                                                                                                                       |

| Table 5-2 Candidates of PSP model parameters for statistical extraction (excerpt from design kit manual)                                                                                     |

#### Acknowledgments

First, I want to express my deepest and most sincere gratitude to my research advisor, Prof. Costas Spanos, who has provided me with outstanding support in both personal life and research work throughout my years of doctorate study. Costas has been my research advisor for over six years; and I have always found him dependable, inspirational and unfailingly excited about mentoring. His willingness to take on challenging projects like my early-stage design proposals and see them to successful completion has repeatedly impressed me over the years. I also became acutely aware of his great knowledge and skills in guiding me towards better presentation, as well as the endless hours he worked in a determination to help finish my manuscripts before a top conference submission deadline. I cannot imagine accomplishing so much work without his enthusiastic, yet well-organized mentorship.

I am very grateful to Professor Bora Nikolic for collaboration and support in designing, fabricating and measuring the test patterns I used in this work. I enjoyed our research discussions and I learned a lot from you, who sets the standard for how to be a great researcher, to always try to seek insight and intuition behind a problem. I also owe my gratitude to my thesis committee member, Professor Haiyan Huang, for reading my thesis and providing support suggestions each time I have interacted with her.

The majority part of the thesis project is sponsored by the IMPACT+ funding from Applied Materials, ARM, ASML, Global Foundries, IBM, Intel, KLA-Tencor, Mentor Graphics, Panoramic Tech, Qualcomm, Samsung, SanDisk and Tokyo Electron.

I very much appreciate the collaboration and friendship from all my group mates as well as from Berkeley Wireless Research Center (BWRC), present and past: Brian, Katerina and Amy. Kun, thank you for all your noble help. Zhaoyi and Claire, thanks for all the collaboration during class and all the good times. Yu and Qianying, thank you for all the laughs we shared, and all the advice you gave me, academic or non-academic. You made my life here truly fun and enjoyable.

Finally, my family deserves all the credit for this accomplishment, and thank you for your unconditional love. Cuimei and Jinping, you are the best mom and dad one can ever wish for. Thank you for always being there with me to share the cheers during my success and comfort me during my down times. To my husband, Qikai, you have been extremely loving and caring from the time we met and I cannot thank you enough. Without you, my accomplishment here would mean nothing to me. You deserve every part of this thesis as much as I do. Thank you and I love you so much.

## **Chapter 1**

### Introduction

#### 1.1 Motivation: Process Variation

In 1965, Gordon Moore observed that the number of transistors on a single chip doubled every 18 to 24 months [1-1]; this is an observation now widely known as Moore's Law. The perpetual doubling of transistor density has served as the driving force of an astonishing increase in the functionality and computational capability of electronic devices since then hitherto. Between generations, minimum transistor dimensions undergo scaling by a factor of 0.7, enabling the integration of more transistors with less power dissipation. In recent years, however, several bottlenecks have appeared as we continue to scale down beyond sub 28nm technologies. One of the key issues related to deeply scaled semiconductor manufacturing is the yield, defined as the proportion of manufactured circuits that are functional and meet their performance requirements [1-2]. The overall yield loss falls into two major categories: catastrophic yield loss (due to physical and structural defects, e.g., open, short, etc.) and parametric yield loss (due to parametric variations in process parameters, e.g., threshold voltage, stress, etc.). A large portion of yield loss in circuits now occurs due to process variations, which can be defined as the deviations in the manufactured circuit in comparison to its design [1-3].

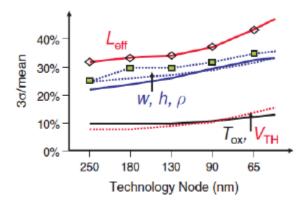

With decreasing transistors sizes and increasing transistor densities, the effect of process and manufacturing variabilities are more significant; meeting performance and yield specifications is increasingly challenging. For example, Figure 1-1 shows the general trend in the ratio between the corresponding  $3\sigma$  variation and mean value for some key technology devices and wire parameters from 250nm to 45nm. Over the time of interest, we see that the proportion of  $L_{eff}$  variation increases from 30% to 45%. Wire geometry parameters - width W, height H and resistivity  $\rho$  - also undergo significant increases. Other parameters such as the threshold voltage  $V_{th}$  and oxide thickness  $T_{ox}$  increase at a lower rate.

Figure 1-1 Increase of process variability in conventional scaled MOS technology [1-2]

Increasing process variations introduce significant uncertainty for both circuit performance and leakage power. It has been shown in that even for the 180nm technology, process variation can lead to 1.3X variation in frequency and 20X variation in leakage power [1-4]. In future technology generations, such an impact will become more magnified because the technology is approaching a fundamental randomness regime in the behavior of silicon structures. In recent years, Design for Manufacturability (DFM) methods, including attempts to reduce the systematic sources of variability, statistical modeling, extraction, and optimization for VLSI circuits, have been developed to alleviate the variation effects. For DFM to be meaningful, however, variability needs to be characterized empirically for a specific semiconductor process to obtain a quantitative understanding of variability mechanisms. Such "statistical metrology" methods

include measurement techniques for the characterization of variabilities, and statistical modeling and extraction methods for properly interpreting measurement results.

### 1.2 Background

Background knowledge about advanced transistor structures, sources of variability and test structures for variability characterization is necessary to understand the motivation and context behind the following chapters in this work.

#### 1.2.1 Advanced Transistor Structures

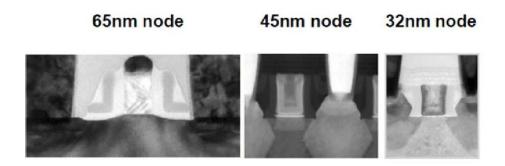

To achieve a higher transistor density on a chip, the dimensions of a transistor must be scaled. Constant field scaling - where device dimension, doping density, and supply voltages are scaled simultaneously - has worked for a while, but it has started to slow down dramatically when the minimum half-pitch reached 90nm [1-5]. Figure 1-2 shows a series of transmission electron microscopy (TEM) images of classical planar bulk MOSFET from the 65nm technology node down to the 32nm technology node [1-6]. Here, gate leakage due to the thin layer of gate oxide (SiO<sub>2</sub>) can be mitigated by using a high-permittivity (high-k) dielectric and metal gate (HKMG) stack [1-8]. As the gate length of a transistor is made smaller, non-ideal effects, which are negligible at long gate lengths, can degrade transistor performance. These effects are usually referred to as short-channel effects (SCEs) [1-9].

Figure 1-2 TEM cross-sections of MOSFETs at various technology nodes, with approximately the same scale [1-7]

Short-channel effects can become very difficult to suppress in a planar bulk transistor for gate lengths below 25nm. Therefore, to allow further miniaturization, advanced transistor structures employing thin-body regions such as the fully depleted silicon-on-insulator (FD-SOI) [1-10] and the three-dimensional FinFET have been developed for future generations of CMOS technology [1-11].

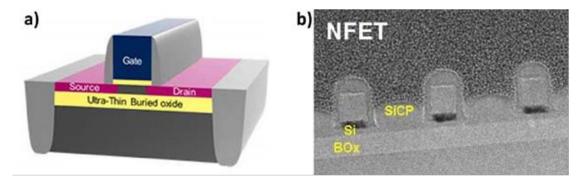

A FD-SOI MOSFET is a planar structure that is fabricated in a thin *Si* layer on top of a buried oxide (BOX) layer. An illustration of the FD-SOI MOSFET structure is shown in Figure 1-3(a) and a TEM cross-section is shown in Figure 1-3(b). Electrostatic gate control in the FD-SOI MOSFET is superior to that in a planar bulk MOFSET due to its thin silicon body, since OFF-state leakage current paths far away from the gate are eliminated [1-13]. Because of the minimal differences between FD-SOI and planar bulk MOSFETs, few changes are needed to migrate circuit designs from bulk to FD-SOI.

Figure 1-3 (a) 3D view of a planar FD-SOI transistor [1-12]; (b) A TEM cross-section of N-channel FD-SOI transistors [1-13].

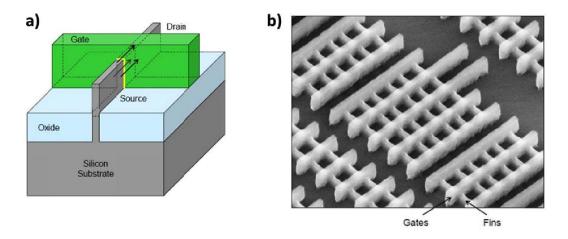

Another variation of a thin-body MOSFET is the vertical FinFET, where the body has a fin-like shape and a gate electrode straddles it, as depicted in Figure 1-4. Due to gating from all three sides of the channel, SCE can be well suppressed if the fin width is less than half the gate length ( $W_{Si} \sim L_g/2$ ). Experimental results have demonstrated FinFET transfer characteristics with low sub-threshold swing and low drain-induced barrier lowering (DIBL) [1-10]. Recently, the FinFET has supplanted the planar bulk MOSFET in the most advanced microprocessor chips at leading semiconductor foundries.

Figure 1-4 (a) 3D view of a vertical FinFET transistor; (b) TEM image of an array of FinFET transistors showing the fin and gate features [1-14].

#### 1.2.2 Sources of Variation

Sources of transistor variation caused by an imperfect manufacturing process are often categorized as either systematic or random. Systematic (or global) variations, dependent on the layout of the transistors and its surroundings, affect all devices on the same die, wafer, or lot; this causes devices of different physical hierarchies or locations to have different drive current versus gate voltage characteristics. Random (or local) variation, on the other hand, can result in differences between identically drawn transistors within the same layout environment, reducing matching in analog differential pairs or proportionally sized devices in SRAM cells. As the critical dimension decreases with technology advancements, the contributions of different physical sources of variation such as random dopant fluctuations (RDF) or line edge roughness (LER) change [1-15].

RDF is caused by variations in the number and placement of dopant atoms in the channel region of the transistor. The small number of dopant atoms makes the threshold voltage susceptible to even the slightest amount of dopant variation. Reducing device dimensions and increasing doping density will result in a larger  $V_{th}$  variation. Conversely, by reducing the effective thickness of the gate oxide (e.g. by adopting a high-k dielectric),  $\sigma_{V_{th}}$  can be reduced. A more detailed analysis of  $V_{th}$  variations due to RDF can be performed through 3D device simulations, which randomly place dopant atoms within the transistor [1-16].

The gate length, aka critical dimension (CD) of the transistor becomes so small that a slight deviation from the nominal value can have a large effect on electrical performance. LER, one of the main contributors to random variation in CD, is caused by the granularity of the photoresist material (used to define the pattern of the gate electrodes) at the molecular level [1-17]. As the CD decreases, LER does not decrease commensurately, which can result in large  $V_{th}$  variations [1-18]. LER can affect both the gate length and channel width of a transistor as depicted in Figure 1-5(a). With a more advanced structure like the FinFET, fin width variations caused by LER is also becoming a major concern. Characterization of LER can be done efficiently by analyzing the top view of the scanning electron microscope (SEM) image of the feature as in Figure 1-5(b) [1-19].

Figure 1-5 (a) Top view showing how LER can affect the gate length and channel width of a transistor; (b) SEM image of a photoresist line with LER [1-19].

When we analyze the scaling factors of the recent technology nodes, we come to the conclusion that the electrical characterization of these really challenging technologies becomes an absolute must. However, the extremely small process windows, and the 3-dimensional nature of the FinFET devices and the complicated interconnect schemes, make this characterization very difficult [1-20]. As FinFETs emerging to be the solution for short channel effects, fin shape significantly impacts transistor leakage in bulk tri-gate nFinFETs with thin fins when the fin body doping profile is optimized to minimize leakage [1-21]. With appropriate doping optimization, a 22-nm nFinFET with triangular fin cross section results in an ineligible reduction in leakage current over a rectangular fin with the same base fin width [1-21].

#### 1.2.3 Test Structures for Variation Characterization

To improve our understanding of process variation and ultimately reduce this variation to improve yield, process variation needs to be thoroughly characterized with the help of on-chip test structures. The test structures are devices or circuits that are added onto a wafer to help control, understand, and model the behavior of MOSFETs. Per the objective of measurements, test structures fall into two classes: (a) test structures for process control, and (b) test structures for modeling [1-2].

Test structures for process control are used for monitoring and controlling the fabrication line. These are typically small devices or circuits placed in the scribe line on all wafers and therefore can model the history of the line. Monitors often consist of simple test structures that allow the measurements of current-voltage (I~V) characteristics of MOSFETs [1-22], of the resistivity of wires and vias [1-23], and of interconnect capacitance [1-24].

It is important to extract physically meaningful model parameters, as they help to identify possible root causes for process failures, and help drive optimization of the process in early stage process development. The difficulty of this problem comes from the fact that measurements are collected from a limited number of early prototype devices rather than from a full suite of designed test structures. Test structures for modeling are used to generate the fundamental data needed to create models of the fabricated components. These test structures are complex in nature and are typically designed to be sensitive to a specific physical parameter. Therefore, a much richer variety of test structures is needed for modeling purposes.

Prior comprehensive test structures of variability studies have previously been published for 45nm [1-25] CMOS, but only limited variability information is available for technology nodes at 28nm and below. Moreover, prior experimental work has focused on addressable device arrays with analog switches that require long design times and cumbersome testing setups with separate bench supplies for each device terminal [1-26]. To address this issue, some prior work [1-27] has demonstrated custom technology characterization chips with fully digital interfaces, including a complete current vs. voltage (*I-V*) characterization chip with an integrated digital to analog converter (DAC) and analog to digital converter (ADC).

### 1.3 Thesis Organization

In this thesis we propose accurate and efficient statistical techniques to solve the following problem in DFM: given hands-on knowledge of the test chip design and the measurements of one or several functions (e.g., transistor *I-V* measurements), we need to find the value of transistor compact model parameters (such as parameters sensitive to process variation) to predict circuit performance and to eventually improve product yield.

In Chapter 2, the design of a test chip to study the impact of transistor variation in 28nm planar bulk and FD-SOI MOSFETs is discussed. A device characterization array including transistors in mismatch pairs and different layout proximities are used to study the impact of random and systematic variation respectively. Measurement setup is documented in detail, and transistor variation observation and characterization limitations are discussed.

In Chapter 3, we establish the background for statistical compact variability modeling. We propose a general parameter extraction method to enable the extraction of an entire set of MOSFET *I-V* model parameters, even in the face of few or missing *I-V* measurements in the data set. Our improved method for modeling the variability of transistors with compact models works seamlessly with the widely-used PSP model for efficient statistical circuit performance estimation.

In Chapter 4, we apply the statistical compact model extraction methodology to the actual silicon data collected from the SRAM bit cells on the 28nm test chip. For the foundry-wrapped PSP model, stepwise parameter selection is applied to find an optimal set of model parameters, from which the measurement data is characterized to create a custom statistical compact model. These statistical compact models provide better accuracies in predicting bit-cell static performance variations than conventional methods.

Chapter 5 demonstrates the full statistical device characterization and circuit performance modeling on the imaging ROIC test array measurement data. With a larger dataset including chip spatial info, we can apply the linear spatial backward propagation of variance method for compact model parameters. Furthermore, a mixture of Gaussian model can be applied onto non-Gaussian correlated model parameters for better circuit performance statistical modeling. Results are shown in detail in this chapter.

Chapter 6 concludes the thesis. We summarize the key contributions of the thesis. With challenges in the analysis of process variation ahead, areas for future

10

research are suggested, including variation prediction within a process development cycle.

#### References

- [1-1] G. Moore, "Cramming more components onto integrated circuits," Proceedings of the IEEE, vol. 86, no. 2, pp. 82-85, 1998.

- [1-2] M. Orshansky, S. Nassif, and D. Boning, Design for Manufacturability and Statistical Design: A Constructive Approach. Springer, 2010.

- [1-3] W. Zhang, "IC spatial variation modeling: Algorithms and applications," Ph.D. dissertation, Carnegie Mellon University, Department of Electrical Engineering, 2012.

- [1-4] S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, "Parameter variations and impact on circuits and microarchitecture," in Design Automation Conference (DAC), June 2003, pp. 338-342.

- [1-5] W. Arden, M. Brillouet, P. Cogez, M. Graef, B. Huizing, R. Mahnkopf, "Morethan-Moore White Paper," ITRS 2010. Available:

- [1-6] S. Yang, L. G. Lin, M. Han, D. Yang, J. Wang, K. Mahmood, T. Song, D. Yuan, D. Seo, M. Pedrali-Noy, D. Alladi, S. Wadhwa, X. Bai, L. Dai, S. S. Yoon, E. Terzioglu, S. Bazarjani, G. Yeap, "High Performance Mobile SoC Design and Technology Co-Optimization to Mitigate High-K Metal Gate Process Induced Variations" in VLSI Symp. Tech. Dig., 2014.

- [1-7] V. Moroz, "Transition from Planar MOSFETs to FinFETs and its Impact on Design and Variability", Berkeley Seminar, Oct. 2011.

- [1-8] T. Ghani, M. Armstrong, C. Auth, M. Bost, P. Charvat, G. Glass, T. Hoffmann, K. Johnson, C. Kenyon, J. Klaus, B. McIntyre, K. Mistry, A. Murthy, J. Sandford, M. Silberstein, S. Sivakumar, P. Smith, K. Zawadzki, S. Thompson, M. Bohr, "A 90nm High Volume Manufacturing Logic Technology Featuring Novel 45nm Gate Length Strained Silicon CMOS Transistors," IEDM Tech. Dig., 2003.

- [1-9] Y. Taur; D. A. Buchanan; W. Chen; D.J. Frank; K.E. Ismail; L. Shih-Hsien; G.A, Sai-Halasz; R.G. Viswanathan; H.-J.C. Wann; S.J. Wind; Hon-Sum Wong, "*CMOS scaling into the nanometer regime*," Proceedings of the IEEE, vol.85, no.4, pp.486,504, Apr 1997.

- [1-10] C. Auth; C. Allen; A. Blattner; D. Bergstrom; M. Brazier; M. Bost; M. Buehler; V. Chikarmane; T. Ghani; T. Glassman; R. Grover; W. Han; D. Hanken; M. Hattendorf; P. Hentges; R. Heussner; J. Hicks; D. Ingerly; P. Jain; S. Jaloviar; R.James; D. Jones; J. Jopling; S. Joshi; C. Kenyon; H. Liu; R. McFadden; B.Mcintyre; J. Neirynck; C. Parker; L. Pipes; I. Post; S.

- Pradhan; M. Prince; S.Ramey; T. Reynolds; J. Roesler; J. Sandford; J. Seiple; P. Smith; C. Thomas; D.Towner; T. Troeger; C. Weber; P. Yashar; K. Zawadzki; K. Mistry, "A 22nm high performance and low-power CMOS technology featuring fully-depleted trigate transistors, self-aligned contacts and high density MIM capacitors," VLSI Technology (VLSIT), 2012 Symposium on , pp.131,132, 12-14 June 2012.

- [1-11] W. Shien-Yang; C,Y, Lin; M.C. Chiang; J.J. Liaw; J.Y. Cheng; S.H. Yang; M. Liang; T. Miyashita; C.H. Tsai; B.C. Hsu; H.Y. Chen; T. Yamamoto; S.Y. Chang; V.S. Chang; C.H. Chang; J.H. Chen; H.F. Chen; K.C. Ting; Y.K. Wu; K.H. Pan; R.F. Tsui; C.H. Yao; P.R. Chang; H.M. Lien; T.L. Lee; H.M. Lee; W. Chang; T. Chang; R. Chen; M. Yeh; C.C. Chen; Y.H. Chiu; Y.H. Chen; H.C. Huang; Y.C. Lu; C.W. Chang; M.H. Tsai; C.C. Liu; K.S. Chen; C.C. Kuo; H.T. Lin; S.M. Jang; Y. Ku, "A 16nm FinFET CMOS technology for mobile SoC and computing applications," Electron Devices Meeting (IEDM), 2013 IEEE International, pp.9.1.1,9.1.4, 9-11 Dec. 2013

- [1-12] ST Microelectronics. <a href="http://www.st.com/web/en/about\_st/fd-soi.html">http://www.st.com/web/en/about\_st/fd-soi.html</a>

- [1-13] L. Le Pailleur, "28nm FD-SOI Industrial Solution: Overview of Silicon Proven Key Benefits" FDSOI- Workshop 2013 Kyoto, Japan.

- [1-14] M. Bohr, K. Mistry, "Intel's Revolutionary 22 nm Transistor Technology," Intel Presentation, May 2011.

- [1-15] K. Kuhn, M. Giles, D. Becher, P. Kolar, A. Kornfeld, R. Kotlyar, S. Ma, A. Maheshwari, and S. Mudanai, "*Process Technology Variation*," Electron Devices, IEEE Transactions on, vol. 58, pp. 2197-2208, Aug 2011.

- [1-16] K. Takeuchi, A. Nishida, T. Hiramoto, "Random Fluctuations in Scaled MOS Devices," Simulation of Semiconductor Processes and Devices, 2009. SISPAD '09. International Conference on, vol., no., pp.1,7, 9-11 Sept. 2009

- [1-17] Y. Ma; H. J. Levinson; T. Wallow, "Line edge roughness impact on critical dimension variation," Proc. SPIE 6518, Metrology, Inspection, and Process Control for Microlithography XXI, 651824 (April 05, 2007)

- [1-18] A. Asenov, "Simulation of statistical variability in nano MOSFETs," IEEE Symp. VLSI Technol., Dig. Tech. Papers, Jun. 2007, pp. 86–87.

- [1-19] A. Hiraiwa, A. Nishida, "Statistical- and image-noise effects on experimental spectrum of line-edge and line-width roughness," J. Micro/Nanolith. MEMS MOEMS, Dec. 2010.

- [1-20] Andrzej J. Strojwas; Jacob Abraham; Hong Hao; Max Shulaker, "Challenges and opportunities in electrical characterization and test for 14nm and below", 2016 IEEE 34th VLSI Test Symposium (VTS), 2016.

- [1-21] B. D. Gaynor and S. Hassoun, "Fin Shape Impact on FinFET Leakage With Application to Multithreshold and Ultralow-Leakage FinFET Design," in IEEE Transactions on Electron Devices, vol. 61, no. 8, pp. 2738-2744, Aug. 2014.

- [1-22] C. Hess, A. Inani, Y. Lin, M. Squicciarini, R. Lindley, and N. Akiya, "Scribe characterization vehicle test chip for ultra-fast product wafer yield monitoring," in Microelectronic Test Structures, 2006. ICMTS 2006. IEEE International Conference on, Mar. 2006, pp. 110-115.

- [1-23] L. W. Linholm, R. A. Allen, and M. W. Cresswell, "Microelectronic test structures for feature placement and electrical linewidth metrology," in Handbook of Critical Dimension Metrology and Process Control. New York: SPIE Optical Engineering Express, 1994, vol. CR52, pp. 91 118.

- [1-24] J. Chen, D. Sylvester, and C. Hu, "An on-chip, interconnect capacitance characterization method with sub-femto-farad resolution," IEEE Transactions on Semiconductor Manufacturing, vol. 11, no. 2, pp. 204-210, May 1998.

- [1-25] S. Realov and K. Shepard, "On-chip combined C-V / I-V characterization system in 45-nm CMOS technology," IEEE Journal of Solid-State Circuits, vol. 48, 2013.

- [1-26] S. Saxena, "Variation in transistor performance and leakage in nanometer-scale technologies," IEEE Transactions on Electron Devices, vol. 55, 2008.

- [1-27] S. Realov, W. McLaughlin, and K. Shepard, "On-chip transistor characterization arrays with digital interfaces for variability characterization," International Symposium on Quality Electronic Design, 2009.

## Chapter 2

### Variability Characterization Test Structures

#### 2.1 Introduction

To satisfy Moore's Law, transistors are miniaturized in each successive technology node so that more of them can be put onto a chip [2-1]. However, such aggressive scaling can also have an adverse effect on the electrostatic integrity of a transistor, causing large off-state current and worsening short-channel effects. One of the root causes of poor electrostatic control is relatively weak capacitive gate coupling to the electric potential in the silicon body region that is further from the gate-oxide interface [2-2]. To tackle this challenge head on, one can think of removing all paths far away from the gate, which is precisely the idea behind the thin-body (fully depleted) MOSFET [2-3]. If the thickness of the silicon body is made much thinner than the gate length, short-channel effects are dramatically reduced. The two most common implementations of a thin-body MOSFET today are the vertical FinFET or planar FDSOI (Fully-Depleted Silicon-On-Insulator) MOSFET [2-4].

The FinFET is a double-gate MOSFET structure, which is more scalable compared to the FDSOI MOSFET due to superior gate control. However, it requires a high aspect ratio Si fin geometry, which presents a major challenge

from a fabrication standpoint. Additionally, since the drive strength of a FinFET is adjusted by changing the number of fins, circuit designers must cope with discrete adjustments in the drive current for FinFETs [2-5]. On the other hand, the FD-SOI MOSFET structure, which also uses a thin body like the FinFET, offers improved electrostatic control over the planar bulk MOSFET without adding significant fabrication challenges or imposing new restrictions on circuit design. Instead of a bulk Si wafer, the starting substrate is a Silicon-On-Insulator (SOI) wafer [2-6]. The device fabrication process steps are very similar and less complicated compared to those of a standard planar bulk Si device fabrication process. From a circuit designer's standpoint, the FDSOI design kit is also easier to adapt from that of bulk Si technology: device widths can be adjusted to tune transistor drive strength, and back-biasing can be used to dynamically adjust transistor threshold voltage [2-7].

Given that FDSOI technology is a promising candidate to replace planar bulk Si technology, variability analysis of FDSOI MOSFETs is necessary. This can be achieved by implementing a device characterization array in a test chip.

### 2.2 Transistor Characterization Array Design

To capture and understand the impact of different variability sources on device performance, transistors of different sizes and layout geometries are included in the transistor characterization array. Using built-in circuitry on the chip, each individual transistor can be electrically accessed and characterized through the input/output pads. In general, the variability test structures can be classified as *random* or *systemic* variability test structures. Both NMOS and PMOS transistors of different threshold values are included. Test chips were fabricated by STMicroelectronics using a 28nm high-k/metal-gate (HKMG) process, on both bulk-Si and SOI substrates to allow for a direct comparison of planar bulk vs. FDSOI technologies. The layout of the transistor characterization block is shown in Figure 2-1.

Figure 2-1 (a) Layout of transistors characterization block and DUT (b) Photo of a die under test with probe tips landed on top; magnified photo of the die showing the macro on the bottom row.

#### 2.2.1 Random Variability Test Structures

Random variability sources such as random dopant fluctuations (RDF), gate work function variation (WFV), and line-edge roughness (LER) can contribute to variations in  $V_{th}$ ,  $I_{OFF}$ , and  $I_{ON}$  between devices with identical layouts. To isolate the impact of random variability from that of systematic variability, transistor pairs (i.e. mismatch test structures) are often used. These test transistors are identically drawn structures that are placed near one another on the chip. If there were a systematic source of variability, its impact would be the same for both devices. Thus, when the difference (as opposed to the absolute value) of the performance parameters between the two transistors in a pair is analyzed, the impact due to systematic variability will cancel out, i.e. the difference will entirely be caused by random variability. To ensure that the transistors in a pair are identical in every possible aspect, it is important to make sure that the surrounding area is the same for both transistors. Figure 2-2 shows a Device-Under-Test (DUT) surrounded by dummy active regions. The other corresponding DUT in the pair is also drawn in a similar manner. Such a layout will help to eliminate variability that might arise from layout-dependent proximity effects such as mechanical stress from Shallow Trench Isolation (STI) or near-by active devices [2-8].

Figure 2-2 Layout showing DUT surrounded by dummy active regions with equal distance to eliminate any layout-dependent proximity effects

It has been theoretically derived and experimentally validated that variability in MOSFET threshold voltage increases as the transistor channel dimensions are made smaller. Specifically, the variation of MOSFET threshold voltages is proportional to transistor channel dimensions [2-9]. Thus, devices with different channel area values are included in the array to assess the significance of this trend. To further examine the sensitivity of variability sources to various transistor design parameters (e.g. channel width and gate length), different combinations of W and L corresponding to a fixed channel area are also included. This allows us to decouple different variation sources affecting the transistor threshold voltage.

For System-On-Chip (SOC) products, multiple values of  $V_{th}$  must be available to the designers [1-1]. Therefore, it is also important to investigate how variability will affect transistors of different nominal  $V_{th}$  values. To this end, three different  $V_{th}$  levels (Low, Regular, and High  $V_{th}$ ) are included for each value of width/length combinations.

#### 2.2.2 Systematic Variability Test Structures

In addition to transistor structures used to study random variability, several device structures are included to assist with the study of systematic variability associated with layout proximity effects, including mechanical stress induced by STI, Length of Diffusion (LOD), well doping proximity, and segmented channel design. The design and layout of these structures are summarized in the following sections.

#### 2.2.2.1 Shallow Trench Isolation (STI) Effect

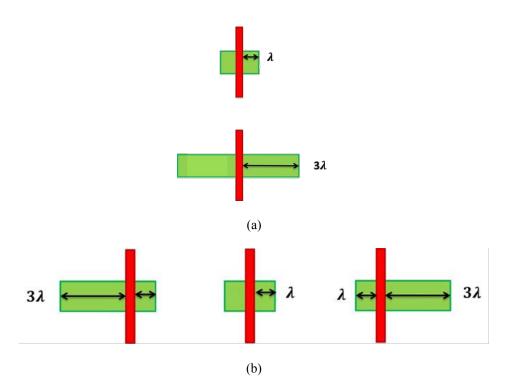

Mechanical stress induced by STI can affect carrier mobility and thereby transistor on-state drive currents [2-11]. To quantify the impact of STI-induced stress from different directions, dummy active regions are drawn at different distances ( $\lambda$ ) away from the device under test. Similarly, the effect of STI-induced stress across the channel (along the width direction) can also be captured by placing the dummy active regions at the top and bottom of a DUT at different distances as depicted in Figure 2-3.

Figure 2-3 (a) Test structures to monitor the effect of STI-induced stress along the channel direction (lateral) (b) Test structures to monitor the effect of STI-induced stress across the channel direction (vertical)

#### 2.2.2.2 Length of Diffusion Effect

The stress profile within the channel region of the DUT also depends on the length of the diffusion (LOD) or source/drain regions of the transistor. To study the impact of LOD on device performances, transistors with the same gate length  $L_g$  and channel width W are drawn with different diffusion lengths at  $\lambda$ ,  $3\lambda$ ,  $4\lambda$ , and  $5\lambda$  for both the source and the drain sides, as shown in Figure 2-4(a).

In addition to devices having equal source/drain diffusion lengths, the LOD of a DUT can also be asymmetric (e.g. source-side LOD is longer than drain-side LOD), as illustrated in Figure 2-4(b). This test structure can be used to decouple the impacts of source-side LOD vs. drain-side LOD, permitting a close examination of parameters that are sensitive to S/D asymmetry such as  $V_{TSAT}$  and source-injection velocity.

Figure 2-4 (a) Test structures used to study the impact of length of diffusion on transistor performance (b) Test structures with asymmetric source/drain diffusion lengths

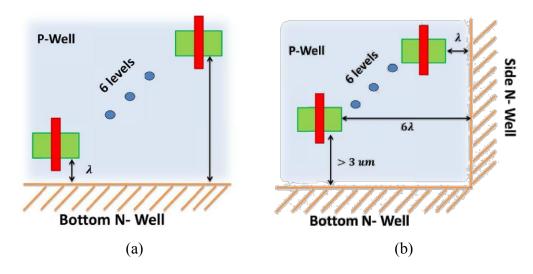

#### 2.2.2.3 Well Proximity Effect

In a planar bulk CMOS technology, NMOS and PMOS transistors are placed inside P-well and N-well regions, respectively [2-12][2-13]. In FD-SOI CMOS technology, the doping type underneath the isolating buried oxide (BOX) layer can be adjusted to achieve the desired  $V_{th}$  specification, for both NMOS and PMOS transistors. Due to lateral straggle of implanted dopant atoms, the doping concentration within the well region of the DUT can be affected if it is situated close to the boundary between the N-well and the P-well. To investigate this effect, test structures shown in Figure 2-5 are used, wherein the DUTs are placed at different distances away from the boundary of the well doping, laterally as well as vertically. In order to isolate the well proximity effect from a particular direction, transistors are placed at least  $3\mu m$  away from that particular well boundary.

Figure 2-5 (a) Test structures used to study the impact of proximity to the bottom N-well (b) Test structures to study the impact of proximity to the side N-well, away from bottom N-well

#### 2.2.2.4 Segmented Channel Transistors

Instead of a transistor having a continuous width, the channel region can be segmented into multiple stripes of equal width as shown in Figure 2-6. From an electrostatic control standpoint, a segmented channel transistor can offer improved short-channel effect due to the slight wrap-around of the gate over the channel and the gate fringing electric field coupling to the channel region through the STI [2-14], if the stripe width is comparable to the channel length. Thus, even though the segmented channel design takes up more layout area as compared to a conventional channel design, the improvement in transistor performance can provide a net benefit when normalized to the same layout area. To observe the greatest benefit of the segmented channel design, the minimum drawn device width is used for each channel segment.

Figure 2-6 Test structures comparing continuous vs. segmented channel designs

# 2.3 Transistor Array Test Setup and Measurement

## **2.3.1** Test Circuitry

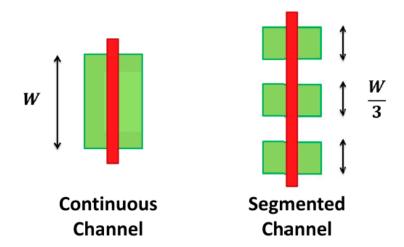

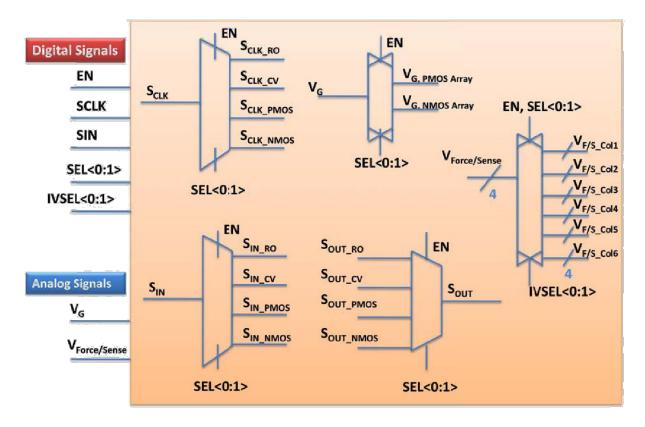

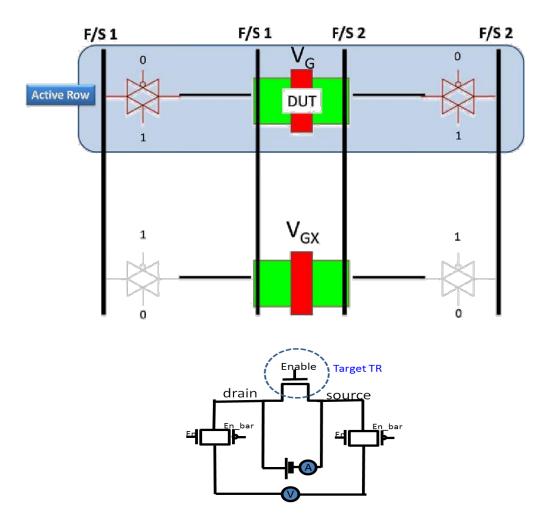

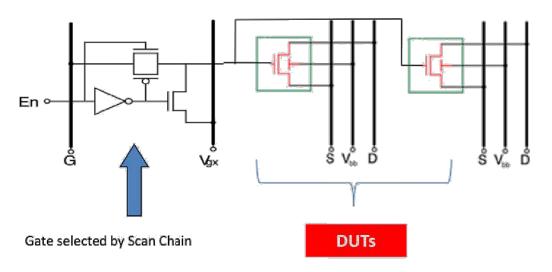

Transistor characterization arrays allow for many test devices of different designs to be included on a single die. Usually, these test devices are not directly probed due to the limited die area. Therefore, electrical access to individual devices in the array is made through the I/O pads of the test chip. Since the number of I/O pads is limited and must be sufficiently allocated for all the signals in different test blocks, a decoder circuit is used to share some common digital signals such as scan-in (SIN), scan-out (SOUT), and scan-clock (SCLK). The decoder is controlled by a 2-bit signal used to select one of the 4 modules within the array, and only one of the modules is active at any given time. Additionally, an enable signal (EN) for transistor characterization is also included. The floor plan of the characterization array is shown in Figure 2-7. There are 6 columns each in the PMOS and NMOS modules: mismatch pair transistors of RVT, LVT and HVT flavors each take up two columns. The digital signals and the selection circuitry are summarized in Figure 2-8.

# IV Test

Figure 2-7 Floor plan for the transistor characterization array consisting of selection circuitry and DUTs

Figure 2-8 Top-level schematic showing selection circuitry and analog signals

Transistors within an array are accessed in a serial manner, in a row-wise fashion using a scan-chain circuit. A simple scan-chain circuit comprised of D flip-flops (D-FF) chained together can be used to activate/deactivate the row under test. A column can be selected through a column multiplexer that has a 3-bit control signal, allowing one out of the six columns to be selected at a given time. The source and drain of devices in the same column share electrical lines. With a combination of row select (through scan-chain clocking) and column select (through multiplexer), each individual transistor inside the array can be accessed, allowing full control over the biasing of the source, drain, and gate terminals through the I/O pads.

Figure 2-9 Circuit schematic showing access transistors for row selection and Kelvin Force/Sense configuration

Analog signal lines used to apply voltage to and measure current from the terminals of the DUT are routed through a series of pass-gates. Due to parasitic resistance along the wire trace from the probe pad to the DUT, the voltage applied to the device's terminals is smaller than the nominal voltage. This voltage difference can be significant if the resistance along the wire is large. To circumvent this problem, the Kelvin measurement technique - utilizing separate sets of Force and Sense lines - is implemented for the source and drain terminals

of the DUT [2-15]. Figure 2-9 shows the basic Kelvin measurement configuration for the source and drain terminals. The current is passed through the Force lines and the voltage drop across the DUT is sensed across the Sense lines. The access transistors which are used to connect the force lines to the device in a row must be large enough to support the current level of the DUT, but small enough such that they will not have a large off-state leakage current. Due to the high impedance associated with the sense line (like the impedance of a voltage meter), very low parasitic current can flow through it.

Leakage control is also important in this type of transistor characterization array. Since only one active device is to be characterized at a time, the leakage current from the other devices in the same column should be as small as possible. To this end, a separate gate bias voltage (VGX) is applied to turn off the transistors that are not being tested. Figure 2-10 shows the schematic of the leakage control circuit.

Figure 2-10 Row selection circuit with  $V_{GX}$  biasing for minimizing off-state leakage for an NMOS array

# 2.3.2 Measurement Setup

The fabricated chip was packaged in a pin grid array (PGA) mountable to a printed circuit board (PCB) using a standard chip socket. The PCB was designed in-house and it contains various test pins, decoupling capacitors, voltage level shifter, and connectors for digital and analog signals. Triaxial connectors are used to bias the source and drain terminals as they help to prevent leakage current through the insulator of the cable, which is necessary for measuring small levels of current flowing through the source and drain of a transistor. A photograph of the test chip mounted on the PCB is shown in Figure 2-11(a).

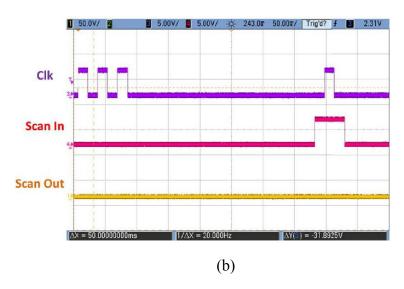

A semiconductor parameter analyzer (SPA) is used to control the digital and analog signals. The SPA outputs the signal per the binary representation of the programmed decimal value. For this specific instrument, a digital high is represented as a '0' and a digital low is represented as a '1'. A level shifter is needed on the PCB board to convert the digital output from the SPA (5V) to the acceptable range used by the test chip (0.9V-1V). An example of a scan-chain test with signals coming out is shown in Figure 2-11(b).

(a)

Figure 2-11 (a) Packaged test chip mounted on the custom-made PCB; coaxial and tri-axial cables are used for delivering analog signals to the chip;

(b) Digital signals outputted from DB25 port used to control the scan-chain.

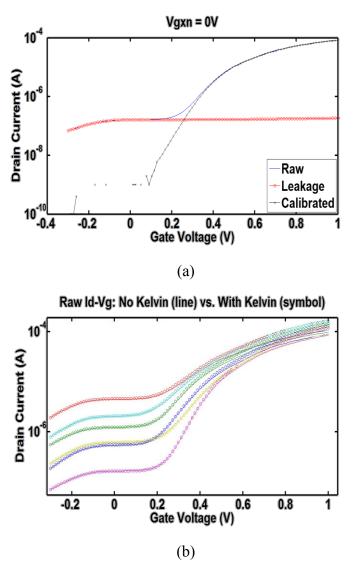

Once the transistor in the array is selected, its source, drain and gate terminals are multiplexed to the I/O pads that are now connected to the SPA. This allows us to perform any basic electrical measurements such as  $I_D$ - $V_G$  and  $I_D$ - $V_D$ . However, the I-V characteristic tends to suffer from a high leakage floor due to the off-state leakage currents flowing through the other transistors within the same column of the characterization array. As mentioned in the previous section, the built-in leakage control circuitry allows the gate terminal of the idle transistors to be set at  $V_{GX}$  to make them strongly off. In conjunction with this method, one can also try to calibrate out the leakage current. This is accomplished by first performing a parametric I-V measurement sweep with none of the devices in the array selected (i.e. the scan-chain is filled with zeros). Let's call the resulting current  $I_{Leakage}$ . Then, one can perform the I-V measurement for the DUT to get  $I_{DIIT}$ . To calibrate the leakage-current out, the two current quantities are subtracted from one another, i.e., the quality of the calibrated current depends on the current sensitivity level of the SPA that can be set for optimal operation, as shown in Figure 2-12.

Figure 2-12 (a) Leakage calibration: leakage floor subtracted out from the raw data. (b) Higher  $I_{on}$  current is observed with Kelvin measurement.

### 2.3.3 Variability Observation

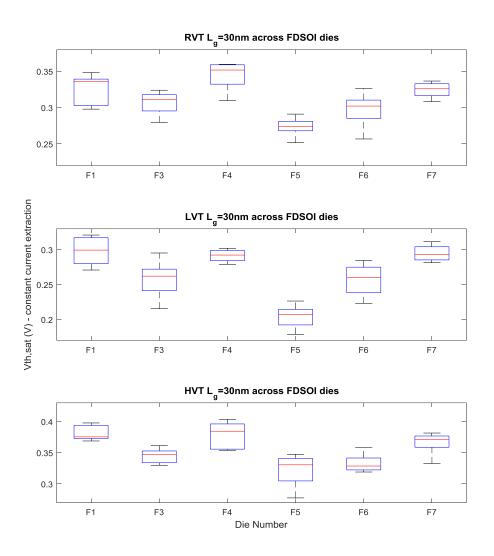

Transistors are characterized in order to understand the underlying variability components. Threshold voltages in both the linear and saturation regimes of operation are extracted using a constant-current definition:  $300nA \cdot W/L$  for NMOS. Once experimental data is acquired, quantities such as DIBL (the difference between  $V_{TLIN}$  and  $V_{TSAT}$ ) can be derived with respect to different modes of measurements. The box plot of  $V_{TSAT}$  of the minimum-sized ( $L_g$ =30nm) transistors across different measured FDSOI dies is shown in Figure 2-13. Different threshold voltage flavors are shown separately across 7 dies with a total of 180 devices in each subcategory. Die mean values are later excluded and modeled as global variations.

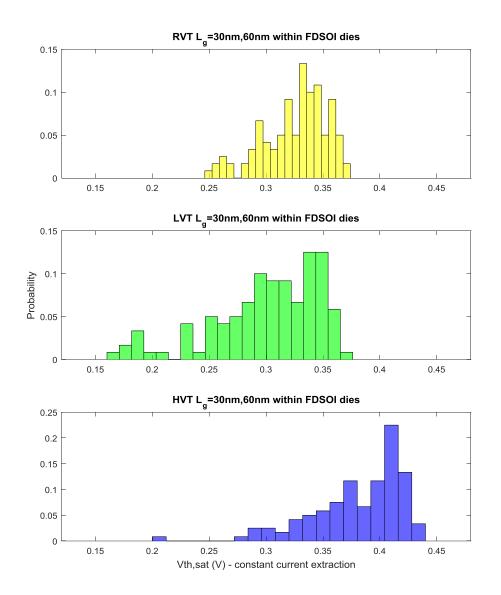

The histograms of  $V_{T SAT}$  for the two minimum-sized ( $L_g$ =30nm, 60nm) transistors are shown in Figure 2-14. The number of mismatched pairs used in this study is 60. Experimental distributions are shown in different colors for various  $V_{th}$  flavors. The distributions of  $V_{T SAT}$  are found to be non-Gaussian due to a limited data size and a premature manufacturing phase. The key point to note here is that non-Gaussian behavior should be captured for compact modeling used in the latter statistical circuit simulation.

Figure 2-13 Boxplot of  $V_{T\,SAT}$  of the minimum-sized (Lg=30nm) transistors across various measured FDSOI dies

Figure 2-14 Distributions of  $V_{TSAT}$  [@ $V_{DS}$ =1V]. RVT have nearly Gaussian distributions, but LVT and HVT do not follow a strict normal distribution.

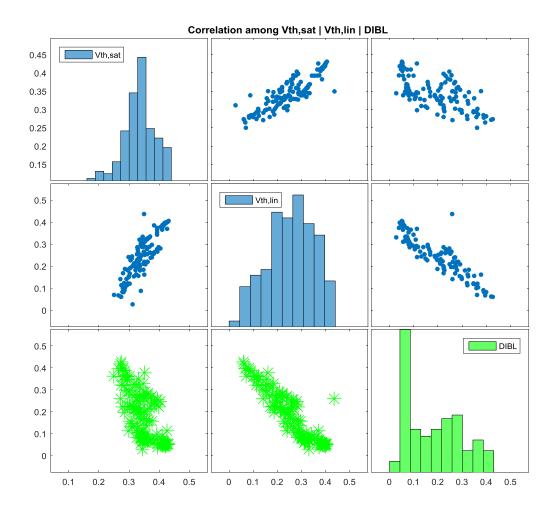

Figure 2-15 Strong positive correlation shows between  $V_{TLIN}$  and  $V_{TSAT}$ ; weak correlation between  $V_{TSAT}$  and DIBL, negative correlation between  $V_{TLIN}$  and DIBL.

Correlation between linear and saturation  $V_{th}$  of the same device measured is plotted in Figure 2-15 (first two rows/columns). Overall, there is a positive correlation between  $V_{TSAT}$  and  $V_{TLIN}$ . The relationship between DIBL and  $V_{th}$  can also be understood by comparing the experimental data in Figure 2-15 (last green row). DIBL (i.e.  $V_{TLIN} - V_{TSAT}$ ) is plotted against the linear threshold voltage  $V_{TSAT}$ . The medians of  $V_{th}$  of the different operation regimes are essentially the same (i.e. this is seen by the same

horizontal spread in the scatter plot). However, there is a large difference in the corresponding DIBL value. Here, the  $V_{TLIN}$  shows a higher correlation with DIBL and a much larger variability. This is because these DUTs are prone to components of RDF [2-16].

# 2.4 Summary

The impact of transistor variability can be efficiently studied using a test chip vehicle. Characterization of an array of test devices including mismatch pairs, different combinations of gate length and channel width dimensions, and different layout proximity allowing for the collection of data, which can be used to analyze random and systematic variability. Since the number of I/O pads is quite limited, many signals must be shared among test blocks either through a decoder or a multiplexer. Care must be taken when designing the selection circuitry to ensure correct operation when accessing a device in an array and to minimize its impact on the measured device characteristics. Leakage minimization circuits can be designed to ensure that the devices that are not under test are turned strongly off to minimize their contributions to the measured current. The variation sources identified in this experiment will help build variability-aware compact models of transistors with physically meaningful parameters sensitive to variability observed in the manufacturing process.

#### References

- [2-1] K. J. Kuhn, A. Murthy, R. Kotlyar, and M. Kuhn, "Past, Present and Future: SiGe and CMOS Transistor Scaling (Invited)" ECS Trans. 2010 33(6): 3-17;

- [2-2] C. Hu, "FinFET 3D Transistor & the Concept Behind it", Solid State Technology & Devices Seminar, UC Berkeley, Aug 26, 2011.

- [2-3] C. Auth; C. Allen; A. Blattner; D. Bergstrom; M. Brazier; etc., "A 22nm high performance and low-power CMOS technology featuring fully-depleted trigate transistors, self-aligned contacts and high density MIM capacitors," VLSI Technology (VLSIT), 2012 Symposium on, pp.131,132, 12-14 June 2012.

- [2-4] Q. Liu; M. Vinet; J. Gimbert; N. Loubet; R. Wacquez; L. Grenouillet; and etc, "*High performance UTBB FDSOI devices featuring 20nm gate length for 14nm node and beyond*," Electron Devices Meeting (IEDM), 2013 IEEE International, pp.9.2.1-9.2.4, 9-11 Dec. 2013.

- [2-5] S.H. Rasouli; H.F. Dadgour; K. Endo; H. Koike; K. Banerjee, "Design Optimization of FinFET Domino Logic Considering the Width Quantization Property," Electron Devices, IEEE Transactions on, vol.57, no.11, pp.2934,2943, Nov. 2010.

- [2-6] M. Bruel; B. Aspar; B. Charlet; C. Maleville; etc, "'Smart cut': a promising new SOI material technology," SOI Conference, 1995. Proceedings, 1995 IEEE International, pp.178-179, 3-5 Oct 1995.

- [2-7] C. Fenouillet-Beranger; P. Perreau; T. Benoist; C. Richier; and etc, "Impact of local back biasing on performance in hybrid FDSOI/bulk high-k/metal gate low power (LP) technology," Ultimate Integration on Silicon (ULIS), 2012 13<sup>th</sup> International Conference on, pp.165,168, 6-7 March 2012.

- [2-8] J.V. Faricelli, "Layout-dependent proximity effects in deep nanoscale CMOS," Custom Integrated Circuits Conference (CICC), 2010 IEEE, pp.18, 19-22 Sept. 2010.

- [2-9] K. J. Kuhn, M. D. Giles, D. Becher, P. Koler, and etc, "*Process technology variation*," IEEE Trans. Electron Devices, vol. 58, no. 8, pp. 2197–2208, Aug. 2011.

- [2-10] B. Pelloux-Prayer; A. Valentian; B. Giraud; Y. Thonnart; J.-P. Noel; P. Flatresse; E. Beigne, "Fine grain multi-VT co-integration methodology in UTBB FD-SOI technology," Very Large Scale Integration

- (VLSI-SoC), 2013 IFIP/IEEE 21<sup>st</sup> International Conference on, pp.168,173, 7-9 Oct. 2013.

- [2-11] M.G. Bardon; V. Moroz; G. Eneman; P. Schuddinck; and etc, "Layoutinduced stress effects in 14nm & 10nm FinFETs and their impact on performance," VLSI Technology (VLSIT), 2013 Symposium on, pp.T114, 11-13 June 2013.

- [2-12] J.V. Faricelli, "Layout-dependent proximity effects in deep nanoscale CMOS," Custom Integrated Circuits Conference (CICC), 2010 IEEE, pp.1-8, 19-22 Sept. 2010.

- [2-13] P.G. Drennan; M.L. Kniffin; D.R. Locascio, "Implications of Proximity Effects for Analog Design," Custom Integrated Circuits Conference, 2006. CICC '06. IEEE, pp.169-176, 10-13 Sept. 2006.

- [2-14] R.A. Vega; T.-J. King, "Comparative Study of FinFET Versus Quasi-Planar HTI MOSFET for Ultimate Scalability," Electron Devices, IEEE Transactions on, vol.57, no.12, pp.3250-3256, Dec. 2010.

- [2-15] N. Damrongplasit, "Study of Variability in Advanced Transistor Technologies", Ph.D. dissertation, UC Berkeley, May 2015

- [2-16] K. J. Kuhn, M. D. Giles, D. Becher, P. Koler, A. Kornfeld, R. Kotlyar, S. T. Ma, A. Maheshwari, and S. Mudanai, "*Process technology variation*," IEEE Trans. Electron Devices, vol. 58, no. 8, pp. 2197–2208, Aug. 2011.

# Chapter 3

# Statistical Compact Model Characterization and Statistical Circuit Verification

### 3.1 Introduction

It is widely recognized that in nanoscale CMOS technology, variation in the manufacturing process has emerged as a fundamental challenge to IC design. While foundries are working hard to mitigate process variability, the design houses are asking for accurate and appropriate models to handle statistical circuit performance evaluation. To accurately represent the process and device variability, it is essential to incorporate the variability during the extraction and calibration phase of compact transistor models. In addition, these compact transistor models require customized test structure designs as well as proper statistical characterization procedures. Conventional statistical compact model characterization methodologies [3-1][3-2] require special single transistor, direct-access test arrays, or virtual measurements from physical simulation data;

moreover, these models do not include rigorous statistical model parameter selection criteria.

After obtaining measurement results from the test structures described in Chapter 2, the next step is to apply statistical analysis techniques to interpret these measurement data. In this chapter, we propose a methodology consisting of a complete flow of statistical compact model characterization (analysis of variability in transistor behavior) and statistical circuit performance evaluation (translation of transistor variability to circuit performance variability).

Our proposed variability-aware compact transistor models can enable statistically optimized designs by capturing device variations in a concise, yet physically accurate way, and they are relatively easy to integrate with existing CAD tool flow. Stepwise parameter selection is combined with sequential extractions of statistical compact model parameters upon foundry-provided nominal compact model cards. These nominal models are trusted as they have been tested extensively and used during the test structure design. Our characterization algorithm selects an optimal statistical model parameter set that can be reliability extracted with the given measurement data.

In addition, we have built a customized Monte Carlo (MC) simulation platform to utilize these compact transistor models in the statistical IC design flow. Different statistical model parameters can be specified prior to the MC simulation within the scripted wrapper of standard SPICE-based simulators. With Gaussian Mixture Models (GMM), non-Gaussian tails in the circuit performances can be more accurately estimated compared to estimation with conventional methods.

# 3.2 Statistical Compact Model Characterization

#### 3.2.1 MOSFET Device Models and Extraction

Interconnect and MOSFET device models are the critical interface between the manufacturing technology and integrated circuit design. *Compact models* include key equations that describe the current of a device as a function of its terminal voltages, to enable circuit simulation. To meet accuracy requirements on device models, existing BSIM [3-4] and PSP [3-5] models are being constantly upgraded to account for the emerging physical phenomena in the nanometer regime. The BSIM models illustrate an example of the evolution of the parametric complexity of transistor models in industrial design kits. For the  $0.5\mu m$  technology in the early nineties, this model had 99 parameters, 7% of which were physical [3-4]. Here, physical quantities directly describe the physical attributes of the system. In the deep sub-micron era (65nm), the BSIM4 generation of this model has 355 parameters, 2.5% of which are physical. The PSP compact model has a similar parametric complexity [3-5].

Once the required transistor measurement data are acquired, one can perform either analytical regression or numerical optimization to estimate the compact model parameters. This procedure and the full set of compact model parameters are commonly referred to as *compact model parameter extraction* and *model card*, respectively. The increasing number of parameters and complexity of equations of compact transistor models drive the need to accurately determine all that many model parameters to reproduce the behavior of a specific observed device. In practice, a complete compact model, for example in this work, a foundry-provided nominal model card, is usually generated using a combination of pre-known technological process data, analytic methods, and numerical optimization methods.

The most widely used numerical optimization methods are based on the deterministic minimization of a nonlinear least squares error function between model output and measurement data. Nearly all optimization methods are iterative, and defining an appropriate starting point as well as parameter bounds is of crucial importance, and often relies on a deep understanding of the model to guide the minimization process.

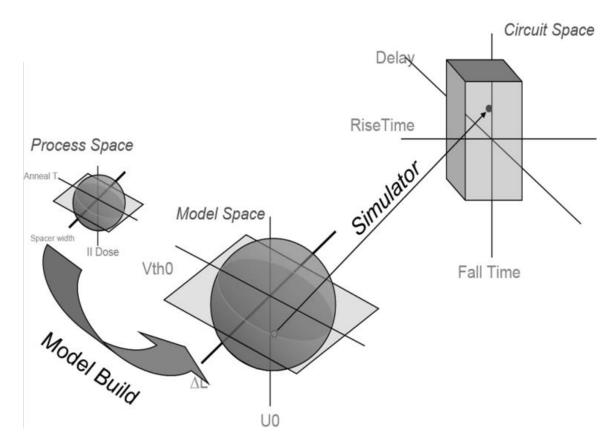

Figure 3-1 Compact Modeling for Statistical Circuit Design Scheme [3-7]

#### 3.2.2 Statistical Device Characterization

Process variations usually manifest themselves as parameter fluctuations in nanoscale transistor physical dimensions or material/electronic properties, such as channel length, threshold voltage, and transistor parasitic [3-6]. All challenges with nominal device characterization become more serious for statistical device characterization, since statistical extraction procedures rely on an accurate extraction of nominal parameters.

After designing appropriate test structures as described in Chapter 2, variation measurements need to be correctly mapped and embedded into a

statistically capable design kit, such that circuit designers can perform statistical circuit analysis and optimization to improve yield. This task is referred to as *statistical extraction*, as illustrated in Figure 3-1. One major problem in statistical estimation is to determine the appropriate distribution of the parameters (e.g., to determine the distribution of  $V_{th}$  follows a normal distribution or a log-normal distribution). The next key question for statistical extraction is to determine the parameters of a specific distribution (e.g., determine mean and variance of a parameter which follows a normal distribution, or to find the mean and covariance structure of a correlated set of multivariate normally distributed parameters).

We focus here on the statistical sub-model of the transistor compact model, which consists of a set of model parameters assigned with a Gaussian variability model. The mean of the distribution is the nominal value given in the full model, while the standard deviation can be determined by various methods, including direct extractions from atomistic device simulation data [3-2] or backward propagation of variance from unit circuit performance measurement data [3-8][3-9].

#### 3.2.2.1 Stepwise Compact Model Parameter Selection Algorithm

Our proposed methodology, using *stepwise selection of compact model* parameters with sequential extractions from transistor measurement data, can provide statistical model parameters that reflect true variability while preserving reduced complexity in subsequent statistical circuit simulations.