# Papyrus: A History-Based VLSI Design Process Management System

by

#### Tzi-cker Chiueh

B.S. (National Taiwan University) 1984 M.S. (Stanford University) 1988

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering -- Electrical Engineering and Computer Science

in the

**GRADUATE DIVISION**

of the

UNIVERSITY of CALIFORNIA at BERKELEY

Committee in charge:

Professor Randy H. Katz, Chair Professor Chittor V. Ramamoorthy Professor Sadashiv Adiga

The dissertation of Tzi-cker Chiueh is approved:

uir ( \ Da

40 11892

Mama mont 11/8/92

Date

University of California at Berkeley

November 1992

# Papyrus: A History-Based VLSI Design Process Management System

Copyright © 1992

by

Tzi-cker Chiueh

#### Abstract

# Papyrus: A History-Based VLSI Design Process Management System

by

#### Tzi-cker Chiueh

Doctor of Philosophy in Electrical Engineering and Computer Science

University of California at Berkeley

Professor Randy H. Katz

With the advent of powerful computer-aided-design (CAD) tools and increasingly complicated VLSI systems, the notion of circuit design has evolved into managing complexity rather than manipulating electronic devices. Complexity arises from enormous amounts of design data as well as the complicated process of creating design data. An important observation is that modern circuit designers spend more time managing the created design data than actually running the CAD tools. The thesis of our work is: the key to further enhance VLSI designers' productivity is not better CAD tools but a more responsive infrastructure. The focus of this dissertation is thus on support mechanisms that allow composition of a set of potentially heterogeneous tools into a coherent design system, and facilitate the integration of design data and design process management.

We develop a design process support model called the Light Weight Transaction (LWT) model, which captures both the structured and exploratory aspects of VLSI design. The former corresponds to the design procedures that are well-understood and thus can be specified in advance, whereas the latter denotes the creative part of a design process. We developed a script facility to support routine design activities and proposed a history-based rework mechanism to allow interactive exploration of the design space. Unlike conventional database transaction models, the LWT model is based on a data visibility abstraction: users can operate on a piece of data only when it is visible to them. We

have shown how this abstraction can support both design exploration and cooperative group work.

To demonstrate the feasibility of the LWT model, we built a prototype implementation on top of the *Sprite* operating system, the Tcl/Tk facility, and the Berkeley OCT CAD tool suite. This implementation features a transparent load balancing scheme to exploit the computation power of networked workstations, an atomicity-guarantee mechanism to preserve the high-level task abstraction. In addition, the rework mechanism depends on a single assignment update principle, which in turn could pose serious storage overheads. Our implementation alleviates this overhead by performing a history-based object reclamation in the background.

Based on the design operation history, we propose a novel design management paradigm: Rather than requiring users to supply design meta-data, the system maintains and analyzes the design history to deduce the metadata, in particular, object attributes and inter-object relationships, according to a suite of domain-specific knowledge and inference procedures. This paradigm can be viewed as a generalization of the approach used in syntax-directed editors. However, we believe this to be the first attempt to apply the idea in the context of design database management systems. Instead of using abstract syntax trees, we use a special representation of the design history called *augmented derivation graph* as the basis for design metadata inference. This paradigm opens a new way of thinking about creating information that are interesting to the system, be that a user, an operating system, or a database system.

Randy H. Katz-

## Acknowledgement

First, I would like to thank my advisor, Professor Randy Katz, for providing a level of support that a graduate student can ever want. By example, he shows that a professor who performs world-class research can also be a caring and enthusiastic teacher. During the four-year stay in Berkeley, I enjoyed and benefited enormously from the numerous stimulating discussions and enlightening conversations. Most of all, Randy offers a latitude for me to work with that no professor can possibly give. For all of these, I hope I can repay him by following his step when I become a professor myself. I also want to thank Professor Adiga and Professor Ramamoorthy for being on my dissertation committee and for patiently reading through the drafts of my thesis.

Like all great research universities, stimulation from fellow students makes up a significant part of one's graduate education. I was fortunately enough to have the following people as my officemates: Ann Chervenak, Mike Dahlin, Valerie King, Ethan Miller, Fred Obermeier, Srini Seshan, Mario Silva, and David Wood. I want to thank them for everything they've done for me. In particular, I want to thank David for setting an example on computer architecture research, Fred for teaching me various tricks of using workstations, Valerie for early discussions on my work, Srini for interesting ideas and discussions, and Mario for his warm friendship.

My parents and brothers deserve special thanks for being always understanding when I said that I need four years to finish my PhD degree. Without their constant prodding, I might still wander around without getting anything done. My big brother, Tzihong, in particular convinced me that theoretical physicists are no more than problem solvers, and that a good scientist should not restrict himself to any particular field. Looking back, I can only say: "How true! How true!" For that I want to thank him.

Last, I want to thank my wife, Sheng-I. For still believing in me after I broke several promises on honeymoon trips. For always patiently listening to my complaints

and frustrations. For taking three hours of commute to work everyday in order to let me walk to school. For trying painfully to understand my work upon my insistence. For cheering with me when my paper got accepted and griping for me when things didn't go our way. For just being there so that I know I can never go too wrong. There must be tons of barriers on the way to get a PhD. But Sheng-I renders them so trivial and makes my journey a delightful adventure. Now that I am done, Honey, let's go to Hawaii!

# **Contents**

| Chapter 1  | Introduction                                      | 1  |

|------------|---------------------------------------------------|----|

| 1.1 The P  | roblem                                            | 1  |

| 1.2 New 1  | Dimension of Design Data Management               | 2  |

| 1.3 What   | A Design Flow Manager Is Not                      | 3  |

| 1.4 Funct  | ional Requirements of A DFM                       | 5  |

| 1.5 Thesi  | s Overview                                        | 9  |

| Chapter 2  | Related Works                                     | 12 |

| 2.1 Proce  | ss Support Systems                                | 12 |

| 2.2 Electr | ronic Design Environments                         | 13 |

| 2.2.1 H    | EDA's PowerFrame                                  | 13 |

| 2.2.2 A    | Automatic Design Manager VOV                      | 15 |

| 2.2.3      | Tool Execution Control Systems at Carnegie Mellon | 17 |

| 2.2.4 I    | Distributed Design Methodology Management         | 22 |

| 2.2.5 I    | DEAS                                              | 23 |

| 2.2.6 I    | Petri Net-based Systems                           | 23 |

| 2.3 Softw  | are Engineering Environments                      | 25 |

| 2.3.1 I    | Process Programming                               | 25 |

| 2.3.2 1    | Hewlett Packard's Tool Encapsulator               | 26 |

| 2.3.3 1    | BM's Programming Process Architecture             | 26 |

| 2.4 Offic  | e Automation Environments                         | 27 |

| 2.4.1 ]    | POISE                                             | 27 |

| 2.5 Sum    | mary of Previous Systems                          | 29 |

| Chapter 3  | The Conceptual Model            | 32         |

|------------|---------------------------------|------------|

| 3.1 Introd | uction                          | 32         |

| 3.2 Basic  | Assumptions                     | 32         |

| 3.3 Light  | Weight Transaction Model        | 35         |

| 3.3.1 E    | Design Step                     | 36         |

| 3.3.2 E    | Design Task                     | 37         |

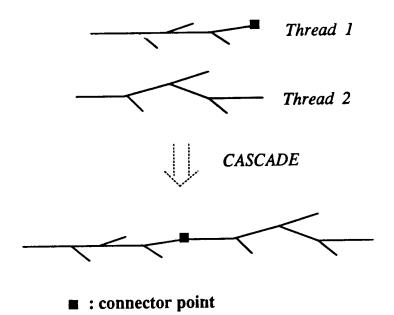

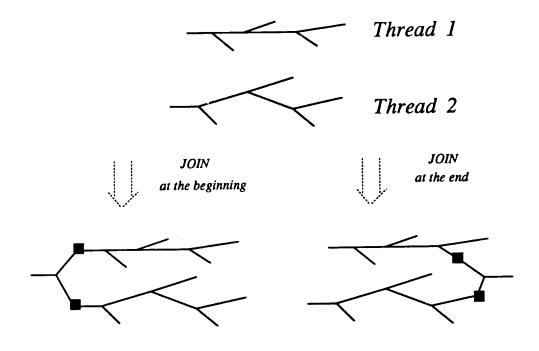

| 3.3.3 E    | Design Thread                   | 41         |

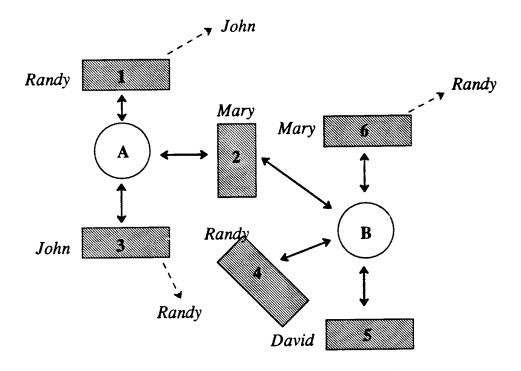

| 3.3.4 I    | nteraction Among Design Threads | 47         |

| 3.3.4      | 4.1 Thread Manipulation         | 47         |

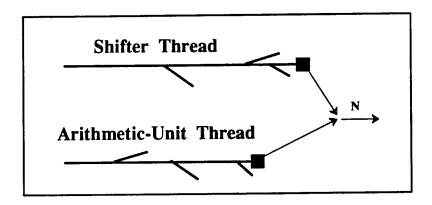

| 3.3.4      | 4.2 Thread Synchronization      | 51         |

| 3.4 Sumn   | nary                            | 54         |

|            |                                 |            |

| Chapter 4  | Design Task Management          | 58         |

| 4.1 Introd | luction                         | 58         |

| 4.2 The T  | ask Description Language        | 59         |

| 4.2.1 T    | Cool Command Language           | <b>6</b> 0 |

| 4.2.2 E    | Extensions                      | 63         |

| 4.2.3 E    | Examples                        | 66         |

| 4.3 Imple  | mentation                       | <b>7</b> 1 |

| 4.3.1 7    | Cool Navigation/Encapsulation   | 71         |

| 4.3.2 F    | Parallelism Extraction          | 74         |

| 4.3.3 F    | Re-Migration                    | 76         |

| 4.3.4 F    | Programmable Abort Semantics    | 77         |

| 4.3.5 H    | History Recording               | 79         |

|            | Attribute Management            | 80         |

| 4.4 Sumn   | nary                            | 80         |

| Chapter 5  | Design Activity Management                           | 82  |

|------------|------------------------------------------------------|-----|

| 5.1 Introd | uction                                               | 82  |

| 5.2 User I | nterface                                             | 84  |

| 5.3 Histor | y Management                                         | 92  |

| 5.4 Storag | ge Management                                        | 96  |

| 5.5 Summ   | nary                                                 | 101 |

| Chapter 6  | Automatic Metadata Inference Based on Design History | 102 |

| 6.1 Introd | uction                                               | 102 |

| 6.2 Relate | ed Works                                             | 104 |

| 6.3 Mode   | ls of Design History Representation                  | 105 |

| 6.4 Increr | nental Meta-data Construction                        | 108 |

| 6.4.1 T    | ype Inference and Attribute Evaluation               | 110 |

| 6.4.2 R    | Relationship Establishment                           | 114 |

| 6.4.3 Г    | Discussion                                           | 119 |

| 6.5 Concl  | usion                                                | 121 |

| Chapter 7  | Conclusion and Future Works                          | 122 |

| 7.1 Resea  | rch Contributions                                    | 122 |

| 7.2 Futur  | e Directions                                         | 125 |

| 7.2.1 V    | What's Next in VLSI Design Systems?                  | 125 |

|            | Other Lines of Research                              |     |

| 7.3 Final  | Words                                                | 128 |

# Chapter 1

# Introduction

### 1.1 The Problem

After three decades' development of computer-aided-design (CAD) tools for integrated circuit design, modern VLSI design is characterized by extensive use of automation tools. From initial conceptual specification to low-level physical layout, almost all design work is carried out through tool invocations. Circuit designers, once the experts in manipulating electronic devices, now become *managers* of design tools and the design data that they generated. Because of the rapid evolution of semiconductor technology and electronic industry, state-of-the-art VLSI design is also moving towards more and more technology-dependent, methodology-driven, and product-oriented. Accordingly the functionality of individual design tools becomes specialized, which leads to a proliferation of CAD tools that are usually created by different vendors with rarely compatible interfaces. Consequently VLSI circuit designers are now facing not only a great deal of design data but also a large number of design tools interacting with one another in complicated ways.

With the advent of these highly automated tools, circuit design basically consists of two types of activities: running CAD tools and managing the created design entities. Almost all the CAD tool research in the last thirty years was focused on the former, i.e, on how to perfect each individual step in the design process. However, just because each such step is optimized, it doesn't mean that the entire design process is necessarily optimal. It has been observed in the electronic design community that a set of powerful tools is *not* equivalent to a productive design environment. Why? The reason is today's circuit designers actually spend more time in monitoring the evolution and integration of design data, and figuring out which tools/tool sequences to invoke, than in actually running the tools.

To further improve the productivity of VLSI designers, CAD researchers should take one step back, examine where the bottlenecks are in the entire design process, and strive to reduce the impact of or completely eliminate these bottlenecks. It is our thesis that as individual CAD tools mature, helping circuit designers to use the right tools at the right time, and to keep track of design data evolution, is the single most effective way to achieve significant improvements in design technology. As a result, rather than concentrating on a specific CAD tool, we take a systems approach towards the development of an integrated VLSI design environment. The emphasis is on the mechanisms to transform a set of loosely-coupled tools into a coherent whole, and the abstractions to manage complicated design data. This dissertation describes the design and implementation of a prototype design process system called *Papyrus*, which is based on such an integrated approach.

## 1.2 A New Dimension of Design Data Management

To put the contributions of this work in perspective, we briefly describe the evolution of VLSI design database management systems, and show where this work stands in relation to previous research efforts. First-generation design databases [WONG79] [MITS80] [ROBE81] [ZINT81] [CHU83] focused on efficient storage and manipulation of internal design data structures such as circuit schematics and physical layouts.

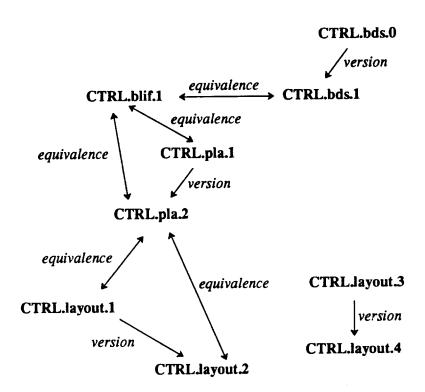

Second-generation design database systems [KATZ87] [WEIS86] [BATO85] [OCT91] recognized the complexities of VLSI design data consisting in not only the internal representations but also the intertwined relationships among pieces of a design, and therefore emphasized the *structural* aspects of design data by providing primitives to model the interrelationships among design components, such as version, configuration, and equivalence relationships. In both generations, the systems only dealt with the *static* aspect of VLSI design, i.e., internal representations and the external structures of VLSI circuits Almost no attention was paid to the *dynamic* aspect of VLSI design, i.e., controlling the design process and monitoring design data evolution.

We believe that the next evolutionary step in design database research is to provide support to facilitate the *process* that creates the design data, and to integrate the management of design data and design process. We use the term *design flow management* (DFM) to refer to this new breed of design database systems. A DFM consists of two components: a *design data manager* (DDM), which manages both design data and metadata, and a *design process manager* (DPM), which controls the sequencing of design activities. These two components are functionally orthogonal, but interact with each other in a synergistic way as we will show in the following chapters. This dissertation mainly focuses on the design process management aspect of a DFM, assuming that a generic object-oriented-like database system takes care of design data management. In our implementation, the design database is OCT [HARR86]. A set of concrete functional requirements that characterizes a DFM are listed in Section 1.4.

### 1.3 What A DFM Is Not

Because design flow management is a relatively new concept, it is also important to understand what it is not, just to set a common ground to continue this presentation. First of all, a DFM is not an implementation of the *CAD Framework Initiative* (CFI) specification. The CFI proposal specifies standard formats for various types of VLSI design data, and procedural interfaces for individual CAD tools and their communications. Although it does have a design methodology/flow management component, the

ideas presented in this work are completely independent of the CFI specifications, and certainly doesn't conform to the standard in any way.

A DFM is not just another design version control system. Although version management systems offer a primitive way of recording design evolution in the form of version history, a DFM not only provides more refined support for tracking design data, but also helps designers to create the design data in the first place. On the other hand, because a DFM manages both design data and design process, a DFM can actually complement a version control system by inferring version-related metadata from the design process, as explained in Chapter 6.

Although it is tempting to categorize a DFM as a long-term transaction system [], it turns out that the fundamental goals of our work are very different from those of long-term transaction systems. For example, in this work no attention is directed to crash recovery. Also maximal concurrency is not as important as design context maintenance. In the choice of concurrency control algorithms, conceptual simplicity dominates theoretical elegance. The reason is that these mechanisms are supposed to be used directly by circuit designers, who may not have the slightest idea of what a transaction is, not to mention more complicated notions of nested or compensating transactions [MOLI87].

Even though a DFM could automate some of the design steps during the design process, it is not a high-level synthesis tool. There are two major differences. First, the major goal of a DFM is to facilitate the designers' interaction with the design environment. A DFM assists but doesn't replace human designers. It is still the human designer that makes most of the design decisions. Second, a DFM is a generic software layer that is built on top of a set of tools and a design database system. In this sense, a DFM assumes an *open* architecture that is independent of the rest of the design environment, which is in contrast to the typically close-coupled synthesis systems whose ultimate goal is to automate the entire design process.

# 1.4 Functional Requirements of A DFM

Instead of giving a precise definition of a design flow management system, it is much more easier to describe a DFM in terms of a list of design goals for such a system. Specifically we have the following functional requirements that have guided the design and implementation of *Papyrus*.

### **Tool Encapsulation**

Modern VLSI CAD tools typically have dozens of parametric options, each of which typically specifies how the tools behave in a particular aspect. As the tools become more powerful and versatile, the users tend to become confused and intimidated by the complicated tool command interfaces. The concept of tool encapsulation separates what a CAD tool does from how it is used. Ideally, users only need to express what needs to be done but not how to do it. By providing a layer of indirection, users are insulated from the invocation details of individual tools such as command options and input/output object naming. Consequently, users only interact with a consistent and high-level (preferably graphical) user interface. Actual invocations of CAD tools are handled by an interpreter that is completely user-transparent. Moreover, this extra level of indirection makes it easier to compose a set of heterogeneous tools into a coherent design environment since users are shielded from the underlying tool set. Modification on individual tools or replacement of one tool with another functionally equivalent one would not affect the users' perception towards the design environment.

## **Tool Navigation**

Because of the proliferation of CAD tools, choosing the appropriate set of tools and applying them in the right order to achieve a given design objective is not a trivial task. Given a goal, a DFM provides a navigation mechanism that guides users through the tool invocation sequence which accomplishes that goal. Tool navigation facilitates routine design work by freeing experienced circuit designers from memorizing the exact tool sequence while leading novice users through an otherwise convoluted web of tools. Tool navigation is essentially a by-product of raising the design abstraction one level beyond

individual CAD tools. Instead of invoking primitive tools, users think and interact with what we call *tasks*. Tasks can automate pre-specified tool execution pipelines when user intervention is not needed, and/or can enforce high-level design methodologies that are specified in terms of constraints on tool execution sequencing.

## Support for Design Exploration

Design by its very nature is a trial-and-error process. Exploration of various design alternatives and choosing the one that fits best according to some criterion is one of the salient characteristics of engineering design. And yet, the current design environments provide almost no support for what we call design exploration. From the users' stand-point, a DFM should allow them to travel back and forth between the design states that correspond to various design choices, and to examine the detailed design tradeoff without having to do the bookkeeping themselves for the mapping between design alternatives and the associated subset of design objects in the database. Design typically also involves many iterations of an identical sequence of steps, e.g., applying the same procedure over and over again to optimize certain property. A DFM facilitates this iterative refinement process by automating the iteration steps, and structuring the intermediate data objects in such a way that users can easily keep track of their correspondence relationships with the iterations.

## **Recording of Design Evolution**

Being conservative, engineering design database is typically version-oriented: modifications are made on the copy of a design object rather than on the object itself. With this so-called *single-assignment* update semantics concurrent development on a design entity becomes possible when there is no need to guarantee mutual exclusion. The notion of *version history* in previous design databases [CHAN89] captures a design's history in the form of snapshots of the database. However, it is often desirable to maintain the design history beyond the simple "which object is derived from which" relationships. For example, the UNIX *Make* facility requires the knowledge of the detailed tool execution sequence that are involved in creating an object, i.e., its *derivation history*, to

reconstruct the design object when one or more of its dependent objects are modified. The concept of derivation history is an operation-based representation of the design history, in contrast to a version history based on snapshots.

### **Context Management**

The notion of directory in a file system is very successful in helping users to organize files into a manageable hierarchy. Now that a DFM manages both design data and design process, one can apply the same idea to cope with complexity. We use the term context to refer to the set of design operations (i.e., CAD tool invocations) AND their input/output data objects that are associated with a particular design entity, which could be either a library cell, a circuit module, or a subsystem. Thus, a context is actually a generalized notion of a file system directory: the latter clusters related data, and the former clusters related data and the operations used to create these data. A context provides a focal point for circuit designers to concentrate their cognitive capacity only on relevant data and operations. A context answers that with respect to a design entity, what have been done? and what are the associated data objects? Contexts also offer a natural way for data protection and consistency enforcement via partitioning of the data space.

## Support for Cooperative Work

Designing a VLSI chip is almost always a group effort. Although CAD tools have been developed that significantly enhance circuit designers' productivity, [CHOW88] has reported that there is still a significant portion of the overall development time spent in phases where automation tools are mostly lacking. In particular, as design technology matures the focus of VLSI design gradually shifts from improving individual productivity to facilitating project completion. One of the major problems is the so-called integration problem: individual modules work just fine, but when they are put together, something always goes wrong. This problem is especially serious when the interacting pieces are separately developed by different designers. There are essentially two aspects to the integration problem. The first aspect is related to version and configuration control. When a system is to be constructed, version/configuration control systems make sure that

the right configurations of the appropriate component versions are used in the composition process. However, simply guaranteeing right versions and configurations doesn't necessarily result in successfully integrated designs. The problem is that the interfaces of the interacting modules do not necessarily "fit" when integrated into a complete system. In other words, the modules are inconsistent with respect to VLSI domain semantics (e.g., timing/electrical characteristics). Incompatibility of interfaces may result from lack of communication, imprecise interface specifications, or both. In VLSI design, cooperation typically occurs via data sharing, for instance, a cell developed by one designer is used by the others, or two modules interacting with each other must agree on protocols at various levels of abstractions. A data sharing facility protects the rights of producers of design objects by preventing security violations, and keeps consumers from using objects that are not considered well-formed by prohibiting pre-mature access. In addition, change management in the form of active propagation or passive notification should be provided to maintain certain degrees of consistency.

#### **Distributed Architecture**

With the advent of powerful workstations in engineering design environments, a DFM should be able to take advantage of this technology by transparently distributing design data and tool execution across the network, thus making efficient use of the otherwise wasted CPU cycles. In a distributed environment it is important to guarantee certain atomicity property so that the side effects of a pre-specified tool execution sequence are either all or none across failures. It is also desirable to have some priority mechanism to prioritize tool execution and to load-balance workload in the networked computing environment. In this regard a DFM can be viewed as a specialized operating system that extends and tailors the services provided by the operating system to the needs of VLSI design.

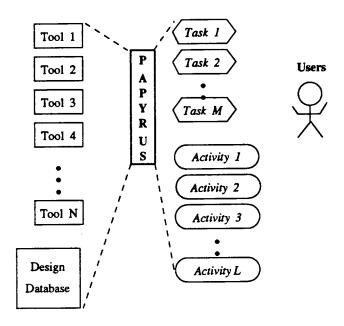

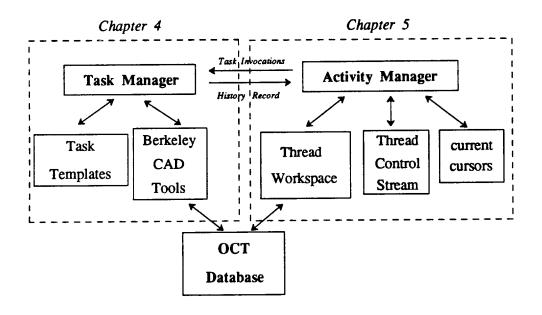

Figure 1.1 Conceptual Architecture of A Design Environment Using Papyrus

#### 1.5 Thesis Overview

In summary, *Papyrus* provides the necessary hooks that glue a set of CAD tools, which may well come from different development sources, into a consistent environment as seen by the end users. In addition, it provides support mechanisms to facilitate generic engineering design activities such as alternative exploration or iterative refinement. *Papyrus* does not make any assumptions about the CAD tools and/or database systems. Figure 1.1 shows the global architecture of a design environment that uses *Papyrus* as the coordination entity of the design tools and design data in the system. From the user's standpoint, he or she only interacts with high-level abstractions such as design tasks and activities (to be explained in later chapters). As a result, individual CAD tools and their complicated interfaces and interactions are shielded from normal users, in this case the circuit designers. *Papyrus* also provides a link between design data and design process management. The rest of this thesis are organized as follows.

In Chapter Two, previous research efforts related to this work are surveyed. We are primarily interested in how previous software systems support *processes* in various

domains such as office automation, software engineering, and electronic design. The survey is meant to convey novel concepts developed in these systems rather than their complete descriptions.

In Chapter Three, the conceptual model that guides the design and implementation of *Papyrus* is described. We call this model the *light-weight transaction* (LWT) model. It aims to strike a balance between the rigorous control of data integrity in conventional database transactions and the user-friendliness requirements of an interactive engineering design environment. Rather than resorting to the notion of *atomicity*\*1, we advocate the concept of *visibility* as the central abstraction. The word *light-weight* is used to describe the fact that our model doesn't adhere to all the *ACID*\*2 requirements that characterize database transactions, but rather chooses to relax these requirements to accommodate creative design activities.

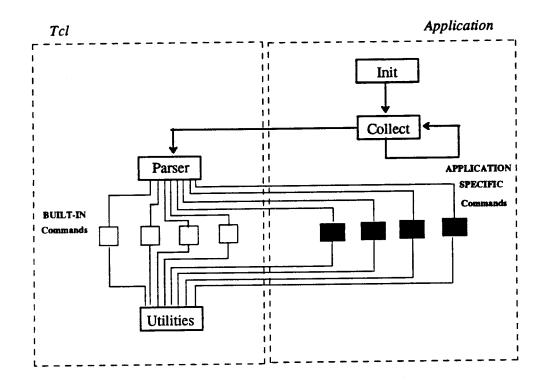

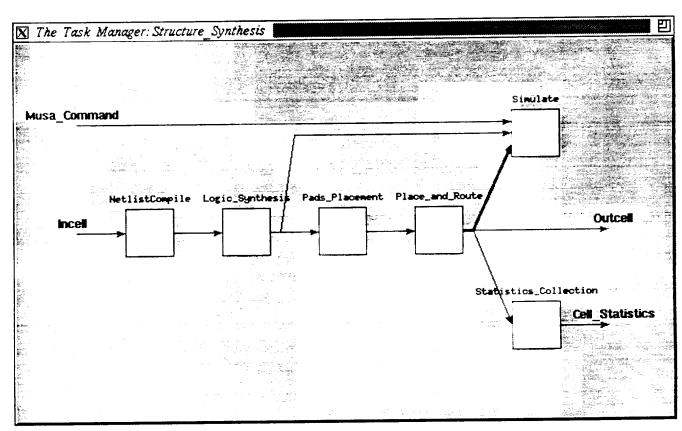

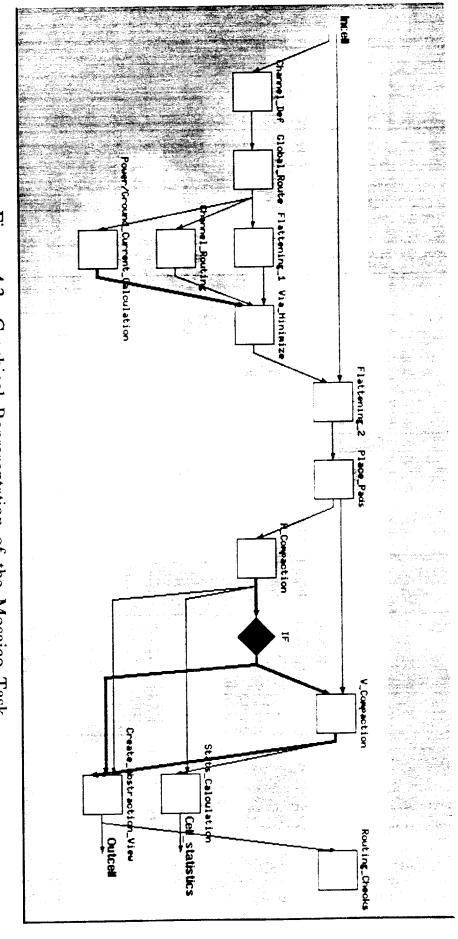

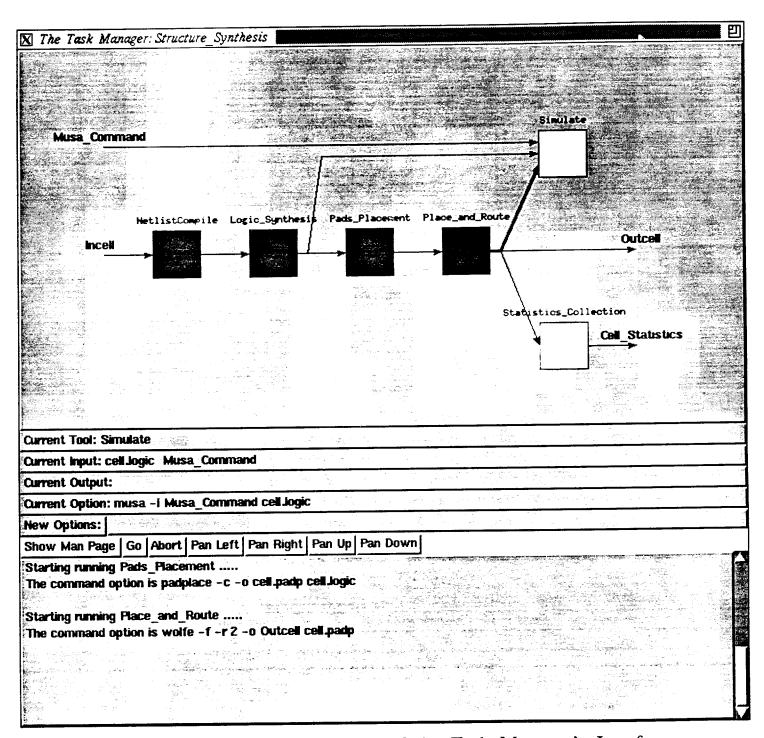

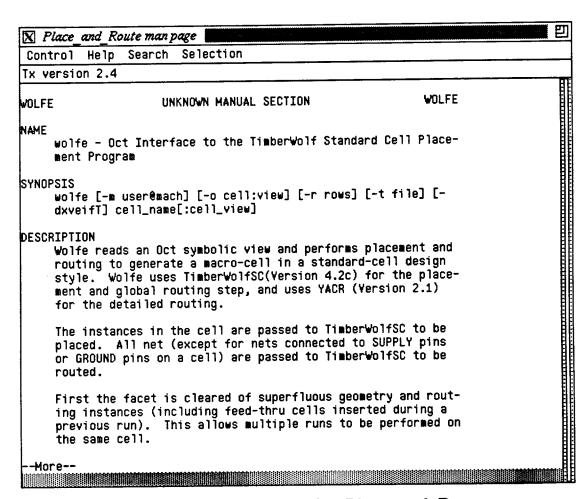

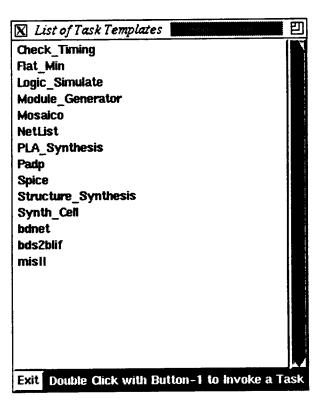

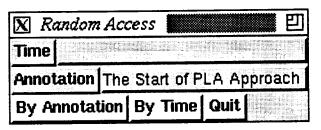

Chapter Four and Five describe the implementations of *Papyrus*'s two major components: the *Task Manager*, which is essentially a parallel and distributed process control system augmented with the capabilities of tool encapsulation and navigation, and the *Activity Manager*, which transparently maintains the contexts associated with various design alternatives, and provides a controlled data sharing mechanism to synchronize concurrent design activities. We discuss how these two subsystems are implemented on top of Sprite and the Tcl/Tk package, and the interaction among them.

In Chapter Six, we describe an application of the design operation history maintained for supporting design task and activity management. We propose a novel design data management paradigm in which design meta-data, such as per-object attributes and inter-object relationships can be inferred from a design object's derivation history, which is automatically collected as a by-product of activity management. This approach not only enhances the data management capability of a DFM but also relieves the designers from the burden of explicitly computing or entering some of the meta-data, thus indirectly improves the productivity of circuit designers.

<sup>\*1</sup> A set of operations is said to be atomic if either they all occur or none of them occurs.

<sup>\*2</sup> ACID stands for Atomicity, Consistency, Isolation, and Durability.

Chapter Seven summarizes the main research contributions of this thesis, reexamines how the proposed mechanism satisfy the stated design goals, recapitulates the lessons learned from this project, and provides a personal speculation on what future VLSI design systems should look like as well as the further research issues entailed by this vision.

# Chapter 2

# **Related Works**

## 2.1 Process Support Systems

A process support system aims to facilitate the work processes of developing artifacts, e.g., designing circuits or writing software. The notion of process support is a relatively new concept, which only has begun to emerge in the last decade. Before then, the consensus was that the data upon which an organization operated is the central focus of organizational computing. Correspondingly the emphasis of computer support has been placed on the database facility that allows fast and reliable access to the data. With the advent of ever more advanced database services, organizations recognized that to further promote their productivity, it is at least as important to improve the process of creating data as managing the data after they are created. In some domains, the process of generating data and the final data are both considered precious knowledge that needs to be documented and maintained.

In this section, we review a set of representative process-support systems in electronic design, software engineering, and office automation domains. The goal of this

survey is to understand the design issues for supporting work processes, how the proposed solutions in the surveyed systems address these issues, and to make the case for why design process management systems are needed. We make no attempt to describe the systems in greater detail than necessary. Despite this field's relatively young age, this list is also not meant to be exhaustive. We have based our selections on new ideas, not an exhaustive listing of new systems. Wherever possible, we examine and analyze the systems along the dimensions corresponding to the functional requirements outlined in the last chapter. Because we are mainly interested in VLSI circuit design, the survey is necessarily biased towards that particular domain.

## 2.2 Electronic Design Environments

### 2.2.1 EDA's PowerFrame

Primitive forms of VLSI design process management products have emerged in the last three years, e.g., the Falcon system from Mentor Graphics, the Framework system from Cadence, and the PowerFrame system from Digital Equipment Corporation. PowerFrame [GOLD88] was originally developed by EDA Systems and is perhaps the earliest one among these offerings. Since the takeover of EDA by DEC, PowerFrame is emerging as the de facto standard for design process management products in the industry. As can be seen in Chapter Three, Papyrus shares many ideas with PowerFrame.

In a word, *PowerFrame* attempts to make it easy for end users (i.e., circuit designers) to use the right tools on the right set of data objects. Moreover, the design process should be automated whenever possible. *PowerFrame* allows routine tool execution sequences to be specified in advance, and stored in a database for later use. These pre-defined sequences are called *templates*. Users do their design work by invoking templates. Multiple tasks can be invoked in parallel. *PowerFrame* instantiates templates and navigates users through the associated tool execution sequences.

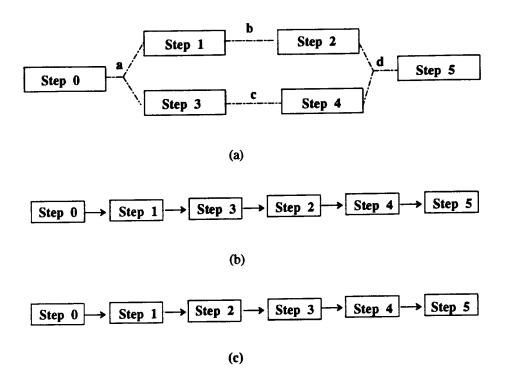

PowerFrame provides a graphical user interface in which templates are represented as an annotated directed graph with various process and edge operators. For example, in

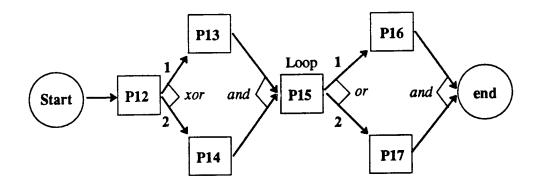

Figure 2.1 Graphical Representation of PowerFrame's Task Templates

Figure 2.1, a task P consists of six tool invocations: P12, P13, P14, P15, P16, and P17. The sequencing among these tool invocations is specified in terms of edge operators such as and, or, and xor. The numbers on the edges represent priorities. For example, after the completion of P12, the xor operator indicates that only one of P13 and P14 is allowed to execute and P13 has a higher priority. The or and and operators assume obvious semantics. There are also process operators such as the Loop operator on P15, which means that P15 will be invoked on elements of a set or a queue.

On the data management side, *PowerFrame* provides several mechanisms for organizing and maintaining design data. The basic abstractions are *workspace*, *filter*, and *configuration*. The notion of workspace allows grouping of logically related data to form a unit of protection and consistency. Each member of a design project can separate his own data from others by forming a private workspace. At a higher level, a group workspace is formed as a synchronization point for data sharing. The filter mechanism takes a VLSI module and returns a selective part of the module. Filters allow users to concentrate on certain aspects of design data, e.g., a specific representation of a circuit. Configurations are aggregations that bind together components of a design entity. This is particularly useful for maintaining VLSI design data, where complex representations and hierarchical structures are ubiquitous.

Although *PowerFrame* seems to achieve the goals of tool encapsulation and navigation by providing a coherent view towards the underlying CAD tools, there is a missing

link between its process management facilities and data management services. In particular, the design history is not maintained and therefore object versions are not tied to the operations that create them. Moreover, the system doesn't offer any assistance beyond script-like automation/navigation. As interesting designs require more interactive decision-making than running routine scripts, it is essential for a process-support system to support higher-level design activities such as trial-and-error and/or iterative refinement. *PowerFrame* also lacks the capability of exploiting the power of distributed computing environments.

## 2.2.2 Automatic Design Manager -- VOV

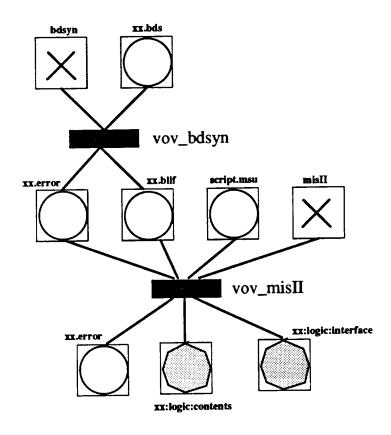

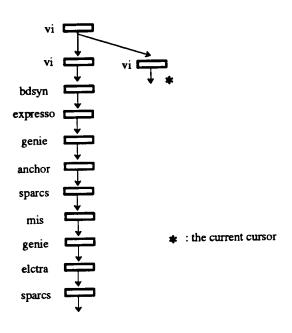

The initial motivation of VOV [CASO90] was to assist novice VLSI designers to use the CAD tools in the Berkeley OCT [HARR86] environment. The central abstraction of VOV is the trace, a history of design operations performed by circuit designers. Figure 2.2 shows an example trace, where shaded rectangular boxes represent a tool invocation and square boxes represent files involved in a tool invocation. Design flows from top to bottom in Figure 2.2, i.e., the files above a tool invocation are inputs while those below are outputs. Different icons are used to represent alternative types of files, e.g., a square with a cross represents an executable file while a square box with a circle represents a normal UNIX file, and so on.

Traces contain the data dependency relationships between design objects and the tool invocations involved in creating them. When an object is modified, an automatic retracing facility consults the trace database to infer the affected set of objects. It re-runs the associated tool execution sequences to regenerate derived objects, keeping the consistency among objects that are related by the derivation relationships. During retracing, objects are updated in place. Portions of a trace can be used as example tool execution sequences, which novice circuit designers can imitate to accomplish certain tasks. VOV provides various data services such as concurrency control to guard against accidental overwrites, and measurements, which serve as the basis for validation and high-level performance estimations. For example, designers can use delay measurements of a layout

object to determine the parametric values of a place\_and\_route tool invocation. Finally VOV has the capability of transparently dispatching tool executions on a network of workstations.

Figure 2.2 An Example Trace of a VOV's Session

The main drawback of VOV is that it assumes a centralized-server architecture, where all traces of all members of a design project are collected in a flat (i.e., non-hierarchical) database. In other words, there is no structure built into a project's traces. When traces grow as a project evolves, this architecture not only makes it difficult for the system to manage traces but also discourages users from browsing traces interactively. The philosophy of VOV is learning from examples, and VOV's author argues against PowerFrame's script-like templates. The reason is the claim that no innovative designs can come out of invoking pre-defined scripts only. However, even VOV later provides example traces to help novice users. On the other hand, traces are little more than

automatically-generated UNIX make files. Although retracing facilitates consistency maintenance, it is not clear how VOV's traces address other design process management problems such as tool encapsulation and navigation, and support for high-level design activities.

# 2.2.3 Tool Execution Control Systems at Carnegie Mellon

Groups at Carnegie Mellon University have built several generations of CAD tool execution control systems, most of which are based on artificial intelligence techniques such as the *blackboard* model. A blackboard is a global database that maintains a set of facts against which rules can be matched and applied. An inference engine matches rules with the facts. If there are multiple matched rules, the inference engine chooses one of them and fire it. New facts can be added to a blackboard as a result of firing matched rules. The goals of these projects were two-fold: automatic tool execution and tool integration. The former aims at automating design work beyond the level of individual CAD tools, while the latter focuses on providing a flexible framework for adding and deleting CAD tools from a design environment without re-programming the environment and/or disrupting the users.

The first project that came out of this group, called *Ulysses* [BUSH89], modeled both CAD tools and circuit designers as *knowledge sources* (KS). In *Ulysses*, a knowledge source can post design goals to a global database called the *blackboard* to request services from other knowledge sources. On the other hand, every knowledge source continuously monitors the blackboard and volunteers to provide services when it detects that its capabilities match posted goals. Every knowledge source is equipped with the following information: *Precondition* file match patterns, *conflict resolution* parameters, and an execution method. The latter is the action performed by a knowledge source when it is chosen to execute.

Knowledge sources are activated by the presence of data on the blackboard that matches their preconditions. When multiple KS's are activated, a special KS called the scheduler ranking the capabilities of volunteering knowledge sources and chooses the

one most qualified. The ranking is done by considering the conflict resolution parameters of each KS such as the execution priority, required computation resources, and etc. After a KS is selected, the system sets up inputs and parameter options for invoking the chosen KS's action event, which is usually one or more tool invocations, thus isolating low-level details from the users. Because the scheduling of tool execution in *Ulysses* is based on individual tool's precondition matching mechanism, deletion or addition of CAD tools won't affect the rest of the environment, except the quality of the resulting designs. This is what *Ulysses* claimed as the open and distributed mechanism to integrate heterogeneous CAD tools.

Ulysses provides a script language for describing knowledge sources, design tasks, and consistency maintenance rules. Knowledge source specifications contain the same information described above. A design task is intended to guide the actions of knowledge sources and are interpreted by the scheduler. Design tasks specify procedurally the sequences of actions to be performed. Some of the actions can be performed by directly invoking tools, and the others can be posted to the blackboard as design goals for other knowledge sources to take over. The script language allows common control constructs such as if-then-else, for-loop, while-loop, and etc. A task can be composed of other subtasks.

Consistency maintenance rules serve the purposes of handling exceptions and cleaning undesired side effects. Specifications of consistency maintenance rules are similar to design tasks. Whenever a tool fails to satisfy the constraints (or goals), certain consistency rules are triggered to perform backtracking, make local modifications to the design, and retry the tool. Rules can also be used to ensure consistency among design components when local modifications made on one component affect the others.

Cadweld [DANI89] extends *Ulysses* by providing a class hierarchy for modeling CAD tools. Each CAD tool is modeled as a *knowledge object*, which is specified in terms of a *frame body* and a *control body*. A knowledge object's control body is similar to a knowledge source's precondition file matching pattern in *Ulysses*, which specify the conditions under which the knowledge object can be activated. A knowledge object's frame body contains tool invocation information such as the location of the binary file, the host

machine, the input/output file type, etc., and corresponds to the action sequences in *Ulysses*'s knowledge sources. The following is an example frame body specification. Detailed descriptions of its semantics can be found in [DANI89].

CLASS: PROCESS-SIMULATOR

USER-NAME: "FabricsII"

HOST: TUCANA

PATH: "/usr/jbb/bin"

**USER-INTERFCAE-TYPE: TTY**

MAN-PATH: "/../maxwell/usr/eecad/man"

**DESCRIPTION:** None

COMPUTING-EFFORT: 90

INTERACTIVE: No

PRIORITY: 10

AGE-TYPE: STANDARD

INPUT-TYPE: ".fin"

OUTPUT-TYPE: ".spin"

**OUTPUT-VIEWER:** None

TYPE:STATISTICAL

A tool class hierarchy allows sharing of the control body among CAD tools with similar capabilities. Both *Cadweld* and *Ulysses* adopt a rule-matching paradigm for automatic tool selection, which shields the impact of tool addition or deletion from the users. High-level design-specific knowledge is embedded in scripts to control the exploration of design space.

It is unclear how this knowledge is derived in the first place (e.g., capability ranking of multiple volunteering CAD tools), how effective this knowledge is in real designs, and how far this automatic design exploration paradigm can go. Furthermore, these systems do not assume that human designers play central roles in the design process. In fact they are treated as just another knowledge source. This is in contrast to our philosophy: we

believe that designers are the ultimate control of the design process, so the design system should aim at providing a friendly environment for exploring the design space, rather than embedding heuristic rules to control the exploration process.

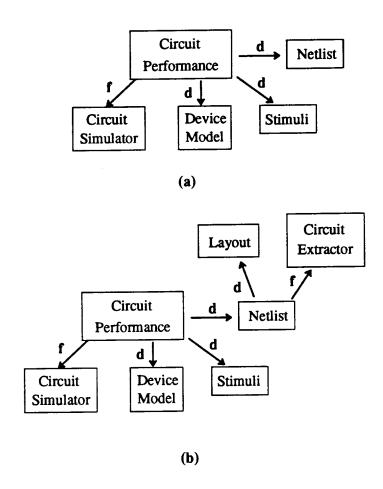

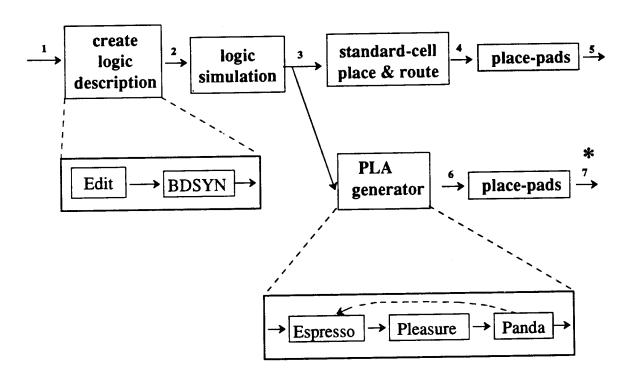

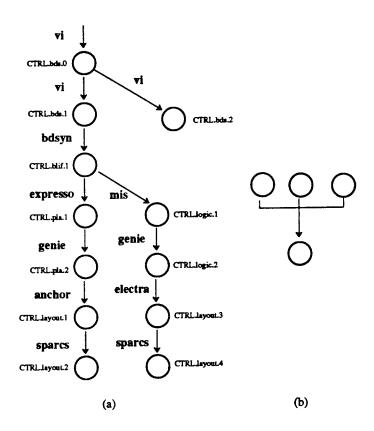

Figure 2.3 Task Schema and Task Derivation

A recent system from the same group, *Hercules* [BROC91], abandons the black-board architecture and instead takes a procedural approach. *Hercules* proposes the concept of *task schema*, which is another form of tool execution template. Each task schema has a *target entity*, which is the intended output when the task is instantiated, and a set of *support entities*, which are either inputs or executables. Figure 2.3(a) shows an example task schema, where circuit-performance is the target entity, while circuit-simulation, device-model, stimuli, and netlist are support entities. The relationship between target

and support entities are represented by directed arrows from targets to supports, with annotations that specify the nature of support entities. An "f" denotes an executable support entity while a "d" a data file. Users run tools through task instantiation, which consists of four steps. The first step is called task derivation, which composes complex task schema by connecting primitive task schema, as shown in Figure 2.3(b). In this case, a circuit extraction task schema is combined with a circuit simulation task schema. Hercules provides a graphical interface for composing task schema. The second step is resource management, which fills in actual arguments (i.e., file names) for the entities in the derived task schema. The third step is task execution, in which the system traverses the derived task schema and invokes corresponding tools. The last step is storage, in which the resulting instance of the target entity is actually stored. It seems to us that the idea of task derivation would put unbearable burdens on the part of the users, and the concept of task schema really didn't offer any more modeling power than a vanilla script language.

Another group at CMU [VIDO89] (Integrated Design Environment: IDE) used similar blackboard models to address tool integration and management. IDE is also based on the notion of a design task, which is specified as a set of design goals and design constraints. A design task is mapped into a tool execution sequence called a design process. This mapping is either by an automatic planner or manually by circuit designers as a fall-back mechanism. A design process is a directed graph, where nodes represent tool invocations and arcs represent flowing data. Internal details of a design process is transparent to the users. The other feature of IDE is its emphasis on distributed and parallel implementation. The idea is to build the entire system on top of a parallel programming environment, harnessing the increasing horsepower of distributed computing environments.

In summary, most of the CMU systems take an "intelligence-embedding" approach in which domain-specific and application-specific domain are exploited to help designers beyond the design task level. Our position is that if something can be specified in advance, either in terms of procedures or rules, it probably can also be embedded into tasks. Moreover, there is always a limit on how much knowledge the system can exploit.

Beyond that limit, the CMU systems are completely ineffectual. It seems to us that as far as design process management is concerned, these systems simply address the wrong problem because of the ignorance of the interactive nature of VLSI design. For example, almost no effort is spent in coupling design data and process management. To be fair, the CMU systems should be better viewed as descendants from their high-level synthesis systems, rather than a true standalone design process management system.

# 2.2.4 Distributed Design Methodology Management

Microelectronics and Computer Corporation's (MCC) CAD Framework Methodology Management System (MMS) [ALLE90] provides users with a task abstraction and a distributed tool execution mechanism. A task is a sequence of tool executions written in LISP functions. Therefore it can take advantage of all the language features of LISP. Circuit designers interact with tasks rather than individual tools. A task engine interprets the specifications in the invoked task templates and communicates with the Process Control Server (PCS) facility to determine initial process placement for load balancing. Moreover MMS provides specialized communication services on top of the Remote Procedure Call facilities offered by the underlying operating system. Processes on any supported host, enabling multiple processes to cooperate in a distributed manner while being isolated from the underlying network transport mechanism. This facility makes it easy to develop parallel programs on a heterogeneous computer network.

Like *PowerFrame*, MMS doesn't provide any support for high-level design activities. The coupling between design data and design process management appears to be weak. In addition, because MMS only provides initial process placement as opposed to process migration, long-running tool executions could still occupy a machine even when its owner returns and wants to reclaim the machine. In this case, either the tool execution is aborted or the machine's owner is forced to tolerate degraded performance.

#### **2.2.5 IDEAS**

AT&T Bell laboratories developed an electronic design framework called IDEAS [MEHM87] [TAYL87], which provides mechanisms for description, control, documentation, and automation of a design process. IDEAS consists of two components: a design data tracking module (DDT) and a design methodology management module (DMM). DDT in turn is built on two abstractions: design state and design file tracking. Design states allow designers to have a comprehensive view of design versions and data management. The design file tracking mechanism records tool invocations and their inputs/outputs to keep track of the derivation relationship among design files and the associated tool executions. Facilities are provided to allow designers to query the design process history and the dependency relationships among design files.

The design methodology management system provides a hierarchy of process abstractions to describe various granularities of a design activity. In particular, a design thread is a description of a generic methodology for accomplishing a certain goal, just as a task in previous systems. A run-time facility, called the process specification agent, takes design thread specifications and guides users to customize design threads to the requirements of specific designs.

IDEAS is probably the closest work to *Papyrus* in terms of its mechanisms and software architecture. The only defect of IDEAS is the lack of a clean conceptual model, which makes IDEAS more a set of loosely-coupled mechanisms than an integrated environment. In addition, it doesn't address the issues of group work and distributed computation.

## 2.2.6 Petri Net-based Systems

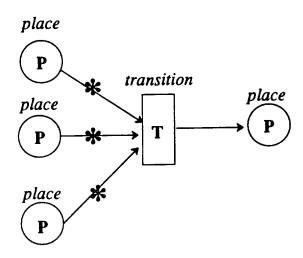

Because of their superior capability for describing parallel and concurrent activities, Petri Nets have been used in several systems as the central formalism for design task description. Among these systems, *Monitor* [JANN85] is probably the earliest work. A Petri Net is basically a bipartite graph, as shown in Figure 2.4, with two types of nodes: places and transitions. Tokens flow on the nodes via the following rule: A transition T is

#### \*: token

Figure 2.4 Generic Petri Net Formalism

enabled if and only if all input places to the transition hold one token and all output places hold no tokens. *Monitor* shows how this formalism can capture the data dependency relationships among tool executions that constitute a high-level task. It also provides a graphical user interface for users to specify and interact with the Petri-Net design process specifications. Another system [BRET90], developed at Siemens uses a more refined version of Petri Net called Predicate-Transition Petri Nets. In this formalism tokens can assume arbitrary types in the form of n-tuples over values from n domains (most frequently used domains are strings, integers, reals, etc.). Typed tokens allow a generic Petri Net to be used in different instances that share an identical structure but different types of data objects. Combining this formalism with rules, the system is able to make complex decisions based on the current state of the design. As a result, both static data dependencies in the form of tool sequencing, and dynamic decision-making in the form of backtracking and conflict resolution, are supported within a single framework.

The drawback of these systems is that they are pre-occupied with abstract models for representing CAD tool invocations and neglect the fact that there is more to design

than invoking tools such as managing design data. In addition these systems implicitly assume that all the operation sequences involved in a design process can be specified in advance. Consequently the templates in these systems are generally flat, and no composition operators are provided that could be used to organize design operations to reflect a particular design's development process. And again, no effort is spent in integrating design data and process management.

## 2.3 Software Engineering Environments

### 2.3.1 Process Programming

Process programming paradigm [OSTE87] advocates that software engineering activities, such as code development and maintenance, should be viewed as systematic processes that themselves should be described thoroughly and rigorously in program-like notations. In other words, programming itself can be described as a program. With this model, a run-time support system executes process programs by guiding programmers through the software development lifecycle according to the specifications. An important part of this paradigm distinguishes the activities performed by humans from those by automatic tools, and orchestrates the actions of humans, the support system, and tools. Activities involved in a software development lifecycle are neither completely mechanical and automatable, nor completely spontaneous and undefinable. Rather they are a mixture of these. It is believed [TBOW87] that this mixture can best be specified and communicated to the users by expressing it in a concrete form such as a process program. Unfortunately so far there has not been any significant systems that have been built and tested based on this paradigm. As a result, process programming remains an intriguing academic curiosity whose advocated advantages are still left to be validated.

## 2.3.2 Hewlett Packard's Tool Encapsulator

HP's SoftBench [FROM90] is an integrated software development environment in which a set of software tools such as editors, compilers and debuggers are integrated under a single framework. HP encapsulator is the tool integration and process specification facility of SoftBench. There are two mechanisms of HP encapsulator that are particularly interesting. Encapsulator Description Language (EDL) is a specification language that allows integration of non-native tools into SoftBench, and provides interfaces for encapsulated tools to make use of certain systems facilities in SoftBench such as the broadcast message server, which provides a multicast service to registered processes. A tool trigger represents cause-effect relationships between tools. A trigger occurs when a notification message is sent from one tool to its destination tool(s). Then one or more tools respond to that notification by taking certain actions. A trigger is actually an event-action pair that is specified in EDL. Therefore EDL not only allows customization of the appearance of each individual tool (e.g., the user interface part), but also supports tailorable project-specific management policies via trigger specifications. In summary, tool encapsulation consists of two tasks: interface customization and trigger specification, and they are both written in EDL. There is no process support mechanisms beyond tool encapsulation.

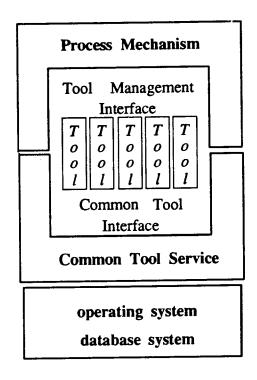

## 2.3.3 IBM's Programming Process Architecture

Programming Process Architecture (PPA) [RADI85] [HOFF85] [CHRO90] promises a framework for formally describing software development processes. In this framework, a software development process is decomposed into primitive process stages called activities, which represent one or more tool invocations. For each activity, the following are defined: (1) a list of Entry criteria that should be satisfied before starting the activity, (2) a set of Task descriptions that indicate what is to be accomplished, (3) a Validation procedure to verify the quality of the work items in the task specifications, (4) a checklist of eXit criteria that should be satisfied before the activity is considered completed. Based on this so called ETVX paradigm, the system provides process management operations

that capture and analyze product/process data in each process stage and give immediate feedbacks to the programmers. Early corrective measures, such as specifications modification, could be taken if errors are detected.

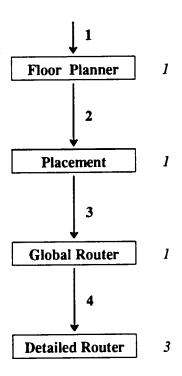

Figure 2.5 Architecture of the PPA System

As shown in Figure 2.5, the system consists of two components: a process mechanism (PM) and a common tool service (CTS). CTS presents a uniform data model and offers data access services to the tools in a development environment. It also includes a well-defined interface to the underlying operating systems. Tools built on top of this interface are independent of the underlying operating system and thus are portable across different platforms. A key feature of PPA is the separation of the design process from the products developed using the process. The PM provides a process management language for users to define the sequencing among activities. The PM encodes this process definition as a set of life-cycle control rules. During process execution, the PM accepts user requests for data and development tasks to be performed, and records

actions taken for later analysis. It accesses the process rules to determine if a request should be granted, based on whether the actions and conditions specified in the process as prerequisites to this request have been satisfied. If so, the PM either invokes appropriate tools through a *tool management interface*, to satisfy the request, or notifies the user to carry out the task. One implementation of this model is AD/Cycle [CHRO90].

Because PPA is really a software life-cycle support system, the proposed process model is too *large-grained* to be directly applicable to a VLSI design environment. For example, there is no support for choosing the right tools to accomplish a certain task. Also, the model as it stands, is heavily oriented towards pre-specified scripts for high-level management operations only, which doesn't necessarily ease low-level tool selection/invocation.

## 2.4 Office Automation Environments

#### **2.4.1 POISE**

POISE [CROF84] is an earlier system that aimed to reduce the overhead of office information flow by providing hierarchies of task descriptions. Task descriptions specify the steps in a task, the corresponding tool invocations, and their goals. POISE acts as an intelligent interface between users and tools in an office. Three types of information are used by POISE: the procedure library contains task descriptions; the semantic database contains the objects operated on by tools, and the tools themselves. A particular user's state includes partial instantiation of a task, parameters derived from user actions, as well as the objects involved.

POISE provides an Event Description Language to express a task's sequence of actions in a procedure. The language also allow specifications of preconditions for a task to start. Tasks can be nested to an arbitrary depth. The lowest level in this hierarchy corresponds to an individual office tool execution. Data is modeled in a semantic database model, which is based on a frame-based representation language. A frame is a named collection of attribute-value pairs called frame slots. Objects are mapped to

frames, with their attributes corresponding to frame slots. Composite objects are described via sets of frames. POISE can work in two different modes -- interpretation or planning. In the interpretation mode, users posted goals and POISE attempts to match the user's goals with task descriptions in the procedural library. Once a match is found, the corresponding sequence of tools are invoked. In the planning mode, users invoke procedures directly and POISE automates as much of that procedure as possible. By providing both a goal-based and a procedure-based descriptions of a task, POISE automates the operations within a task as well as provides navigation among task invocations. Unfortunately, the variety of operations and data representations in an office environment are relatively simple compared to those in VLSI design. As a result, the issue of highly complex tool sequencing and data control is not really stressed in POISE.

## 2.5 Summary of Previous Systems

Judging from the systems surveyed so far, we can safely conclude that the need of computer support for *processes* in addition to *data* is emerging as a major component of future interactive computer systems, in particular the VLSI design systems. This further confirms our assertion in Chapter One that next-generation VLSI design database systems should focus on the support for design processes as well as the interaction between design data and processes.

From these systems, we draw the following observations concerning the design issues of software systems that support processes.

- The first component of process support is a high-level abstraction that encapsulates primitive steps provided by the underlying environment, e.g., CAD tools in VLSI design. In most systems, this abstraction is called a *task*. Tasks address the issues of tool encapsulation and tool navigation at the same time.

- Beyond the task level, it is desirable to provide a facility that could allow domainspecific expert knowledge to be exploited in process support systems, thus offering scenario-dependent assistance beyond script-oriented tasks. The systems surveyed implemented this facility through mechanisms ranging from blackboard rules,

- predicate-transition Petri Nets, to goal-driven template matching.

- Since most future software systems, if not now, will be based on a group of computers connected through a local area network, it is essential to effectively exploit the computational resources in this type of environment. For computation-intensive engineering design environments, this issue will assume increasing importance.

- One serious drawback of all the systems surveyed, except IDEAS [MEHM87], is

the level of integration between processes and data. After all, to invoke an operation requires selection of the right tools AND the right data subset. To genuinely

facilitate tool execution, a process support system should help users track the evolution of data as well.

In Table I, we summarize the systems reviewed according to the functional requirements listed in Chapter One. *Papyrus*, as a process support facility for VLSI design, fulfills all the functional requirements and can be viewed as a meta-tool for making more efficient use of the CAD tools. Early on in the project, we decided that user-friendliness is the predominant concern. As a result, rather than drawing various complex mechanisms that handle specific scenarios, we put simplicity as the first consideration in the design of the conceptual model that guides the implementation of *Papyrus*. In the next chapter, we introduce *Papyrus*'s conceptual model. It combines some of the mechanisms of previous systems with several new ideas to form a coherent substrate for supporting VLSI design process model.

| Characteristics Summary of Process Support Systems |                       |                    |                       |                   |                       |                     |                             |

|----------------------------------------------------|-----------------------|--------------------|-----------------------|-------------------|-----------------------|---------------------|-----------------------------|

| System<br>Name                                     | Tool<br>Encapsulation | Tool<br>Navigation | Design<br>Exploration | Data<br>Evolution | Context<br>Management | Cooperative<br>Work | Distributed<br>Architecture |

| Powerframe                                         | Yes                   | Yes                | No                    | No                | Yes                   | No                  | No                          |

| vov                                                | Yes                   | No                 | No                    | No                | No                    | Yes                 | Yes                         |

| Ulysses                                            | Yes                   | Yes                | Yes                   | No                | No                    | No                  | No                          |

| Cadweld                                            | Yes                   | Yes                | Yes                   | No                | No                    | No                  | No                          |

| Hercules                                           | Yes                   | Yes                | No                    | No                | No                    | No                  | No                          |

| IDE                                                | Yes                   | Yes                | Some                  | No                | No                    | No                  | Yes                         |

| MMS                                                | Yes                   | Yes                | No                    | Yes               | No                    | No                  | Yes                         |

| IDEAS                                              | Yes                   | Yes                | No                    | Yes               | Yes                   | No                  | No                          |

| Monitor                                            | Yes                   | Yes                | No                    | No                | No                    | No                  | No                          |

| Siemens                                            | Yes                   | Yes                | Some                  | No                | No                    | No                  | No                          |

| SoftBench                                          | Yes                   | Yes                | Some                  | No                | Yes                   | No                  | No                          |

| PPA                                                | Yes                   | Yes                | No                    | No                | No                    | No                  | No                          |

| POISE                                              | Yes                   | Yes                | Some                  | No                | No                    | No                  | No                          |

| Papyrus                                            | Yes                   | Yes                | Yes                   | Yes               | Yes                   | Yes                 | Yes                         |

Table I Comparison of Process Support Systems

## Chapter 3

# The Conceptual Model

### 3.1 Introduction

Engineering design is generally characterized by two types of activities: exploration and cooperation. Designers usually explore various alternatives before settling down a particular design decision. Design exploration typically takes the form of creating versions of objects, and choosing the best subset of object versions according to certain criterion. As the design complexity increases, keeping track of the correspondence between object versions and design decisions, which we call version mapping, becomes a difficult problem in practice. To address the version mapping problem, the system should maintain a separate "context" for each design decision, and allows users to visit these contexts without being confused. For conceptual clarity, the notion of context should be tied to the processes that create contexts.

Engineering design is also almost always a group effort. Designers cooperate by sharing data, e.g., they assemble components and reuse common modules. Uncontrolled data sharing could lead to inconsistency due to un-coordinated updates to shared objects.

There is a consensus in the database research community that two-phase locking<sup>1</sup> is inadequate because of the long lifetime of these so-called *long-lived transactions* (as distinguished from *database transactions* in commercial data processing, whose lifetime is relatively short.), and hence the degraded concurrency. A better approach, particularly in an interactive design environment, is to take an optimistic concurrency control approach and to make it relatively easy to resolve conflicts when they arise.

If one models a CAD tool invocation (called a design step hereafter) as an indivisible operation against a shared database (e.g., a file system), then it is natural to model a sequence of design steps as a conventional database transaction. Various models [BANC86] [KAIS90] [PUKA90] [WIDY86] have been proposed that either provide complicated transaction structures or relax serializability<sup>2</sup>, with a view to enhancing concurrency among long-lived transactions. However, a closer examination reveals that certain properties of engineering design activities simply preclude the application of database transactions. Notable among them are interactivity, which implies that it is impossible to confine a designer's data access behavior to a particular pattern, e.g., locking objects in two phases, and open-endedness, which means that there is no commit operation as in database transactions.

In the course of developing a process model to support engineering design, it gradually becomes clear that the model should stand at a higher level of abstraction than database transactions. Rather than maintaining data integrity and enhancing concurrent data access, the design process model is supposed to support design exploration and cooperative work. For that matter, even long-lived transaction models are not appropriate. On the other hand, we find that the concept of data visibility can adequately support both design context maintenance and cooperative data sharing. Data visibility is the abstraction that controls whether a piece of data is visible to the outside world. Based on this abstraction, we develop a so-called light-weight transaction model (LWT), which

<sup>1.</sup> In a two-phase locking scheme, a transaction can't acquire more locks after it starts to release locks.

<sup>2.</sup> An execution schedule of concurrent transactions is serializable if the effect on the database is as if these transactions are executed in some serial order.

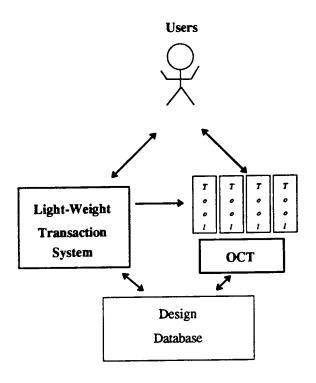

provides a set of operational constructs for users to manage the visibility of the data objects interactively and dynamically. Just as a light-weight process doesn't carry as much state as a normal process, a light-weight transaction doesn't provide as much integrity guarantee as a normal transaction. Specifically the light-weight transaction model provides constructs for controlling data visibility rather than guaranteeing data integrity. Moreover, a system based on the LWT model is built on top of a conventional database transaction facility that enforces all-or-nothing atomicity at the physical storage level. In our case, since a design step, which corresponds to a UNIX process, is modeled as an indivisible operation, the LWT system delegates the concurrency control and error recovery issues within a tool execution to the underlying design database management system, i.e., OCT. As shown in Figure 3.1, concurrent accesses to the design database are controlled by OCT, while users interact with a light-weight transaction system to manage their design process.

### 3.2 Basic Assumptions

An object is a uniquely identified piece of data, whose identifier is known to the users. An object can contain other objects. Updates to an object follows a single assignment semantics. Modifications to an object are not performed in place, but made to a copy of the original object, thus creating a new version of the object. Version numbers are managed by the system, which automatically provides a new version number whenever a new object version is created. Under the semantics of single assignment update, an update can be viewed as a transformation, with the old version as the input and the new one as the output.

The fundamental principle of the LWT model is that visibility dictates accessibility. Users can only access those objects that are visible to them, and visibility can change depending on the context from which a design operation is issued. The system enforces access control by properly managing the data visibility to individual users. When an object is accessed, the system verifies whether that object is visible to the user that issues the access operation.

Figure 3.1 Relationship Between a Light Transaction System and Its Underlying

Database Management System

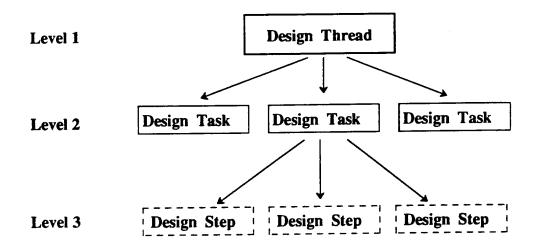

## 3.3 Light Weight Transaction Model

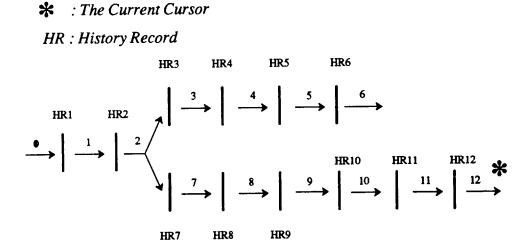

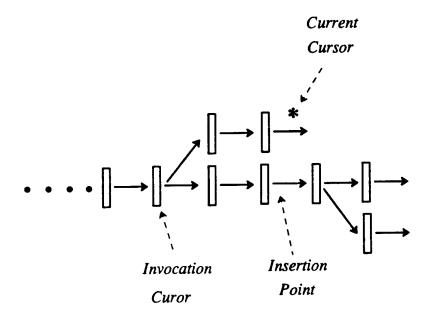

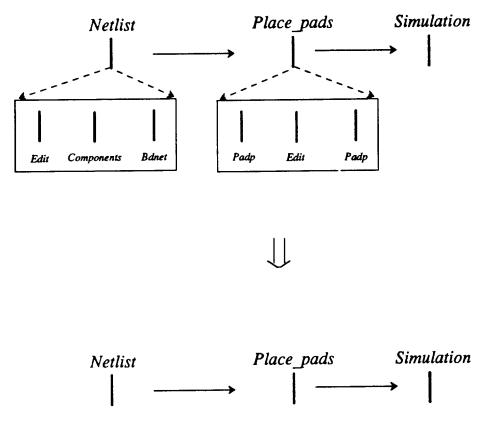

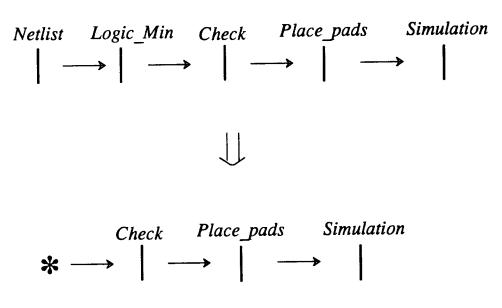

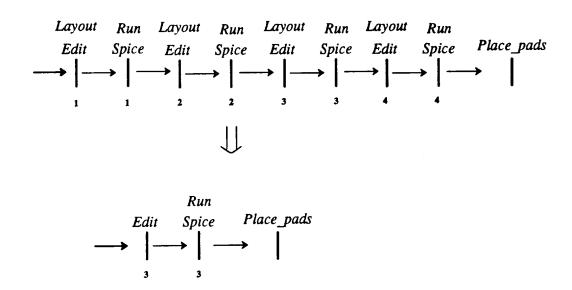

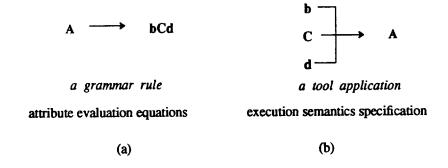

As in previously proposed models, our Light Weight Transaction (LWT) model provides a hierarchy of operational constructs for users to manage their design process. As shown in Figure 3.2, there are three levels in this hierarchy, each of which is intended for a specific purpose and provides a different set of visibility control operations. *Papyrus* is an implementation of the LWT model. Briefly, a *design step* corresponds to an individual CAD tool invocation. A *design task* provides users with a higher-level abstraction than primitive CAD tool executions, thus serving the purpose of tool navigation, automation, and encapsulation. A *design thread*, consisting of a set of design tasks and the data objects involved in the tasks, is meant to be the focal point for collecting the design operations and objects related to a logical design entity, e.g., an arithmetic logic unit (ALU). Design tasks automate routine design work while design threads support

Figure 3.2 The Light Weight Transaction Hierarchy

interactive exploration of design space.

## 3.3.1 Design Step