## Design Synthesis of Monolithic CMOS Operational Amplifiers

By

#### Han Young Koh

B.S. (Seoul National University) 1980 M.S. (Georgia Institute of Technology) 1984

## DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

in

## ENGINEERING ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

in the

#### GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA at BERKELEY

| Approved: Carlo H. Seguin. | April 17, 1989   |

|----------------------------|------------------|

| Lau Chair Gray             | Apric 17, 19.89. |

| Larles Stone               | April 17, 1929   |

| i |  |  |   |  |

|---|--|--|---|--|

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  |   |  |

|   |  |  | • |  |

|   |  |  |   |  |

|   |  |  |   |  |

# Design Synthesis of Monolithic CMOS Operational Amplifiers

Han Young Koh

Ph.D.

Department of Electrical Engineering and Computer Sciences

#### **Abstract**

This research effort explores efficient methods for the design synthesis of monolithic CMOS operational amplifiers. A synthesis system has been developed. It, called OPASYN, takes as inputs system level specifications, fabrication-dependent technology parameters, and geometric layout rules. Based on the general domain of the specifications, the program first selects an appropriate circuit topology from a database using heuristic pruning of the decision tree. Optimal values for the set of design parameters of the chosen circuit are then determined so as to meet the design objectives. Analytic models of several widely applicable operational amplifier circuit topologies have been developed to eliminate expensive circuit simulation and sensitivity analysis in the inner loop of the optimization step. Subsequently, design-rule-correct mask geometries are constructed using a macro cell layout style. Primitive circuit elements such as transistors, transistor pairs, and capacitors are produced by parameterized leaf cell generators and assembled according to circuit-dependent slicing trees that guarantee sound arrangements of the individual components. The synthesis process is fast enough for the program to be interactively used at the system design level by system designers who are inexperienced in op amp design.

Carlo H. Séquin Chairman of Committee

Vant. H. Seguin

## **ACKNOWLEDGMENTS**

I would like to express my heart-felt thanks to Professor Carlo H. Séquin and Professor Paul R. Gray for their excellent guidance and continuous encouragement. Professor David A. Hodges, my major field advisor, deserves much gratitude for his warm consideration and consistent advice ever since I started my graduate study. I also appreciate Professor A. Richard Newton, who was one of my qualifying examination committee members, for his interest and support on this work. Without their help, this work could not have been successful.

I am also grateful to the Berkeley CAD group as well as many other graduate students for their contributions. Deog-Kyoon Jeong has provided a great deal of constructive feedback at the beginning of this work. Special thanks are due to Jeff Burns who helped me to understand the operation of his spacing program, SPARCS. Rick Spickelmier, David Harrison, and Peter Moore taught me how to use the CAD framework developed by the Berkeley CAD group. I would also like to thank Hyunchul Shin for providing his router, MIGHTY. I appreciate Beomsup Kim, Yuh-Min Lin, Gani Jusuf, Glenn Adams, and Ping-San Tzeng for their various contributions.

Finally, I would like to express my heart-felt thanks to my parents and my wife who have supported me with their love and patience throughout my Ph.D program.

#### **DEDICATION**

This dissertation is dedicated to my parents, Hye Sook Chun and Bum Seo Koh, and my beloved wife, Hyeri Koh. They have made a big sacrifice to make it possible for me to pursue my graduate studies and they have continuously encouraged me with their wonderful love. Thus this ph.D. thesis is the result of all our joint efforts.

|   |   |  |  | ~ |

|---|---|--|--|---|

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

| ! |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   | , |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

|   |   |  |  |   |

# TABLE OF CONTENTS

| Acknowledgments                                | ii  |

|------------------------------------------------|-----|

| Dedication                                     | iii |

| Table of Contents                              | iv  |

| Chapter 1. Introduction                        | 1   |

| Chapter 2. Synthesis of CMOS OP Amps           | 7   |

| 2.1 Background                                 | 7   |

| 2.2 Performance Objectives                     | 9   |

| 2.3 Generic Architectures for OP Amps          | 11  |

| 2.3.1 Two-Stage Architecture                   | 11  |

| 2.3.2 Single-Stage Architecture                | 17  |

| 2.3.3 Fully Differential Architecture          | 20  |

| 2.3.4 Class AB and Dynamic Architectures       | 23  |

| 2.4 Conventional Synthesis Procedure           | 25  |

| 2.5 Review of Automatic Synthesis Systems      | 30  |

| Chapter 3. OPASYN: A Compiler for CMOS OP Amps | 34  |

| 3.1 System Overview                            | 34  |

| 3.2 OPASYN and the Berkeley CAD Environment    | 39  |

| Chapter 4. Heuristic Circuit Selection         | 43  |

| 4.1 Alternatives                               | 43  |

| 4.1.1 Creating New Topologies                         | 44 |

|-------------------------------------------------------|----|

| 4.1.2 Modifying Seed Topologies                       | 45 |

| 4.1.3 Selecting from Proven Topologies                | 49 |

| 4.2 Heuristic Pruning of the Decision Tree            | 50 |

| 4.3 Implementation                                    | 56 |

| 4.3.1 Implementation Requirements                     | 56 |

| 4.3.2 A Rule-Based Systems Implementation             | 56 |

| Chapter 5. Parametric Circuit Optimization            | 61 |

| 5.1 Sizing a Circuit Schematic                        | 61 |

| 5.2 Analytic Circuit Models                           | 63 |

| 5.2.1 Definition                                      | 63 |

| 5.2.2 Model Acquisition                               | 67 |

| 5.2.3 An Example — A Basic Two-Stage OP Amp           | 68 |

| 5.2.3.1 Design Parameter Selection                    | 68 |

| 5.2.3.2 Parameter Range Setting                       | 70 |

| 5.2.3.3 Derivation of Analytic Design Equations       | 71 |

| 5.3 Parameter Space                                   | 77 |

| 5.3.1 Formation of Parameter Space                    | 77 |

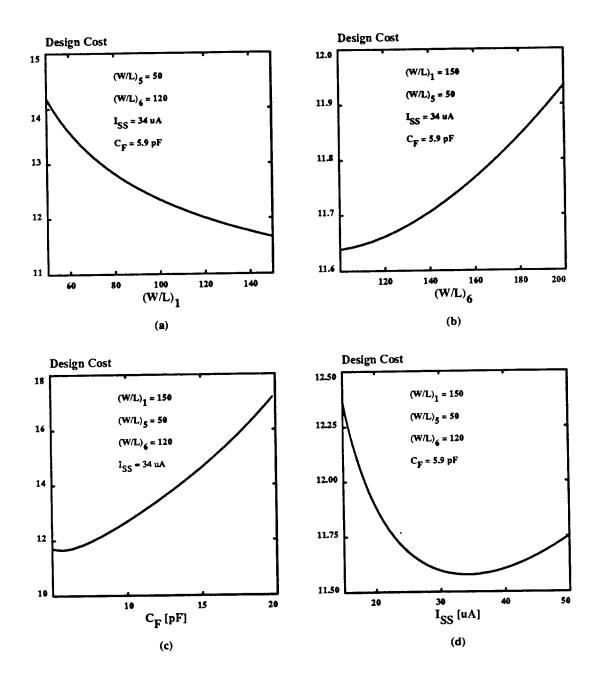

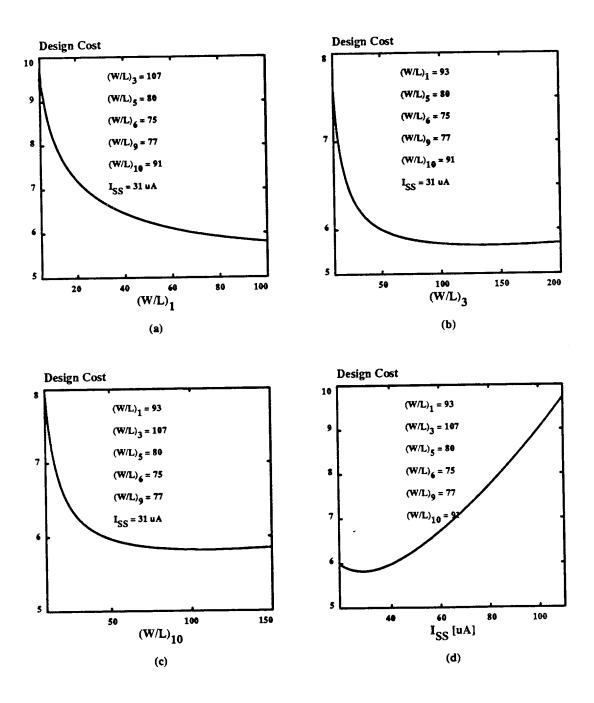

| 5.3.2 Characteristics (Smoothness) of Parameter Space | 82 |

| 5.4 Optimization Strategy                             | 82 |

| 5.5 Further Discussions                               | 87 |

| 5.5.1 Fine Tuning the Analytic Models                 | 87 |

| 5.5.2 Other Optimization Methods                      | 88 |

| Chapter 6. Layout Generation                | 89  |

|---------------------------------------------|-----|

| 6.1 Layout Requirements for Analog Circuits | 89  |

| 6.2 Cell Generation for Analog Circuits     | 95  |

| 6.2.1 Cell Generators Versus Cell Libraries | 95  |

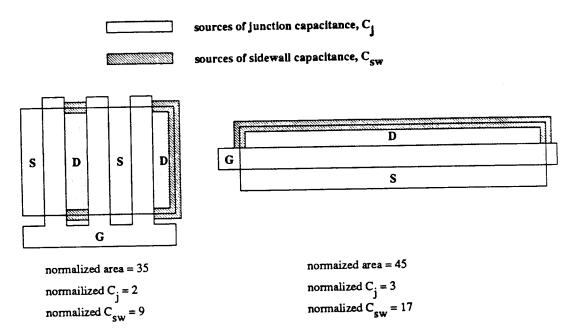

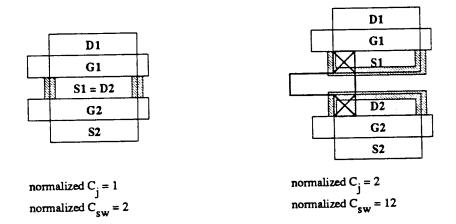

| 6.2.2 Leaf Cell Generators in OPASYN        | 97  |

| 6.3 Floorplanning                           | 100 |

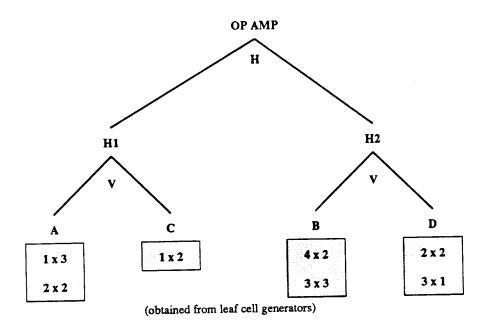

| 6.3.1 Use of Slicing Trees                  | 100 |

| 6.3.2 Floorplanning Algorithm               | 103 |

| 6.3.2.1 An Overview                         | 103 |

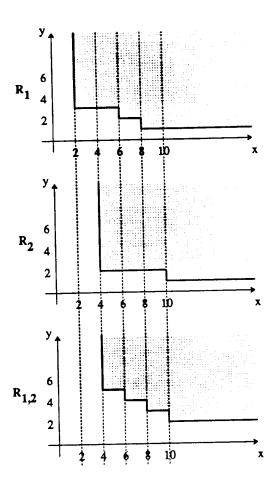

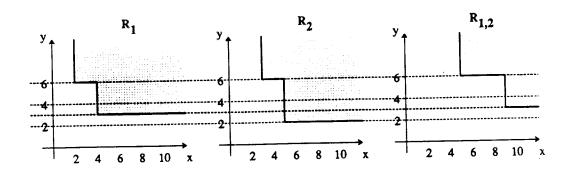

| 6.3.2.2 Stockmeyer's Algorithm              | 104 |

| 6.3.2.3 Algorithm — OPASYN_FLOORPLAN        | 110 |

| 6.4 Routing                                 | 110 |

| 6.4.1 Routing Requirements                  | 110 |

| 6.4.2 Routing Strategy                      | 117 |

| 6.5 Layout Spacing                          | 118 |

| 6.5.1 Layout Spacing Requirements           | 118 |

| 6.5.2 Spacing Strategy                      | 119 |

| Chapter 7. Experimental Results             | 120 |

| 7.1 Implementation                          | 120 |

| 7.2 A Synthesis Example                     | 121 |

| 7.3 Performance Evaluation                  | 125 |

| 7.3.1 Run Times                             | 125 |

| 7.2.2. Quality of Results                   | 125 |

| Chapter 8. OPASYN as a Component in a Larger Synthesis System | 137 |

|---------------------------------------------------------------|-----|

| 8.1 Concept                                                   | 137 |

| 8.2 An Example — A SC-Filter Compiler                         | 139 |

| 8.3 Macromodeling of OP Amps                                  | 143 |

| 8.3.1 Circuit Theoretical Backgrounds                         | 143 |

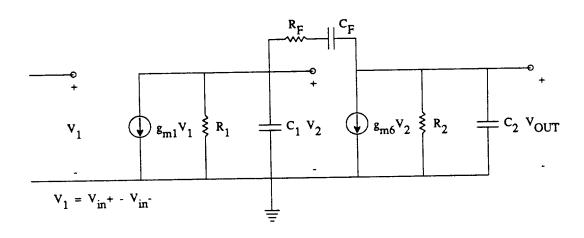

| 8.3.2 An Example — A Two-Stage OP Amp                         | 149 |

| Chapter 9. Conclusions                                        | 152 |

| References                                                    | 155 |

| Annendix                                                      | 162 |

## **CHAPTER 1**

## INTRODUCTION

The pervasive trend in recent years towards the integration of whole systems into a single chip VLSIC's requires that both digital functional units and dedicated analog interface subsystems (such as A/D converters and filters) be implemented onto the same chip. Many digital parts of such chips can nowadays be synthesized rapidly and reliably using CAD tools developed for semicustom design methods such as gate arrays, standard cells, and macro cells. On the other hand, analog interface subsystems still need to be fully hand-crafted by a specialist. Therefore, the design time and cost associated with dedicated analog interface components often constitute a bottleneck in semicustom design of mixed analog/digital systems such as voiceband data modems and high speed data transceivers. <sup>1</sup>

For semicustom design of analog circuits, building blocks may be stored in the form of parameterized generators or as entries in macro cell or standard cell libraries.<sup>2,3,4,5</sup> As in the digital domain, the usage of libraries of predefined analog building blocks can shorten the design period significantly. However, in the analog domain it is difficult to configure a rich enough set of library cells for the wide spectrum of possible applications. Performance specifications for analog building blocks are much more diverse and complicated than those for digital blocks. For a digital inverter, delay and area are the major performance specifications. On the other hand, specifications for an operational amplifier (op amp) may include power dissipation, small signal dc gain, bandwidth, phase margin, slew rate, settling time, output voltage swing, 1/f noise, area, and so forth. Some of these specifications, such as the small signal dc gain of a CMOS op amp may vary over a wide range, depending on applications and system architectures being used. Furthermore, analog library entries

become obsolete even more quickly when technology or design rules change. A performance characteristic such as 1/f noise of a CMOS op amp degrades as technology scales down while that for small signal dc gain improves. As a result, generators that operate at the circuit or netlist level are more flexible and can be useful over a much larger domain of applications than fixed library cells. With such generators, design parameters (such as device sizes or bias currents) of a building block can be individually optimized for a particular application and for the particular technology to be used. The physical layout geometry of the block with its optimal design parameter values is then also produced by the generator.

The most often used analog building block is the operational amplifier. It is at the heart of many interface circuits, in particular, A/D and D/A converters, and filters. An efficient design of optimal op amps is thus a corner-stone of a design environment for many applications. As discussed above, op amp specifications for different applications vary so widely that it is impractical to store op amps as library cells for all applications. Using one of a few 'standard' library cells that are poorly matched to a particular application is unacceptable; if the performance of the op amp falls below a certain 'threshold', the quality of the overall system will suffer.

Designing a good op amp is a rather complicated multi-facet task. 6,7 An op amp topology appropriate for the given specifications must be chosen. Then its design parameters such as device sizes and bias currents must be adjusted under multiple design objectives and constraints. The many degrees of freedom in parameter space as well as the need for repeated circuit performance evaluation make this a lengthy and tedious process. This circuit optimization can be carried out by a computer but the process is still expensive and requires a skilled operator. The optimized circuit needs then to be transformed into mask level geometries. The layout process is critical for good performance since op amps like other analog circuits are sensitive to parasitic elements, to process/thermal gradients, and to noise. In CMOS technology, device sizes in op amps vary over a large range of values.

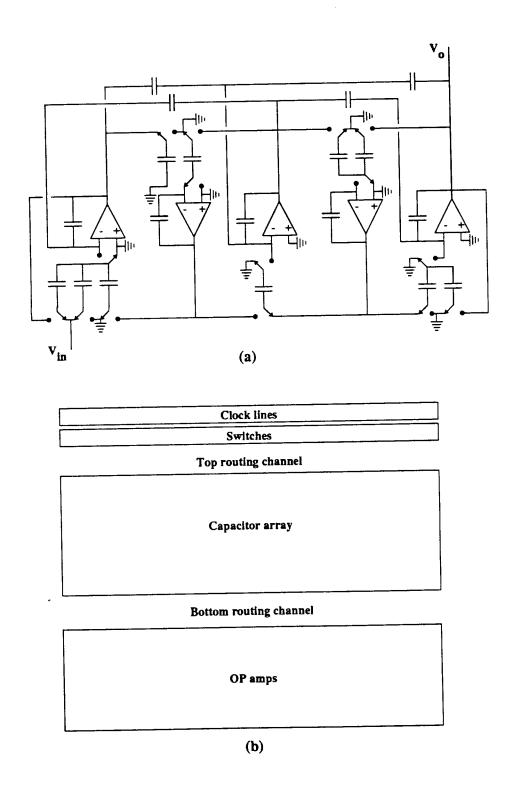

Some devices may have many alternative shapes, and terminal configurations. Thus, most of the classical layout generation methods developed for digital IC's are insufficient for CMOS op amps. 8,9,10,11,12 As a result, work on automatic layout of monolithic switched capacitor filters uses op amps as fixed cells from a library. 13,14,15 For many applications, this approach does not give enough flexibility and performance.

Most of the work published on the automated synthesis of op amps concern the schematic generation and parametric optimization of op amp circuits. The most common approaches are based on optimization, an expert systems approach, or a combination of both. The optimization-based approach uses various optimization algorithms combined with circuit simulation techniques to produce general purpose parametric optimization tools. 16, 17, 18 Since no a priori circuit design knowledge is necessary, this approach is applicable to a broad range of analog circuits. High degrees of optimality can be obtained through the use of robust and elaborate optimization algorithms. However, optimization tools based on this approach are not tailored to be used by novice designers. For instance, a system designer who wants to design an op amp for his/her A/D converter, has to provide the system with detailed design knowledge on op amps such as how to calculate slew rate from a particular node voltage. Besides, the designer must determine from manual or other design techniques a good initial guess for each design parameter. Without such a good starting point, an optimization run can converge very slowly or converge to a local minimum whose performance is significantly worse than the circuit's best capabilities. 17 This approach is normally very costly in CPU time because repeated circuit simulation is performed in the inner loop of the optimization step.

In the knowledge-based approach, domain specific knowledge has been used to produce synthesis tools which emulate expert designer's design processes. 19, 20, 21, 22, 23 The domain specific design knowledge integrated into these systems permits novice designers to specify simply their design requirements. Fine tuning of the system for a specific application area

can also be achieved easily. But a large complicated search space occurring from design of op amp circuits and a lack of an efficient performance estimation method make it difficult and inefficient to perform design optimization using this approach. In addition, a priori design knowledge has to be integrated into the system whenever a new type of building block is added. A general synthesis system that starts from first principles of circuit design such as Kirchoff's current and voltage laws does not yet exist!

Alternatively, advantages of both approaches can be combined to devise synthesis tools whose optimization is done in an algorithmic way but substitutes expensive circuit simulation with algebraic evaluation of analytic design equations acquired from domain specific design knowledge.<sup>24</sup> This is the approach taken by OPASYN described in this paper.

Automatic layout generation for CMOS op amps has been less widely explored. 25, 23, 26 The approaches rely either on dedicated slicing trees 25, 23 or use a general-purpose layout program based on simulated annealing and constraint-based routing. 26

This thesis describes a design synthesis tool for monolithic CMOS op amps (OPASYN), that starts from a set of performance specifications (open loop gain, bandwidth, slew rate, etc) and produces design-rule-correct mask geometries in a macro cell layout style.

In Chapter 2 the performance objectives and generic architectures for op amps are introduced. The conventional synthesis procedure for op amps is examined and automatic synthesis systems for op amps are reviewed. The section is intended to provide background material necessary for understanding the OPASYN compilation method.

Chapter 3 presents an overview of an analog silicon compiler for CMOS op amps (OPASYN) developed using the described method. The framework of the program is delineated, and the function of each program module is explained. The OPASYN's interface to

the Berkeley CAD environment is also discussed.

In Chapter 4 a heuristic circuit selection method is explained. The method is used to select a promising op amp circuit topology based on the user specifications from the alternatives provided in the database. This is contrasted with other methods, such as creation of a new architecture in hierarchical manner, and incremental modification of topologies, and the difficulties and impracticalities of these approaches are discussed. The implementation of the method as a rule-based system is presented.

In Chapter 5 the problem of parametric optimization in op amp synthesis is addressed and a new optimization method using 'analytic circuit models' of op amps is discussed in detail. Analytic circuit models are defined and their acquisition process is presented. The shape of the parameter space is examined for the op amps used in OPASYN and the optimization strategy developed for this parameter space is described. Other optimization methods are briefly reviewed and discussed.

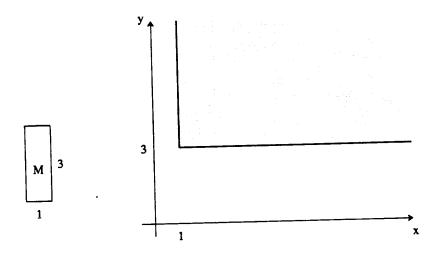

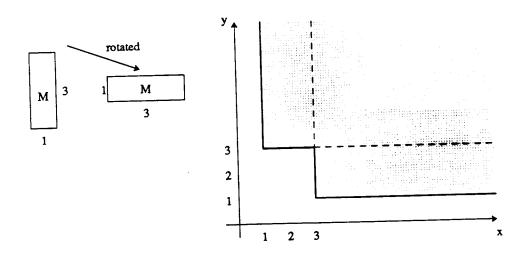

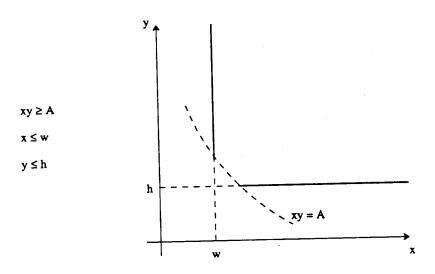

Chapter 6 is concerned with layout generation. Layout requirements for analog circuits and the needs for analog cell generators (instead of analog cell libraries) are discussed. A new floorplanning method based on parameterized cell generators and 'circuit dependent slicing trees' (also known as 'decomposition tree') is first described. It is then explained how Stockmeyer's algorithm can be used to determine optimal shapes for the various modules according to the user's shape constraint. Routing and layout spacing strategies are also described.

In Chapter 7 the implementation of OPASYN and experimental results obtained with the program are discussed. A synthesis example, that starts from a set of performance specifications and completes with an op amp layout in mask geometries, is provided to illustrate the design data flow in the system.

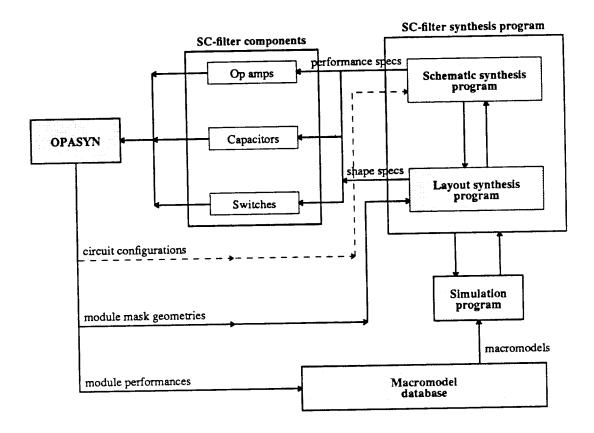

In Chapter 8 the problem of incorporating OPASYN as a module generator into larger

synthesis systems for switched capacitor filters and A/D converters is addressed. Subsequently, macro modeling for op amps is discussed.

Conclusions based on this research are presented in Chapter 9.

## **CHAPTER 2**

# SYNTHESIS OF CMOS OP AMPS

# 2.1 Background

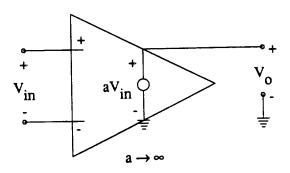

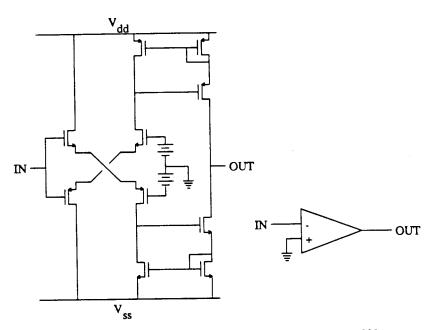

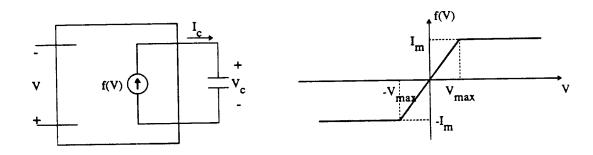

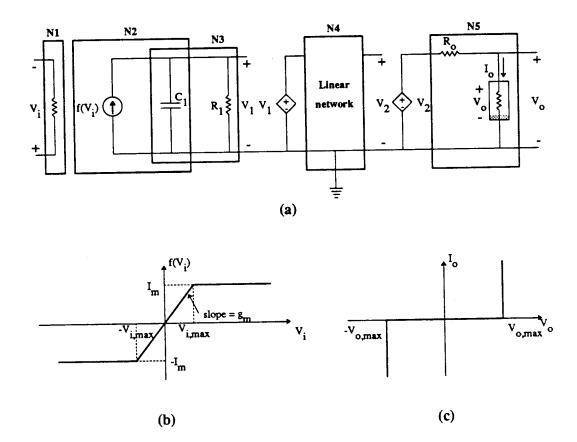

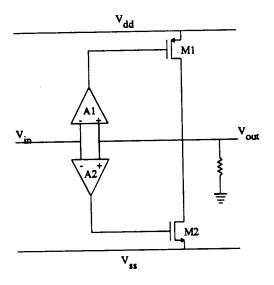

An ideal operational amplifier (op amp) is a differential input, single-ended output amplifier with infinite gain, infinite input resistance, zero output resistance, and no internal delay. A conceptual schematic diagram is shown in Fig. 2.1. While actual op amps do not have these ideal characteristics, their performance is usually sufficiently good that in most applications the circuit behavior closely approximates that of an ideal op amp. With the advent of monolithic-circuit technology, the cost of monolithic op amps has been strongly reduced, and as a result op amps are widely used in the design of all types of analog systems. They are key elements of most analog subsystems, particularly in switched capacitor filters, and the performance of many systems is strongly influenced by the performance of the op amps used.

Figure 2.1 Ideal operational amplifier.

Traditionally, monolithic op amps have been fully hand-crafted by expert designers, either as components in high-volume, cost-sensitive interface subsystems, or as general-

purpose SSI building block elements. However, the large design time and cost associated with full custom design is hardly justified if volume of production is low or if time to market requirements are more important than component costs as is the case in application-specific and customer-specific IC design problems. Suitable synthesis tools must be developed allowing a system engineer who is not an expert analog designer to successfully carry out design, layout, and verification for complex op amps matched to a particular application.

Op amps have been implemented in many different technologies: bipolar, NMOS, CMOS, and BiMOS technologies, depending on such variables as current drive required, requirement for low dc offset voltages, requirement for low power dissipation, requirement for operation at high supply voltages, etc. Currently, general-purpose SSI op amps are mostly implemented in bipolar technology because of its capability of providing high current drive, high gain, and low dc offset voltage. When used as components in dedicated analog interface subsystems such as A/D converters and SC-filters, op amps are implemented exclusively in CMOS technology due to high complexity of on-chip logic functions required in such subsystems. When implemented in BiMOS technology, op amps can have advantages available in both bipolar and CMOS technologies: high input impedance, low dc offset voltages, high current drive capability, etc. However, the larger number of processing steps required for BiMOS technology limits its popularity. In this chapter, only work on CMOS op amps is reviewed because of its prevailing usage in semicustom IC design.

In Section 2.2, the important performance requirements and objectives for op amps within monolithic analog subsystems are discussed. In Section 2.3, generic op amp architectures are introduced and their performance ranges are examined. In Section 2.4, traditional ways of designing op amps are discussed. Finally, automatic synthesis systems for op amps are reviewed in Section 2.5.

# 2.2 Performance Objectives

The performance requirements for op amps to be used within a monolithic analog subsystem are often quite different from those of traditional stand-alone bipolar amplifiers. Perhaps the most important difference concerns output drive capability. For the amplifiers in a monolithic system, the load that each of the amplifiers has to drive is well defined, and is often purely capacitive with values of a few picofarads. In contrast, stand-alone general-purpose op amps must be designed to achieve a certain level of performance independent of loading for capacitive loads up to several hundred picofarads and resistive loads down to 2  $k\Omega$  or less. Within a monolithic analog subsystem, only a few of the amplifiers must drive a signal off chip where the capacitive and resistive loads are significant and variable. In this thesis, these amplifiers are termed 'output buffers', and the amplifiers whose outputs do not go off chip are termed 'internal amplifiers', following Gray and Meyer. From this point on, internal operational amplifiers will be simply called 'op amps'.

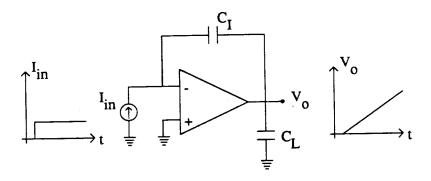

Figure 2.2 Typical application of an internal MOS operational amplifier, a switched capacitor integrator.

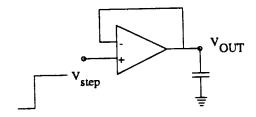

A typical application of an op amp, a switched capacitor integrator, is illustrated in Fig. 2.2. The basic function of the op amp is to produce an updated value of the output in response to a switching event at the input in which the sampling capacitor  $C_I$  is charged from the source and discharged into the summing node. The output of the integrator must assume

the new updated value within the required accuracy, typically on the order of 0.1 percent of the final value, within one clock period (typically on the order of 1 µsec for voiceband filters). It should also be capable of swinging fully between the upper and lower limits specified by the filter designer: The dynamic range of the filter (defined as the ratio of the largest input signal to smallest input signal discernible above the noise level) is strongly dependent on these limits because for multiple stage filters, the input of the present stage comes from the output of the previous one. On the other hand, the smallest input signal treatable by the integrator is limited by noise coming from the op amp, the switch, etc. Accordingly, the noise of the op amp should be also minimized.

Figure 2.3 Typical application of an internal MOS operational amplifier, algorithmic A/D converter.

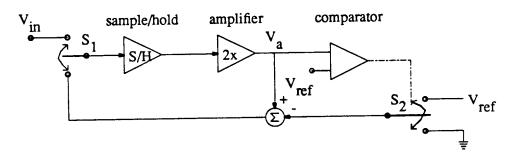

Let's look at another application, an algorithmic A/D converter shown in Fig. 2.3.<sup>27,28</sup> The op amp in this case works as a multiply-by-two block as required by the following conversion technique:

At the start of conversion, the input signal is sampled onto the sample/hold amplifier through the switch  $S_1$ . This signal is then passed onto the precision gain block (op amp) where it is multiplied by the exact factor of 2.0. To extract the digital information from this analog signal, the loop signal, denoted by  $V_a$  in Fig. 2.3, is compared to the reference. If it is larger, then the first bit is set to 1 and the reference is subtracted off from this signal. Otherwise the first bit is set to a 0 and the loop signal is passed on untouched for the second bit conversion.

The A/D conversion process is continued in this manner until the desired number of bits is obtained. The digital information thus comes out in a serial pattern, starting with the most significant bit.

The op amp must provide an 'exact' gain of 2.0 and its output must be settled within one clock period which can be on the order of a few tens of nanoseconds for video and radar signal processing applications. The noise characteristics and the output swing capability of the op amp are also important in terms of the converter's resolution and dynamic range.

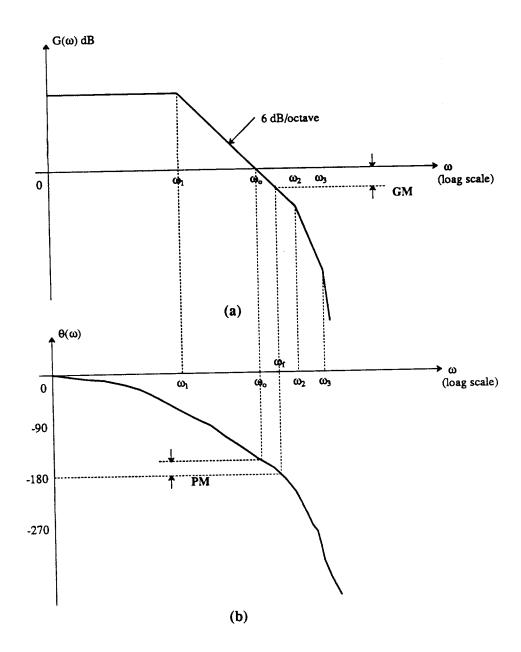

When considered for a wide spectrum of applications, the important performance characteristics for op amps concern power dissipation, maximum allowable capacitive load, open-loop voltage gain, unity-gain bandwidth, output voltage swing, equivalent input flicker noise, equivalent thermal noise, power supply rejection ratio (PSRR), common-mode rejection ratio (CMRR), common-mode range (CM range), supply capacitance and die area. However, for a specific application, some of these parameters are less important than others: For instance, when an op amp is used as an integrator in a switched capacitor filter, input offset voltage, common-mode rejection ratio, and common-mode range are less important but they can be important in other applications. A typical set of values for the parameters given above for a conventional amplifier design in 4 µm CMOS technology are given in Table 2.1.

# 2.3 Generic Architectures for OP AMPs

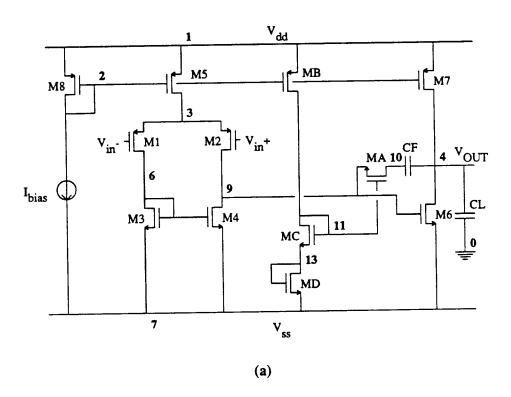

## 2.3.1 Two-Stage Architecture

Currently, the most widely used architecture for the implementation of MOS op amps is the two-stage configuration shown in Fig. 2.4(b) which is derived from its bipolar counterpart illustrated in Fig. 2.4(a). This circuit configuration provides good common-mode range, output swing, voltage gain, and CMRR in a simple circuit that can be compensated with a

Table 2.1

Typical performance, conventional two-stage CMOS

Internal operational amplifier

(+/-5 V supply, 4 µm SI-gate CMOS)

| Dc gain (capacitive load only)        | 5000                 |

|---------------------------------------|----------------------|

| Settling time, 1 V step, $C_L = 5 pF$ | 500 nsec             |

| Equiv. input noise, 1 kHz             | 100 nV∕⁄Hz           |

| PSRR, dc                              | 90 dB                |

| PSRR, 1 kHz                           | 60 dB                |

| PSRR, 50 kHz                          | 40 dB                |

| Supply capacitance                    | 1 fF                 |

| Power dissipation                     | 0.5 mW               |

| Unity-gain bandwidth                  | 4 MHz                |

| Die area                              | $75 \text{ mil}^2$   |

| Systematic offset                     | 0.1 mV               |

| Random offset std. deviation          | 2 mV                 |

| CMRR                                  | 80 dB                |

| CM range                              | within 1 V of supply |

|                                       |                      |

single pole-splitting capacitor.

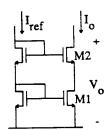

However, in precision applications involving large values of closed-loop gain, the voltage gain available from the basic circuit shown in Fig. 2.4(b) may be inadequate. One approach to improving the voltage gain, without adding an additional common-source stage with its associated high impedance node and pole is to add a common-gate or 'cascode' transistor to increase the output resistance of the basic amplifier. The basic cascode circuit is shown in Fig. 2.5. It is easily demonstrated that the incremental output resistance of this current source is equal to

$$r_o = r_{o2}(1 + g_{m2}r_{o1}) + r_{o1}$$

The output resistance is increased by an amount equal to the open circuit gain of the cascode transistor. This circuit may be directly applied to the basic two-stage amplifier in either the first stage, the second stage, or in both stages. The circuit of Fig. 2.6 illustrates the use of cascodes in the first sage. However, a substantial reduction in input stage common-mode range has been incurred which should be alleviated by optimizing the biasing of the cascodes.

The negative PSRR of the basic two-stage architecture can be improved as follows: Conceptually, if the left end of a capacitor could be connected to a virtual ground, then the capacitor voltage would not have to change whenever the negative supply voltage changed in order to have the output remain constant. This is accomplished by inserting a cascode device in this loop with the gate connected to ground, as shown in Fig. 2.7. The displacement current from the capacitor flows into the source of this transistor and out the drain into the compensation point. An additional current source and current sink of equal values (denoted as I's in Fig. 2.7) must be added to bias the common-gate device in the active region and so as not to contribute any systematic offset. The resulting negative PSRR at high frequencies is greatly improved at the cost of a slight increase in complexity, random

Figure 2.4 Two-stage operational amplifier architecture.

(a) Bipolar implementation. (b) CMOS implementation.

Figure 2.5 Cascode current source.

Figure 2.6 Two-stage architecture with cascoded first stage.

Figure 2.7 Two-stage architecture with cascode feedback compensation.

offset, and noise.7

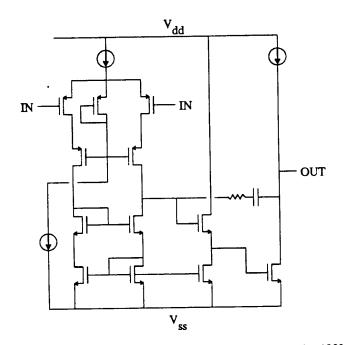

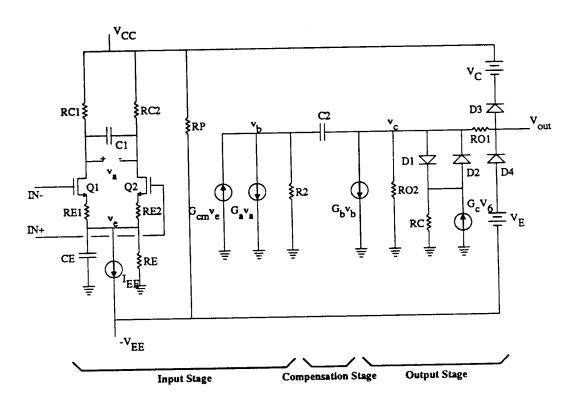

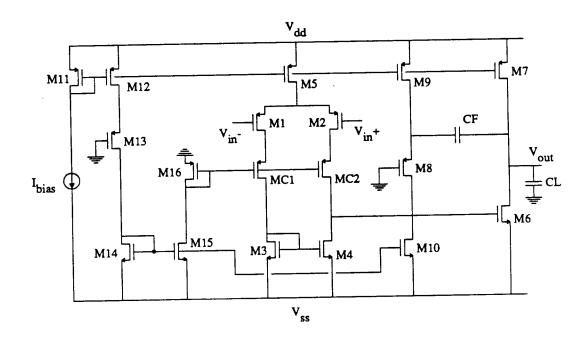

Ahuja also described a modified two-stage architecture shown in Fig. 2.8, where an enhanced compensation technique provides stable operation for a much larger range of capacitive loads as well as much improved negative power supply rejection for very wide frequency range.<sup>29</sup>

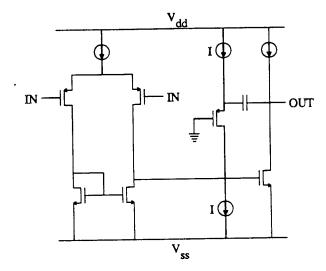

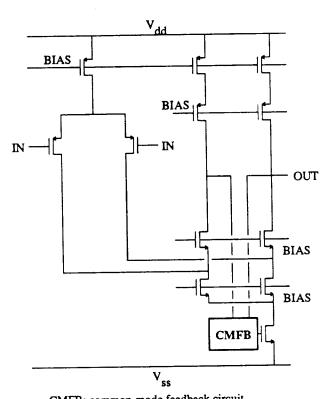

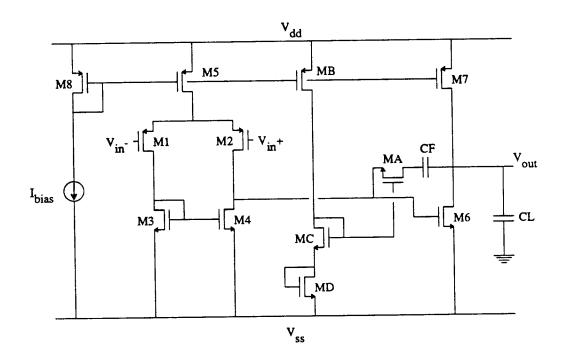

## 2.3.2 Single-Stage Architecture

The basic two-stage architecture considered thus far is actually a cascade of two common-source stages. An alternative approach is to use a cascade of a common-source stage and a common-gate stage, often called a cascode amplifier. An example of an amplifier utilizing this architecture is shown in Fig. 2.9. The voltage gain of this circuit at dc is approximately the same as that of the basic two-stage circuit due to the increased output impedance. The principal reasons for considering this architecture are twofold. First, the compensation capacitor and load capacitor (CL) are the same element in this circuit. The first nondominant pole comes from the g<sub>m</sub>/C<sub>gs</sub> time constant of the n-channel cascode devices, and gives a pole frequency approximately at the ft of these devices. A second nondominant pole results from the differential to single-ended converter. However, the nondominant pole due to the load capacitance present in the two-stage circuit is not present in this circuit. Thus, this circuit is capable of achieving higher stable closed-loop bandwidth with large capacitive load. The principal application of this architecture has been in highfrequency switched capacitor filters. 30,31 Another important advantage of this circuit is that it does not suffer from the degradation of the high-frequency power supply rejection problem inherent in the pole-split compensated two-stage architecture, assuming that the load capacitance or part of it is not tied to a power supply. One of the disadvantages is that the output swing of this circuit is lower than the basic two-stage circuit because of the cascode transistors used at the output. A second disadvantage is that more devices contribute to the

Ref. B. K. Ahuja, IEEE J. Solid-State Circuits, 1983.

Figure 2.8 Two-stage architecture with improved frequency compensation.

Ref. P. R. Gray and R. G. Meyer, IEEE J. Solid-State Circuits, 1982.

Figure 2.9 Single-stage amplifier architecture.

input-referred flicker noise voltage and input offset voltage. Assuming that transistors M5-M8 are biased at the same current as the input devices, the input-referred flicker noise can be shown to be<sup>7</sup>

$$v_{eq}^2 = \frac{2K_p}{W_1L_1} \left[ 1 + \frac{2K_n\mu_n}{K_p\mu_p} \left( \frac{L_1}{L_9} \right)^2 + \left( \frac{L_1}{L_5} \right)^2 \right] \frac{\delta f}{f}.$$

where  $K_p$  and  $K_n$  are the flicker noise coefficients, and  $\mu_p$  and  $\mu_n$  are the mobilities for the p-channel and n-channel devices, respectively.  $C_{ox}$  is the oxide unit capacitance, and f is frequency. W's and L's are widths and lengths of the devices.

By enhancing the biasing scheme used in Fig. 2.9, the low and nonsymmetrical output voltage swing of the circuit can be alleviated. The resulting circuit configuration is shown in Fig.  $2.10.^{32}$

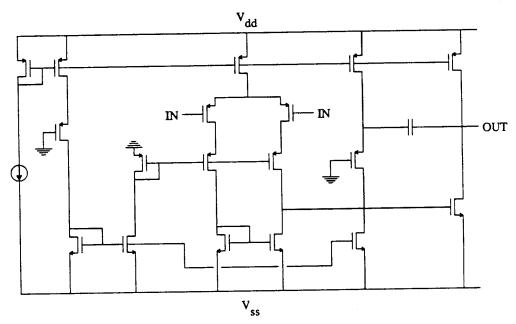

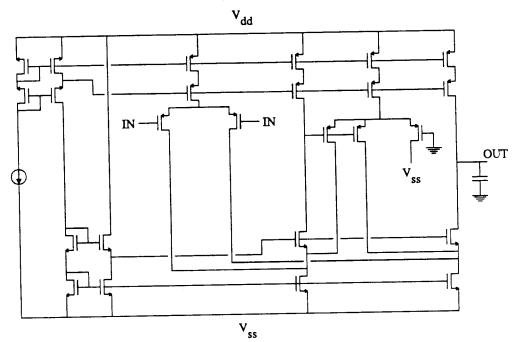

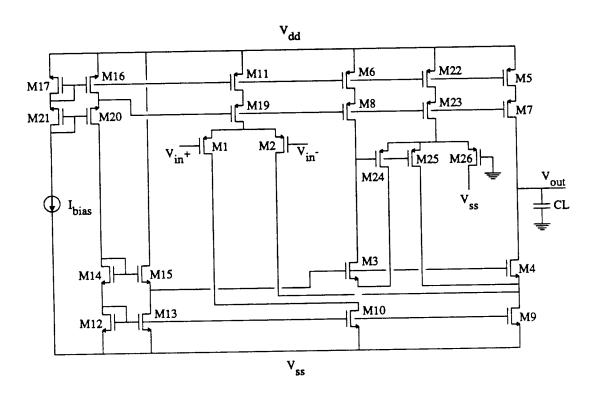

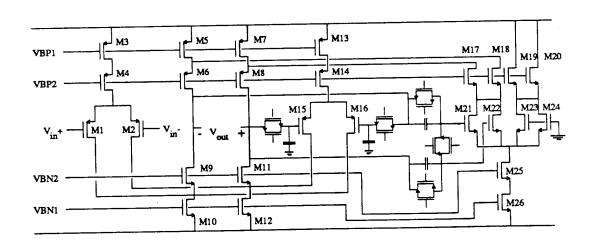

## 2.3.3 Fully Differential Architecture

Power supply rejection ratio is an important performance parameter for amplifiers to be used in complex mixed analog/digital systems. In addition, one inevitable result of technology scaling is a reduction in power supply voltage with an accompanying reduction in internal signal swings and dynamic range. 33 These two considerations make use of fully differential signal paths throughout the analog portion of the system which is attractive for some systems such as switched capacitor filters. The inherently differential nature of the circuit tends to give very high PSRR since the supply variations appear as a common-mode signal. Also the effective output swing is doubled, while the magnitude of the input-referred op amp noise remains the same, giving a 6 dB improvement in op amp noise-limited dynamic range. An example of a differential op amp architecture is shown in Fig. 2.11. An important problem in such amplifiers is the design of a feedback loop to force the common-mode output voltage to be ground or some other internal reference potential. This feedback path can be implemented with transistors in a continuous-time circuit or can be implemented with

Ref. B. K. Ahuja, IEEE J. Solid-State Circuits, 1984.

Figure 2.10 Single-stage architecure with enhanced output swing.

CMFB: common-mode feedback circuit

Ref. P. R. Gray and R. G. Meyer, IEEE J. Solid-State Circuits, 1982.

Figure 2.11 Fully differential amplifier architecture.

switched capacitor circuitry. The continuous approach is potentially simpler, but presents a difficult design problem in making the common-mode output voltage independent of the differential-mode signal voltage. 31,34 Switched capacitor circuitry can make use of the linearity of MOS capacitors to achieve this goal. 35 The choice between the two techniques depends on the sensitivity of the particular application to variations in common-mode voltage. Another important advantage of the differential architecture is that the differential single-ended converter with its associated nondominant poles is eliminated. Thus the configuration is particularly well suited to the implementation of high-frequency switched capacitor filters.

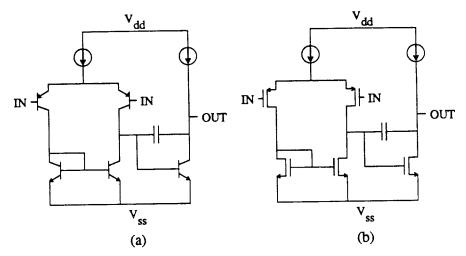

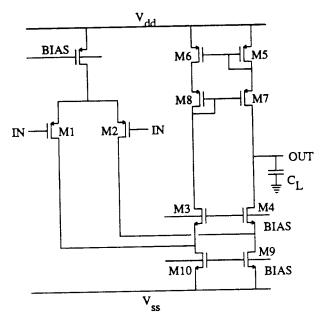

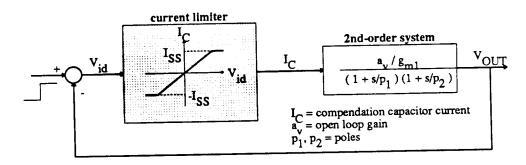

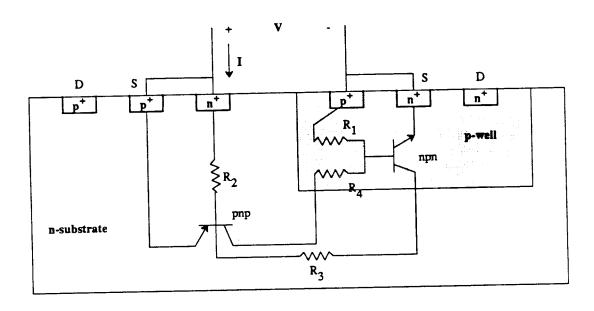

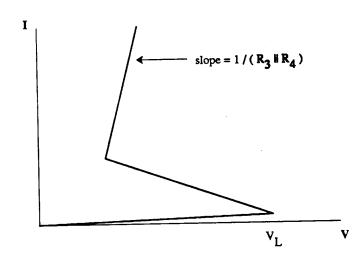

# 2.3.4 Class AB and Dynamic Architectures

In a low-power amplifier where an important objective is the minimization of chip power, a 'class AB' architecture can be effectively used. Here the term class AB is taken to mean a circuit which can source and sink current from a load which is larger than the dc quiescent current flowing in the circuit. The motivation for using class AB architecture is that one of the factors that dictate the value of the quiescent current in an MOS amplifier is the value of current required to charge the load and/or the compensation capacitor in a specified time. However, it is relatively rare that the op amp outputs actually have to change the maximum amount in one clock cycle. Large power savings can be achieved by drawing only that amount of current required to charge the capacitance on that particular cycle. An example of single-stage op amp which operates on this principle is shown in Fig. 2.12. This particular circuit can be used in the inverting mode only. With the input grounded, the quiescent current in the input transistors is determined by the bias voltage shown. Upon the application of a voltage to the input, the current in one side of the input stage increases monotonically with the applied voltage until the power supply is reached, while the other side of the input stage turns off. The amount of current available at the output is much larger

Figure 2.12 Single-stage class AB amplifier architecture.

than the quiescent current, and the circuit does not display slew rate limiting in the usual sense. Another advantage of this circuit is that the small-signal voltage gain in the quiescent mode can be quite high because of the low current level. The fact that the voltage falls off during transients because of the high current levels is of little consequence for the ac response of the circuits.

DeGrauwe et al. have described a novel approach achieving the same objective.<sup>36</sup> A conventional class A amplifier architecture is used, but an auxiliary circuit detects the presence of large differential signals at the input. The bias current in the class A circuitry is then increased when such signals are present.

Dynamic architecture has been explored by several authors. Copeland<sup>37</sup> described a configuration in which the quiescent current in the absence of signals is allowed to decay to zero. Such amplifiers are fully dynamic in the sense that no dc paths exist for current to flow from the supply. While very low power dissipation can be obtained, difficult problems of settling time and power supply rejection remain to be solved with these amplifiers. Hostica <sup>38</sup> invented a biasing scheme where the power supply current is independent of signal amplitude, and is made large during the early part of the clock period (used in the switched capacitor filter) for fast slewing and is made small during the later portion for high gain and power savings.

# 2.4 Conventional Synthesis Procedure

Op amps like other analog circuits traditionally have been fully hand-crafted by expert analog circuit designers. A conventional synthesis procedure for op amps as illustrated in Fig. 2.13 can be divided into three design phases: Circuit topology selection, device sizing, and layout generation. First, a suitable op amp circuit is selected based on the general domain of the performance specifications. Then each device in the chosen circuit is properly

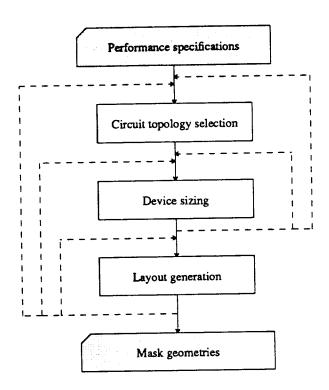

Figure 2.13 Conventional synthesis procedure for op amps - Simplified view.

sized to meet the given specifications. Finally, the sized circuit schematic is laid out in mask geometries. Feedback paths (shown in dotted lines in Fig. 2.13) around some of the design phases represent possible re-design efforts needed when the design results from those phases violate the design requirements implied by the performance specifications. Let's look at each of the design phases in more detail.

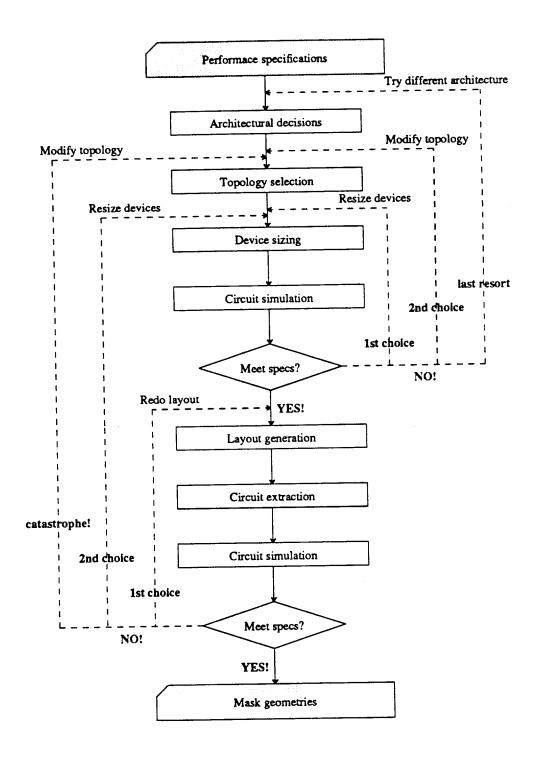

The circuit topology selection phase is subdivided into two steps as shown in Fig. 2.14. First, based on the performance specifications given and the process technology to be used, a suitable op amp architecture must be selected: Two-stage, single-stage, fully differential, dynamic, class AB, etc. Upon deciding which architecture is suitable for the particular application, a specific circuit topology is selected for the synthesis. The examples of op amp performance characteristics which are used to make such decisions include power supply voltage, power consumption, and DC transfer curve. The many possible variations of different architectures make this phase of the synthesis rather dependent on design experience. A poor selection decision made in this phase may cause a catastrophe at the end of the design cycle as shown in Fig. 2.14 or at best the designer realizes the poor decision in the device sizing phase.

In the device sizing phase the designer tries to adjust variable parameters of each device (which are called 'design parameters') so as to meet all performance specifications given. Width and length of a MOSFET, capacitance value of a capacitor, and current value of a current source are the design parameters for CMOS op amps. The design task is initiated by setting the design parameter values to achieve the desired DC characteristics (quiescent bias points). Next the designer readjusts the initial parameter values to get the specified ac (small signal) response about the quiescent points. Finally, the characteristics of the transient response are used to make further changes in the design parameter values and operating points in order to meet the performance requirements. The entire procedure is repeated until all the design requirements are satisfied. In case some of the requirements are still violated

Figure 2.14 Conventional synthesis procedure for op amps - Detailed view.

in spite of the repeated design efforts, the chosen topology is often modified in order to enhance certain performance characteristics as needed. If all these efforts go wrong, a different architecture may have to be selected as a last resort.

In fact, the afore-mentioned design task (device sizing) can be formulated as a parametric optimization problem. Given a fixed circuit topology and performance specifications, some of the variable device parameters can be selected as design parameters and the specifications can be transformed into constraints and performance objectives. Then the rest of the problem is reduced to finding the optimal values of the design parameters that maximize the performance objectives while keeping all constraints satisfied. Chapter 5 is devoted to the parametric optimization aspect of op amp design.

Layout generation starts with a sized circuit schematic of an op amp. The designer first reduces the complexity of the problem by adding a higher level of abstraction to the circuit. For instance, a few circuit elements are grouped together to form a building block based on their connectivity, geometrical matching, functionality, etc. This abstracts the circuit as a composition of several building blocks. The designer then sketches a rough placement of these blocks considering layout rules, terminal locations, routing of critical signals and so forth. After the initial placement of the blocks, the designer routes the nets and at the same time compacts the resulting layout as much as the spacing rules allow. Sometimes the initial placement must be modified for better routing capability, better area utilization, or better performance. When the layout is done, parasitic elements such as parasitic capacitances, and resistances from either devices or wirings are extracted from the mask geometries. These parasitic elements are then added to the initial circuit schematic and the resulting circuit is simulated for verification. If all the specifications are met, the design is completed. Otherwise, the current layout must be modified to reduce the excessive parasitic elements. However, if repeated modification efforts do not produce the correct design, some of the design parameters of the circuit must be readjusted. In the worst case, the designer may have to modify the current circuit topology to improve the performance as necessary.

From the above discussion, it can be readily understood that the efforts and time required to design even a single op amp may be significant when the performance specifications are difficult to be achieved: The entire design cycle (as shown in Fig. 2.14) may have to be repeated many times. As a result, the time and efforts devoted to the design of analog interface subsystems used in mixed analog/digital systems constitute a bottleneck in application-specific and customer-specific design of IC's where time to market requirements are more important than component cost.

# 2.5 Review of Automatic Synthesis Systems

The history of automatic synthesis tools for op amps goes back to the days of APLSTAP<sup>39</sup> and DELIGHT.SPICE.<sup>17</sup> These systems consist of a general-purpose optimization program and a circuit simulation program. Accordingly, they have been used in many IC design problems, with bipolar op amp design being just one of them. However, it is not until late 1980's that intensive research efforts have been put into design automation for analog circuitry including CMOS op amps. Knowledge-based design tools such as An\_Com,<sup>23</sup> IDAC,<sup>20,40</sup> and OASYS<sup>19</sup> have been announced.<sup>†</sup>

On the other hand, an optimization-based system such as ECSTACY<sup>18</sup> has been developed as a general-purpose parametric optimization tool. In this section, these synthesis tools are reviewed to discuss their contributions and limitations.

OASYS<sup>19</sup> is a behavior-to-schematic synthesis tool for analog functional blocks. In OASYS, analog circuit topologies are represented as a hierarchy of functional blocks and a planning mechanism is introduced to translate performance specifications between levels in

<sup>&</sup>lt;sup>†</sup> There exist a few other programs developed for analog functional block synthesis such as BLADES, <sup>41</sup> PROSAIC, <sup>22</sup> and one by Allen. <sup>21</sup> However, at the time of their publications, they were either not mature enough to handle the entire synthesis of op amps or not applied to op amp design.

this circuit hierarchy. The program synthesizes a sized circuit schematic for CMOS operational amplifiers and, more recently, for CMOS comparators<sup>42</sup> from performance specifications and process parameters. A sized circuit schematic from OASYS is then sent to the full-custom analog cell layout tool, ANAGRAM<sup>26</sup> to complete the schematic-to-layout path.

IDAC<sup>20,40</sup> is the first system that formally announced a behavior-to-schematic synthesis for CMOS op amps in 1984. The system has been further enhanced to design not only op amps but also other analog functional blocks such as voltage references, comparators, and A/D converters. In IDAC, a specialized software routine is associated with each circuit topology covered by the system. Each routine is self-contained: Not only design decisions (in the form of if-then-else rules) customized for that particular topology but also process-technology-specific data have been included in the routine. The program also generates mask geometries of the sized circuit schematic using the analog layout tool, ILAC.

An\_Com <sup>23</sup> is a behavior-to-layout synthesis tool developed for analog functional blocks. In An\_Com, the silicon compilation process is broken down into several steps, thus resulting in a sequence of successive decompositions. At each decomposition step, the high level specifications are broken into the specifications for the elements or subblocks at a lower level in the hierarchy until the resulting elements are leaf cells that exist in a library or can be produced by a layout generator. This decomposition process is driven by domain-specific knowledge pre-stored in templates. Currently, An\_Com can produce a mask-level layouts of CMOS op amps starting from performance specifications.

ECSTASY<sup>18</sup> is an interactive, general-purpose IC design optimization tool applicable to a broad spectrum of circuits. A forms-based user interface developed for analog design allows the designer to formulate design problems easily. Gradient-based algorithms (such as feasible directions methods) as well as random search algorithms are employed in order to avoid numerical difficulties in the optimization. The tool has been used for switched

capacitor filters and bipolar op amps but not for CMOS op amps so far.

To summarize, OASYS and An\_COM are based on a hierarchical decomposition of performance specifications down to leaf cells (such as current mirrors or differential pairs). But for the synthesis of such basic functional blocks as op amps, comparators, voltage references, output buffers, etc, it is very difficult to decide how the given specifications should be decomposed because of the close, sometimes intricate dependencies between the leaf blocks. Besides, in order for the method to take advantage of specific topologies and their known usefulness, the system must store such information in the database as templates. This violates the hierarchical approach from the method. In fact, such templates are dominantly used for op amp synthesis in both systems.

The OASYS' layout program, ANAGRAM<sup>26</sup> uses a simulated annealing method for placement and a constraint-based line expansion algorithm for routing. However, simulated annealing is in general too inefficient to handle versatile constraints arising from variable-shaped blocks different terminal configurations, geometrical symmetry among some blocks, etc. The routing algorithm developed mainly concerns itself with noise coupling due to internodal capacitances between the signal wires and with shared parasitic resistances in the DC power supply wiring. Constraints such as upper bound in routing capacitance, matching routing parasitics between signal nets, and specified assignments of certain wires to certain layers are not treated. After all, op amp layouts from ANAGRAM look quite different from those hand-crafted by expert designers. In An\_Com, op amp layouts are generated based on a slicing structure; its overall layout strategy (such as a floorplanning method) is not mentioned except that it is based on leaf cell generators.<sup>23</sup>

IDAC<sup>20,40</sup> operates on a flat circuit description, i.e. each topology is a basic unit. However, the consolidation of design 'strategy' and topology-specific 'data' creates much overhead whenever a new circuit topology is added into the system.

Some disadvantages common in all three systems are as follows: Firstly, they require a priori design knowledge to be integrated into the system for each new type of circuitry. Secondly, high degrees of optimization are difficult to be achieved. Since the design strategies consider some but not all of specifications at a time, it is hard to avoid order-dependency in the design process. The op amp layouts from IDAC look promising but no detailed description on IDAC is available.

On the contrary, ECSTASY neither uses a priori design knowledge nor suffers from the order-dependency in its optimization strategies. But the system is capable of only parametric optimization: It can neither select a good circuit topology for an application nor generate a layout. Another drawback is that the user must have detailed understanding of the circuit he/she tries to optimize.

Recognition of the shortcomings of both knowledge-based and optimization-based synthesis approaches has lead to a new approach to the compilation of op amps which is the subject of this thesis and which is described in chapters 4 through 6.

# **CHAPTER 3**

# **OPASYN: A COMPILER FOR CMOS OP AMPS**

## 3.1 System Overview

OPASYN is a behavior-to-layout synthesis tool for CMOS op amps. It is developed with the following objectives:

- a) Mapping from performance specifications to mask geometries. The synthesis system must perform the complete synthesis from specifications to detailed layout.

- b) High quality solution. A solution from the program must meet all the performance specifications and consume minimal power and area.

- c) High computation efficiency. The program must run fast enough so that it can be used interactively at the system design level; this means turnaround time should be on the order of a few minutes or less.

- d) Minimal user interaction. The program must possess ample design knowledge about op amps to complete the synthesis task with minimal help from the user. In this way, even a novice designer, i.e., a system designer who needs to employ an op amp in his/her system design can use the program without having to learn op amp design.

The rest of this section presents the framework of the program and gives an overview over the flow of the synthesis.

The program consists of an internal database and three functional modules: a circuit selection module, a parametric circuit optimization module, and a layout generation module.

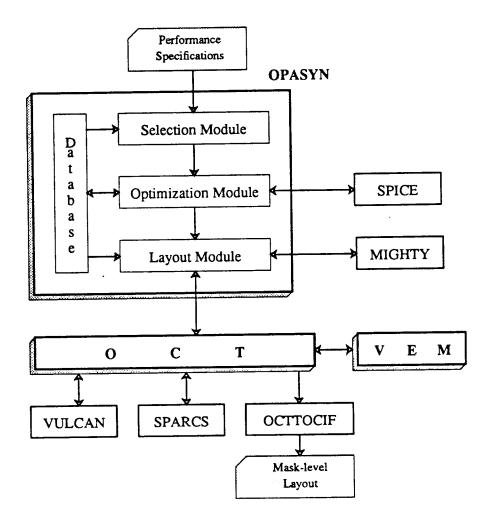

The framework of OPASYN and its interface to other physical design tools in the Berkeley CAD environment are shown in Fig. 3.1.

The database contains the necessary design knowledge for each op amp topology available to the users of the system; it includes<sup>24,25</sup>

- a decision tree for topology selection,

- analytic circuit models for parametric circuit optimization,

- slicing structure descriptions for floorplanning,

- netlist descriptions for routing.

Device parameters and layout design rules for different process technologies are retrieved from a technology library which is a part of the database.

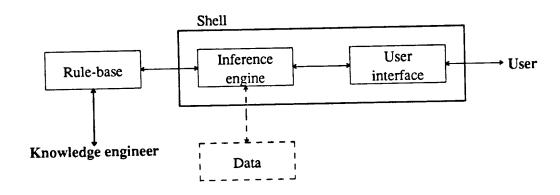

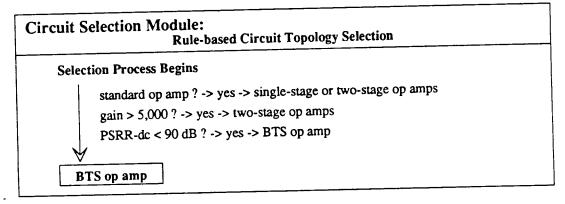

The circuit selection module is a rule-based system where an inference engine selects a promising circuit topology based on the user specification. The decision tree used for topology selection is implemented as a set of production rules (if-then rules) in the database to permit flexible and easy upgrading of the system. In addition, a simple query mechanism has been incorporated to explain the decision made by the system or to show the rule(s) used in the decision process. A detailed description is presented in Chapter 4.

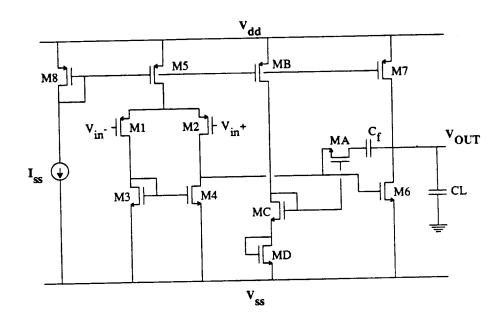

The parametric optimization module is composed of an optimization routine and an interface to the circuit simulator SPICE. First, the analytic model for the given circuit topology (that is pre-designed by an expert circuit designer and stored into the database) and the data for the specified process technology are loaded from the database. Starting from the given circuit schematic, optimal sizes of the devices in the circuit are determined so as to meet all input specifications. The optimization routine is quite general and works in the same manner for all circuits to be optimized and for all process technologies. The SPICE interface routine generates input decks for SPICE, makes system calls to SPICE, and interprets the results from SPICE to verify the optimization results. Chapter 5 discusses this subject in detail.

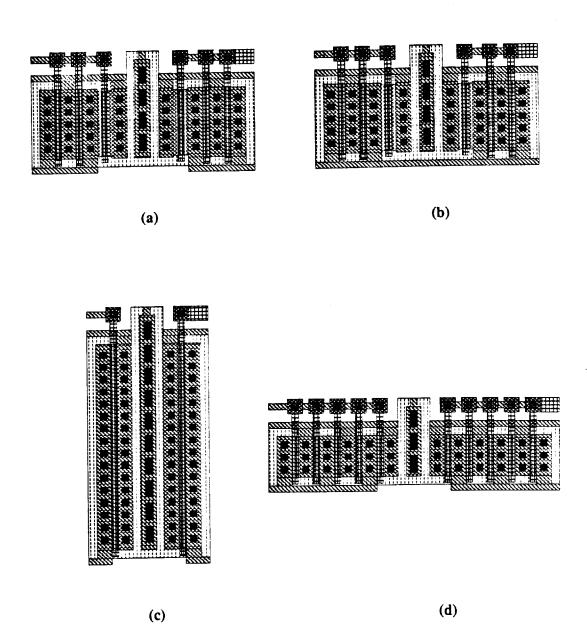

Figure 3.1 OPASYN Framework and its Interface to the Berkeley CAD Environment.

The layout generation module includes a floorplanning routine, parameterized leaf cell generators and interface routines to a router and a spacing program. The input to this module is a sized circuit schematic. The module outputs design-rule-correct mask geometries of an op amp layout. The leaf cell generators provide small circuit elements such as MOSFET's, MOSFET pairs, and capacitors at run time. The interface routines take care of constraint generation and intermediate data format conversion. The layout module also works independent of any specific layout design rules; these rules are parameterized and read from the database. The layout generation is the topic of Chapter 6.

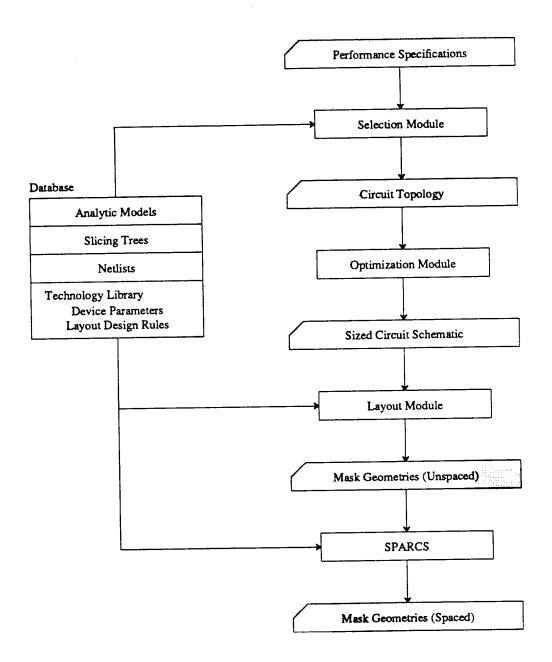

The synthesis flow in OPASYN is shown in Fig. 3.2. Synthesis starts from a set of op amp performance specifications. Based on the general domain of the specifications, the program selects an appropriate option out of a small database of generic, widely applicable op amp circuit topologies, unless the user explicitly specifies the particular circuit topology to be used. For the chosen circuit, optimal values of its set of design parameters will be determined to meet the objectives implied by the given specifications. <sup>25</sup> The SPICE interface program is called by this module to verify the optimization result through extensive circuit simulation. <sup>43,44</sup> Finally, the layout generation module takes the netlist of the sized circuit schematic from the previous synthesis phase together with a specification of a desired aspect ratio or of a vertical/horizontal size constraints, and a reference to a file of geometrical design rules. It produces an unspaced, symbolic layout of the circuit using a macro cell style. The symbolic layout is then properly spaced by a spacing program to produce design-rule-correct (spaced) mask geometries.

The modular architecture and flexible functional modules used in OPASYN make it possible to extend the system to synthesize other analog building blocks such as output buffers, comparators, and bandgap references with minimal alterations to the program.

<sup>†</sup> In fact, the intermediate data format conversion is necessary for routing only. All the other tools communicate through the data manager OCT (which is explained in the next section).

Figure 3.2 Synthesis Data Flow in OPASYN.

Various technologies such as CMOS, bipolar, and BiMOS can be also accommodated. Up to now, CMOS technology has been exclusively employed because of its prevailing usage in analog interface component designs.

## 3.2 OPASYN and the Berkeley CAD Environment

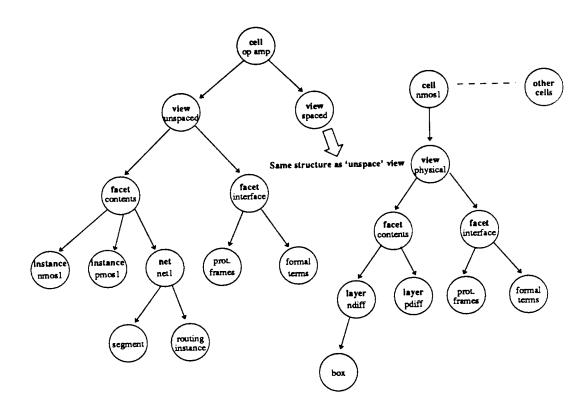

OPASYN gets much benefit from the Berkeley CAD environment, especially for its layout generation. Fig. 3.1 shows that many physical design tools communicate with OPASYN either directly or indirectly through a data manager. In fact, the internal database of OPASYN provides only the specific design knowledge necessary for the layout synthesis: layout design rules, 'slicing structures' for the circuit topologies (will be explained in Chapter 6), and netlists. Design data (mask geometries) produced at each phase of the layout generation is hierarchically managed by the data manager OCT<sup>45, 46</sup> developed at U.C. Berkeley. In the rest of this section, the abstraction hierarchy of OCT and its application to OPASYN are explained, and other design tools used in the synthesis process are briefly described.

OCT is a hierarchical, object-oriented data manager developed for VLSI/CAD applications. The program offers a simple interface for storing information about the various aspects of an evolving chip design. A basic unit in a design is called a 'cell'. A cell is a portion of a chip (or the entire chip) the designer wishes to consider as a unit. A cell has many aspects called 'views', depending on the design stage (i.e. logic synthesis, layout synthesis, circuit simulation, etc) and on the design style to be used. Each view has one 'facet' named 'contents' that contains the actual definition of the view as well as various application dependent 'interface' facets that contain the minimal amount of information about the view necessary for its manipulation or for interfacing to it from the outside. With these abstraction entities, cells can be defined hierarchically. This means that a view of a cell can contain 'instances' of other cells whereas each of these cells has their own views and possibly

instances of some other cells). The different views communicate with one another through suitably abstracted interface facets.

In OPASYN, during various phases of the layout process, different views such as a 'physical view', an 'unspaced view', and a 'spaced view' are used. Leaf cells are represented in a physical view with fully specified geometry for all devices and connections stored in their contents facets. They observe all specified design rules and need no further spacing. Their interface facets contain overall cell shapes, terminal locations, and protection frames. The entire layout of an op amp, on the other hand, is represented in an unspaced view where only relative placement, sizes and shapes of instances of component blocks, and the general routing of the interconnections are recorded in its contents facet. This abstraction of the layout needs to be subject to a spacing program where all the design rules are checked and the placements of the leaf cells are suitably adjusted. The result is a design-rule-correct spaced view of the entire op amp. Fig. 3.3 illustrates the hierarchical data abstraction discussed so far.

The advantage of using such a general data manager is two-fold. By observing a set of pre-defined policies, our layout program can communicate with other existing tools with minimal overhead and with no need for intermediate data conversions. For instance, OPASYN can call the spacing program SPARCS to re-space the layout in symbolic format, or the dedicated graphics editor VEM to visually verify the synthesis result without having to provide explicit interface modules to these programs. The system development time could be significantly reduced by relying on this data manager and on many existing tools.

VEM is an interactive graphics shell/editor for IC designs represented using the OCT data manager. The primary use of VEM by OPASYN is to provide a means of looking at the graphics representation of an OCT view and invoking various CAD tools on these views. VEM also provides standard graphics editing capabilities to the users.

Figure 3.3 Hierarchical data abstraction used in OPASYN.

VULCAN creates/updates geometrical information and required properties (such as technology, cell type, etc.) in an interface facet for an OCT view from its contents facet.<sup>47</sup> Formal terminals of a cell are copied to the interface facet along with their implementation, and all the geometry other than terminal implementation geometry on each layer in the contents facet is merged into a protection frame for that layer in the interface facet. Instances of other cells are replaced by the geometry contained in their interface facets before this merging process.

SPARCS is a graph-based, 1-dimensional compaction program for spacing IC symbolic layouts. Its input is an OCT view of type 'unspaced' and its output is another OCT view called 'spaced' with the elements translated so that the overall area is minimized and the spacing rules are satisfied. The usage of SPARCS in OPASYN is further discussed in Chapter 6.

OCTTOCIF accepts as input an OCT facet and produces a CIF file.<sup>48</sup> The program is used to generate mask geometries of a layout that is suitable for a certain IC foundry (i.e. MOSIS).

MIGHTY is a two-layer symbolic detailed router for any rectagonal routing area.<sup>49</sup> The routing process is also explained in Chapter 6.

#### **CHAPTER 4**

# HEURISTIC CIRCUIT SELECTION

#### 4.1 Alternatives

The first step in op amp design is to obtain a promising circuit topology based on the given design requirements. As illustrated in Fig. 2.14, expert designers perform this task in two phases. They first make an architectural decision using some of the design requirements such as load capacitance, load resistance, power dissipation, noise requirement, etc. Among many, existing variants of the chosen architecture, they then select a topology which, based on prior experience, fits the new application. Or they may modify one that almost fits by enhancing specific performance characteristics, again partly based on experience and partly by trial and error. This often requires many design cycles.

For knowledge-based synthesis systems that must perform the same task, the following approaches can be considered:

- Creation of a topology from basic building blocks,

- Modification of basic (seed) topologies,

- Selection from a library of 'proven'<sup>††</sup> topologies.

Let's investigate advantages and drawbacks of these approaches to find out which one is most practical. It should be noted that the above approaches can be applied not only to op amps but also to most other analog functional building blocks such as output buffers, voltage references, comparators, etc.

<sup>†</sup> We mean, by an architecture, a collection of similar topologies.

<sup>††</sup> By a proven topology, we mean that the topology has been proven to have good, stable performance and is widely used in the industry.

## 4.1.1 Creating New Topologies

Creating a topology required by the performance specifications using building block elements and basic knowledge about circuit design would be the most general solution. If such an approach is feasible, no circuit topologies need be pre-stored in the database, and there would be no overhead of adding new topologies as the application range of the synthesis program is expanded. However, creating a topology from basic principles is very difficult for a couple of reasons. First, the tight and often intricate coupling between functional modules in typical op amp circuits makes hierarchical decomposition of functionality very difficult. As a result, breaking the high-level specifications into the specifications for the lower-level building blocks in the hierarchy is not well understood. For instance, the phase margin of a two-stage op amp must be determined by considering the frequency response of the entire circuit. Propagating the constraints imposed by the phase margin of the circuit to its constituent modules, namely input stage, output stage, and compensation stage is very difficult. As a matter of fact, most synthesis techniques for analog circuits are based on analysis; an appropriate circuit topology is first created and all component values are then adjusted to meet the overall design requirements by analyzing the circuit. Second, a circuit topology should be designed to cancel out first-order variations in design parameters to yield stability and immunity against a rather wide range of spreads in integrated circuit active and passive component values. In other words, whenever a new circuit topology is constructed, the sensitivities of its performance characteristics to its component value changes should be derived and checked. If the sensitivities are considered too high for the design requirements, the topology should be modified.

Bowman et al.<sup>1</sup> made an effort to create op amp topologies from basic design principles but with very limited success; the generated topologies are simple two-stage op amp circuits even without any compensation scheme. Similar efforts have been put into OASYS<sup>2, 3</sup> and An\_Com.<sup>4</sup> However, no new topologies have been invented by these systems so far.

Practical op amp topologies are still being devised by expert designers. When one takes a closer look, one realizes that the above systems do not really create any topologies but rather assemble basic building blocks into complete topologies based on pre-stored templates (in An\_Com) or plans (in OASYS) which implicitly contain the proven op amp topologies. Therefore, one might as well store proven topologies explicitly and select one of them (as described in 4.1.3).

# 4.1.2 Modifying Seed Topologies

An easier approach is to start from some basic (seed) op amp topologies and to modify it to meet certain design goals. For each architecture to be used, a seed topology is defined. For instance, a topology composed of an input stage, a compensation stage, and an output stage is a seed topology for the two-stage op amp architecture. Similarly, one with a differential pair and a gain stage serves as a seed topology for the single-stage op amp architecture. The most appropriate seed topology is then selected according to the architectural decision made from the specifications. The selected seed topology is then modified during the device sizing phase of the synthesis as required by the design requirements. This approach has the advantage that the seed topology can be incrementally modified as it becomes clear which design requirements are hard to match. Thus a detailed topology does not have to be selected in the beginning; only the architectural decision has to be made at the top level. Subsequently, two kind of modifications can be made: weak modification and strong modification.

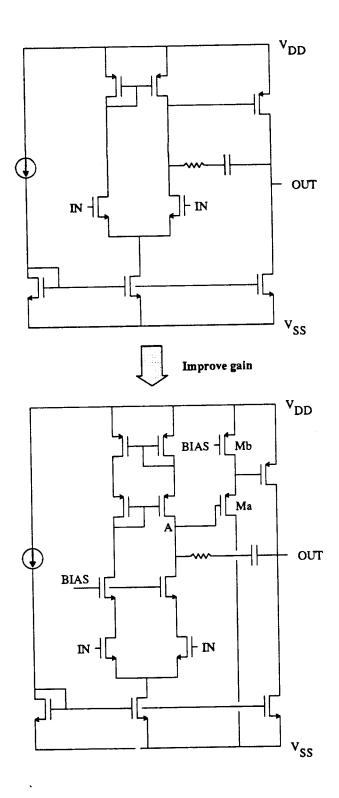

In weak modification, the topology change is incremental and is made within the same architecture. Fig. 4.1 shows an example of the weak modification. In this case, the seed topology (two-stage op amp with pole-zero compensation) is modified to produce a higher small signal gain; the input differential pair and the active load have been replaced with cascoded versions. However, since these changes limit the voltage swing at node A, the

Figure 4.1 Weak modification of topology for improved performance.

level shifter composed of transistors Ma and Mb is added to the circuit. We consider the change as incremental in the sense that the resulting topology is still a variant of the two-stage architecture. But even with these incremental changes, the resulting circuit is a rather new topology in terms of its ac performance (phase margin, unity-gain bandwidth, etc). This is because of the newly introduced doublet (pole-zero pair) from the source follower Ma. Now, the compensation problem has been changed from that of a two-pole and one-zero system to that of a three-pole and two-zero system. It is well known that the latter system is very difficult to compensate and the currently used pole-zero compensation scheme may not work for this topology. This incremental change also requires more power and area consumption as well as different bias voltages. The implication here is that weak modification in most cases is not robust; an incremental change made to improve a certain performance characteristic often causes other characteristics to deteriorate.

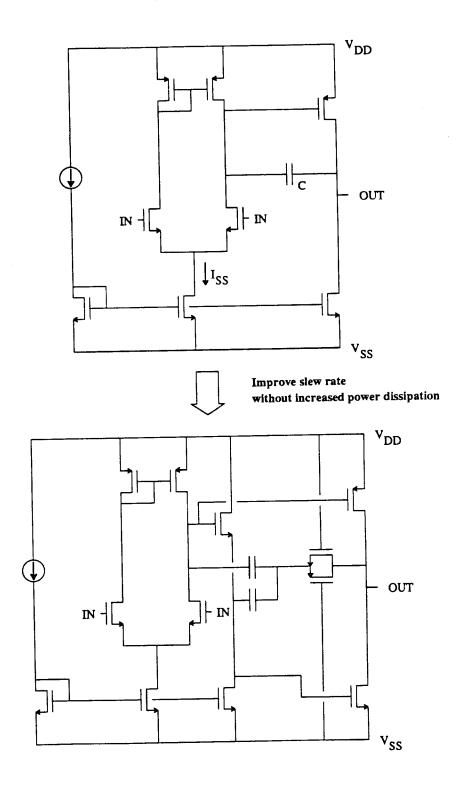

In strong modification, the topology change is rather global and the resulting topology is often no longer a variant of the same architecture. Fig. 4.2 illustrates an example of strong modification. The seed topology in the figure is modified to improve the slew rate characteristic. An incremental modification in this case would be to increase the bias current  $I_{SS}$ ; the slew rate is calculated from  $\frac{I_{SS}}{C}$  and reducing C would worsen the ac response. But increasing the bias current  $I_{SS}$  will increase the power and area consumption. Therefore a strong modification of the topology is made, which can increase the slew rate without increasing the power dissipation. The resulting topology shown in Fig. 4.2 is the outcome of such a strong modification where the output stage of the original topology has been replaced with a class AB output stage. Consequently, the new topology slews better even with reduced power dissipation. However, the change made here is so drastic that not only the transient characteristics but also the ac characteristics and the dc characteristics of the original topology have been changed; the new topology is actually a variant of the class AB

Figure 4.2 Strong modification of topology for improved performance.

architecture.

From the above discussion, it can be seen that an incremental modification of a topology in order to improve a certain performance characteristic often fails. The effect of the modification to all the other performance characteristics must be considered at the same time. When sensitivity issues are considered as well, the situation gets even more difficult; 'intelligent' strong modification is required in most cases. However, such modifications are as difficult as creating new topologies. Therefore, it is more efficient and robust to switch among a set of proven topologies rather than to try to make intelligent strong modifications because they most likely just produce the few proven topologies that have been already developed by human designers.

## 4.1.3 Selecting From Proven Topologies

Selection from a library of proven topologies is a rather limited solution. Topology selection has to be made at the top decision level and additional design knowledge must put into the database each time a new circuit topology is added. However, the approach is efficient and robust for the following reasons:

- The approach most closely emulates a human designer's approach.

- The selected topology is robust it is proven by thorough analysis and by its repeated usage.

- All the known useful properties and approximations specific to a certain topology can be fully utilized in this approach.

- The poor judgement made at the top decision level can also be quickly recovered because a typical run time of the automatic synthesis process is in the order of a few minute; whenever the current architecture cannot meet a certain specification, another architecture can be considered, and the synthesis can thus be carried out for a several

potentially suitable topologies.

• The effort of adding a new topology to the database does not seem to be a problem because the number of proven op amp topologies that are typically used for analog interface subsystems is quite limited. For instance, a single-stage fully-differential op amp is almost everyone's choice for an A/D converter application. Furthermore, as symbolic analysis techniques are being developed,<sup>6</sup> such effort may become significantly smaller.

The heuristic circuit selection method used in OPASYN has been developed based on the above discussion. The detailed explanation of the method is given in the next section.

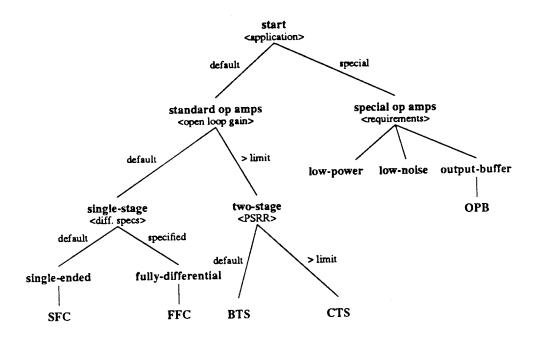

# 4.2 Heuristic Pruning of the Decision Tree

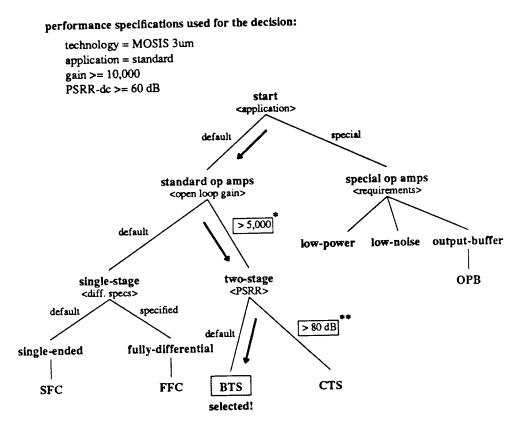

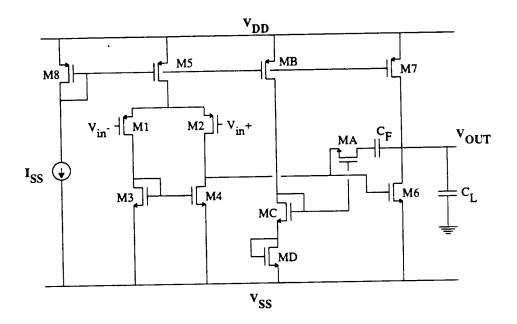

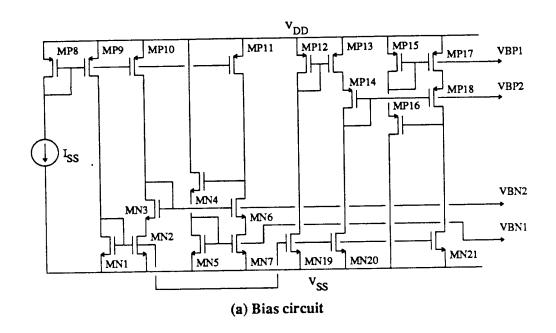

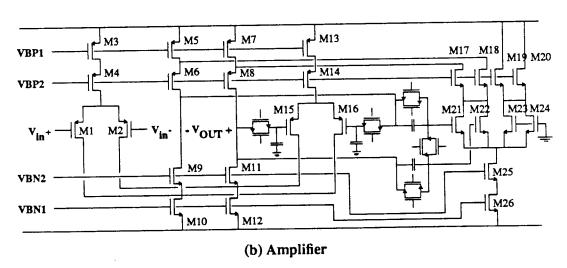

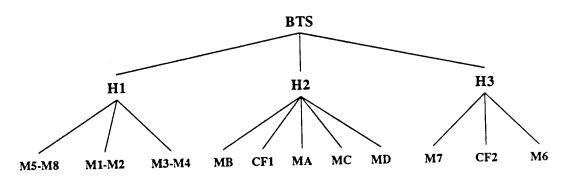

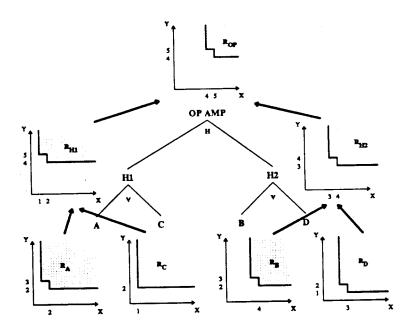

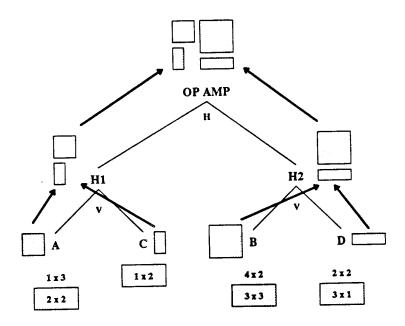

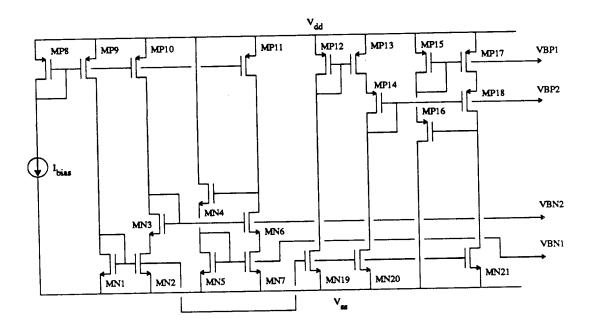

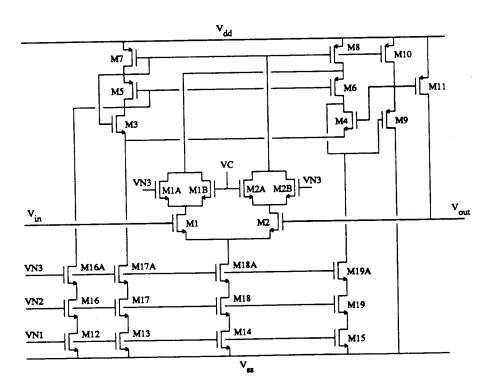

The circuit selection strategy used in OPASYN is based on a decision tree (shown in Fig. 4.3) which has been defined based on some key performance specifications such as general application area, open loop gain, PSRR, fully differential topology requirement, load capacitance, load resistance, power dissipation, or noise requirement. The leaf nodes in this tree correspond to proven op amp topologies commonly used in many applications, and the corresponding design knowledge is stored in the database of OPASYN. Currently five different circuit topologies have been fully incorporated and they are denoted in Fig. 4.3 as SFC, FFC, BTS, CTS and OPB. The meanings of various notations used in Fig. 4.3 are as follows:

- 'default' represents the default choice.

- '> limit (< limit)' the branch is to be selected if the corresponding design specification at the node is greater (less) than the limit value retrieved from the technology library.

default - default choice

> limit - select if the attribute value at the node is greater than the preset limit.

< limit - select if the attribute value at the node is less than the preset limit.

specified - select if it is so specified.

special - select if application needs a special op amp.

Figure 4.3 Decision tree for heuristic circuit selection.

- 'special' the branch is to be selected if any of the special-purpose op amps is required.

- 'specified' the branch is to be selected if it has been specified explicitly by the user.

Searching for a suitable topology starts at the root of the decision tree; nodes of this tree are checked in turn whether some subtrees can be pruned away (eliminated from further consideration) based on the range of the given specifications. The un-pruned leaf nodes are forwarded to the optimization module. The following example illustrates the basic idea.

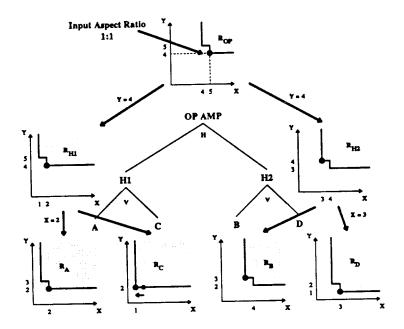

#### Example:

Let's assume that the application demands an 'ordinary' op amp with an open loop gain of 10,000 and a PSRR of 60dB at dc using the MOSIS 3 µm process. The decision process starts at the top and immediately eliminates all the 'special-purpose' op amps since none of these special characteristics has been called for. Among the 'standard' op amps, the subtree of two-stage op amps is selected since the specified open loop gain of 10,000 is higher than the gain limit of single-stage op amps for the MOSIS 3 µm process (which is set to 5,000 in the technology library). Between the two two-stage op amps (BTS and CTS), the BTS op amp has been selected because the relaxed requirement on PSRR does not dictate the use of the CTS op amp. The particular decision path of this example is shown in Fig. 4.4 with bold arrows.