# Aspects of Cache Memory and Instruction Buffer Performance

Mark Donald Hill

Report No. UCB/CSD 87/381

November 1987

Computer Science Division (EECS) University of California Berkeley, California 94720

| <del></del> |  |  |

|-------------|--|--|

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

|             |  |  |

# ASPECTS OF CACHE MEMORY AND INSTRUCTION BUFFER PERFORMANCE

Mark Donald Hill

Computer Science Division University of California Berkeley, CA 94720

#### **ABSTRACT**

Techniques are developed in this dissertation to efficiently evaluate direct-mapped and set-associative caches. These techniques are used to study associativity in CPU caches and examine instruction caches for single-chip RISC microprocessors. This research is motivated in general by the importance of cache memories to computer performance, and more specifically by work done to design the caches in SPUR, a multiprocessor workstation designed at U.C. Berkeley. The studies focus not only on abstract measures of performance such as miss ratios, but also include, when appropriate, detailed implementation factors, such as access times and gate delays.

The simulation algorithms developed compute miss ratios for numerous alternative caches with one pass through an address trace, provided all caches have the same block size, and use demand fetching and LRU replacement. One algorithm (forest simulation) simulates direct-mapped caches by relying on inclusion, a property that all larger caches contain a superset of the data in smaller caches. The other algorithm (all associativity simulation) simulates a broader class of direct-mapped and set-associative caches than could previously be studied with a one-pass algorithm, although somewhat less efficiently than forest simulation, since inclusion does not hold.

The analysis of set-associative caches yields two major results. First, constant factors are obtained which relate the miss ratios for set-associative caches to miss ratios for other set-associative caches. Then those results are combined with sample cache implementations to show that above certain cache sizes, direct-mapped caches have lower effective access times than set-associative caches, despite having higher miss ratios.

Finally, instruction buffers and target instruction buffers are examined as organizations for instruction memory on single-chip microprocessors. The analysis focuses closely on implementation considerations, including the interaction between instruction fetches, instruction prefetches and data references, and uses the SPUR RISC design as the case study. Results show the effects of varying numerous design parameters, suggest some superior designs, and demonstrate that instruction buffers will be preferred to target instruction buffers in future RISC microprocessors implemented on single CMOS chips.

25 November 1987

|  |   |  | 1 |

|--|---|--|---|

|  |   |  |   |

|  |   |  |   |

|  |   |  | - |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  | • |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  | • |

|  |   |  |   |

|  |   |  | - |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

|  |   |  |   |

# ASPECTS OF CACHE MEMORY AND INSTRUCTION BUFFER PERFORMANCE

Copyright © 1987

by

Mark Donald Hill

All rights reserved.

|  |  |  | - |

|--|--|--|---|

|  |  |  | - |

|  |  |  |   |

#### Acknowledgments

Many people deserve thanks for their help in making this dissertation possible. I want like to thank my committee, Alan Smith, David Patterson and Ronald Wolff, for their many insightful suggestions that enhanced the quality of my research and this presentation of it. In particular, I'd like to thank Alan Smith for his stern evaluation of my work that contributed considerably to making the final product better, and David Patterson for his many years of cogent advice and for providing an environment conducive to productive research.

Thanks also to: Sue Dentinger and Susan Eggers for critiquing drafts of my entire thesis, Jim Thompson and David Wood for improving drafts of Chapters 1 and 2, Valerie King for assisting me with the proofs in Chapter 2, Ken Lutz for assisting me in developing the cache hit implementations, my friends and colleagues on the SPUR project for numerous inspiring technical conversations, and all my friends and family for encouraging me these many years.

I want to acknowledge and thank those who provided trace data: Dick Sites at Digital Equipment Corp.; Anant Agarwal at Stanford; Alan Smith, George Taylor, and David Wood at Berkeley; Joe Hull and Rollie Schmidt at Synapse; John Lee and Bill Harding at Amdahl; and Robert Henry at Washington.

The material presented here is based on research supported in part by the Defense Advanced Research Projects Agency monitored by Naval Electronics Systems Command under Contract No. N00039-85-C-0269, the National Science Foundation under grants CCR-8202591 and MIP-8713274, by the State of California under the MICRO program and by IBM Corporation, Digital Equipment Corporation, Hewlett Packard Corporation, and Signetics Corporation.

Finally, a special thanks to el amor de mi vida and Cafe Roma.

|   |  | • |

|---|--|---|

|   |  |   |

|   |  |   |

|   |  |   |

|   |  |   |

| • |  |   |

## **Table of Contents**

| CHAPTER 1. Introduction                                                       | 1          |

|-------------------------------------------------------------------------------|------------|

| 1.1. Cache Memory                                                             | 1          |

| 1.2. Computer Performance Architecture                                        | 3          |

| 1.3. SPUR                                                                     | 3          |

| 1.4. Thesis Overview                                                          | 3          |

| 1.5. References                                                               |            |

| CHAPTER 2. Simulation Techniques for Direct-Mapped and Set-Associative Caches | 8          |

| 2.1. Introduction                                                             | 8          |

| 2.2. Background                                                               | 9          |

| 2.2.1. Set Associative Caches                                                 | 9          |

| 2.2.2. Stack Algorithms                                                       | 9          |

| 2.2.3. Linked-List Stack Simulation                                           | . 11       |

| 2.2.4. Other Stack Simulation Implementations                                 | 13         |

| 2.3. Inclusion in Set-Associative Caches                                      | . 13       |

| 2.4. Simulating Direct-Mapped Caches with Inclusion                           | 16         |

| 2.5. Simulating Set-Associative Caches without Inclusion                      | . 19       |

| 2.6. Comparing Actual Simulation Times                                        | 29         |

| 2.7. Conclusions                                                              | . 37       |

| 2.8. References                                                               |            |

| CHAPTER 3. The Effect of Set-Associativity on Cache Memory Performance        |            |

| 3.1. Introduction                                                             | . 40<br>41 |

| 3.1.1. Cache Performance Metrics                                              |            |

| 3.1.2. Methods                                                                |            |

| 3.1.3. Previous Work                                                          |            |

| 3.2. Analysis with Miss Ratio                                                 |            |

| 3.2.1. Raw Miss Ratios                                                        |            |

| 3.2.2. Smith's Model of Set-Associativity                                     |            |

| 3.2.3. Ratios of Set-Associative Miss Ratios                                  |            |

| 3.3. Analysis with Effective Access Time                                      |            |

| 3.3.1. Incorporating Previous Miss Ratio Analysis                             |            |

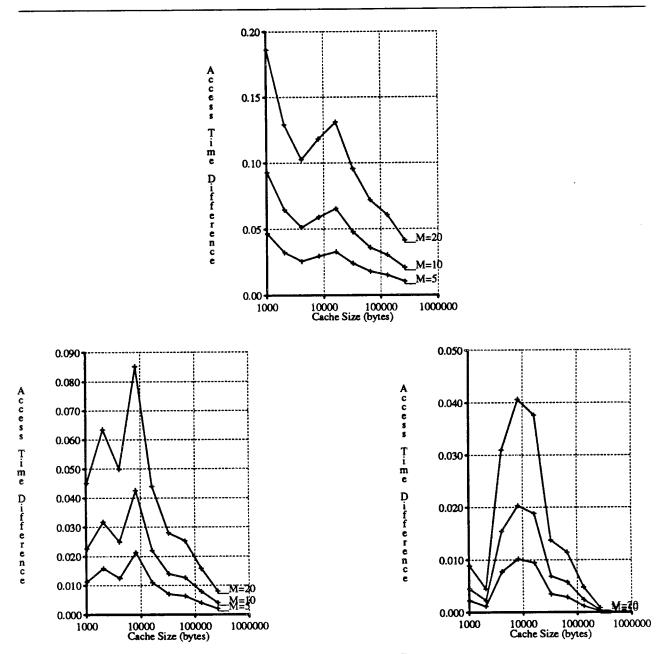

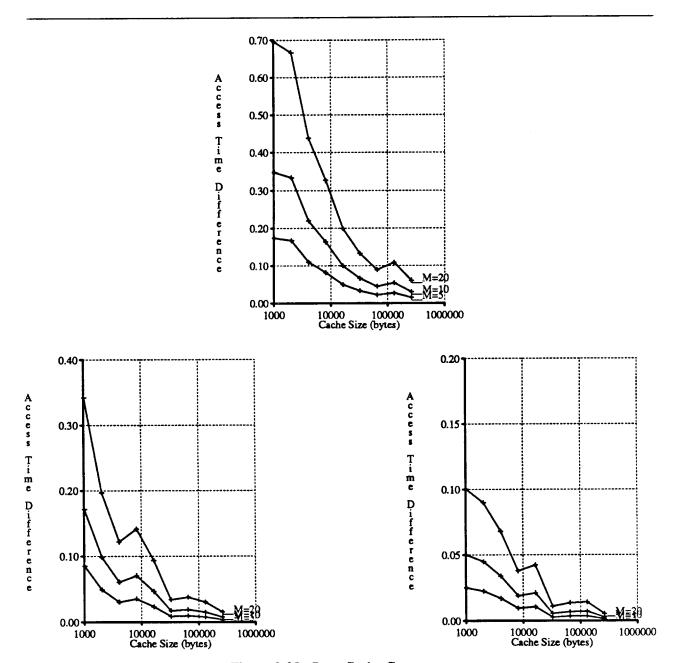

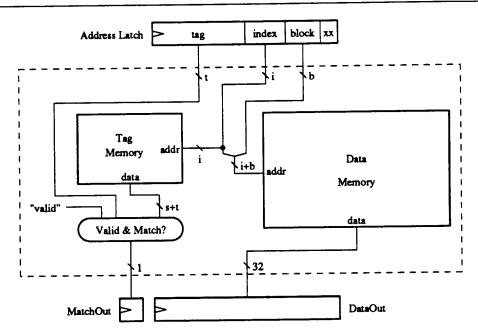

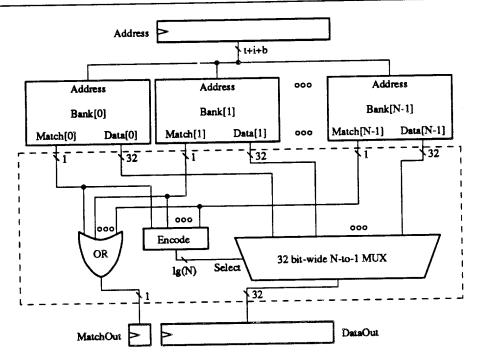

| 3.3.2. A Cache Architecture                                                   | . OU       |

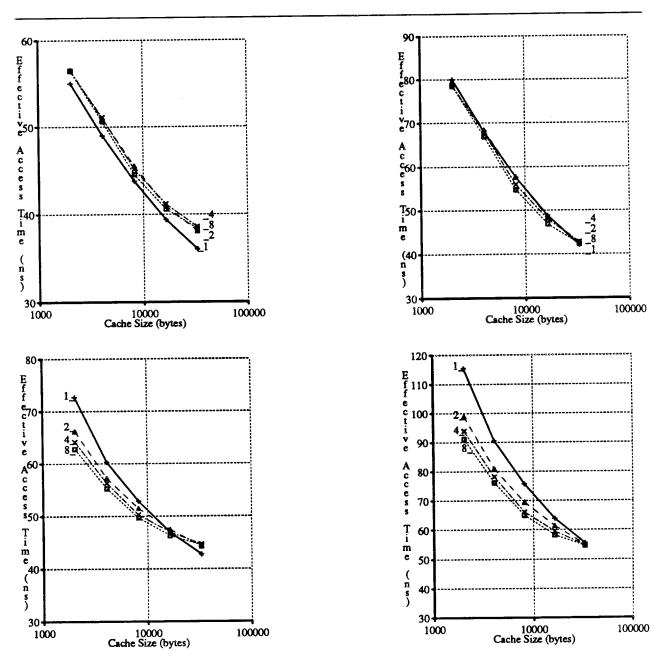

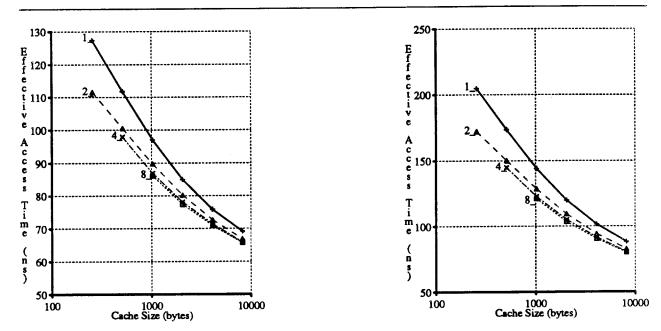

| 3.3.3. Comparing Effective Access Times                                       | . 83<br>84 |

| 3.3.3.1. TTL Caches                                                           | . 84       |

| 3.3.3.2. ECL Caches                                                           | . 91       |

| 3.3.3.3. CMOS Caches                                                          |            |

| 3.3.4. A Hybrid Design                                                        | 104        |

| 3.4. Summary and Conclusions                                                  | 10/        |

| 3.5. Appendix: Cache Implementations                                          | 108        |

| 3.5.1. AS TTL Logic and Static CMOS RAMs                                      | 110        |

| 3.5.2. Emitter Coupled Logic                                                  | 111        |

|     | 3.5.3. Custom CMOS                                      | 115 |

|-----|---------------------------------------------------------|-----|

|     | 3.6. References                                         | 117 |

|     |                                                         |     |

| CHA | PTER 4. Instruction Memory on a Single-Chip RISC        | 119 |

|     | 4.1. Introduction                                       | 119 |

|     | 4.1.1. Instruction Memory Background                    | 119 |

|     | 4.1.2. Why Limit Study to Single-Chip RISCs?            | 122 |

|     | 4.1.3. Methods                                          | 124 |

|     | 4.2. Instruction Buffers                                | 127 |

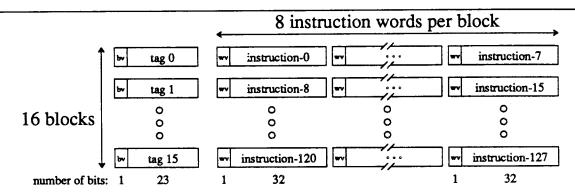

|     | 4.2.1. SPUR IB Architecture and Implementation          | 127 |

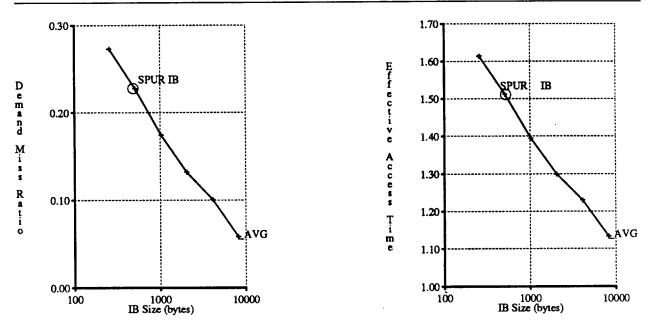

|     | 4.2.2. IB Evaluation                                    | 129 |

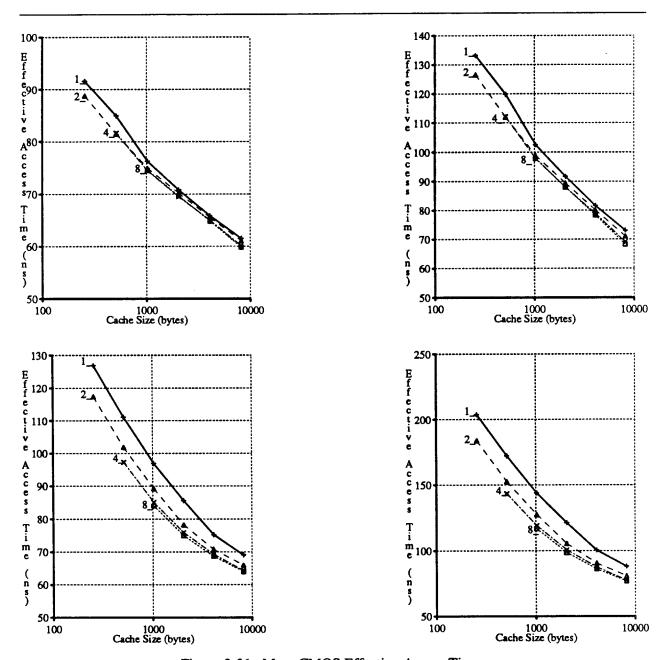

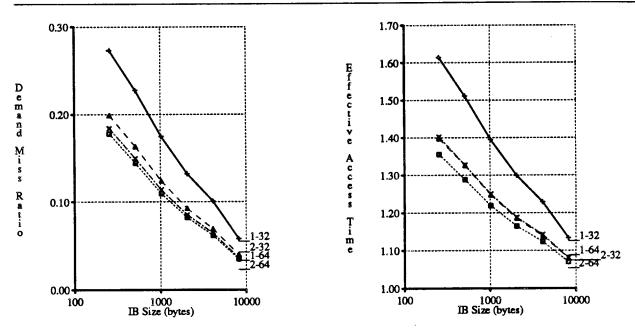

|     | 4.2.2.1. IB Size, Associativity, and Block Size         | 130 |

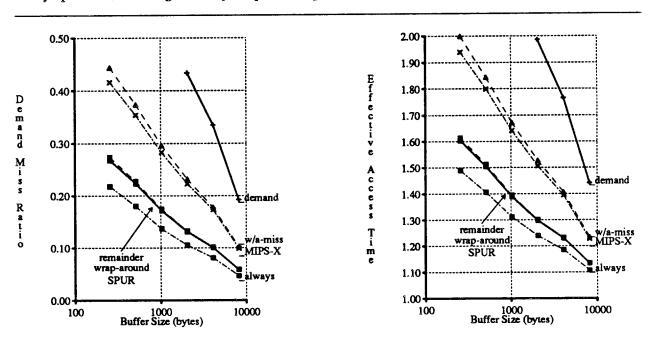

|     | 4.2.2.2. Off-Chip Bandwidth and Prefetching             | 131 |

|     | 4.2.2.3. Reducing IB Miss Penalty                       | 137 |

|     | 4.2.2.4. An Improved SPUR IB                            | 140 |

|     | 4.3. Target Instruction Buffers                         | 141 |

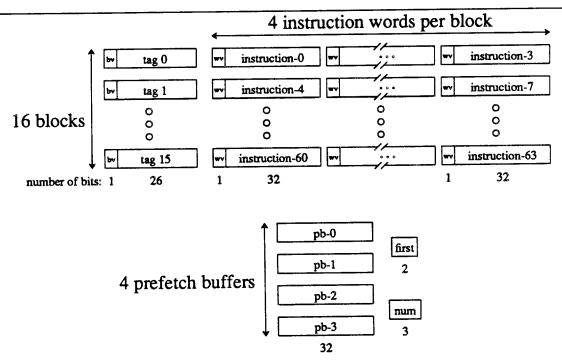

|     | 4.3.1. SPUR TIB/PB Architecture and Implementation      | 141 |

|     | 4.3.2. TIB/PB Evaluation                                | 143 |

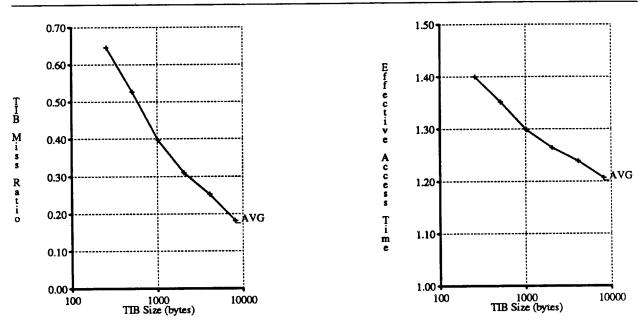

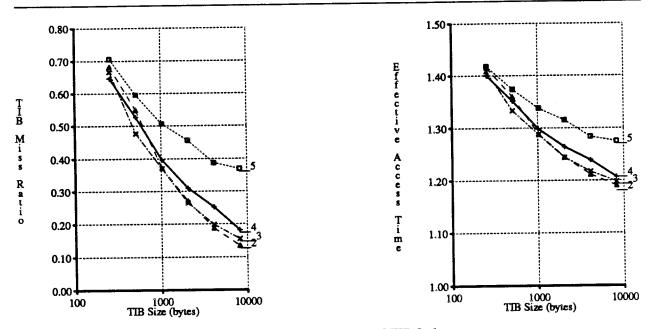

|     | 4.3.2.1. TIB Size, Associativity, Indexing, and PB Size | 144 |

|     | 4.3.2.2. Off-Chip Bandwidth                             | 14/ |

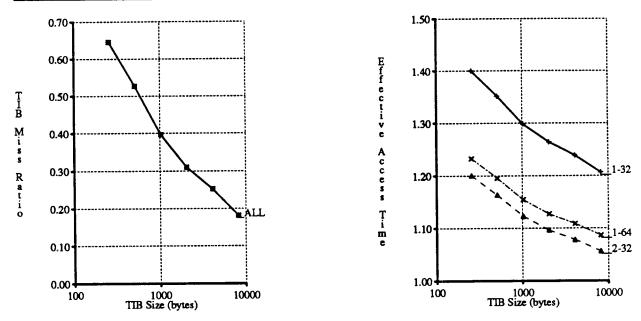

|     | 4.3.2.3. An Improved SPUR TIB                           | 149 |

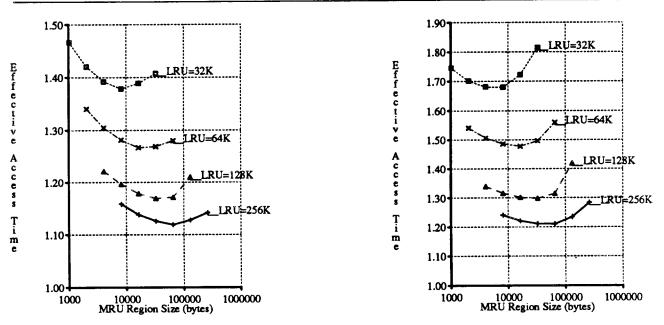

|     | 4.4. IBs vs. TIBs                                       | 121 |

|     | 4.4.1. One-Cycle External Cache                         | 151 |

|     | 4.4.2. Multiple-Cycle External Cache                    | 153 |

|     | 4.5. Conclusions                                        | 159 |

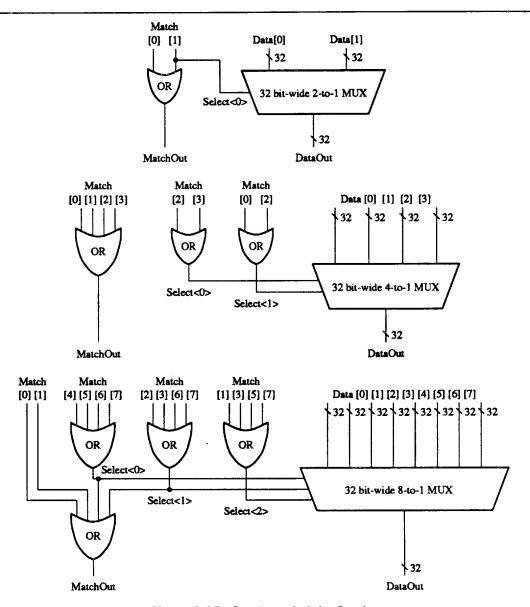

|     | 4.6. Appendix: SPUR Instruction Buffer Implementation   | 100 |

|     | 4.7. References                                         | 100 |

## List of Figures

| CHAPTER 1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

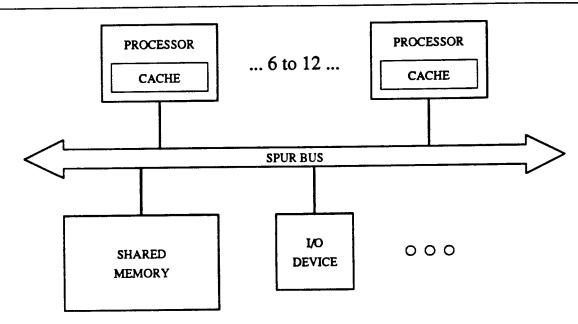

| 1-1. SPUR Workstation System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4           |

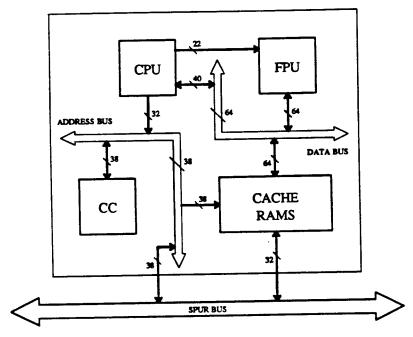

| 1-2. SPUR Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

| CHAPTER 2. Simulation Techniques for Direct-Mapped and Set-Associative Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8           |

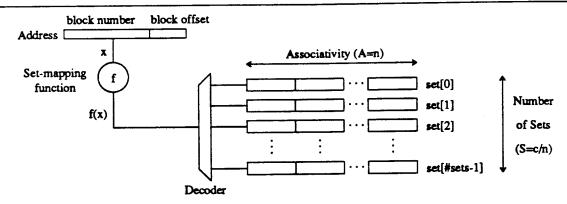

| 2-1. Set-Associative Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10          |

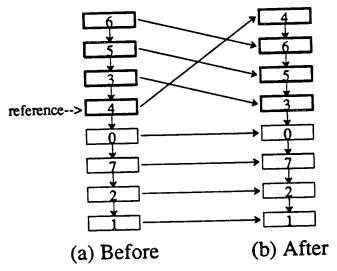

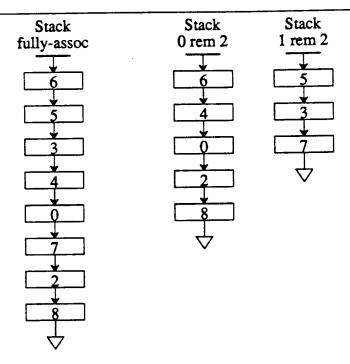

| 2-2. Stack Simulation Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12          |

| 2-3. Stack Simulation Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12          |

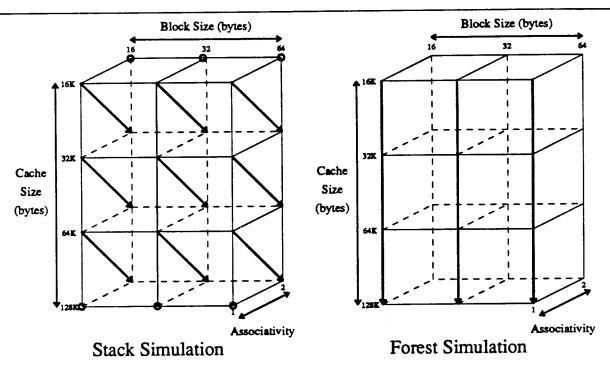

| 2-4. Stack Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16          |

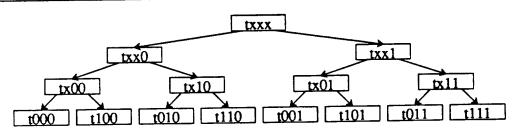

| 2-5. Forest Simulation Forest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17          |

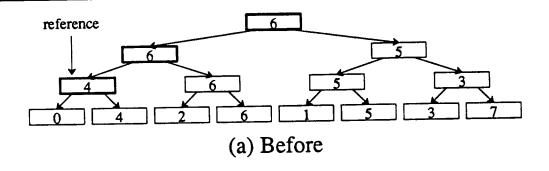

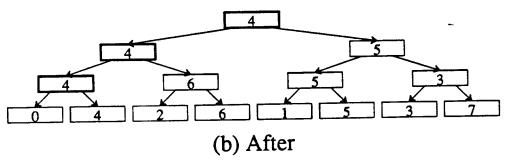

| 2-6. Forest Simulation Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17          |

| 2-7. Forest Simulation Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12          |

| 2-8. Forest Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20          |

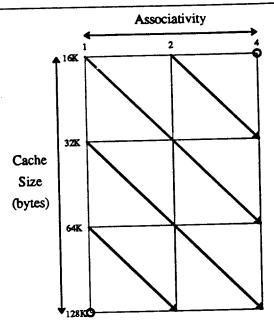

| 2-9. Simulating Cache Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21          |

| 2-10. Concurrent Stack Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22          |

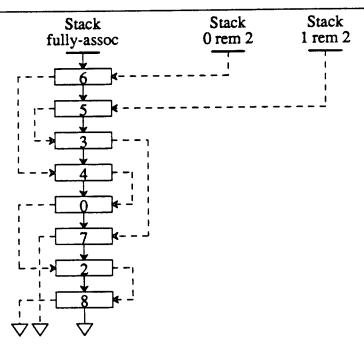

| 2-11. Concurrent Stack Simulation with Shared Storage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23          |

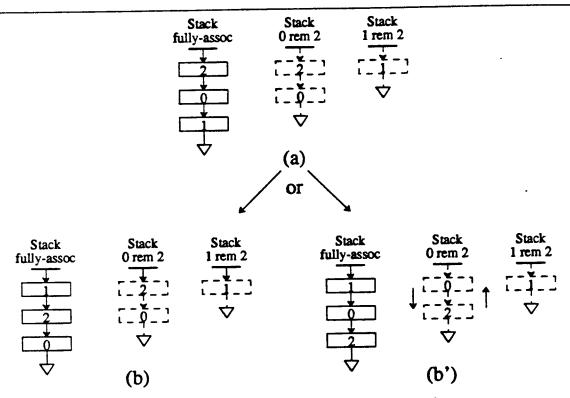

| 2-12. All-Associativity Simulation Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24          |

| and the contract of the contra | 25          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 25        |

| 2-16. All-Associativity Storage w/ Set Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 26        |

| 2-17. All-Associativity simulation w/ Set Headery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 28        |

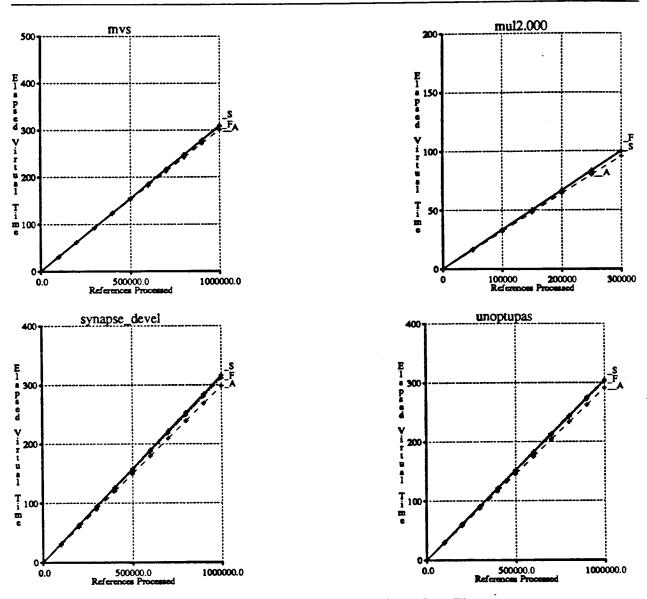

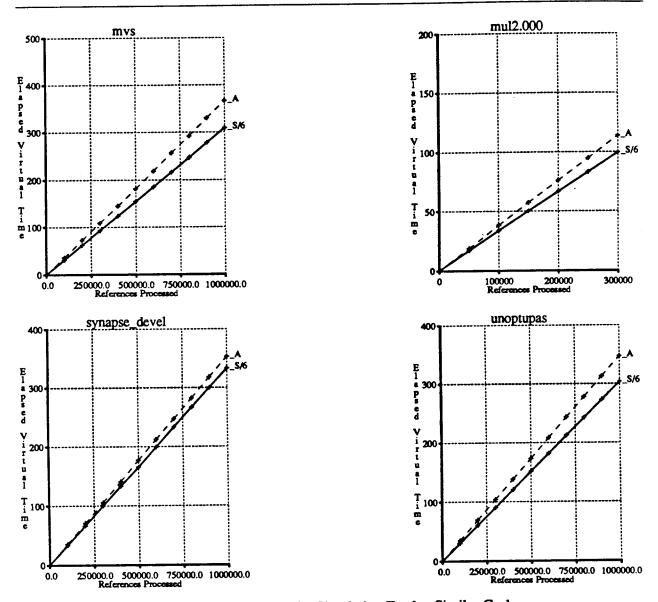

| 2-18. Random Replacement Does Not Work  2-19. Single Direct-Mapped Cache Run-Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 31        |

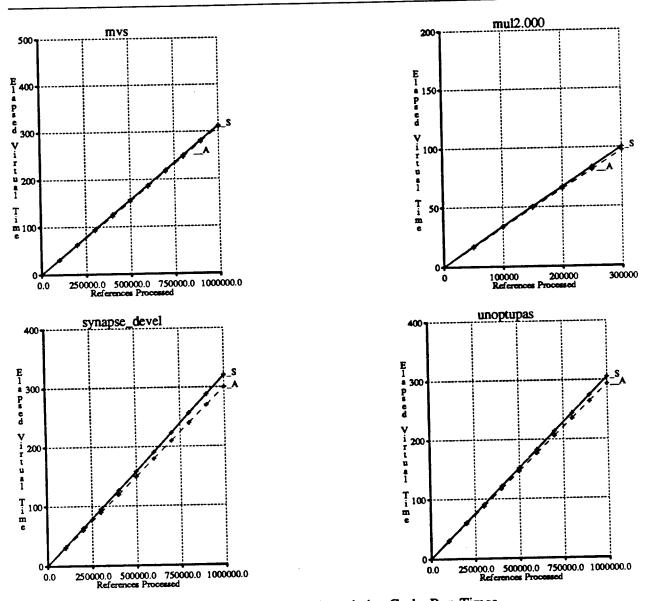

| 2-20. Single Set-Associative Cache Run-Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 32        |

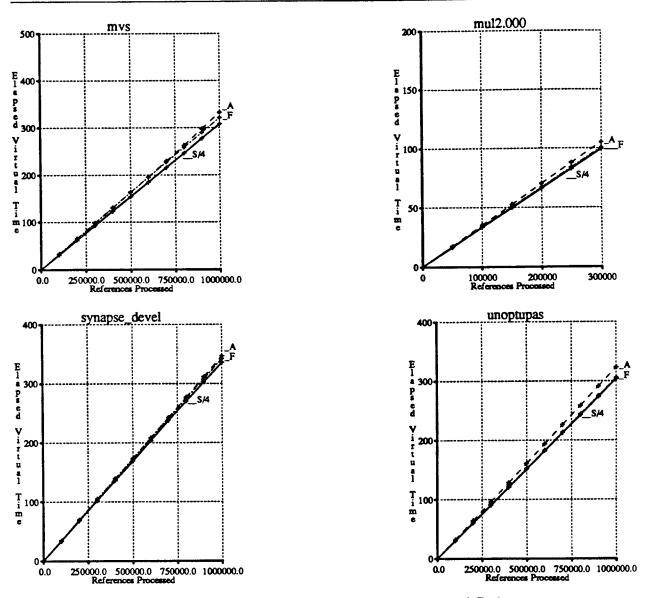

| 2-21. Run-Times for a Series of Direct-Mapped Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 33        |

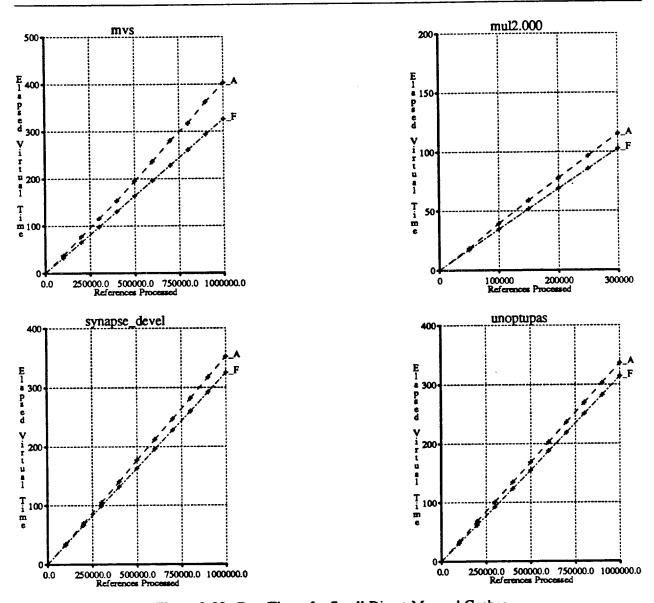

| 2-22. Run-Times for Small Direct-Mapped Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 34        |

| 2-23. Simulating a Design Region with Stack Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 35        |

| 2-24. Run-Times for Simulating Twelve Similar Caches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 36        |

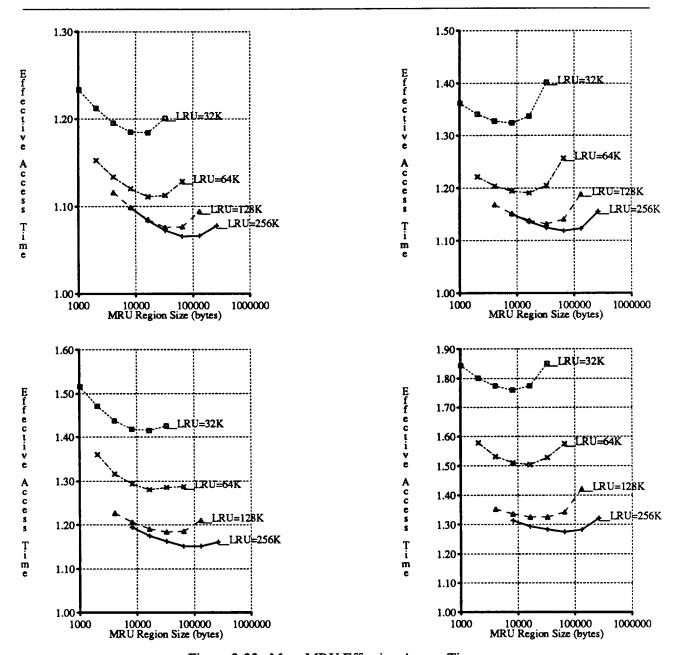

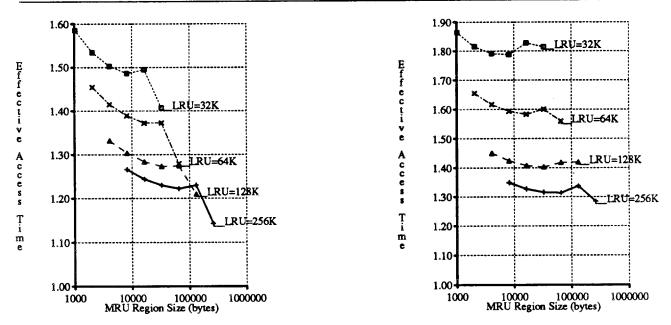

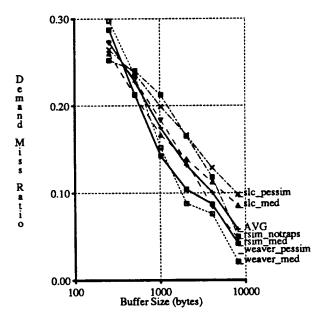

| CHAPTER 3. The Effect of Set-Associativity on Cache Memory Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

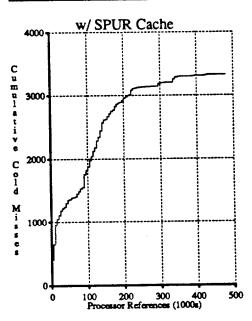

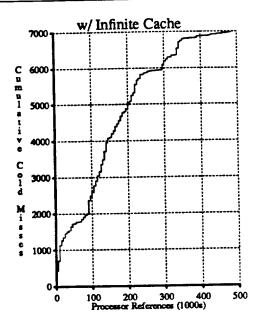

| 3-1. Cumulative Cold Misses for "mul2"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 46        |

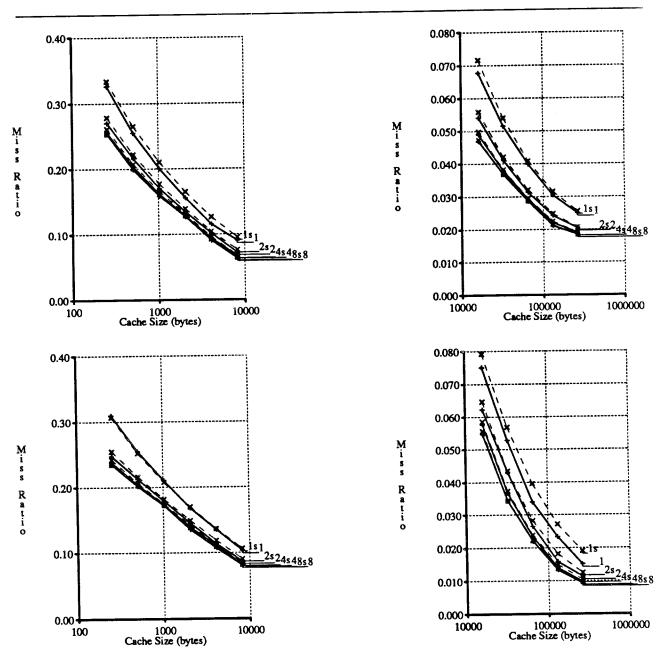

| 3-2. Cold-start Miss Ratios for Some User Traces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48          |