## A Big RISC

Richard A. Blomseth, Capt., USAF

Masters Project Final Report

Computer Science Division

Department of Electrical Engineering and Computer Science

University of California, Berkeley

Berkeley, CA 94720

#### ABSTRACT

Big RISC (BRISC) is a high-speed CPU designed with 100K ECL logic and based on the RISC I architecture. Design, performance, and cost of BRISC is presented. Performance is shown to be better than high end mainframes such as the IBM 3081 and Amdahl 470V/8 on integer benchmarks written in C, Pascal and LISP. The cost, conservatively estimated to be \$132,400, is about the same as a high end minicomputer such as the VAX-11/780. BRISC has a CPU cycle time of 46 ns, providing a RISC I instruction execution rate of greater than 15 MIPs.

BRISC is designed with a Structured Computer Aided Logic Design System (SCALD) by Valid Logic Systems. An evaluation of the utility of SCALD for computer design is also included.

July 18, 1983

The work reported herein was supported in part by Defense Advance Research Projects Agency (DoD) ARPA Order No. 3803, Monitored by Naval Electronic System Command under Contract No. N00039-81-K-0251, and the U.S. Department of Energy under Contract DE-AT03-76SF00034, Project Agreement DE-AS03-79ER10358.

| Richard A. Blomseth |

|---------------------|

| Author              |

|                     |

|                     |

| A Big RISC          |

|                     |

|                     |

|                     |

| •                   |

|                     |

| Title               |

| , ·                 |

### RESEARCH PROJECT .

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, to partial satisfaction of the requirements for the degree of Master of Sciences, Plan II.

Approval for the Report and Comprehensive Examination:

| white the  |                 |                    |

|------------|-----------------|--------------------|

| Committee: | D. A. Patterson | , Research Adviser |

|            | July 18, 1983   | Date               |

| , -        | Jal L. Jath     | _, Second Reader   |

| -          | July 17, 1983   | _, Date            |

# Table of Contents

| 1. Introduction                    | 1  |

|------------------------------------|----|

| 1. Introduction                    | 1  |

| 1.1. RISC I Instruction Set        | 2  |

| 1.1.1. RISC I Instruction Set      | 2  |

| 1.1.2. Register File               | 3  |

| 1.2. Berkeley RISC Implementations | 4  |

| 2. BRISC Design                    | 4  |

| 2.1. Pipeline Timing               | 5- |

| 2.2. BRISC Hardware Design         | 5  |

| 2.2.1. Data Path                   | 5  |

| 2.2.1.1. PCs AND ADDRESS           | 8  |

| 2.2.1.2. CACHE                     | 8  |

| 2.2.1.3. REGISTER FILE             | 9  |

| 2.2.1.4. ALU PATH                  | 9  |

| 2.2.1.5. SHIFTER PATH              | _  |

| 2.2.1.6. SPECIAL REGISTERS         | 9  |

| 2.2.1.7. RESULT LATCH              | 10 |

| 2.2.2. Control                     | 10 |

| 2.2.2.1. Control Hardware          | 10 |

| 2 2 2 2 Control 'Microcode'        | 10 |

| 2 2 2 3 Support Processor          | 11 |

| 2 Performance Analysis             | 11 |

| 3.1 BRISC Performance              | 12 |

| 3 1 1 CPU Speed                    | 12 |

| 3 1 1 1 CPU Cycle Time             | 12 |

| 3 1 1 2 CPU Cycles Per Instruction | 14 |

| 3.1.1.3. Design Changes            | 14 |

| 3 1 2 Memory Speed                 | 17 |

| 3.9 Renchmark Comparisons          | 20 |

| 4 Cret                             | 23 |

| 5. Closing Remarks                 | 26 |

| 5.1 Comments on SCALD              | 26 |

| 5.1.1. SCALD Speed                 | 26 |

| 5.1.2. Graphics Editor             | 27 |

| 5.1.3. Compiler                    | 27 |

| 5.1.4. Timing Verifler             | 2  |

| 5.1.5. Simulator                   | 25 |

| 5.1.5. Simulator                   | 34 |

| Appendix A. BRISC Instruction Set  Appendix B. Commercial Cache Summary  Appendix C. Effective Cycle Time Calculation  Appendix D. BRISC Parts List  Appendix E. BRISC Drawings  Appendix F. DAPL Microcode Listings | e Summary ime Calculation Listings | Lessons Learned  Future Work  Conclusion  Acknowledgements | 33    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------|-------|

| Appendix C. Effective Cycle Time Calculation  Appendix D. BRISC Parts List  Appendix E. BRISC Drawings  Appendix F. DAPL Microcode Listings                                                                          | me Calculation Listings            | endix A. BRISC Instruction Set                             |       |

| Appendix D. BRISC Parts List  Appendix E. BRISC Drawings  Appendix F. DAPL Microcode Listings                                                                                                                        | Listin <b>g</b>                    |                                                            |       |

| Appendix E. BRISC Drawings Appendix F. DAPL Microcode Listings                                                                                                                                                       | Listin <b>gs</b>                   | endix C. Effective Cycle Time Calculation                  |       |

| Appendix F. DAPL Microcode Listings                                                                                                                                                                                  | Listings                           | endix D. BRISC Parts List                                  |       |

|                                                                                                                                                                                                                      | •                                  | ·                                                          |       |

| •••                                                                                                                                                                                                                  |                                    | endix F. DAPL Microcode Listings                           |       |

|                                                                                                                                                                                                                      |                                    |                                                            | • • • |

|                                                                                                                                                                                                                      |                                    |                                                            |       |

|                                                                                                                                                                                                                      |                                    |                                                            |       |

|                                                                                                                                                                                                                      |                                    |                                                            |       |

### A Big RISC

Richard A. Blomseth, Capt., USAF

Masters Project Final Report

Computer Science Division

Department of Electrical Engineering and Computer Science

University of California, Berkeley

Berkeley, CA 94720

#### 1. Introduction

Even though microprocessors are now available with the power of previous years' minicomputers, and are expected to get faster, there will always be problems where even the fastest microprocessors are not fast enough. This paper describes the design of BRISC (Big Reduced Instruction Set Computer), a high performance 32-bit processor designed with discrete 100K ECL logic. BRISC uses the same concepts used to speed up the RISC I microprocessor; <sup>14</sup> these concepts include a simplified instruction set and overlapping register windows.

BRISC is designed with a Structured Computer-Aided Logic Design (SCALD) system. <sup>11</sup> Most of the CPU design has been entered into the SCALD system and post processed for physical design errors. The worst case logic path has been timing verified using SCALD to approximate the CPU cycle time. Some simulation has been done (about 70% of the design) to verify functional correctness of the CPU design.

This paper describes the design, performance and cost of BRISC. Performance and cost are compared to other high performance computers to evaluate the usefulness of the RISC architecture for high performance computer design. The rest of this section describes the RISC I architecture and the Berkeley RISC implementations. RISC I architecture is described because BRISC uses the RISC I architecture at the instruction set level.

## 1.1. RISC I Architecture

Fundamental to RISC architectures is the concept that frequent, time consuming tasks should be done as fast as possible, and infrequent tasks may be done more slowly. RISC I is designed to execute high level languages such as C and Pascal efficiently, so the RISC I instruction set concentrates on the most time consuming operations of high level languages. Two time consuming operations optimized by the RISC I instruction set are: (1) procedure calls and returns, that account for 40% of the time spent in traditional architectures; and (2), data references to local scalar variables and constants, that account for over 60% of data references. <sup>14</sup> RISC I is

designed for integer programs; floating point operations are done in software and are therefore significantly slower than integer operations.

The remainder of this section provides a brief introduction to the RISC I architecture. For more information, the reader is referred to the RISC I Principles of Operation. 25

RISC I has two significant departures from traditional computer architectures. First is a small and simple instruction set; second is a large register file consisting of overlapping register windows.

## 1.1.1. RISC I Instruction Set

The RISC I instruction set consists of 31 instructions and supports five addressing modes. Three address modes — register, immediate and indexed — are supported directly by the instruction set. Two addressing modes — absolute and register indirect — may be synthesized from indexed addressing. Only the LOAD and STORE instructions access the main memory, all other instructions read and write registers. Most operations read two registers and write into a third. Because of the register-to-register orientation of the instruction set, RISC processors complete an instruction nearly every memory cycle. LOAD and STORE instructions are the only exceptions and require one or two extra cycles.

RISC/E added 23 instructions to the RISC I instruction set to support relative loads and stores, increased access to the special registers, and support for the virtual memory. BRISC uses the RISC/E instruction set. The BRISC instruction set is included in Appendix A.

### 1.1.2. Register File

RISC I relies on multiple sets or windows of 32-bit registers to speed up calls, returns, and access to local variables. This collection of register windows is known as the register file.

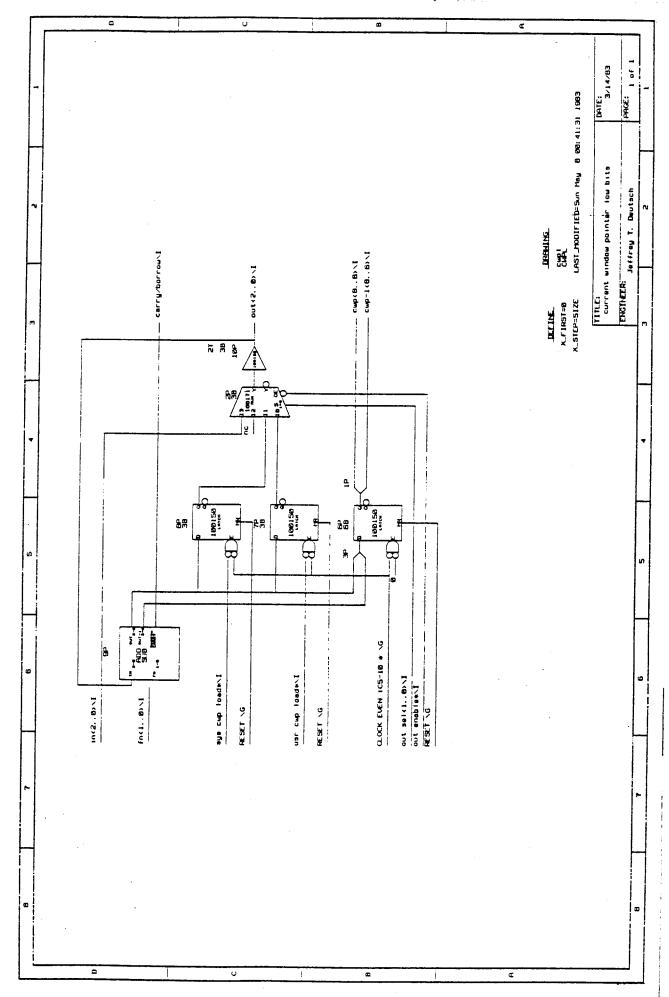

BRISC contains a register file consisting of 123 32-bit registers. Sixteen of these registers (the register window) are available to a procedure at any one time, and a new set is allocated for a CALL and deallocated for a RETURN. Memory accesses are not required to save and restore the return address or other registers as required by conventional architectures. Furthermore, movement of data is not required for parameter passing because allocation and deallocation of registers for CALL and RETURN is done with overlapping windows. Overlapping register windows usually allow the program's complete activation stack to remain in registers, so that the CPU references fast registers, rather than slow main memory.

BRISC has two sets of 123 registers, one set is active in user mode, the other is active in system mode. RISC I registers spill into memory if the 123 register limit is exceeded. Ten of the 16 registers in a register window are shared by all windows in a register file and are known as the

global registers.

# 1.2. Berkeley RISC Implementations

Four RISC processors have been designed at UC Berkeley since the project was started in 1980. Two of them are single chip NMOS designs (RISCs I and II), and two are discrete logic ECL designs (RISC/E and BRISC).

#### RISC I

RISC I is the first RISC designed at Berkeley. It was designed by five students in 6 months. The 44,500 transistor chip was fabricated using 4 micron NMOS technology, and is 10.3 x 7.74 mm (406 x 305 mils). Through the use of computer aided design tools, RISC I worked on first silicon. Even though the chips work, they do not meet their design goal for speed. The design goal for RISC I was a 400 ns cycle; RISC I runs with a 2000 ns cycle. Even at 2000 ns RISC I runs C programs faster than an 8 MHz 68000. 14

#### RISC II

RISC II was designed by two graduate students in two years and is a more refined processor than RISC I. Building on the success of RISC I in using computer aided design tools to design chips that were logically correct, RISC II used a newer set of tools that included a program to verify the speed of the chip (Crystal). <sup>10</sup> The longer design cycle and better tools resulted in a better circuit design and working chips with 75% more registers (138), 25% less area (10.3 x 5.8 mm), and four times the speed (500 ns cycle time) of RISC I.

RISC II uses a three stage pipeline as opposed to the two stage pipeline of RISC I. A similar three stage pipeline was subsequently used by RISC/E and BRISC. The three stage pipeline is discussed in Section 2.1.

### RISC/E

RISC/Extended (RISC/E) was a paper design of a 10K ECL CPU and cache also started in 1980 to see if the RISC I concepts could be applied to a high performance discrete logic CPU. <sup>5</sup> The result is the design for a fast CPU with a 75 ns cycle time consisting of 450 10K ECL parts. The cache also has a cycle time of 75 ns and consists of 550 10K ECL parts.

#### BRISC

Big RISC (BRISC) continues the work started by RISC/E to verify the applicability of RISC concepts to high performance computer design. Jeff Deutsch and the author designed the first version of BRISC during the Winter quarter of 1983. BRISC started as a translation of the 10K ECL design of RISC/E to 100K ECL. Minor changes were made throughout the design to accommodate differences between the 10K and 100K parts. The ALU, shifter, program counters, and control logic were redesigned for increased speed and decreased parts count. Timing was kept nearly identical to RISC/E.

The resulting design from the Winter quarter consisted of 606 parts. The high part count was due primarily to the lack of buffers in the SCALD library to prevent loading violations; instead parts were replicated to obtain the desired drive. Simulation was completed on the ALU, shifter and program counters, and post processing was started. Timing verification was not performed because of bugs in the timing verifier.

The author continued work on BRISC during the Spring quarter of 1983. BRISC was redesigned to use buffers that were added to the SCALD library, and control was redesigned to require fewer bits. The resulting design uses 332 parts. The BRISC equivalent of microcode was written for the arithmetic instructions, and simulation was started for the entire design. The timing verifier became available from Valid, so enough of the design was verified to calculate the cycle time. Post processing was completed for the entire design.

BRISC is faster than RISC/E (47 ns vs. 75 ns) with fewer chips (332 vs. 550). 100K ECL is a faster logic family than 10K ECL, but was not widely available when the RISC/E project was started (1980). The 100K ECL parts tend to have more functionality than 10K ECL parts, but this functionality is bought at the expense of more pins per package. Nearly all 100K ECL parts have 24 pins, whereas most 10K ECL parts have 16 pins.

The remainder of this paper describes the design, performance and cost of BRISC.

## 2. BRISC Design

BRISC's design is based on the three stage pipeline developed by Lloyd Dickman that was used by RISC II and RISC/E. This section describes the pipeline timing and the hardware design of BRISC.

### 3.1. Pipeline Timing

BRISC pipeline timing will only be summarized here, a more complete description may be found in the RISC/E design study. <sup>5</sup> BRISC uses a two phase, non-overlapping clock. Most instructions take three cycles, or six phases, to execute. The CPU is pipelined so that three

instructions are being acted on simultaneously, allowing instructions to issue and complete at a rate approaching one per cycle. Figure 1 describes the six phases of a typical instruction, and Figure 2 shows three instructions passing through the pipeline. The pipeline is designed to make maximum use of key resources — the cache, register file, and ALU — and to minimize contentionfor these resources. The pipeline is also designed to not require pipeline flushes, all instructions entering the pipeline go through to completion unless externally interrupted.

Most instructions follow the pipeline timing shown in Figures 1 and 2 so that no complex pipeline interlocks are required. Even instructions that receive special treatment in traditional pipelines - such as CALL, JUMP, and RETURN - do not affect pipeline timing in BRISC and follow the same basic three cycle timing.

Only the LOAD and STORE instructions require more than three cycles to execute. One extra cycle is required for the memory access; a second extra cycle is required for 8- and 16-bit loads and stores to align the memory data with the register file using the shifter. The second extra cycle is not required for LOAD WORD and STORE WORD because 32-bit words are always aligned with memory.

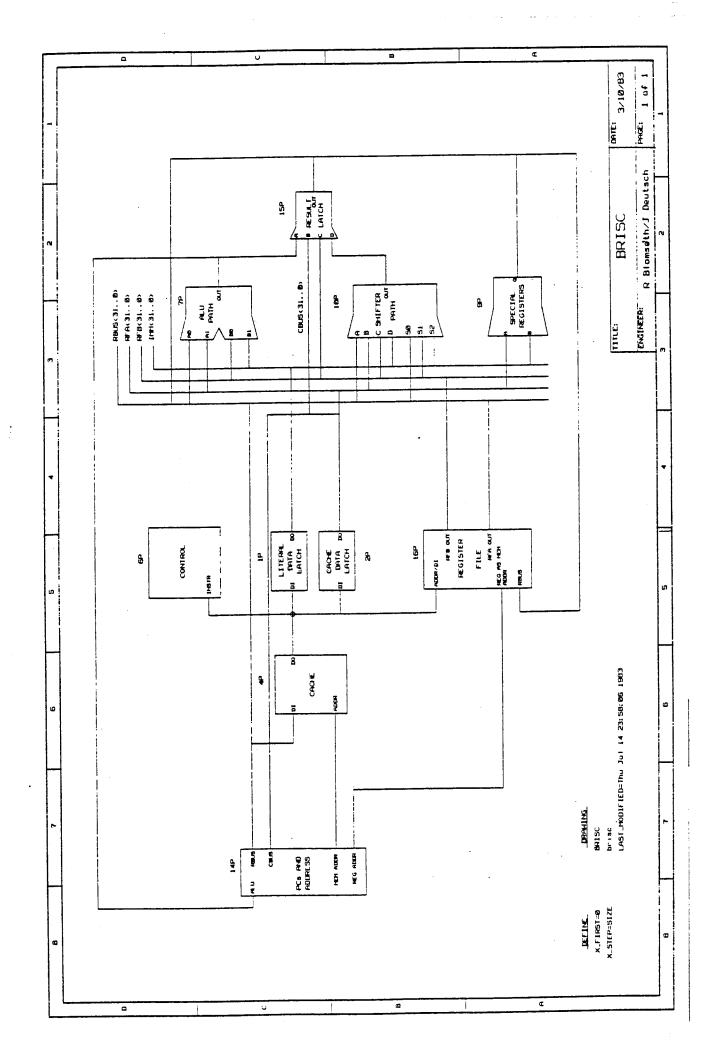

### 2.2. BRISC Hardware Design

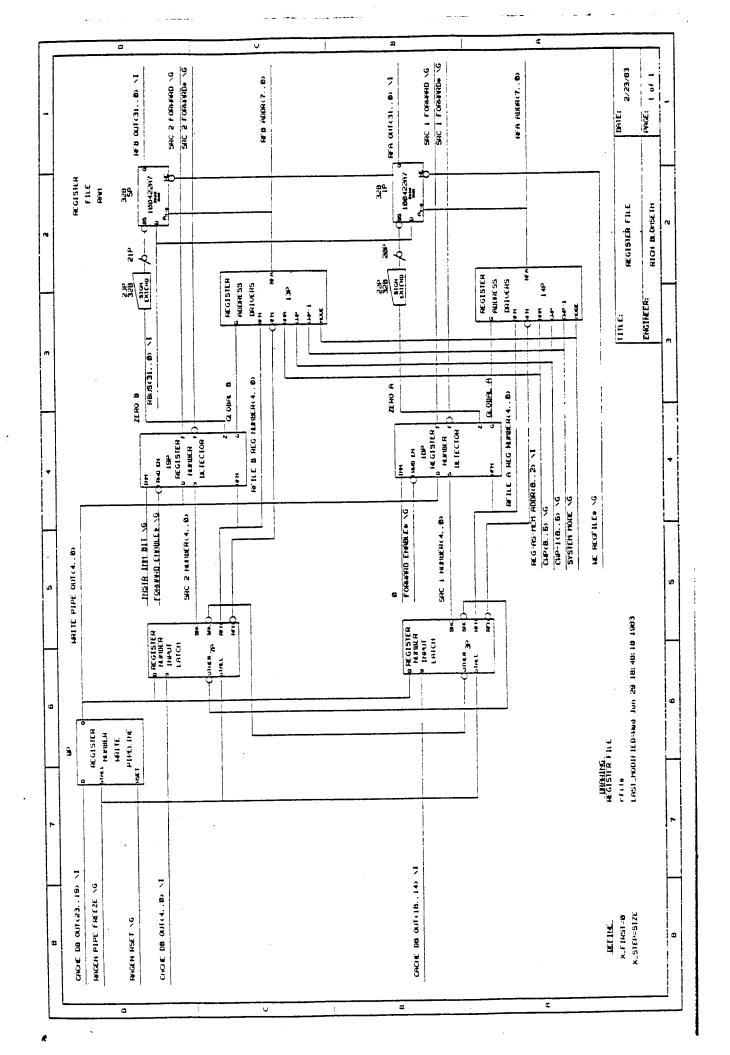

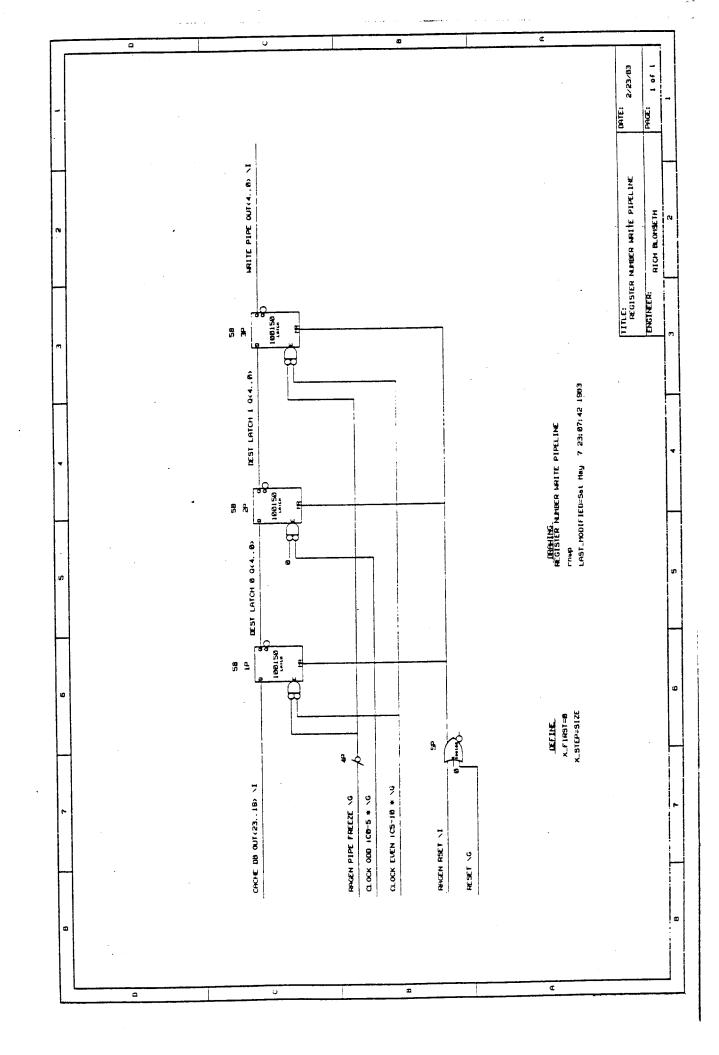

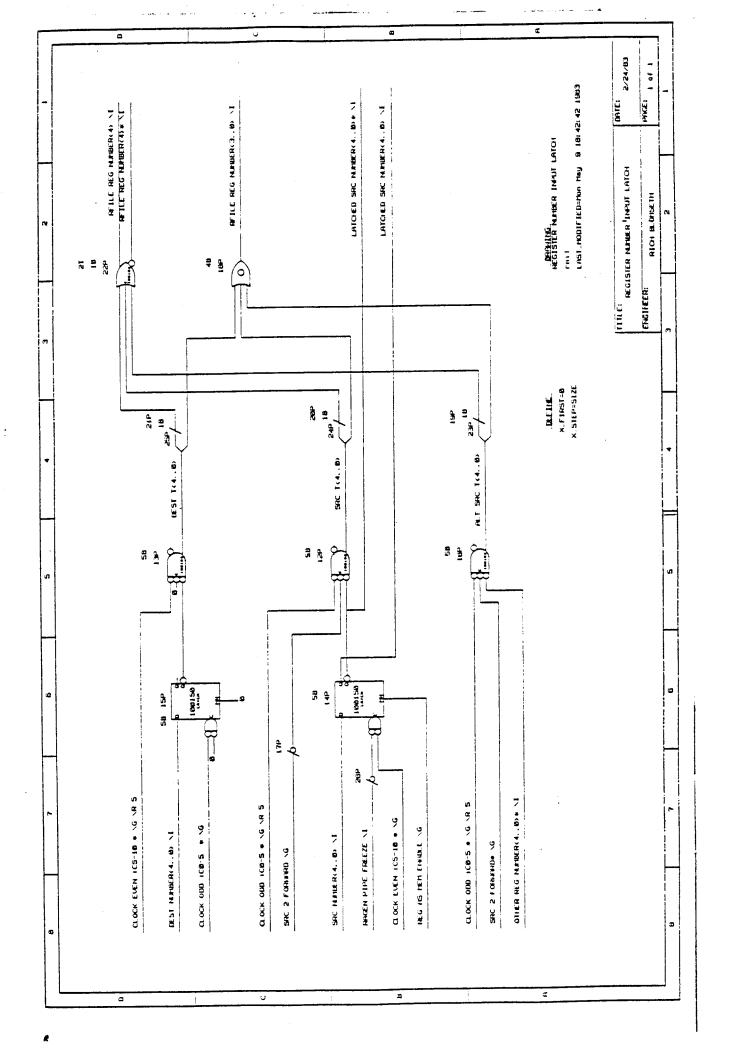

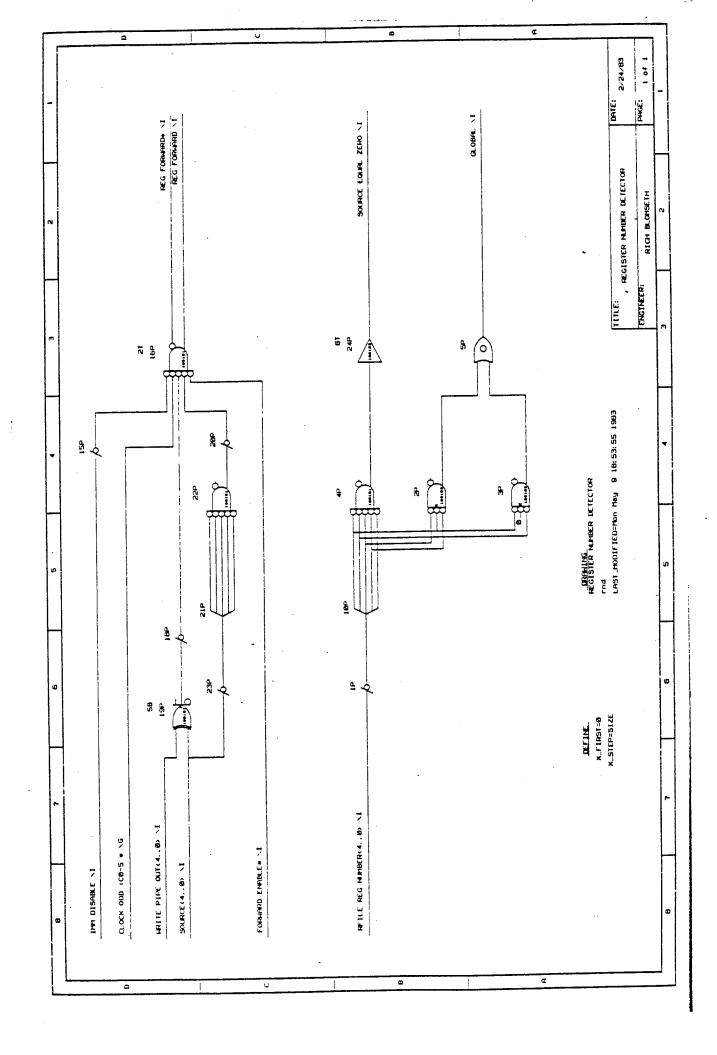

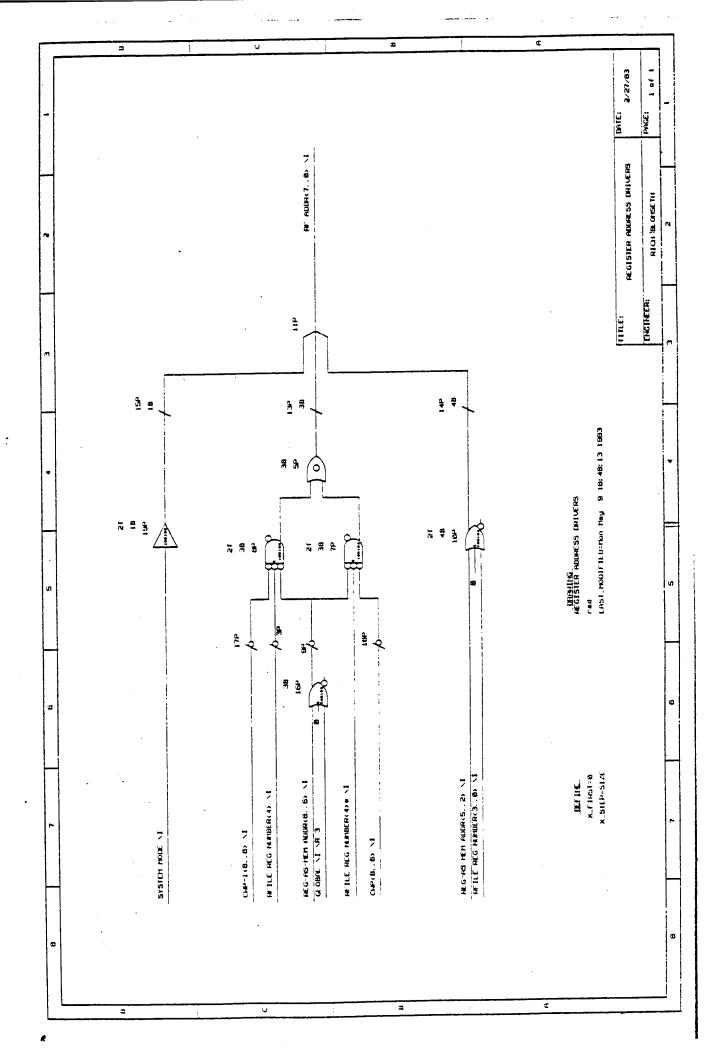

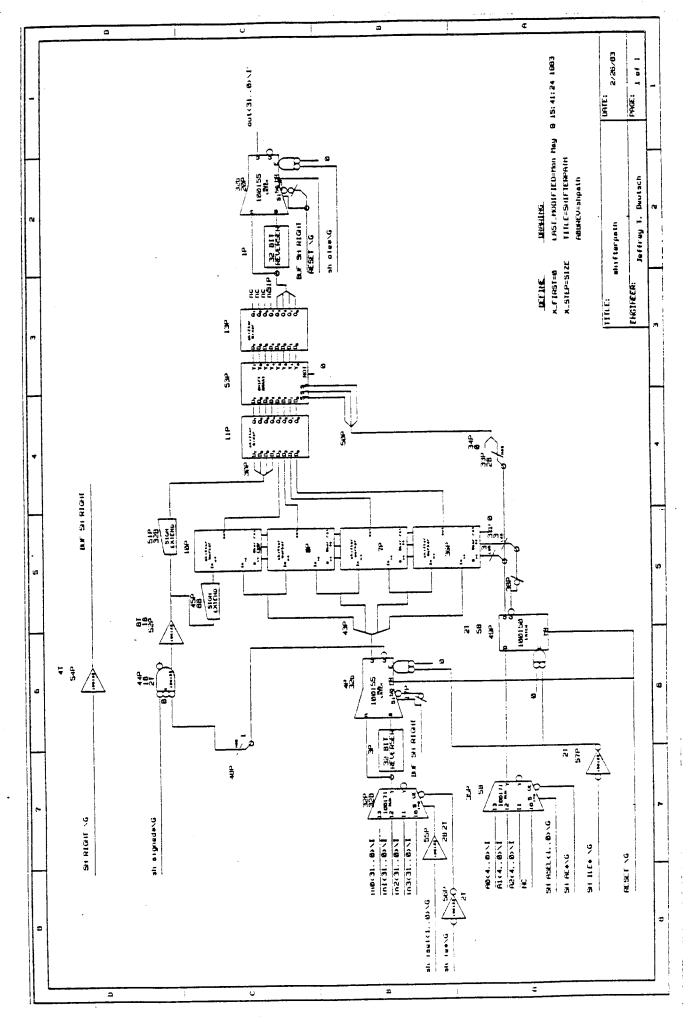

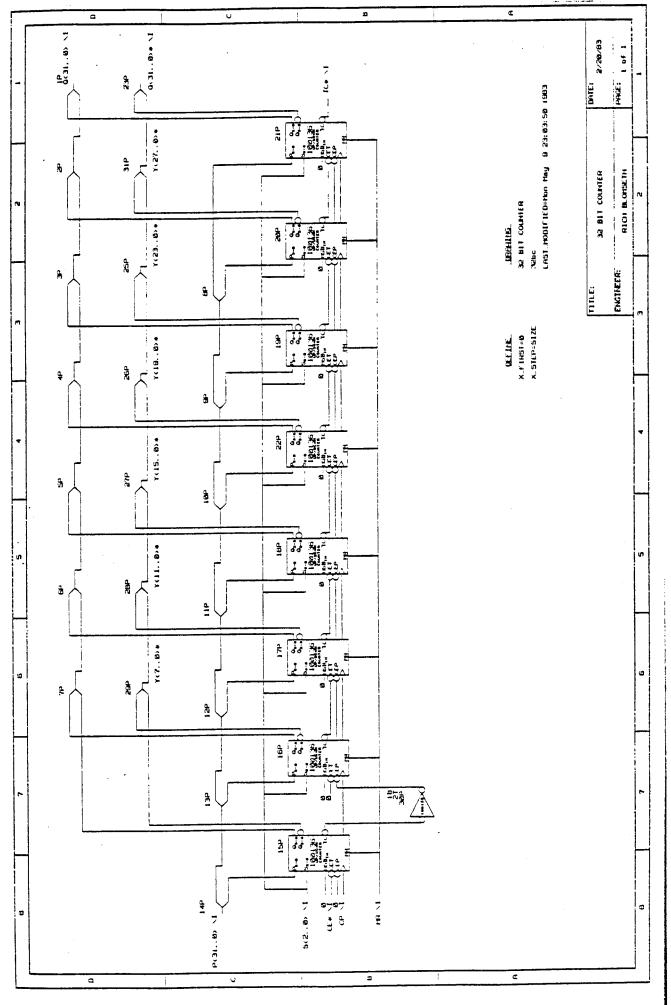

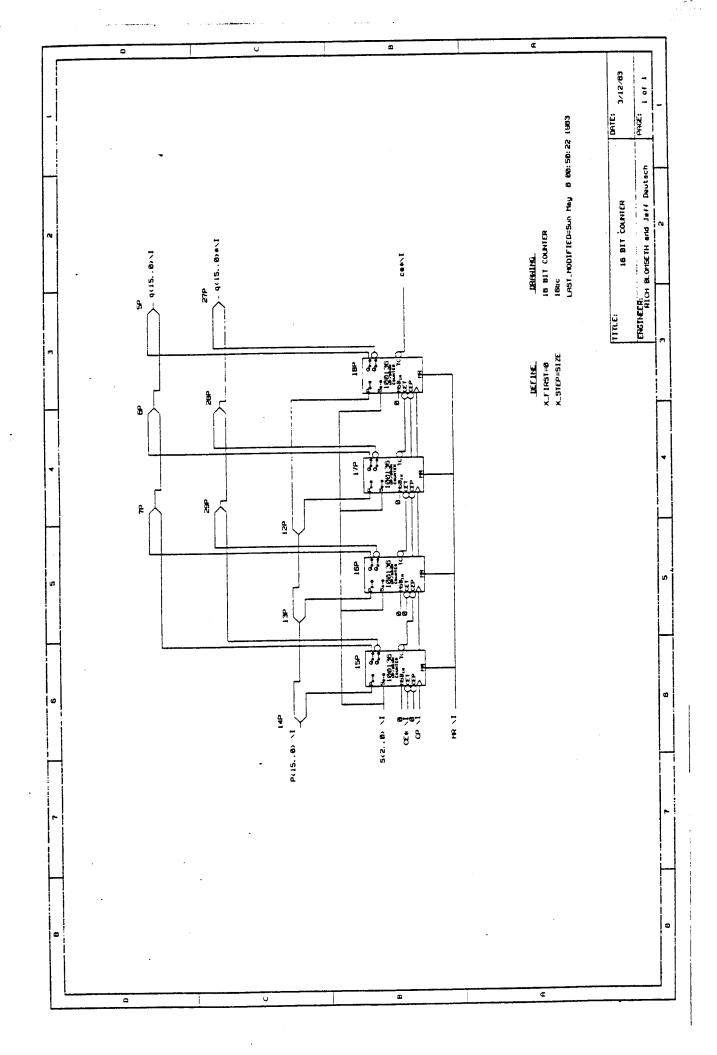

Figure 3 is the top level SCALD drawing for BRISC (Appendix E contains the complete set of SCALD drawings for BRISC). The BRISC CPU contains the ten modules shown in Figure 3. The control logic is in the CONTROL module and the other nine modules constitute the data path. Design of the BRISC data path and control is described in the following sections.

#### 2.3.1. Data Path

Most data flows from left to right in Figure 3, starting with the instruction address being generated in PCs AND ADDRESS and ending with the result in the RESULT LATCH for subsequent writing back to the REGISTER FILE. The following paragraphs describe each of the modules in the data path.

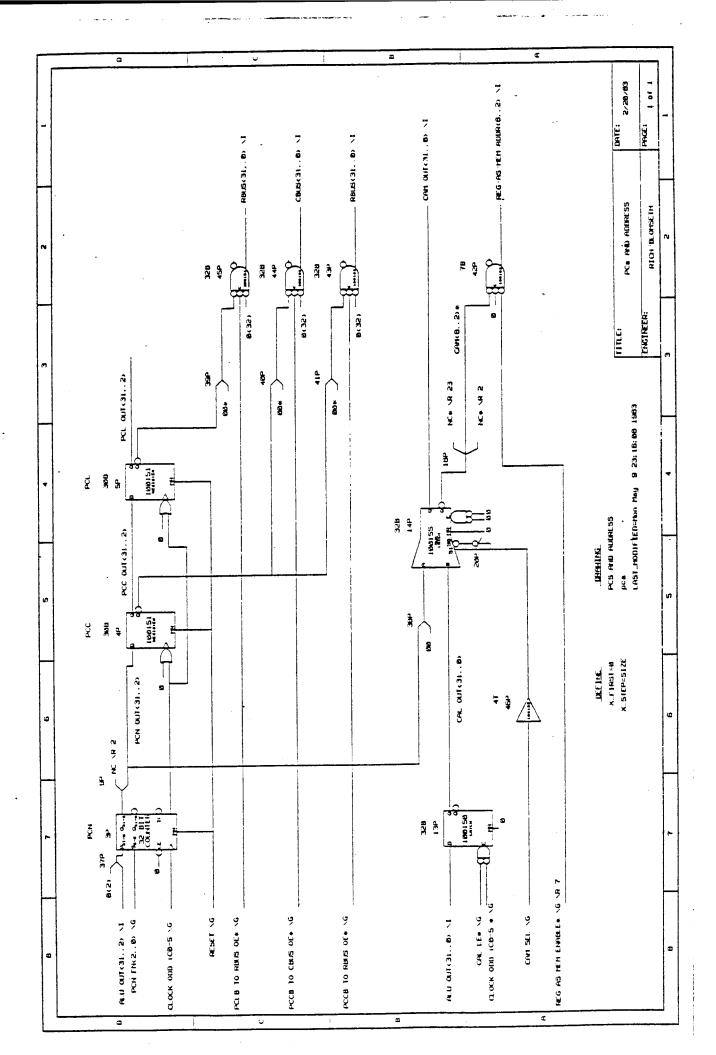

## 2.2.1.1. PCs AND ADDRESS

The top half of the PCs AND ADDRESS drawing in Appendix E contains the program counters (PCs). BRISC has three PCs: the Next PC (PCN), Current PC (PCC), and Last PC (PCL). The PCN is incremented at the start of the instruction cycle, used to fetch the next instruction, and, except for jumps, becomes the PCC at the end of the instruction cycle. The PCC holds the value of the program counter for the currently executing instruction and the PCL holds the 'last' value of the PC, useful for interrupts and exceptions.

|            | CYCLE 1:<br>FETCH |          |           |        | CYCLE 3:<br>WRITE |  |

|------------|-------------------|----------|-----------|--------|-------------------|--|

| +1         | <b>\$</b> 2       | Ф3       | Φ4        | ф5     | <b>ф</b> 6        |  |

| Start Read | Read              | Decode   | Execution | Buffer | Write RF          |  |

|            | Complete:         | Complete | Complete  | Result |                   |  |

|            | Start Decode      | Read RF  | ]         |        | 1                 |  |

| 1          |                   |          | 1         |        |                   |  |

| PCN-PCN+4  |                   |          | Latch     | Result |                   |  |

TIME -

FIGURE 1. BASIC TIMING CYCLE. The three cycles of an instruction, and correspondingly the three stages of the execution pipe, are called Petch, Esecute, and Write. At the start of phase 1, the Next Program Counter (PCN) is gated onto the cache address bus and by the end of phase 2 the instruction has been decoded. In phase 3, the two operand registers are read from the register file and the Arithmetic Logic Unit (ALU) and shifter operations are selected. By the end of phase 4, the ALU and shift operations are complete. In phase 5, the result of the data-path operation is buffered and the sign optionally extended. Finally, in phase 6 the result is written back into the register fie.

| FET                                     | СН         | EXE        | CUTE     | WI         | RITE     |

|-----------------------------------------|------------|------------|----------|------------|----------|

| <b>+1</b>                               | <b>♦</b> 2 | <b>4</b> 3 | 44       | <b>♦</b> 8 | +6       |

| START READ                              | B          | ALU IN-    | ALU.OUT- | BUFFER     | P-RESULT |

| • • • • • • • • • • • • • • • • • • • • | GUB D.E.F) | 0.2        | 3-0      | RESULT     | 1        |

| FE:        | TCH        | EXCE       | CUTE     |             | RITE      |

|------------|------------|------------|----------|-------------|-----------|

| <b>+1</b>  | <b>♦2</b>  | <b>+</b> 3 | 44       | <b>♦</b> \$ | <b>46</b> |

| START READ | IL-        | ALU_IN-    | ALU.OUT- | BUTTER      | N-RESULT  |

|            | (אטב נאנאו | LM         | L+M      | RESULT      | 1         |

| FE         | TCH         | EXE       | CUTE       | W7         | RITE     |

|------------|-------------|-----------|------------|------------|----------|

| <b>♦1</b>  | ♦2          | ♦3        | 44         | <b>♦</b> 5 | 46       |

| START READ | 11          | SHUFT.IN- | SHIFT.OUT- | BUTTER     | R-RESULT |

|            | (SLL P.Q.R) | P.Q       | P<<9       | RESULT     | 1        |

| 1          |             |           | 1          |            |          |

| 2YPC2++ (  |             |           | RESULT-6   | HUT.OUT    |          |

FIGURE 2. STANDARD PIPELINE TIMING. The following instruction stream is shown travening the pipeliae:

SUB D.E.F

PCN-PCN+4

ADD L,M,N

SLL P.Q.R

The x-axis is time. A vertical line drawn through the three timelines would show up to three simulatazeous operations occuring in the CPU.

•

\_

Figure 3. BRISC Top Level Diagram

Œ

The bottom half of the PCs AND ADDRESS drawing shows the memory address generation.

There are two sources for the memory address going to the cache, one is the PCN for instruction fetches, the other is the ALU for loads and stores. The Cache Address Multiplexor selects the correct address source and sends it to the CACHE module.

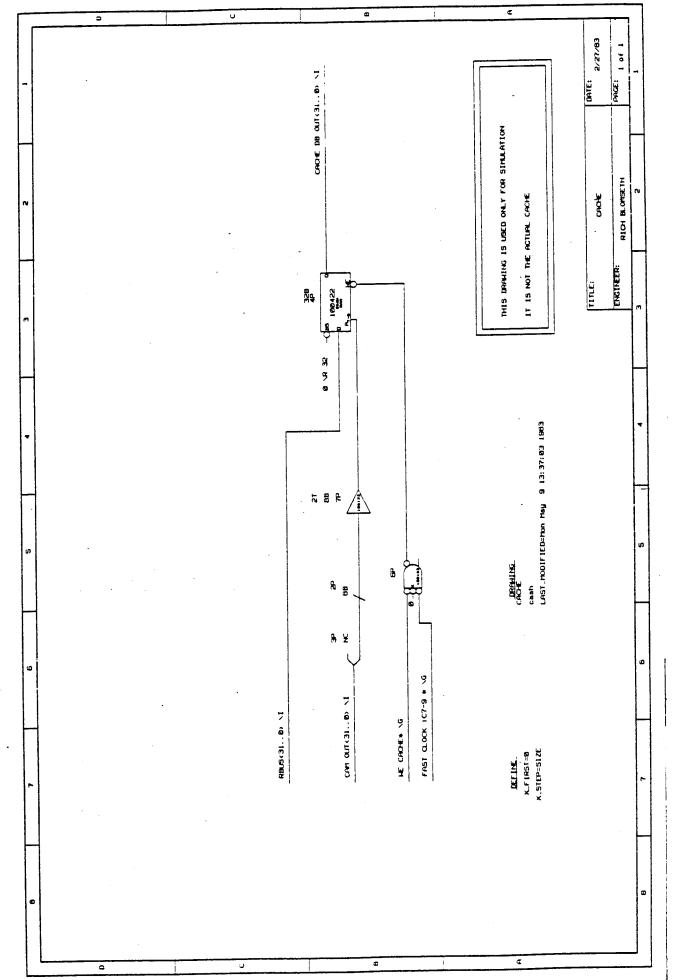

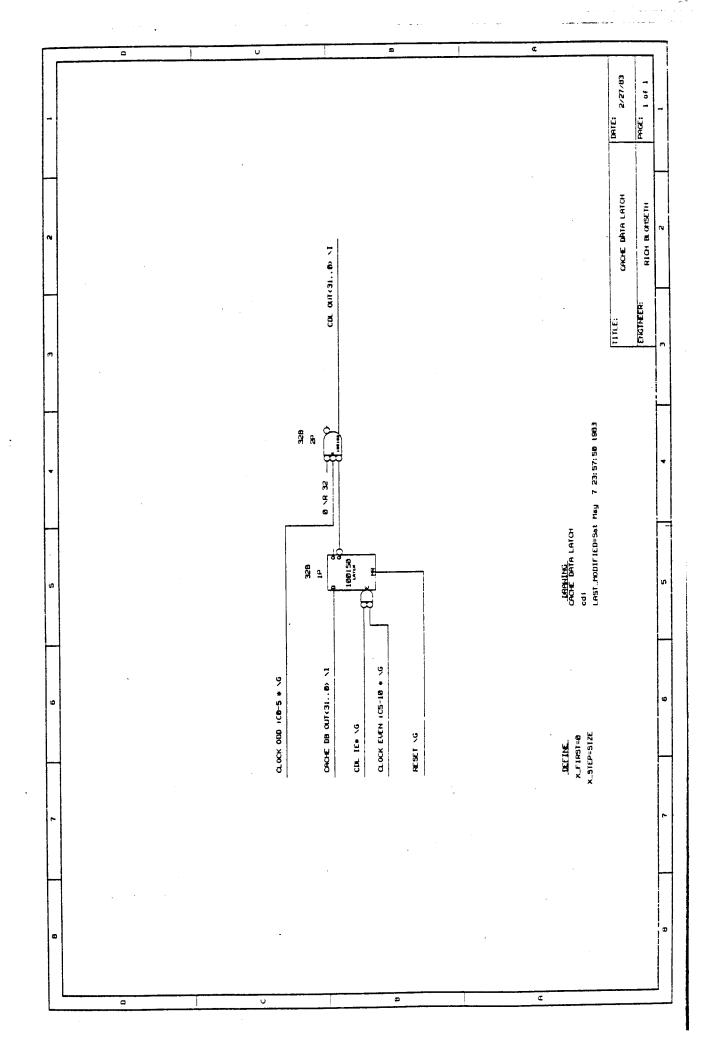

#### 3.3.1.3. CACHE

A cache has not been designed for BRISC. The 'cache' in the drawings is a 256 by 32-bit memory used only to enable SCALD simulation of the BRISC design. The actual cache would be on a separate board and would be similar to the cache designed for RISC/E. The RISC/E cache board contains a cache, Translation Buffer, and Page Usage Buffer.

## RISC/E Cache

The RISC/E cache is a 2-way set associative data and instruction cache with 2048 32-bit words. The line size may be set by software and is variable from 4 to 32 words. The number of sets is variable from 64 to 1024. A write-back policy and least recently used (LRU) block replacement algorithm is used.

## RISC/E Translation Buffer (TLB)

The purpose of the TLB is to store the most recent virtual to physical memory address translations. Accesses to virtual addresses not in the TLB are trapped and translated by software. The TLB is a 2-way set associative buffer that stores 1024 address translations and associated memory protection and replacement information.

## RISC/E Page Usage Buffer (PUB)

The PUB contains reference and modification history for each physical page frame. This information is updated by hardware and used by the page replacement software to identify pages to be replaced when more physical page frames are required.

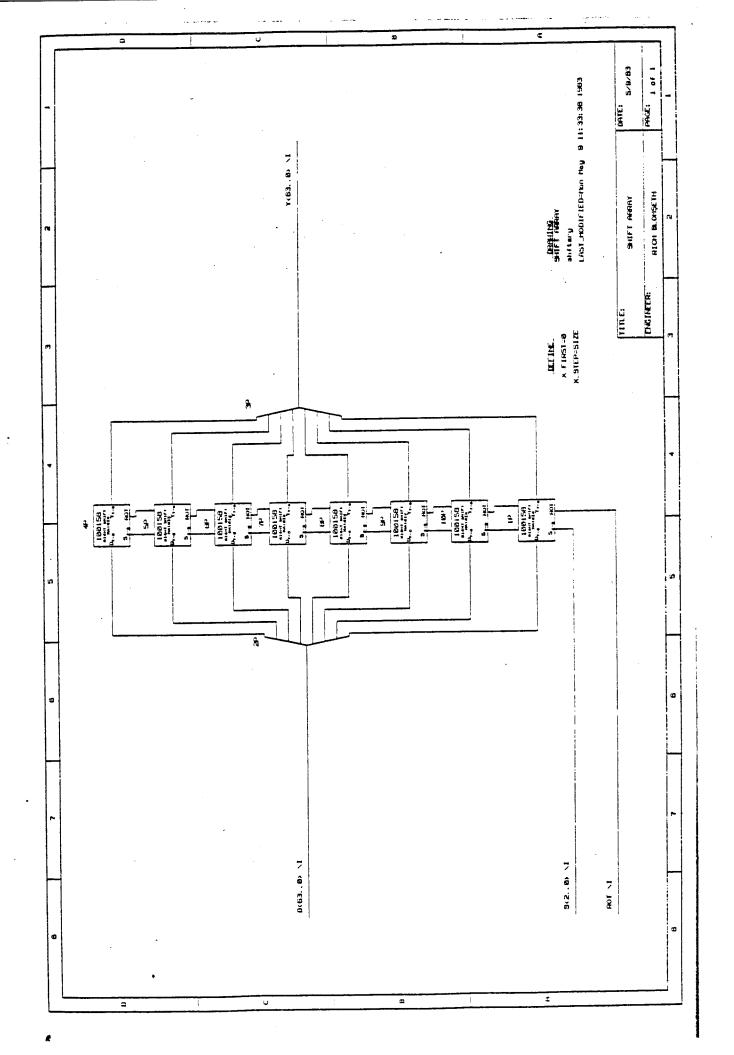

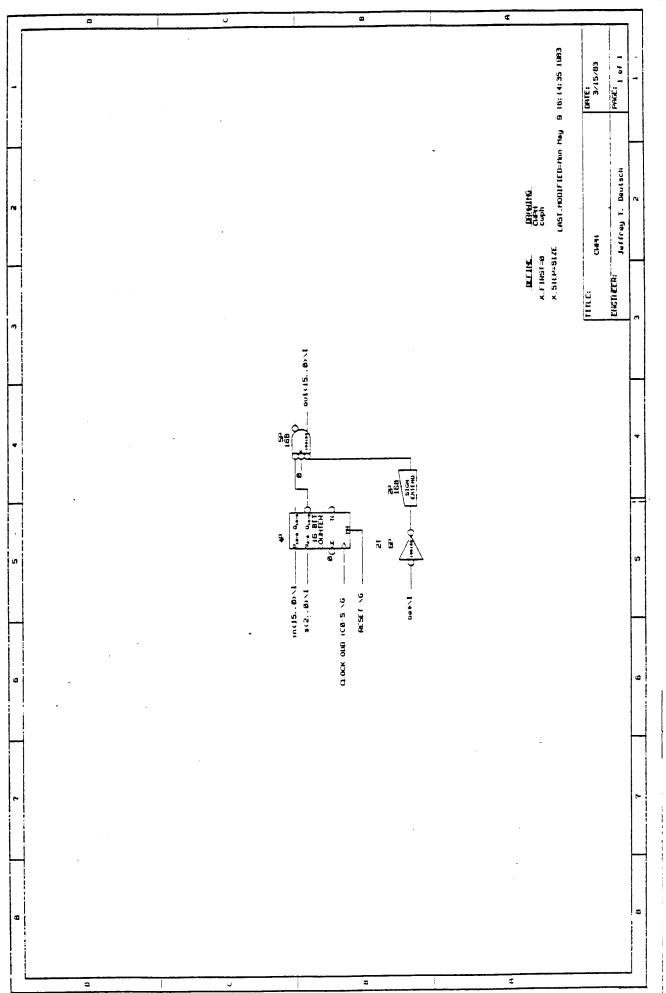

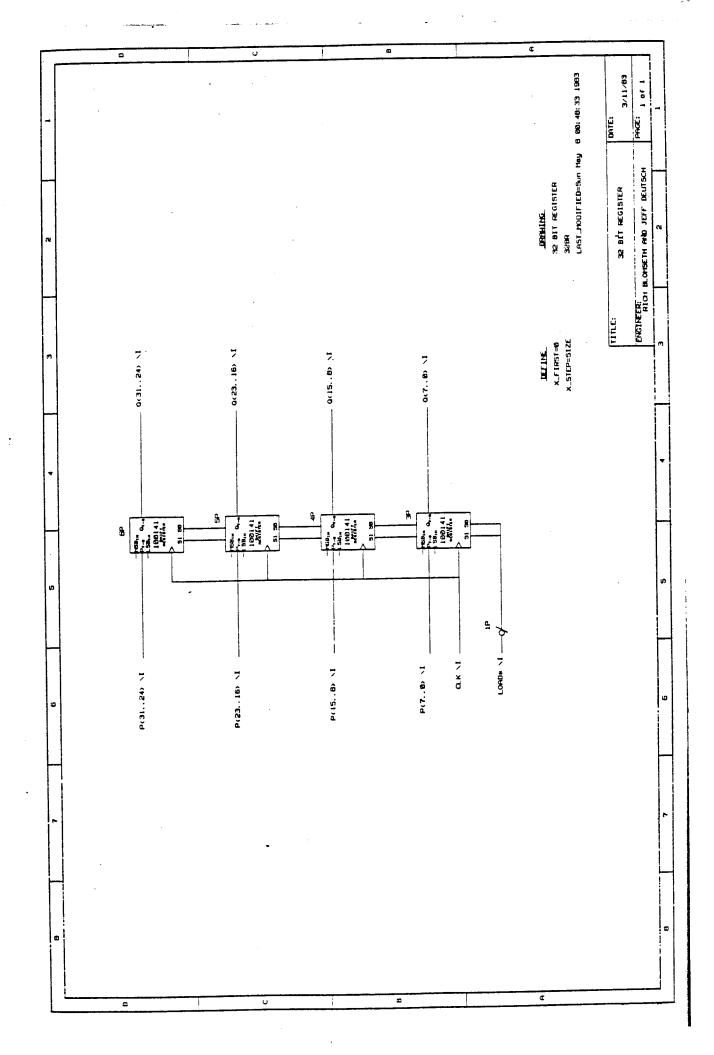

### 2.3.1.3. REGISTER FILE

The REGISTER FILE module contains two sets of 128 32-bit registers used for the system and user register files. Two independent read requests, or a single write request, may be serviced in a single clock phase. The dual read is implemented by using two redundant copies of the registers. Both copies are written simultaneously, but are read independently to retrieve two operands at a time. The register file memory is implemented with eight 256x4-bit Fujitsu ECL RAMs. The RAMs have a 7 ns access time.

The REGISTER FILE module supports mapping the 128 registers into the virtual address space so that executing processes may access any of the 128 registers by referencing the appropriate virtual address.

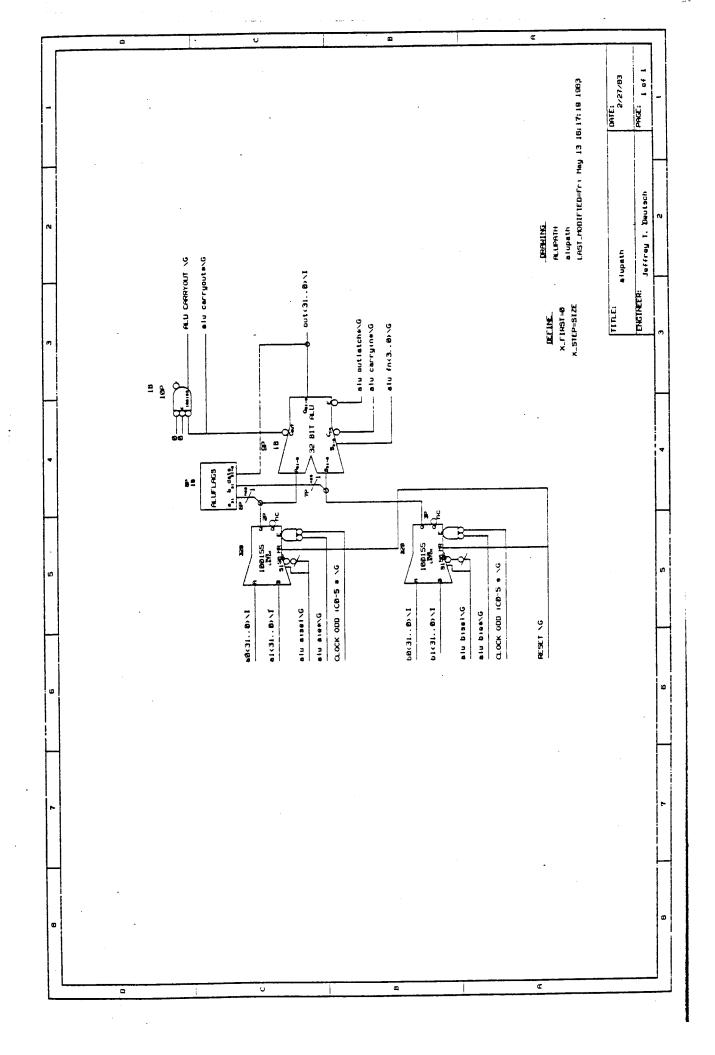

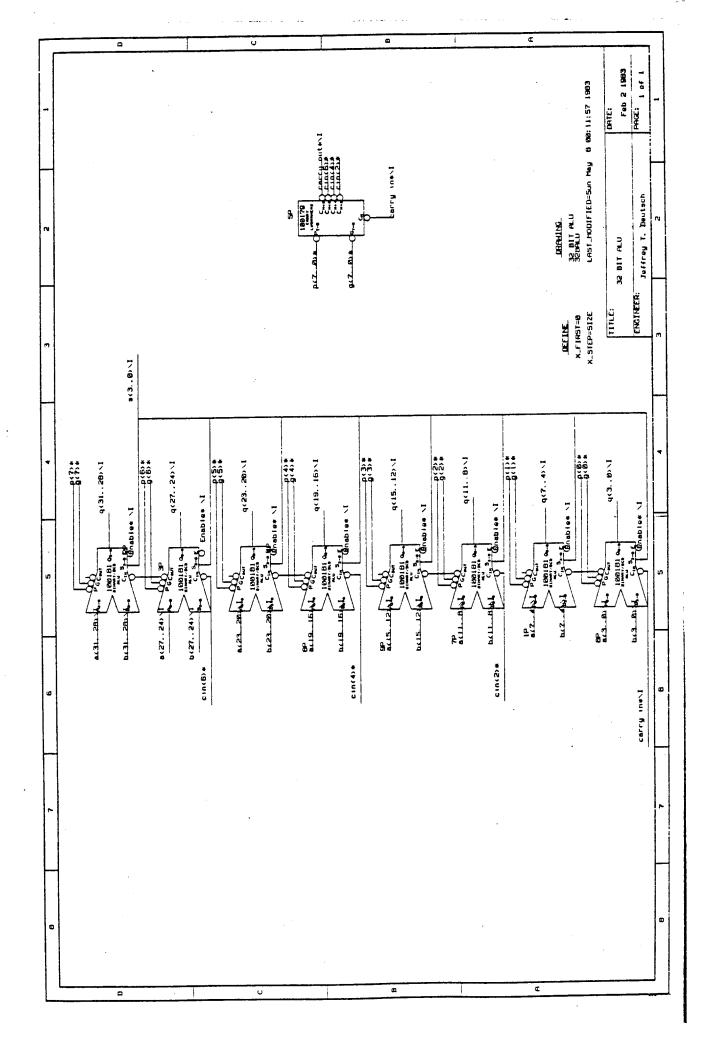

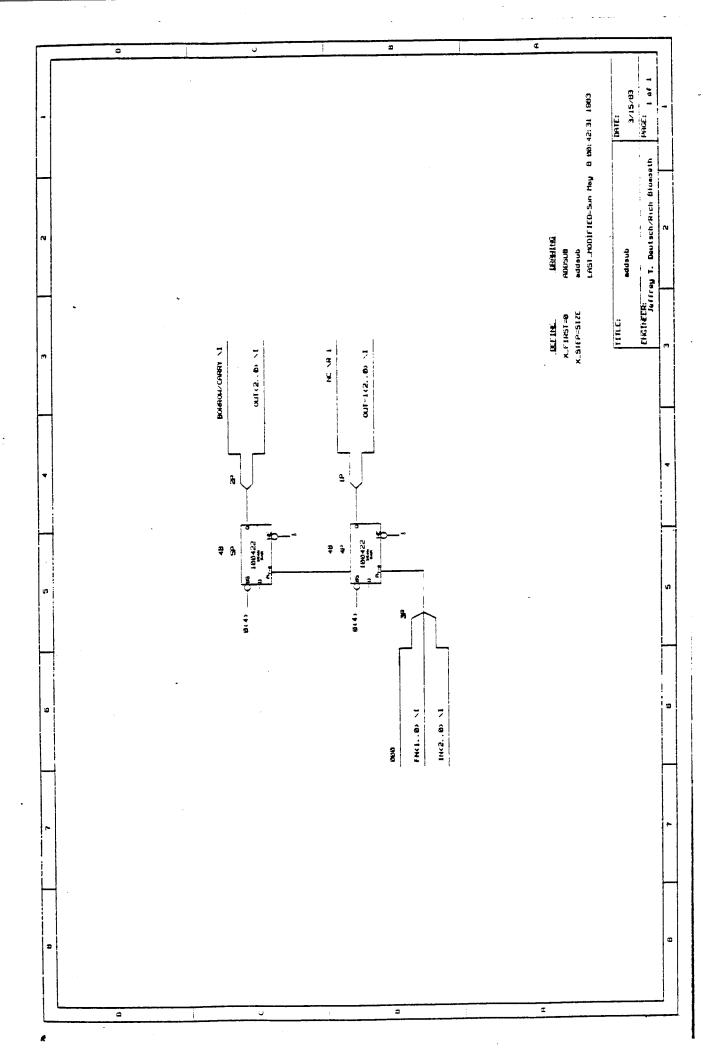

## 3.3.1.4. ALU PATH

The ALU PATH module contains a high-speed ALU and carry lookahead unit, input multiplexors and input/output latches. Each of the two inputs of the ALU can accept data from two independent sources. The sources may be either of the two source registers specified in the instruction, immediate data contained in the instruction, the Current PC for relative addressing, or the result of the previous instruction. ALU PATH output is routed to the RESULT LATCH for writing to the REGISTER FILE and also to the Cache Address Multiplexor in PCs AND ADDRESS to be used as the memory address for branches, loads and stores. All ALU operations execute in a single clock phase.

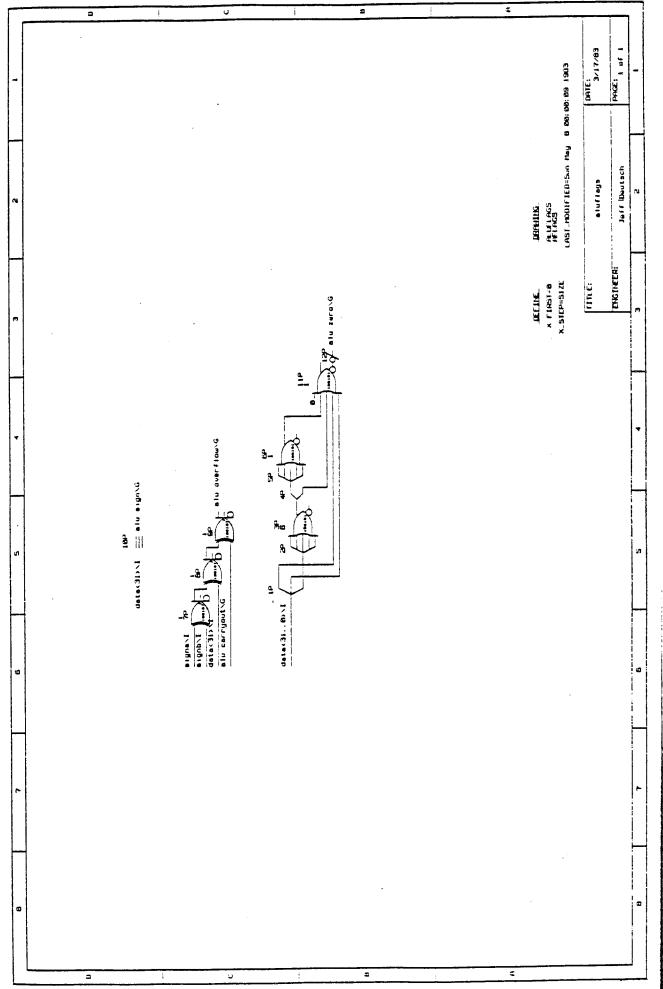

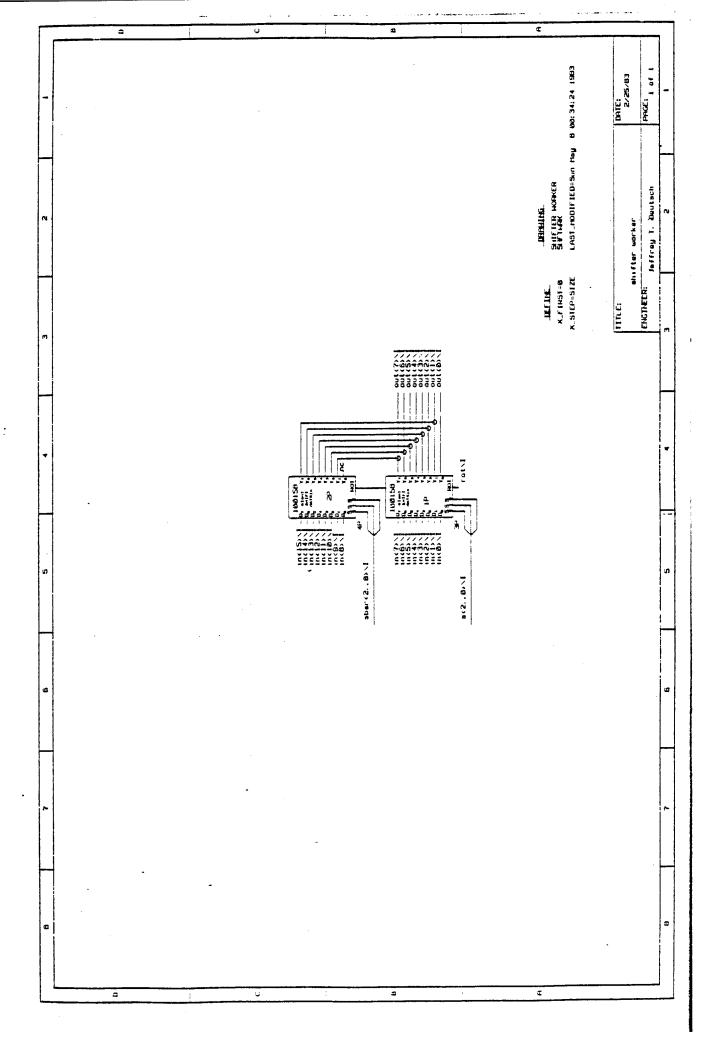

### 2.2.1.5. SHIFTER PATH

The SHIFTER PATH module performs 1- to 32-bit left or right shifts with optional sign extension. Input multiplexors and latches select from the same set of inputs used by the ALU PATH. The output is latched and routed to the RESULT LATCH for writing to the REGISTER FILE.

The basic shift part provided in 100K ECL can only do a logical shift right or a rotate. The BRISC instruction set also requires arithmetic shifts and left shifts. Arithmetic shifting is provided by extending the sign bit of the 32-bit operand to an additional 32 bits and making it the upper 32 bits of the 64-bit input to the shifter. Left shifting is provided by having a path into the shifter that reverses the input bits and then reverses the result bits on output.

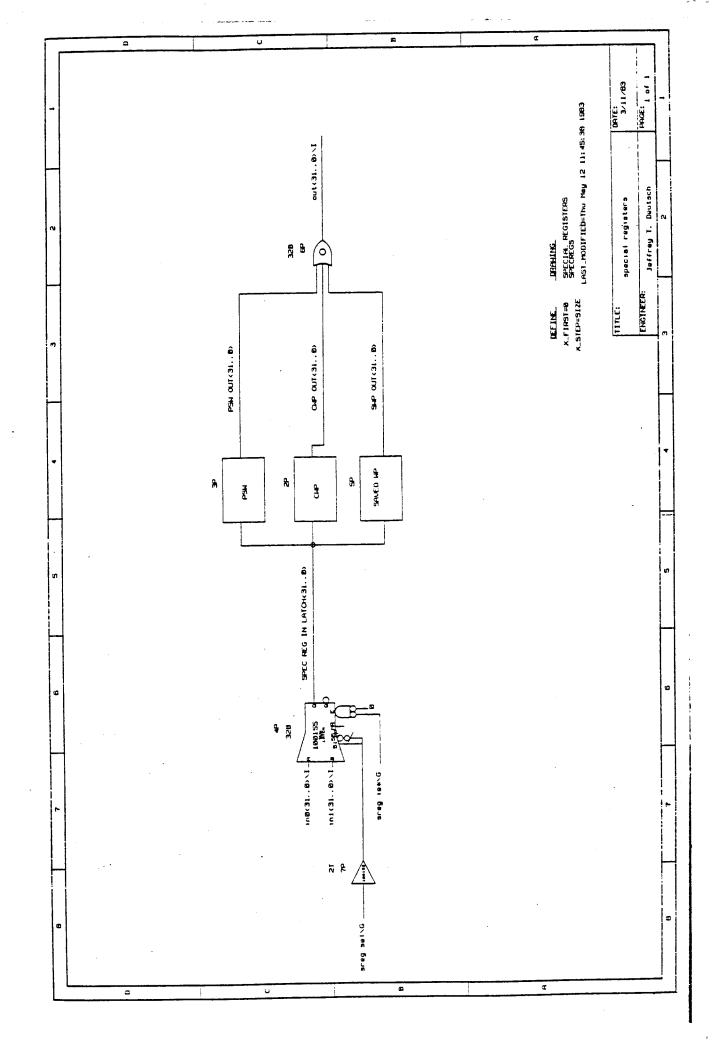

## 2.2.1.6. SPECIAL REGISTERS

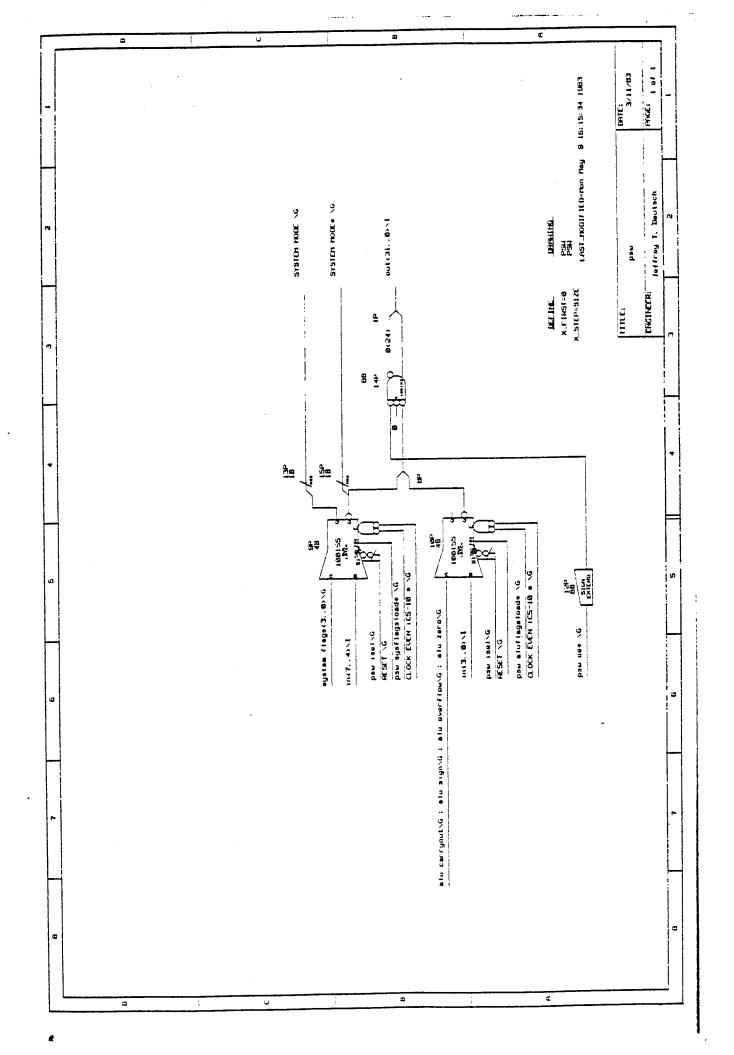

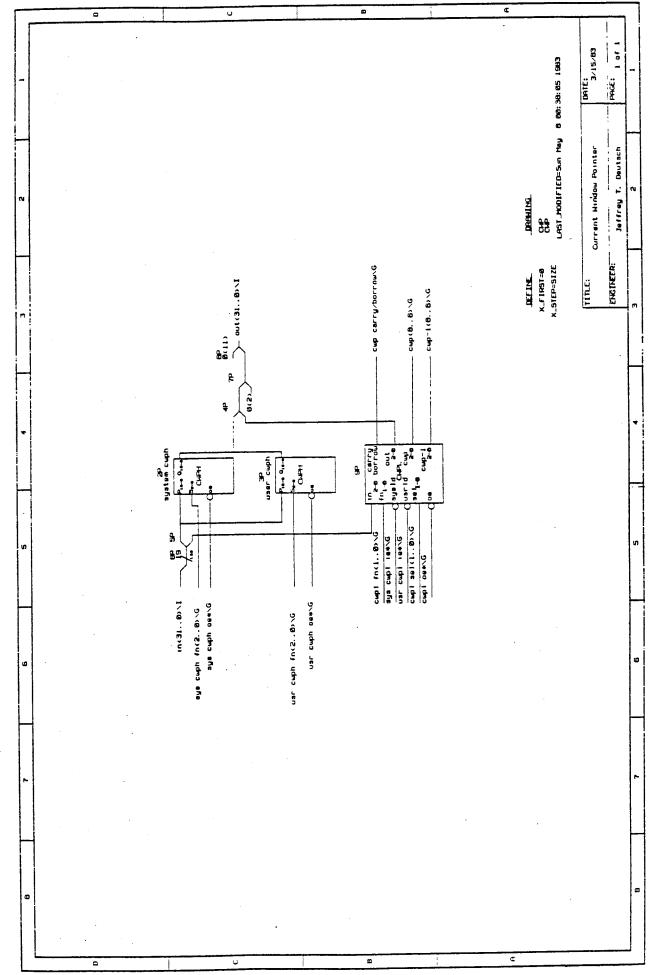

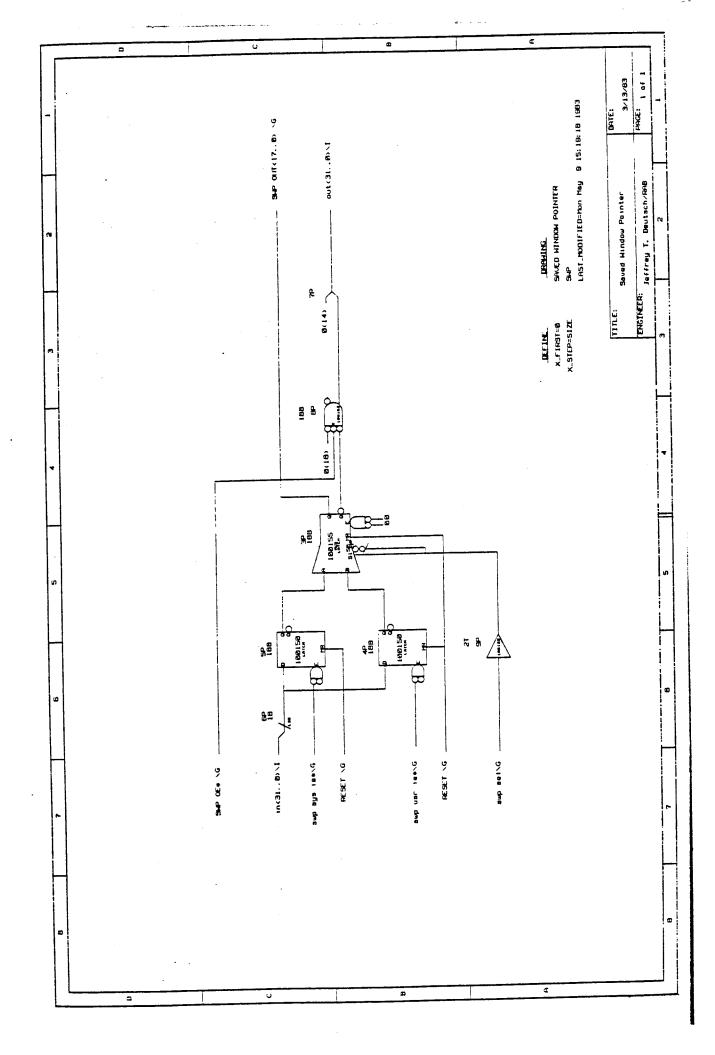

The SPECIAL REGISTERS module contains the Program Status Word (PSW), Current Window Pointer (CWP), and Saved Window Pointer (SWP). The PSW holds the ALU condition codes and a byte of CPU status flags. The CWP contains the counters and registers used to point into the currently active position in the system and user register files. The SWP points to the last words of the system and user register files that are in memory and provides detection of register window overflow and underflow for CALL and RETURN.

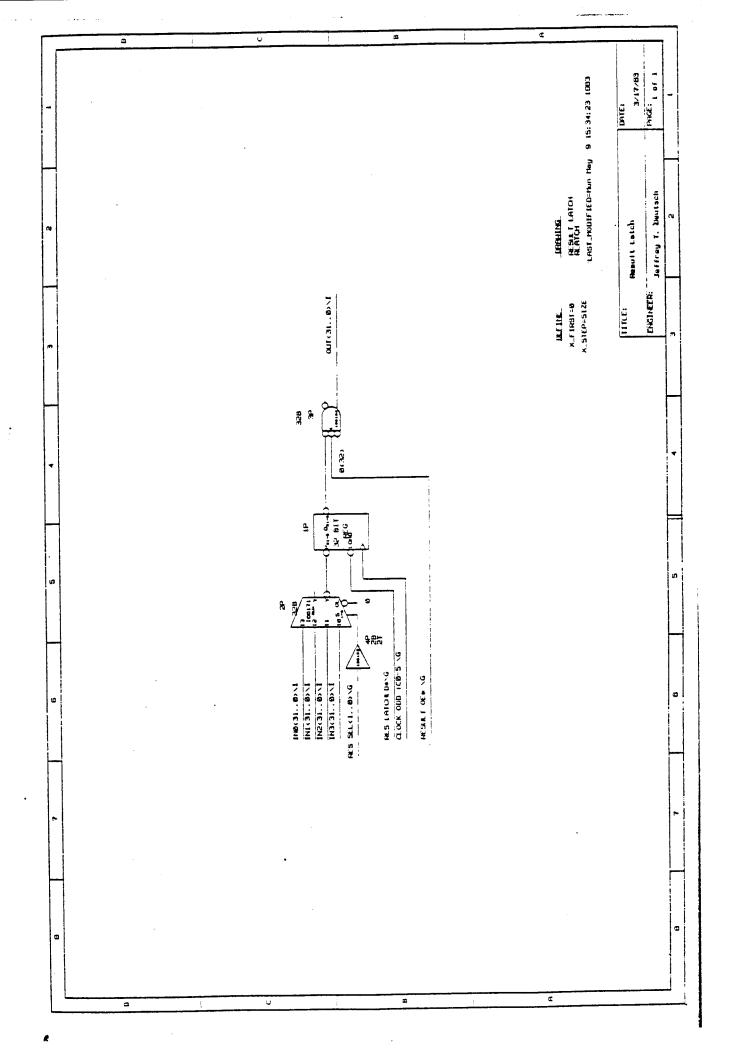

## 2.2.1.7. RESULT LATCH

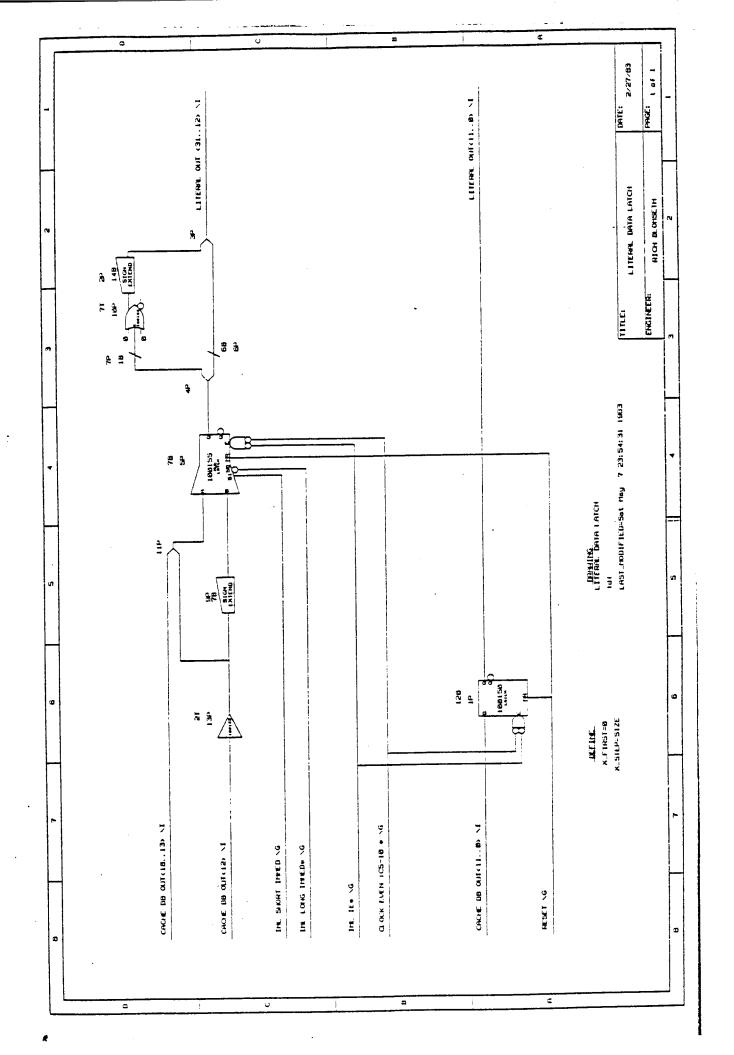

The RESULT LATCH module is composed of a 4-way multiplexer and a 32-bit latch. It serves to buffer the result of a computation at the end of each cycle. The four inputs to the RESULT LATCH are the ALU PATH output, the SHIFTER PATH output, one REGISTER FILE output and the Current PC from PCs AND ADDRESS. The output is routed to the REGISTER FILE for register writes and to the result bus (RBUS) for register forwarding. Register forwarding is required when an instruction requires the result of its preceding instruction. Because of the nature of the pipeline, the result will not have been written back to the register file, so it is routed directly to the input multiplexors.

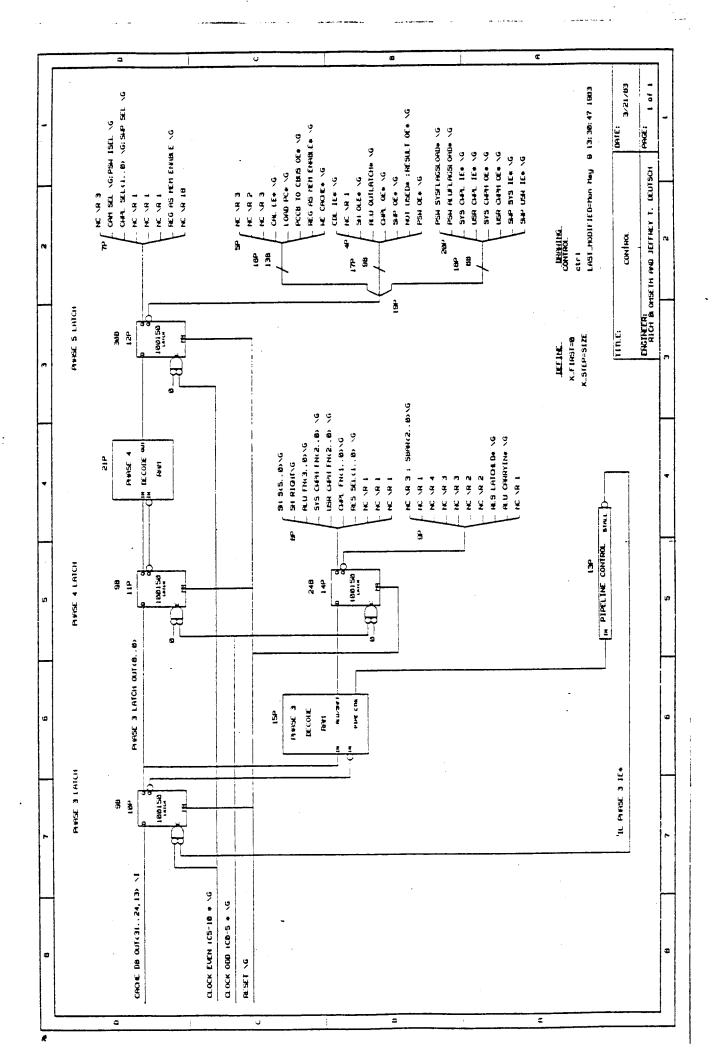

#### 2.2.2. Control

RISC processors achieve high performance by optimizing the data path, not by expanding control. The simple instruction set results in simpler control than is found in conventional processors. Control consists of pipelined latches driven by control RAMs. The RAMs are used to decode instructions and control the data path. Control is described in terms of hardware, contents of the control RAMs, and the support processor used to program the control RAMs.

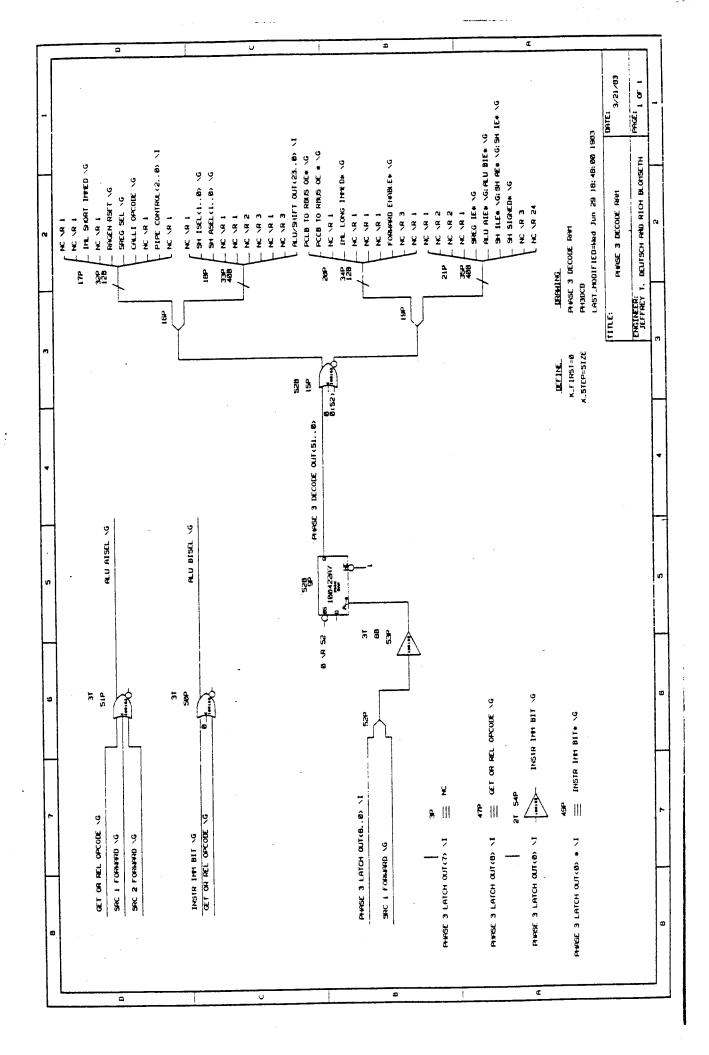

### 2.2.3.1. Control Hardware

The CONTROL module consists of a pipeline of three latches that correspond to phases 3, 4 and 5 of instruction execution. Instructions are stepped through the pipe and decoded during phases 3 and 4. Movement of control data through the control pipeline corresponds to the movement of data through the execution pipeline in the data path.

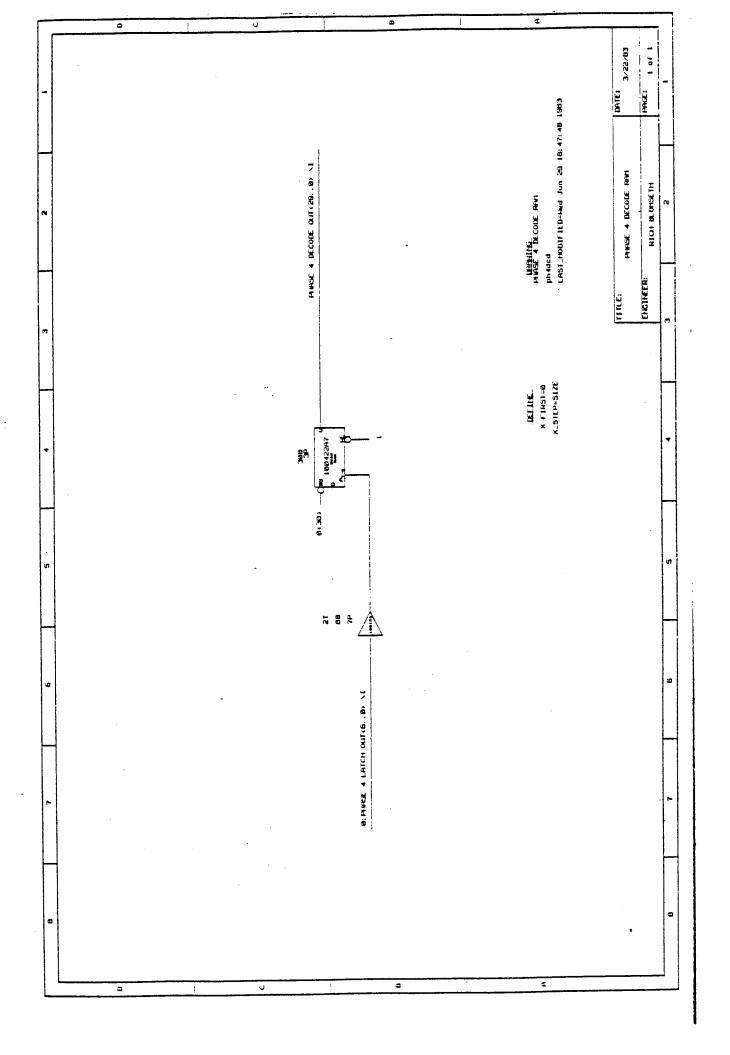

Decoding of instructions is done with RAMs in the PHASE 3 DECODE RAM and PHASE 4 DECODE RAM modules. Input to the RAMs consists of the opcode and immediate fields of the executing instruction, the outputs from the RAMs are the control signals for the data path.

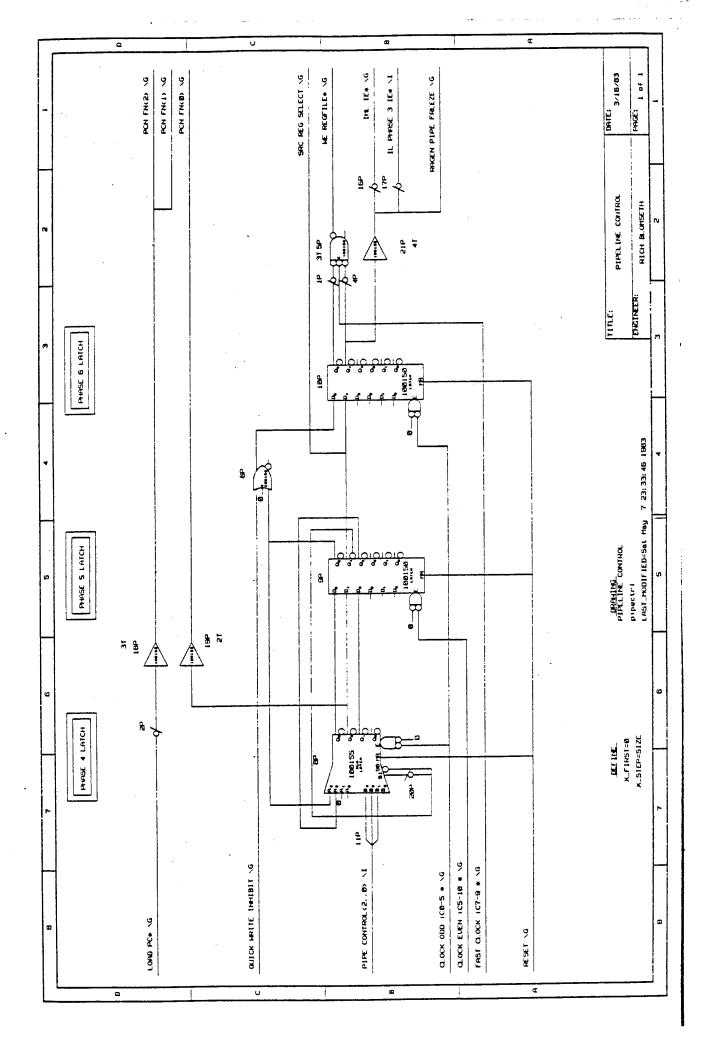

The pipeline is controlled by another set of latches in the PIPELINE CONTROL module. Input to PIPELINE CONTROL consists of the Pipe Control bits generated by the PHASE 3 DECODE RAM. These bits control insertion of one or two extra cycles for LOAD and STORE instructions.

## 2.3.3.2. Control 'Microcode'

Stone defines microprogramming as 'the use of storage to implement the control unit.' 1 By this definition, the contents of the decode RAMs in CONTROL are the BRISC equivalent of microcode. BRISC microcode, however, is much simpler than traditional microcode. Traditionally, a variable number of microinstructions are executed per machine instruction. Sequencing of

microinstructions is usually controlled by bits in the microinstructions and a microinstruction counter. BRISC always fetches exactly two microinstructions per RISC instruction, thus BRISC does not require a microinstruction counter or complex sequencing control. Sequencing of the microcode is controlled only by the instruction stream; each opcode field is decoded to the 54-bit microcode word during Phases 3 and 4. Only two bits affect timing in any way, they are the Pipe Control bits described above.

A microcode assembler called *DAPL* is used to create microcode for BRISC. <sup>15</sup> Only a subset of the full capability of DAPL is required because of the simplicity of the BRISC microcode. DAPL is used primarily to allow for symbolic names instead of absolute bit patterns in order to identify the field names and field contents of the microcode. Symbolic field names and contents simplify shuffling bits as the microcode is finalized.

The microcode for BRISC has not been completed. Enough microcode has been written to allow simulation of the BRISC arithmetic instructions. A listing of the microcode as DAPL input is included in Appendix F.

## 2.2.2.3. Support Processor

The support processor initializes contents of the control RAMs. The support processor may also be used to debug the BRISC hardware. Serial inputs and outputs of the edge-triggered shift registers used as latches in BRISC may be tied together to allow scan-in scan-out of processor state by the support processor. Some of the flow-through latches currently used by BRISC may be converted to edge-triggered shift register latches to provide more of the processor state to the support processor. Additional hardware may be added to allow single stepping the BRISC CPU with the support processor.

The interface to the support processor has not been designed, nor has a support processor been selected. It is envisioned that the interface to the support processor will have minimal impact on the BRISC design, and that any commercially available micro or minicomputer may be used for the support processor.

### 3. Performance Analysis

BRISC performance is estimated in terms of benchmark performance, and is compared to the same benchmarks run on other high performance computers.

## 3.1. BRISC Performance

BRISC performance is determined by the speed of the CPU, memory, and Input/Output (I/O) subsystems - and also by the degree of overlap of each. Degradation of performance by the I/O subsystem is assumed to be minimal for the benchmarks used, and is not considered. The benchmarks do not include system overhead because task time is measured instead of elapsed time; therefore, system overhead is not considered.

As a result of ignoring I/O and system overhead, only CPU and memory subsystem speed is used to determine BRISC performance. CPU speed is first considered to determine the CPU cycle time; then this time is degraded by the memory subsystem overhead to calculate an estimate of BRISC performance.

BRISC performance calculation can only be an approximation because of the number of variables that affect performance. As a result, three BRISC performance figures are calculated using three sets of assumptions for the performance variables. The three performance figures provide a simple sensitivity analysis of the assumptions made, and are identified as BRISC A, BRISC B and BRISC C. BRISC A is a fictitious best case figure, unattainable but a reasonable upper bound on performance. BRISC B is a middle of the road figure, with conservative estimates used to calculate a plausible estimate of BRISC performance. BRISC C uses worst case figures to give a lower bound on performance.

#### 3.1.1. CPU Speed

CPU speed is determined by the basic cycle time of the CPU and the number of cycles per instruction. These numbers are presented, and suggestions made for possibly improving the BRISC CPU speed.

## 3.1.1.1. CPU Cycle Time

The SCALD system timing verifier was used to determine the BRISC CPU cycle time. The SCALD timing verifier uses worst case minimum and maximum delay times through all parts of the design to find timing errors. Output of the timing verifier may be used to calculate worst case logic delays. The timing verifier identified the register file read as the worst case path through the CPU. The register file is in the critical path because of the time required to do the register address calculation and the time required to read the register file RAM (7 as access time). The minimum time for a register file read including address calculation and RAM access time is 18.5 as. Assuming equal length phases, the BRISC minimum cycle time is therefore 37 as.

A 37 ns cycle time assumes worst case logic delays, but no wire delays. Wire delays account for about half the cycle time of many high performance CPUs, so the 37 ns cycle time for BRISC

needs to be corrected for wire delays. The SCALD system does not include a physical design system, so accurate values for the wire delays in BRISC are not available.

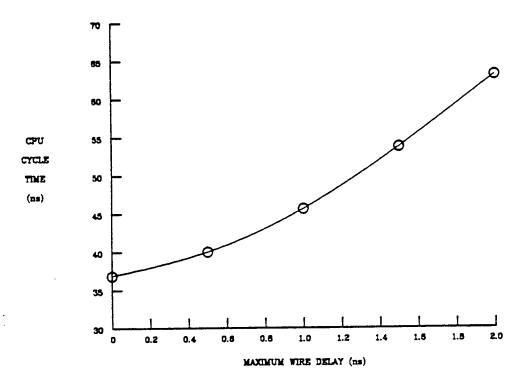

SCALD does provide a means to input an estimate of wire delay. Wire delay input is specified as a minimum and maximum delay to be used on all wires. The minimum and maximum numbers are used to find worst case delays as determined by worst case wire delays and worst case logic delays. Figure 4 shows the affect of different values of worst case wire delays on the BRISC cycle time as reported by the SCALD timing verifier.

Figure 4. BRISC CPU Cycle Time

The BRISC CPU has been designed to fit on a single board to keep wire lengths short and to avoid the delay penalty of connectors to other boards. It is assumed that chips will be located on the CPU board such that wire delay is minimized through the worst case path. For example, the register file address generation logic will be located in a small area to minimize worst case wire delays.

A best case wire delay of 0.0 ns is used for BRISC A, a median wire delay of 0.5-1.0 ns is used for BRISC B, and a worst case wire delay of 0.5-2.0 ns is used for BRISC C. The resulting CPU cycle times are 37 ns for BRISC A, 46 ns for BRISC B, and 63 ns for BRISC C. A median wire delay of 0.5-1.0 ns is considered reasonable because most of the parts in the critical path can be kept together. Adjacent ICs have a 0.5 ns delay between them, so most wires in the critical

path should be close to a 0.5 ns delay. A few wires may be longer than 2.0 ns, but the average in the worst case path is estimated to be 1.0 ns.

### 3.1.1.3. CPU Cycles Per Instruction

As stated in Section 3.1, BRISC completes an instruction every cycle except for the LOAD and STORE instructions that add an extra one or two cycles. RISC I requires one extra cycle for LOAD and STORE, and this extra cycle was considered in the original RISC I benchmarks. These benchmarks will be used to calculate BRISC performance, so the affect of a single extra cycle for loads and stores will be included. RISC I did not require a third cycle for unaligned loads and stores as required by BRISC. The benchmarks considered, however, only use 32-bit data, so all loads and stores in the benchmarks require only two cycles, and the third cycle may be safely ignored.

The affect of unaligned loads and stores on programs other than the benchmarks should be minimal. Loads and stores can be conservatively estimated to occur in 20% of RISC I instructions. Even if half of the loads and stores are unaligned, the total affect on BRISC performance is an 8% degradation in throughput. This performance degradation may be avoided by using only 32-bit data.

### 3.1.1.3. Design Changes

An advantage of using SCALD for designing a computer is that experiments may be tried with slightly different architectures to find the overall impact on performance and cost of alternative architectures. An architectural feature is justified only if the benefits of the feature outweigh the cost. For example, if a feature adds 3 ns per phase (6 ns per cycle) to the critical path because of a single logic delay and a wire delay, then that feature increases the 47 ns cycle time of BRISC B by 13%. The feature is therefore not worthwhile unless it makes up for the 13% decrease in CPU cycle time.

Even if a feature does not add gate delays to the critical path, if additional chips are required, the room required by the additional chips may add wire delays to the critical path, and the additional chips add to the total cost. Performance and cost impact is much more severe if an additional board is required.

A few architectural experiments have been run on the BRISC design. The ALU PATH, SHIFTER PATH, and CONTROL modules were redesigned several times to decrease parts count and increase speed. This section describes some further experiments that should be run to find the cost of specific architectural features. The changes are grouped under design deletions, design enhancements, and other changes.

#### Design Deletions

SEPARATE SYSTEM AND USER REGISTER FILES: The RISC I architecture does not include separate system and user register files. The separate files were added by RISC/E because the single 128-word register file required by the RISC I architecture occupied only half of the 256-word RAM. The unused half of the RAM was allocated to a second register file. Separate system and user register files do not directly affect BRISC CPU performance, but they do add complexity and parts to the BRISC CPU design and as a result may impact overall CPU performance. Complexity is added because ten registers of each register file are devoted to the global registers, which are shared by all register windows. In order to avoid addressing the global registers in the register file RAMs, additional RAMs are used (the ADDSUB module) to increment the Current Window Pointer (CWP). If the system registers were deleted, the global registers could be moved to the unused half of the register file RAM, counters could be used instead of the latches currently used in the CWP, and ADDSUB deleted. The system CWP and SWP could also be deleted, for a total chip savings of over 9 chips. CPU performance may be improved because of the smaller number of parts, but system performance may be degraded because of slower switching between system and user modes (but only if system mode required a separate stack from user mode).

REGISTER FILE: Since the register file is in the critical path, an interesting experiment would be to delete the register file entirely and replace it with a single set of registers as used in conventional architectures. Then register address calculation would be greatly simplified because the CWP would no longer be required and the register address determined only by the register number bits in the instruction. Deleting the register file would save at least two gate delays and associated wire delays for a total savings of at least 5 ns per phase (10 ns per cycle). A savings of 10 ns translates to a 21% performance increase for BRISC B. More than 30 chips would also be deleted from the design. The resulting CPU would be significantly faster and smaller, but calls, returns, and accesses to local variables would take many more instructions than required by the RISC I instruction set with the register file. More analysis needs to be performed to find the true cost of the register file.

REVERSE SUBTRACT: The REVERSE SUBTRACT instruction allows the two source operands of an instruction to be subtracted in the reverse order from the SUBTRACT instruction and is of questionable utility. REVERSE SUBTRACT has not been deleted because it does not seem to have any impact on the BRISC CPU performance or cost.

### Design Additions

MULTIPLY: As will be shown in the benchmark section, BRISC performs well on benchmarks with multiplies, even without a MULTIPLY instruction. But BRISC could be made even faster if MULTIPLY could be added with little impact to the rest of the CPU. This could be accomplished by adding a single chip multiplier in parallel with the ALU. Currently available single chip multipliers are significantly slower than the BRISC CPU cycle time, but are getting faster. As faster multipliers become available, a multiplier will be a useful addition to the BRISC CPU.

FLOATING POINT: BRISC is not well suited for problems with heavy floating point emphasis because of the lack of floating point hardware in the BRISC CPU. Floating point performance of BRISC could be enhanced by adding hardware to do the time consuming tasks of floating point operations. This is in keeping with the RISC philosophy of adding hardware only for time consuming tasks. A possible addition for floating point is the multiplier mentioned in the previous paragraph. Another addition would be a leading zeroes counter to be used with the shifter for normalization. Ideally, changes for floating point should not complicate control, instead they should only enhance the data path for floating point operations. More research is required to identify the best way to add floating point to a RISC processor.

#### Redesign

MULTIPLEXORS VS. OPEN-EMITTER BUSSES: BRISC uses two methods for selecting one of several sources into an input. One is a multiplexor on the input; the other is an OR-gate for each of the sources with outputs tied together on an open-emitter bus. Examples of multiplexor input can be found in the ALU PATH and SHIFTER PATH inputs. An example of an open-emitter bus is the result bus (RBUS) which is driven by the Last PC, Current PC and the RESULT LATCH. Open-emitter busses have less logic delay, but can have longer wire delays because of the length of the busses and transmission line effects along the busses. Open-emitter busses should only be used if the sources are close together, or if there are too many destinations to add multiplexors on every input. More analysis may show that BRISC should use a different mix of multiplexors and open-emitter busses to increase performance or decrease cost.

SHARED MULTIPLEXORS: Bussing may also be improved by combining multiplexors. For example, analysis may show that the SPECIAL REGISTER input multiplexor may be combined with the ALU PATH input multiplexor for a savings of six parts. Sharing multiplexors may have an adverse affect on CPU performance because of longer wires caused by the sharing of a single multiplexor between two logical portions of the CPU.

REGISTER ADDRESS CALCULATION: As stated previously, register address calculation is a major contributer to the critical path of the BRISC CPU. Register address calculation should be redesigned to save gate and wire delays in the critical path. One or two gate delays may be

saved by reallocating some of the random logic used for register address calculation. The expected performance increase is between 2 and 5 ns per phase (4 to 10 ns per cycle), for a performance gain of between 9 and 21% for BRISC B.

### 3.1.2. Memory Speed

Section 3.1.1 derived the CPU cycle time for BRISC and suggested methods of improving the cycle time. CPU cycle time was derived for BRISCs A, B, and C by using three sets of assumptions for wire delay. The purpose of this section is to derive numbers for the cycle times of BRISCs A, B, and C weighted by the delays caused by the memory subsystem. These numbers are used to calculate the speed of BRISCs A, B, and C relative to a 400 ns RISC II processor. Performance of a 400 ns RISC II processor is not degraded by the memory subsystem because address translation and main memory access occur within a single 400 ns cycle, so no cache or TLB is required.

Memory subsystem performance is determined by many factors including cache performance, virtual memory performance, and access time of main memory. These factors interact with each other and with the CPU performance.

This section assumes that the overhead incurred by the virtual memory for BRISC is minimal. Virtual memory overhead includes virtual address translation time and page fault time. Virtual address translation time can be kept low with the use of a Translation Buffer (TLB). For example, the observed hit ratio for the Amdahl 470V/6 TLB is about 99.6 to 99.7%. <sup>21</sup> The penalty incurred by page faults can be kept low by using a large physical memory to keep the page fault rate low, and by switching processes during disk accesses caused by page faults to minimize their affect.

If virtual memory overhead is assumed to be low, then memory subsystem performance is determined by the cache performance and main memory access time. Factors affecting cache performance include cache size, line size, set size, cache bandwidth, main memory bandwidth, cache fetch algorithm, placement algorithm, replacement algorithm, write-through vs. write-back, cache priorities, and prefetch. Smith provides an excellent discussion of these factors. <sup>21</sup> Appendix B shows the variability of these factors for some typical commercial computers as presented by Smith <sup>21</sup>, Pier <sup>16</sup> and Clark. <sup>3</sup>

For purposes of determining the memory subsystem performance, the cache performance factors mentioned in the previous paragraph may be summarized by three performance numbers: the access time of the cache, the cache hit ratio, and the memory waiting time due to cache misses. Access time of the cache is the time measured from the start of a memory request by the CPU to the time the request is fulfilled by the cache when there is a cache hit. Cache hit ratio is the percentage of CPU memory references that are found in the cache. Memory waiting time is

the average time that the CPU must wait for a cache miss. 3

The access time of the cache should be designed to be at least as fast as the cycle time of the CPU, otherwise the CPU will never run at full speed. The 10K ECL RISC/E cache is the same speed as the 10K ECL RISC/E CPU; therefore, it is assumed that a 100K ECL cache may be built for BRISC with the same cycle time as the 100K BRISC CPU.

Best case performance for the memory subsystem is a hit rate of 100% so that the CPU always runs at full speed; BRISC A assumes a 100% hit rate as the upper bound on performance.

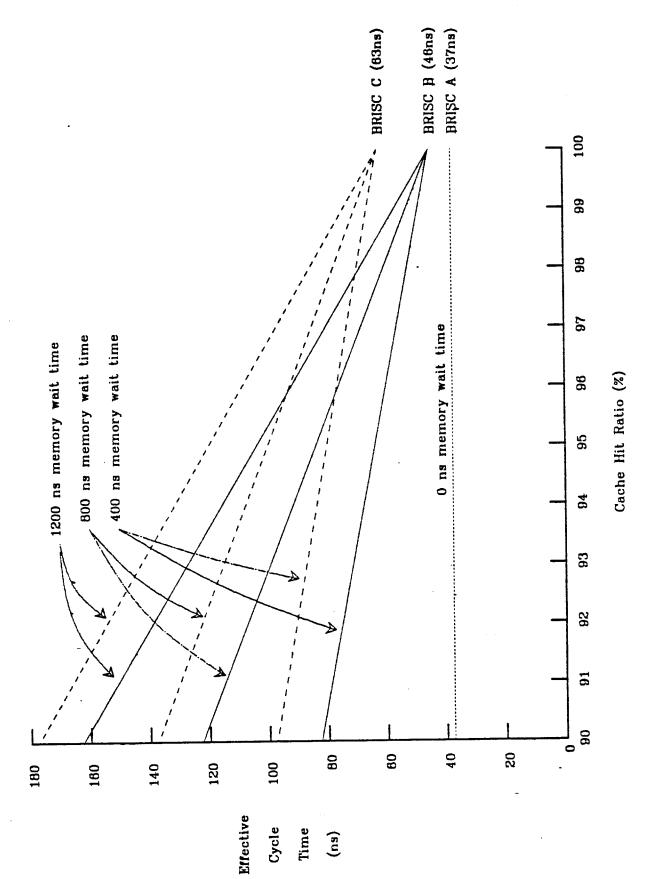

Figure 5 plots the affect of cache hit ratio and memory waiting time on BRISC B and BRISC C performance (Appendix C includes the data used to generate Figure 5). Three curves are shown for each processor, one each for 400, 800, and 1200 ns memory wait times. BRISC A with no memory wait time is also included for reference.

Smith <sup>21</sup> presents analytic results of cache hit ratios of over 99% for typical caches. He also presents empirical results of cache hit ratios of over 98% for user state programs on the Amdahl 470 with a 16K cache. Simulations performed by DEC for the PDP-11/70 cache showed a hit ratio of over 98% for a 2K cache with a line size of four words. <sup>2</sup> Based on these results BRISC B will assume a cache hit ratio of 98% as a reasonable estimate of cache performance.

Both the analytic and empirical curves presented by Smith seldom show less than a 95% hit ratio. DEC's simulations also show better than a 95% hit ratio for a 2K cache with a line size of one. As a worst case estimate, BRISC C will use a 95% hit ratio.

Memory waiting time may be approximated by the cycle time of main memory, as long as the line size equals the size of the path to main memory. Memory waiting time may be made less than the cycle time of main memory by using write buffers, but some of this gain may be lost because of interference from pre-fetches. Smith reports typical main memory access times of 300 to 600 ns for the Amdahl 470V/7 and IBM 3033. These numbers are similar to the main memory access times of smaller computers such as the Sun Workstation†, which has a main memory access time of 400 ns including virtual address translation time. <sup>22</sup> Clark reports a main memory access time of 1200 to 1400 ns for the VAX-11/780. <sup>3</sup> BRISC A is not affected by main memory access time since it has a 100% hit ratio; BRISC B assumes a 400 ns main memory access time and BRISC C assumes a 1200 ns main memory access time.

<sup>†</sup> Sen Workstation is a registered trademark of Sun Microsystems, Inc.

Figure 5. BRISC Effective Cycle Time

## 3.2. Benchmark Comparisons

Table 1 summarizes the performance of BRISCs A, B, and C based on the results of Section 3.1. The cycle times of 37, 53 and 120 ns were divided into the 400 ns cycle time of RISC II to determine the ratio of BRISC cycle time to RISC II cycle time, which is shown in the bottom line of Table 1. This ratio is used to calculate BRISC performance in the following benchmarks.

| Table 1. BRISC A. B and C                                                               | Table 1. BRISC A, B and C Performance Summary |                         |                         |  |  |  |  |  |

|-----------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------|-------------------------|--|--|--|--|--|

| FACTOR                                                                                  | BRISC A                                       | BRISC B                 | BRISC C                 |  |  |  |  |  |

| Logic Cycle Time (ns) Clock Skew (± ns) Minimum Wire Delay (ns) Maximum Wire Delay (ns) | 37<br>0.0<br>0.0<br>0.0                       | 37<br>0.1<br>0.5<br>1.0 | 37<br>0.1<br>0.5<br>2.0 |  |  |  |  |  |

| TOTAL CPU CYCLE TIME (ns)                                                               | 37                                            | 46                      | 63                      |  |  |  |  |  |

| Cache Hit Ratio Miss Penalty (ns)                                                       | 100%                                          | 98%<br>400              | 95%<br>1200             |  |  |  |  |  |

| EFFECTIVE CPU CYCLE TIME (ns)                                                           | 37                                            | 53                      | 120                     |  |  |  |  |  |

| BRISC/RISC II Cycle Time Ratio                                                          | .09                                           | .13                     | .30                     |  |  |  |  |  |

The original RISC II benchmarks were run with a RISC simulator. The RISC simulator takes into account the extra cycle required for loads and stores, and also takes into account the affect of register window spills into main memory. Three benchmarks are presented, the Puzzle program, TAK LISP benchmark, and UNIX Portable C Compiler. Three benchmarks are used to measure BRISC performance for different applications. Each benchmark presents the time in seconds to execute the benchmark. Benchmark performance is also presented as a multiple of VAX-11/780 performance, shown as the ratio of the number of seconds required by the VAX divided by the number of seconds required by the computer being measured. VAX performance is used because the VAX has become a pseudo-standard for comparison, and because a BRISC computer could be built for about the cost of a VAX.

#### Pussie Program

The Puzzle program is a recursive puzzle solving program originated by Forest Baskett that has been used to benchmark many mainframe and minicomputers. Selinger <sup>19</sup> presents listings of the Puzzle program and sources of Puzzle benchmark data for many computers. Patterson and Séquin<sup>14</sup> identify benchmark results for a 400 ns RISC I. Table 2 lists the results of Puzzle benchmarks for BRISCs A, B and C relative to the Selinger and Patterson numbers. Table 2 only lists the better numbers where conflicting data is available for the same machine. BRISCs A and B outperform all available Puzzle times; even the worst case BRISC C outperformed all benchmarks except for the best time reported for the Amdahl 470V/8.

|                  | 1    | able 2. Puzzle | e Benchmark R | esults               |         |

|------------------|------|----------------|---------------|----------------------|---------|

|                  |      | TIME           | LANGUAGE      | COMMENTS             | CPU     |

| MACHINE          | sec  | VAX sec/sec    | LANGUAGE      | COMMENTS             | COST    |

| BRISC A (37 ns)  | 0.3  | 11.8           | C             | pointers             | \$132K  |

| BRISC B (53 ns)  | 0.4  | 8.3            | C             | pointers             | \$132K  |

| Amdahl 470V/8    | 0.7  | 5.0            | C             | pointers, reg vars   | \$1100K |

| BRISC C (120 ns) | 1.0  | 3.6            | C             | pointers             | \$132K  |

| Amdahi 470V/8    | 1.1  | 3.2            | C             | pointers             | \$1100K |

| Amdahl 470V/8    | 1.1  | 3.2            | Pascal        | no range checking    | \$1100K |

| Amdahl 470V/8    | 1.2  | 2.9            | C             | reg vars             | \$1100K |

| IBM 3081         | 1.4  | 2.5            | Pascal        |                      | \$3260K |

| Amdahl 470V/8    | 1.6  | 2.2            | C             | subscripts           | \$1100K |

| S-1 Mark 1       | 2.0  | 1.8            | Pascal        | subscripts           | \$2000K |

| Dorado           | 2.0  | 1.8            | Mesa          | pointers             | \$118K  |

| Amdahl 470V/8    | 2.3  | 1.5            | Pascal        |                      | \$1100K |

| Dorado           | 3.0  | 1.2            | Mesa          | subscripts           | \$118K  |

| RISC II (400 ns) | 3.2  | 1.1            | C             | pointers             | \$10K   |

| VAX 11/780       | 3.5  | 1.0            | l c           | pointers             | \$132K  |

| DEC 2060         | 4.4  | 0.8            | Pascal        | pointers             | \$502K  |

| DEC 2060         | 4.6  | 0.8            | C             | pointers, hand opt   | \$502K  |

| VAX 11/780       | 4.6  | 0.8            | C             | subscripts           | \$132K  |

| RISC II (400 ns) | 4.7  | 0.7            | l c           | subscripts           | \$10K   |

| DEC 2060         | 4.7  | 0.7            | c             | subscripts, hand opt | \$502K  |

| DEC 2060         | 5.3  | 0.7            | C             | pointers             | \$502K  |

| DEC 2060         | 5.4  | 0.6            | Pascal        | subscripts           | \$502K  |

| DEC KL10         | 6.0  | 0.6            | C             | pointers             | \$540K  |

| VAX 11/780       | 6.1  | 0.6            | Pascal        | subscripts           | \$132K  |

| PDP 11/70        | 6.4  | 0.5            | C             | pointers             | \$70K   |

| DEC 2060         | 7.3  | 0.5            | C             | subscripts           | \$502K  |

| IBM 158          | 7.5  | 0.5            | Pascal        | subscripts           | \$1550K |

| 68000 (8 MHz)    | 17.0 | 0.2            | C             | pointers, nunix      | \$10K   |

#### TAK Benchmark

The TAK benchmark is a heavily recursive function used to measure the efficiency of LISP procedure calls as well as the efficiency of LISP fixnum and bignum arithmetic. <sup>17</sup> Fixnum arithmetic refers to integers of bounded length, whereas bignum arithmetic refers to integers of unbounded length. Figure 6 is a listing of the TAK benchmark. Table 3 presents the results reported by Ponder compared to the times calculated for BRISC. BRISCs A and B again outperform all available benchmarks; BRISC C is only beat by the Dorado.

Ponder estimated RISC I performance for LISP by compiling the LISP code on a VAX and hand translating the output to RISC I assembly code. Ponder states that a LISP compiler optimized for RISC could be built with better performance than is shown in Table 3. Recent studies by Ponder show that with minor enhancements a 400 ns RISC processor could be built that executed the TAK benchmark in under 0.66 seconds. This translates to times of 0.06, 0.09 and 0.20 seconds for BRISCs A, B, and C (5.6 to 18.0 times faster than a VAX).

Figure 6. TAK Benchmark

| Tab              | le 3. | TAK Benchm  | ark Results    |        |

|------------------|-------|-------------|----------------|--------|

|                  |       | TIME        | LANGUAGE       | CPU    |

| MACHINE          | sec   | VAX sec/sec | LANGUAGE       | COST   |

| BRISC A (37 as)  | 0.2   | 5.9         | PSL/Franz LISP | \$132K |

| BRISC B (53 ns)  | 0.3   | 4.2         | PSL/Franz LISP | \$132K |

| Dorado           | 0.5   | 2.2         | InterLISP      | \$118K |

| BRISC C (120 ms) | 0.6   | 1.8         | PSL/Franz LISP | \$132K |

| DEC KL10         | 0.8   | 1.4         | MacLISP        | \$540K |

| VAX 11/780       | 1.1   | 1.0         | Franz LISP     | \$132K |

| RISC II (400 ns) | 2.0   | 0.6         | PSL/Frans LISP | \$10K  |

| 68000 (8 MHz)    | 2.9   | 0.9         | PSL SYSLISP    | \$10K  |

| Dolphin          | 5.7   | 0.2         | InterLISP      | \$40K  |

## C Compiler

Miros ported the Portable C Compiler by Steve Johnson <sup>8</sup> to RISC L <sup>12</sup> After porting the compiler, Miros compared the performance of the VAX Portable C Compiler running on a VAX to the VAX Portable C Compiler running on a 400 ns RISC L His results are presented in Table 4. BRISCs A, B, and C are all significantly faster than a VAX.

| Ta               | ble 4. | VAX Portable      | C Co | mpller Benchm        | ark F | lesults                |        |

|------------------|--------|-------------------|------|----------------------|-------|------------------------|--------|

| MACHINE          |        | LD.C<br>PILE TIME |      | SORT.C<br>APILE TIME | F     | PUZZLE.C<br>MPILE TIME | CPU    |

| MACIMAD          | sec    | VAX sec/sec       | sec  | VAX sec/sec          | sec   | VAX sec/sec            |        |

| BRISC A (37 ns)  | 1.6    | 17.8              | 1.0  | 17.7                 | 0.3   | 19.4                   | \$132K |

| BRISC B (53 ns)  | 2.2    | 12.5              | 1.4  | 12.4                 | 0.4   | 13.5                   | \$132K |

| BRISC C (120 ns) | 5.1    | 5.5               | 3.2  | 5.5                  | 0.9   | 6.0                    | \$132K |

| RISC II (400 ns) | 16.9   | 1.7               | 10.6 | 1.6                  | 29    | 1.8                    | \$10K  |

| VAX 11/780       | 27.9   | 1.0               | 17.4 | 1.0                  | 5.2   | 1.0                    | \$132K |

## Benchmark Summary

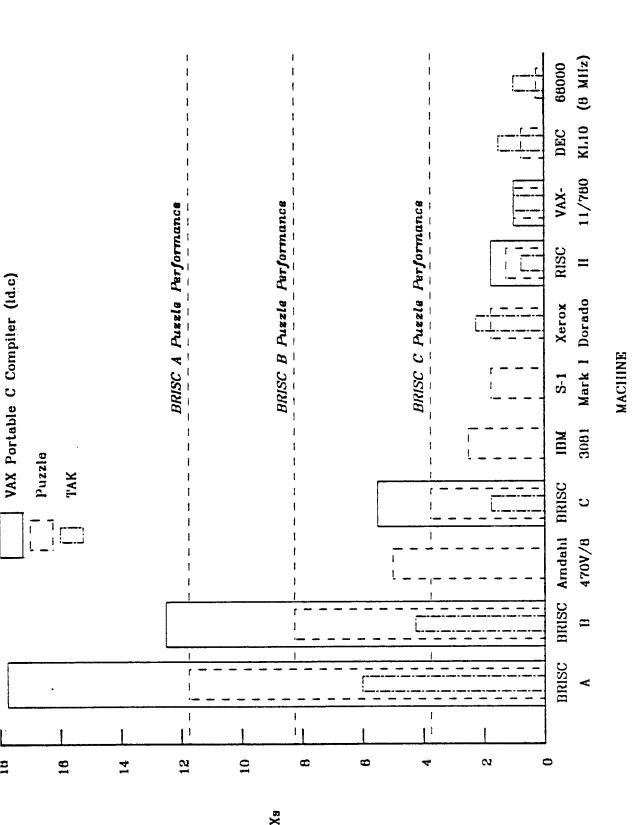

Figure 7 is a summary of some of the results from the above benchmarks. The best times are shown for four mainframes, two minicomputers, and two microcomputers. Performance is shown as a multiple of VAX performance. BRISCs A and B outperform all the listed computers, and BRISC C is competitive. Using BRISC B as the best estimate of BRISC performance, BRISC is 8 to 13 times faster than a VAX for C programs, and 4 times faster than a VAX for LISP programs.

#### 4. Cost

Much as performance is determined by the combination of many factors, so is cost determined by many factors. Selinger defines computer workstation cost as the sum of the manufacturing and labor costs of parts, boards, cables, logic cages, backplanes, cabinets, power distribution back panel, front panel, assembly, and test. <sup>19</sup> He then defines price as the sum of manufacturing cost, development cost, sales cost, service cost, and profit or loss. It is beyond the scope of this paper to estimate the values of all these items to calculate the price of a computer built around the BRISC CPU. Instead, the cost of a BRISC computer will be estimated by comparing BRISC to an existing computer to calculate the relative price of BRISC. The Dorado <sup>9</sup> computer by Xerox was selected as the existing computer for comparison because it is also an ECL computer, and is about the same size as a system built around BRISC.

The Dorado is a high-performance personal computer consisting of 3200 medium scale integrated components (not including memory), most of which are ECL 10K. <sup>16</sup> The Dorado contains everything a BRISC computer would need including up to 8 Megabytes of main memory, a high-performance cache with a 30 ns cycle time, peripheral interfaces, and a large 2050 watt power supply producing sufficient power and ECL voltages (-5V at 250A and -2V at 75A).

The cost for a BRISC computer is calculated by comparing the cost of the BRISC CPU to the Dorado CPU and keeping all other costs the same. The difference in cost of the two CPUs is found by first determining the difference in the number of chips. To compare the number of chips in the Dorado with the number of chips in BRISC, a lower bound is determined for the number of chips in the Dorado that would be replaced by the BRISC CPU.

The Dorado consists of up to 24 boards with up to 288 chips per board. Five of the 24 boards constitute the Dorado CPU and are listed in Table 5. Table 5 also lists a lower bound for the number of chips on each of the five boards in the CPU. 17

About half of the Instruction Fetch Unit (IFU) is used to control the memory, the other half is devoted to the CPU; the IFU will not be considered as part of the CPU to obtain a conservative estimate.

Figure 7. Performance Summary

| Table 5. Dorado CPU Boards                                                                            |                                             |                                                 |  |  |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------|--|--|

| BOARD                                                                                                 | % POPULATED                                 | # CHIPS (288 Max)                               |  |  |

| Instruction fetch unit Processor high byte Processor low byte Control section Microinstruction memory | 80%<br>90-95%<br>90-95%<br>90-95%<br>90-95% | 230<br>260-275<br>260-275<br>260-275<br>260-275 |  |  |

The Dorado CPU performs task switching at the microcode level. Microcode tasks are called microtasks. Some microtasks are used as device controllers - a DMA controller would therefore be required if the Dorado CPU was removed. A DMA controller would be no more complex than the Control Section of the Dorado, so the Control Section will not be counted as part of the Dorado CPU.

Ignoring the IFU and Control Section leaves three boards in the Dorado CPU: the Processor High Byte, Processor Low Byte, and the Microinstruction Memory. These three boards contain about 780 chips. The 332 100K chips of the BRISC CPU would occupy the same board space required by about 664 10K chips because of the 24-pin packages used by the 100K parts versus the 16-pin packages used by the 10K parts. The BRISC CPU therefore requires 15% less board area than the Dorado CPU. Insertion cost is also 15% less for BRISC; 24-pin packages cost twice as much to insert as 16-pin packages, <sup>19</sup> but BRISC has 43% the number of chips of the Dorado CPU.

In order to calculate a conservative estimate for the cost of a BRISC CPU, the Dorado and BRISC CPUs are assumed to have the same PC board and IC insertion costs. PC board and insertion costs being equal, the difference in cost of the two CPUs will therefore be largely determined by the difference in parts cost. Parts cost of the Dorado CPU is not known (except by Xerox). The least expensive 10K part sells for 61 cents in quantities of 100 to 1000, so a lower bound on parts cost for the Dorado CPU is \$475.80. The BRISC parts list (Appendix D) shows the parts cost of BRISC is \$3330.32 in parts quantities of 100 to 1000. The resulting parts cost difference between the BRISC CPU and the Dorado CPU is at most \$2854.52. Selinger calculated the markup for the VAX-11/780 to be 5.2 times, which he showed to be consistent with the markups used by other manufacturers. Using a 5.2 times markup for the parts differential between BRISC and Dorado gives a selling price difference of \$14,843.50. Dorados sell for \$129,500 with 2 Megabytes (MB) of main memory and an 80 MB disk. Discounting for the cost of an 80 MB disk (\$11,900) 23 gives a selling price of \$117,600 for the Dorado without peripherals. A BRISC computer could therefore be sold for less than \$14,843.50 over the \$117,600 seiling price of a Dorado, or about \$132,444. This is nearly identical to the price of a VAX-11/780 without peripherals, which Selinger calculates to be \$132,400 with 1 MB of main memory (the Dorado comes with 2 MB).

#### 5. Closing Remarks

This section presents retrospectives by the BRISC designers on the BRISC project.

## 5.1. Comments on SCALD

The BRISC project would not be at the point it is today without the SCALD system. SCALD has proven to be an invaluable tool for computer design. Traditionally, computer design has been a rigid process because of the difficulty of making changes to hardware once it is built. SCALD provides a vehicle to do exploratory hardware design, much as a good programming environment allows exploratory programming. Bean Sheil defines exploratory programming as an approach to programming combining system design with implementation. <sup>20</sup> In an exploratory programming environment, the programmer experiments with changes to the design and immediately sees their effect on the operation of the system. Exploratory hardware design combines design and implementation in the sense that the hardware designer can make changes to the hardware design and immediately see the effect on the operation of the hardware system. Effects are seen by using timing verification, simulation and post processing rather than by building and testing physical hardware. In this way many possible solutions to the same problem may be tried and evaluated, and the best solution selected. The best solution is picked on the basis of logical correctness, speed and parts cost.

SCALD provides the equivalent of what Sheil calls programming power tools in the form of five application programs: a graphics editor, compiler, timing verifier, simulator, and post processor. These tools amplify the power of the hardware designer so that he can produce a better design in less time.

As with most software tools, the tools provided by the Valid SCALD system have several deficiencies that detract from the usefulness of the system, the most noteable being the speed of the system. This section describes the speed of the Valid SCALD system and comments on each of the Valid SCALD tools from the point of view of the BRISC designers.

#### 5.1.1. SCALD Speed

While SCALD comes a long way in making exploratory hardware design as simple as exploratory programming, the single biggest detractor is the speed of the SCALD system. Exploratory hardware design implies interactive use of the SCALD system, which means that fast response is required for most commands (i.e. less than one second), and response time may occasionally go up to 30 seconds. Studies have shown that user productivity goes down when response times go over three seconds, probably because of the disruption of user thought processes. <sup>24</sup>

Table 6 lists a few of the response times encountered during the BRISC design. While Valid has significantly improved the speed of the post processor - it once took over six hours for BRISC with 606 parts, and now only takes 12 minutes with 332 parts - the response times need to be much better to allow true interactive design.

| Table 6. Valid SCALD Speed |                        |               |                        |                    |

|----------------------------|------------------------|---------------|------------------------|--------------------|

| FUNCTION                   | APPLICATION<br>PROGRAM | MODULE        | ELAPSED TIME (min:sec) | CPU TIME (min:sec) |

| Timing Verification Time   | Compiler               | PCs & Address | 3:58                   | 3:23               |

|                            |                        | BRISC         | 23:19                  | 22:21              |

|                            | Timing                 | PCs & Address | 2:31                   | 2:30               |

|                            | Verifier               | BRISC††       | 13:32                  | 12:19              |

| Simulation                 | Compiler               | PCs & Address | 4:13                   | 3:37               |

|                            |                        | BRISC         | 32:26                  | 26:56              |

|                            | Simulator              | PCs & Address | 7:10                   |                    |

|                            | (start-up)             | BRISC         | 17:59                  |                    |

|                            | Simulator              | PCs & Address | :04                    |                    |

|                            | (per cycle)            | BRISC         | :36                    |                    |

| Processing                 | Compiler               | PCs & Address | 1:59                   | 1:28               |

|                            |                        | BRISC         | 10:19                  | 9:34               |

|                            | Post Processor         | PCs & Address | 1:40                   | 1:38               |

|                            |                        | BRISC         | 12:23                  | 12:19              |

†Does not include PCs & Address, Cache, Special Registers, or Result Latch.

In fairness to Valid it should be mentioned that the Valid SCALD system used for BRISC runs on a 68000. Valid also sells SCALD systems for VAXs (with the VMS operating system) and IBM 370s. Table 2 may be used to compare the performance and cost of the 68000, VAX and IBM 370 (Models 158 and 3081).

#### 5.1.2. Graphics Editor

The graphics editor proved to be a useful tool for entering drawings and changing drawings after they were entered. The graphics editor is very fast for most drawings and encourages interactive design. The graphics editor's interactive nature made it much more useful than other drawing tools previously available at Berkeley.

#### 5.1.3. Complier

The compiler converts drawings from the format created by the graphics editor to a format usable by the timing verifier, simulator and post processor. As such, the compiler is nothing more than an intermediary between the graphics editor and the other applications as opposed to a design tool.

The compiler has proven useful for finding assertion violations. Assertion violations are signals that are asserted high which are inadvertently tied to signals that are asserted low. While only a few such errors have been found by the compiler in BRISC, the errors were detected faster and corrected sooner than if they had been found with the simulator (see Table 6).

The compiler is not designed for interactive use. A command file must be edited every time a different type of output is required (i.e. for the timing verifier, simulator or post processor), and every time a different drawing is compiled. The command file supports batch versions of SCALD, and is not appropriate for an interactive environment.

## 5.1.4. Timing Verifier

The timing verifier uses minimum and maximum timing parameters for all parts in a circuit to calculate a value history of all signals during a single clock cycle. The timing verifier has two uses, one is to find timing violations such as changing signals violating set-up times, the other is to calculate the cycle time of a circuit.

## Timing Violations

The timing verifier is useful when it finds valid timing violations, but is sometimes difficult to use and is too conservative. To get realistic outputs, timing behavior of undriven inputs to a circuit must sometimes be specified, otherwise all signals may stay stable and no verification will occur. Sometimes, the timing verifier is so conservative that it finds errors that could never occur in a real circuit. For example, the timing verifier once identified the input to a flip-flop to be changing before the clock, even though the input was driven by the negative output of the flip-flop (that cannot possibly change before the clock).

Some timing violations cause the timing verifier to go into an endless loop, making them exceedingly difficult to find. A few timing violations have been detected in BRISC by the timing verifier; mostly with the endless loop method.

#### Cycle Time Calculation

The timing verifier does not automatically identify the worst case path through a circuit, as is done by Crystal. <sup>12</sup> Instead, the designer must examine the value history of all signals in a circuit and find the signal that is stable last. The worst case path is important for two reasons. First, the delay through the worst case path must be known to find the minimum cycle time of a circuit. Second, the designer should concentrate on optimizing the worst case path to speed up the circuit, but he needs to know the worst case path before he can fix it. The minimum cycle time may also be found by running the timing verifier with successively shorter and shorter clock cycles until timing errors are found; that still does not identify the worst case path and is time

consuming.

Since large CPUs tend to spend about half of their cycle times in wire delays, it is essential that wire delays be included in timing verifier calculations. Wire delays for ECL should include both delays due to the length of the wires, and delays induced by loads along the wires. Because of the speed of ECL, most wires act like transmission lines, and the wire delay calculator should treat them as such. As was mentioned in Section 3.1.1.1, a single pair of minimum and maximum wire delays may be specified to the verifier, but that is too crude an approximation. Alternatively, the timing verifier does have the capability to accept calculated wire delays from a physical design system, but the Valid SCALD system does not include a physical design system. Even though a SCALD design may be transformed into the input format of another vendor's design system, this precludes exploratory hardware design because it is no longer interactive; the design cycle is measured in days instead of minutes when two design systems are used.

#### 5.1.5. Simulator

The simulator does logic simulation of a circuit to verify logical correctness of a design. The simulator is potentially the most useful of the SCALD tools, but it also takes the longest to get any results and to correct errors that are found. The simulator has been used to simulate the operation of the PCs AND ADDRESS, the ALU PATH, and the SHIFTER PATH. These modules were picked for simulation because they each do a well defined logical function. The entire BRISC design has been loaded into the simulator, but simulation has only been partially completed because of lack of time.